Multibit-Generating Pulsewidth-Based Memristive-PUF Structure and Circuit Implementation

Abstract

1. Introduction

- We present the electrical characteristics of an analog memristor model exposed to varied numbers of pulses with different pulsewidths and show that this memristor model is beneficial for wide variations.

- We propose a new structure for a memristor-based PUF that utilizes fabrication variations that are physically inherent in nanoelectronic devices. A practical bank design is suggested for a multibit-generating pm-PUF.

- The circuit implementation of the proposed pm-PUF architecture and its operation are described in detail.

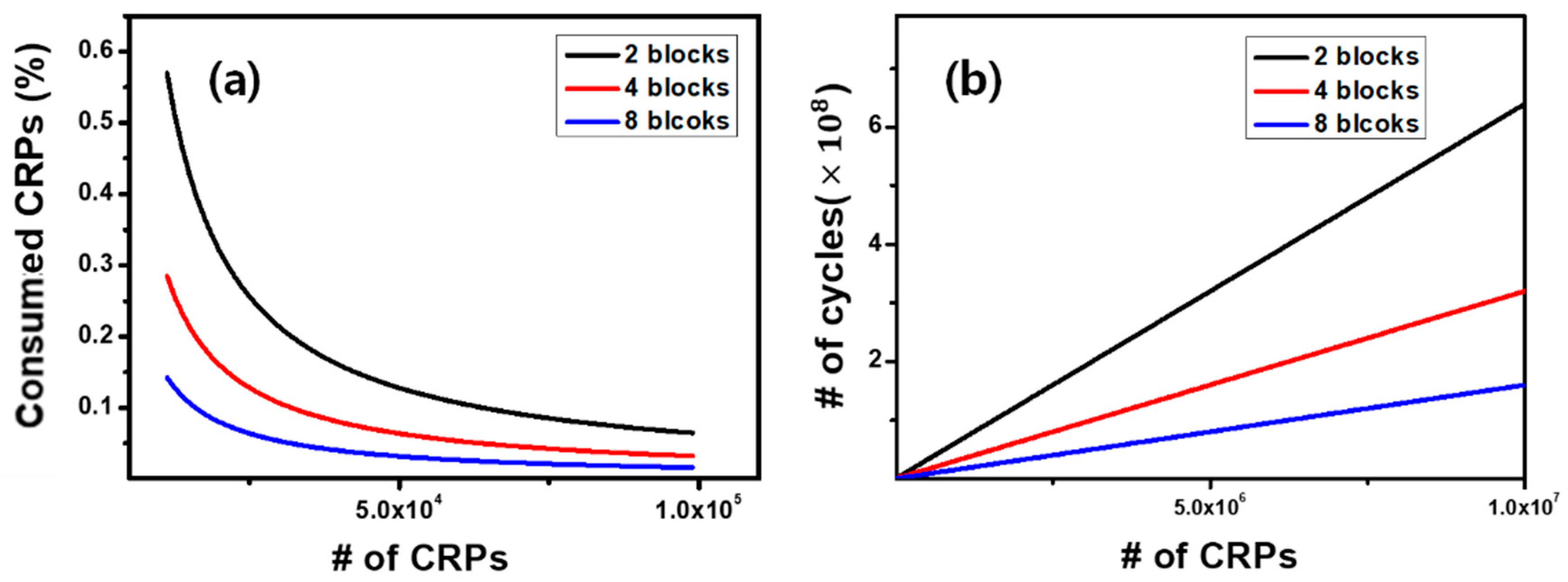

- The multiple bits stored in a single pm-PUF cell by quantization resolve the problem of wasted CRPs, dramatically reducing the pulse cycles required to generate them.

- We report on a circuit simulation with HSPICE to demonstrate the unique performance of pm-PUFs in terms of randomness, diffuseness, uniqueness, and steadiness. The evaluation methods are also explained.

2. Materials and Methods

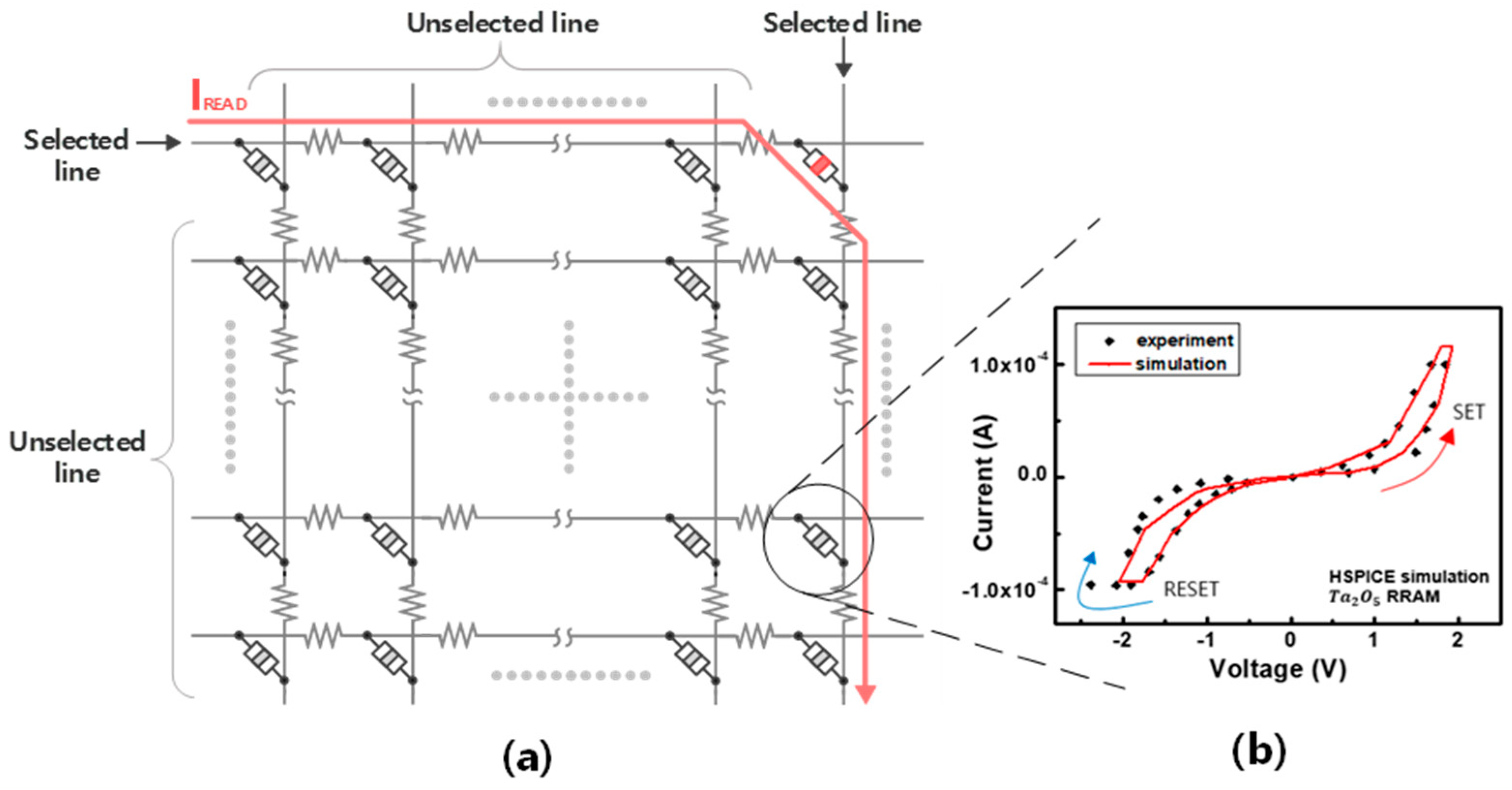

2.1. Cross-Point Array and Memristor Model

2.2. Initial Distributions

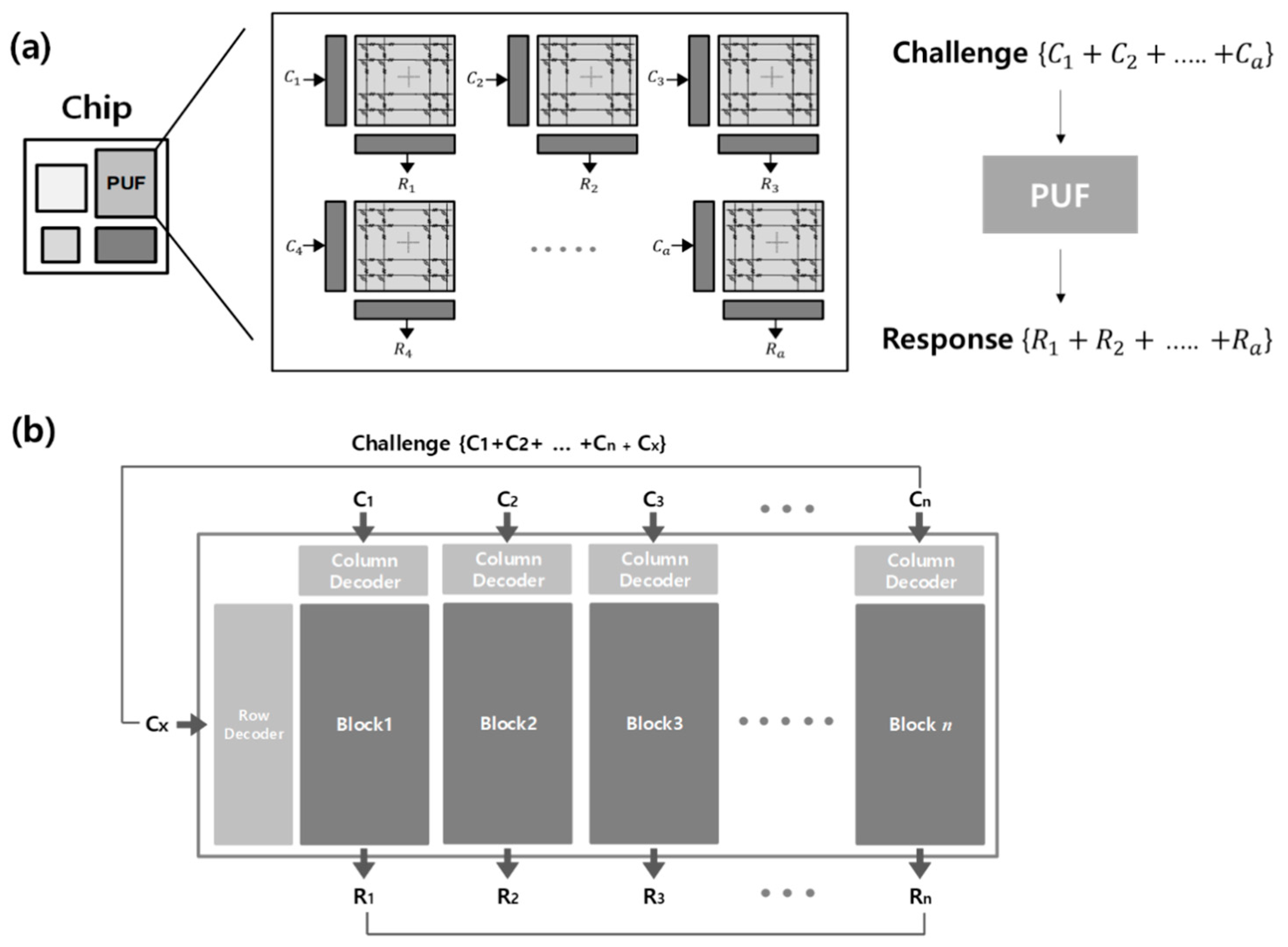

2.3. Concept of Bank Design

2.4. Pm-PUF Architecture

3. Results

3.1. Simulation Environment

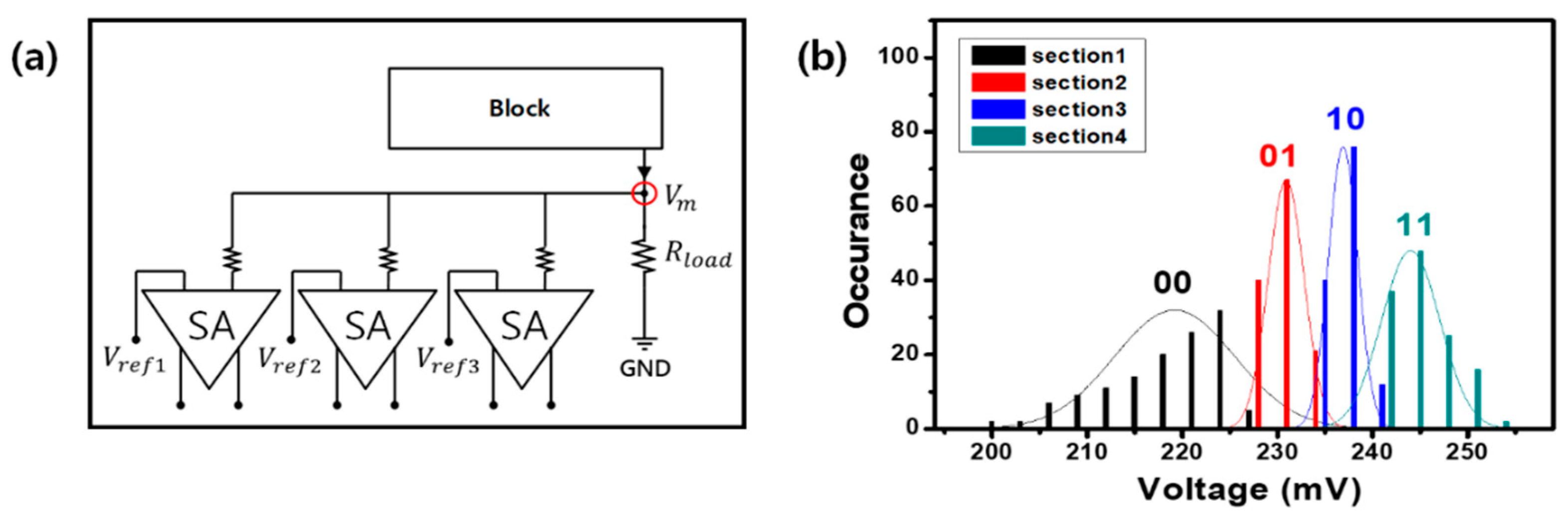

3.2. Performance Evaluation

- (1)

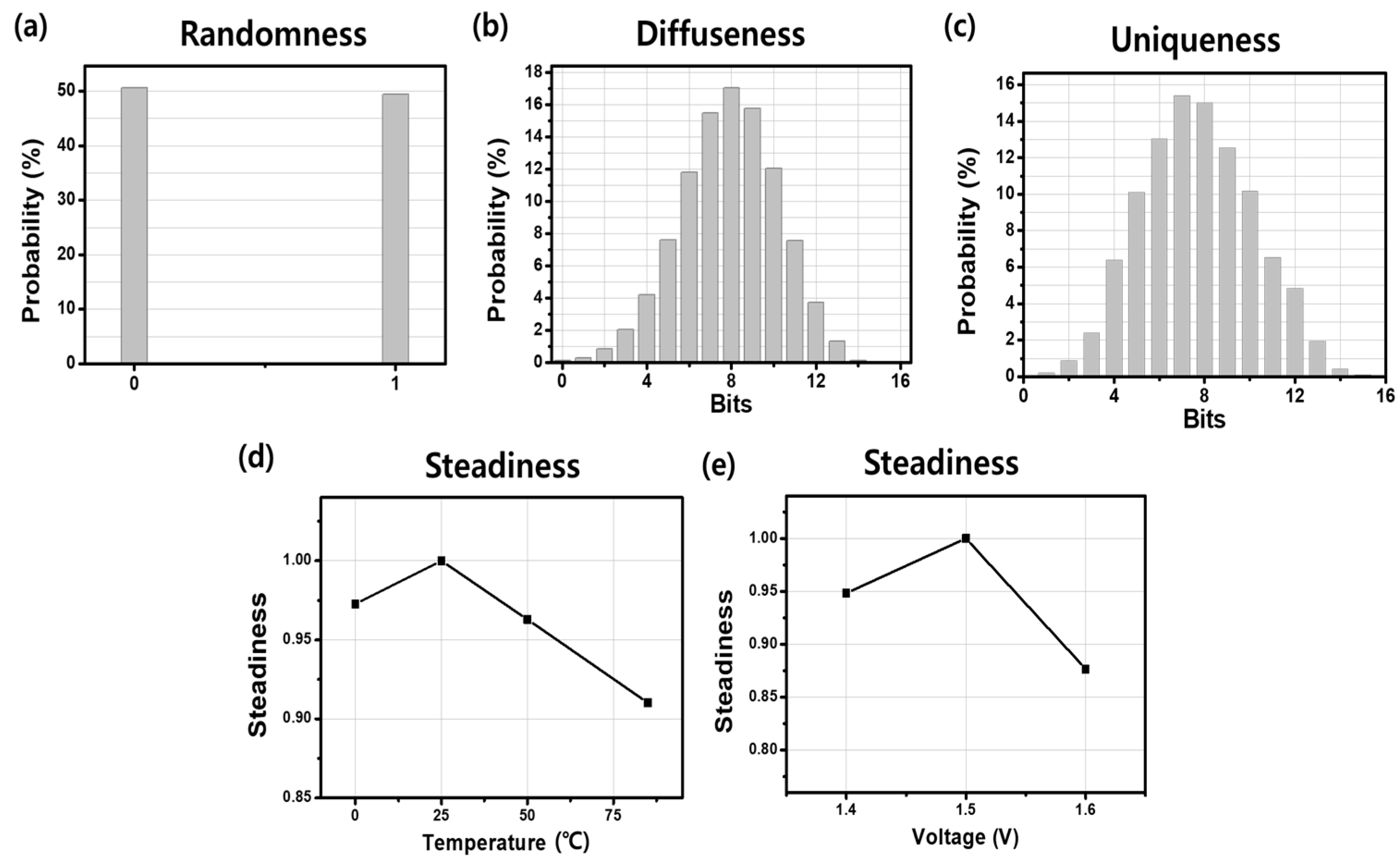

- Randomness. Ideal “0” and “1” response bits generated from a PUF are expected to be equiprobable. Randomness is a measure of the balance of “0” and “1” values in the responses; Equations (9) and (10) define the randomness . Randomness is not related to the response generating mechanism because only the frequency of the two values is considered. To measure the frequency, we investigated 5500 responses obtained from the pm-PUF. The randomness of the pm-PUF is 0.9828 (98.28%), slightly lower than the ideal value of 1. This randomness corresponds to the probability of a “0” being 50.6% (49.4% for a “1”), as shown in Figure 6a. Therefore, almost 8 bits (8.096 bits) out of a 16-bit response are likely to be 1, which indicates that the pm-PUF shows a high degree of randomness.where is the experimentally generated the lth bit of the kth response in device n in the tth test and is the relative frequency of 1 in all the response bits generated in device n.

- (2)

- Diffuseness. Diffuseness indicates the degree of difference among the responses obtained by applying different challenges to the same PUF. Diffuseness is determined by calculating the intra-hamming distance (intra-HD) of all possible responses from a PUF instance, as shown in Equations (11) and (12). To measure the diffuseness of the pm-PUF, we applied 5500 sets of random challenge bits to the PUF and obtained 5500 sets of 16-bit response bits. The distribution of intra-HDs among the obtained responses is shown in Figure 6b, and the mean of the HDs is 7.886 bits, which means 49.29%. The diffuseness of the pm-PUF as calculated with the equations below is 0.9871, which is close to the highest value of 1, thus the PM-PUF is expected to have high intra-device performance.where is the sum of HD of the possible bit combinations in .

- (3)

- Uniqueness. When the same challenges are applied to different PUF instances, the responses are expected to be different due to the variations of the PUFs. Uniqueness indicates the probability of difference between responses from the same challenge applied to different PUFs. Uniqueness can be calculated with the inter-HDs of responses from different PUFs and is defined below in Equation (13). To evaluate the uniqueness of the pm-PUF, we used 100 different PM-PUF instances, and the distribution of the number of different bits among the responses is shown in Figure 6c. The figure shows an inter-HD mean of 47.93%, which is 7.67 bits out of the 16-bit response. From Equation (13), the uniqueness of the pm-PUF is 0.9507, which is close to the ideal value of 1.

- (4)

- Steadiness. Steadiness (or reliability) indicates how stably a PUF operates. When the same challenge is applied to the same PUF several times, the responses are expected to be identical. However, due to environmental changes such as temperature and voltage shifts, steadiness can become a critical problem [35]. To evaluate the steadiness of the pm-PUF, we obtained a 256-bit response by repeatedly applying a set of random challenges at varied temperatures (0, 25, 50, and 85 °C) and voltages (1.4, 1.5, and 1.6 V) and by comparing the response bits. The reference response was obtained with 1.5 V at 25 °C. Steadiness can be measured based on the number of bit flips in the response bits during multiple tests. Device steadiness is defined as Equations (14) and (15). An ideal intra-HD between the responses under different operating conditions is 0 bits which corresponds to a steadiness of 1. The results are displayed in Figure 6d,e. Figure 6d shows that the worst steadiness of the pm-PUF is 0.9102 when the temperature is 85 °C. At the other temperatures, the pm-PUF also shows high steadiness (0.9726 at 0 °C and 0.9628 at 50 °C). In Figure 6e, the pm-PUF shows its worst voltage steadiness of 0.8765 for 1. 6V and 0.9484 for 1.4 V.where is the relative frequency of 1 in the lth bit of the kth response in device n and is the steadiness of the lth bit of the kth response expected to be generated in device n.

4. Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Shamsi, K.; Jin, Y. Security of emerging non-volatile memories: Attacks and defenses. In Proceedings of the 34th IEEE VLSI Test Symposium, Las Vegas, NV, USA, 25–27 April 2016; pp. 1–4. [Google Scholar]

- Herder, C.; Yu, M.; Koushanfar, F.; Devadas, S. Physical Unclonable Functions and Applications: A Tutorial. Proc. IEEE 2014, 102, 1126–1141. [Google Scholar] [CrossRef]

- Uddin, M.; Majumder, M.B.; Rose, G.S. Robustness Analysis of a Memristive Crossbar PUF against Modeling Attacks. IEEE Trans. Nanotechnol. 2017, 16, 396–405. [Google Scholar]

- Uddin, M.; Majumder, B.; Rose, G.S. Nanoelectronic Security Designs for Resource-Constrained Internet of Things Devices: Finding Security Solutions with Nanoelectronic Hardwares. IEEE Consum. Electron. Mag. 2018, 7, 15–22. [Google Scholar] [CrossRef]

- Pappu, R.; Recht, B.; Taylor, J.; Gershenfeld, N. Physical one-way functions. Science 2002, 297, 2026–2030. [Google Scholar] [CrossRef] [PubMed]

- Gao, Y.; Ranasinghe, D.C.; Al-Sarawi, S.F.; Kavehei, O.; Abbott, D. Emerging physical unclonable functions with nanotechnology. IEEE Access 2016, 4, 61–80. [Google Scholar] [CrossRef]

- Suh, G.E.; Devadas, S. Physical unclonable functions for device authentication and secret key generation. In Proceedings of the 44th ACM/IEEE Design Automation Conference 2017, San Diego, CA, USA, 4–8 June 2007; pp. 9–14. [Google Scholar]

- Ardakani, A.; Baradaran Shokouhi, S. A secure and area-efficient FPGA-based SR-Latch PUF. In Proceedings of the 8th International Symposium on Telecommunications (IST), Tehran, Iran, 27–28 September 2016; pp. 94–99. [Google Scholar]

- Gassend, B.; Clarke, D.; Van Dijk, M.; Devadas, D. Silicon physical random functions. In Proceedings of the 9th ACM Conference on Computer and Communications Security, Washington, DC, USA, 18–22 November 2002; pp. 148–160. [Google Scholar]

- Rostami, M.; Wendt, J.B.; Potkonjak, M.; Koushanfar, M. Quo vadis, PUF?: Trends and challenges of emerging physical-disorder based security. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 21 April 2014; pp. 1–6. [Google Scholar]

- Huai, Y. Spin-transfer torque MRAM (STT-MRAM): Challenges and prospects. AAPPS Bull. 2008, 18, 33–40. [Google Scholar]

- Wong, H.-S.P.; Raoux, S.; Kim, S.; Liang, J.; Reifenberg, J.P.; Rajendran, B.; Asheghi, M.; Goodson, K.E. Phase Change Memory. Proc. IEEE 2010, 98, 2201–2227. [Google Scholar] [CrossRef]

- Strukov, D.; Snider, G.; Stewart, D. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef] [PubMed]

- Kavehei, O.; Linn, E.; Nielen, L.; Tappertzhofen, S. An associative capacitive network based on nanoscale complementary resistive switches for memory-intensive computing. Nanoscale 2013, 5, 5119–5128. [Google Scholar] [CrossRef] [PubMed]

- Guajardo, J.; Kumar, S.S.; Schrijen, G.J.; Tuyls, P. FPGA Intrinsic PUFs and Their Use for IP Protection. In Cryptographic Hardware and Embedded Systems—CHES 2007; Paillier, P., Verbauwhede, I., Eds.; Springer: Berlin/Heidelberg, Germany, 2007; Volume 4727, pp. 43–80. [Google Scholar]

- Koeberl, P.; Kocabaş, Ü.; Sadeghi, A. Memristor PUFs: A new generation of memory-based Physically Unclonable Functions. In Proceedings of the 2013 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 18–22 March 2013; pp. 428–431. [Google Scholar]

- Rose, G.S.; McDonald, N.; Yan, L.; Wysocki, B. A write-time based memristive PUF for hardware security applications. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, 18–21 November 2013; pp. 830–833. [Google Scholar]

- Chen, A. Analysis of Partial Bias Schemes for the Writing of Crossbar Memory Arrays. IEEE Trans. Electron Devices 2015, 62, 2845–2849. [Google Scholar] [CrossRef]

- Wang, C.; Feng, D.; Liu, J.; Tong, W.; Wu, B.; Zhang, Y. DAWS: Exploiting Crossbar Characteristics for Improving Write Performance of High Density Resistive Memory. In Proceedings of the 2017 IEEE International Conference on Computer Design (ICCD), Boston, MA, USA, 5–8 November 2017; pp. 281–288. [Google Scholar]

- Gao, Y.; Ranasinghe, D.; Al-Sarawi, S.; Kavehei, O.; Abbott, D. mrPUF: A Novel Memristive Device Based Physical Unclonable Function. In Applied Cryptography and Network Security; Malkin, T., Kolesnikov, V., Lewko, A., Polychronakis, M., Eds.; Springer: Cham, Switzerland, 2015; Volume 9092, pp. 595–615. [Google Scholar]

- Woo, J.; Padovani, A.; Moon, K.; Kwak, M.; Larcher, L.; Hwang, H. Linking Conductive Filament Properties and Evolution to Synaptic Behavior of RRAM Devices for Neuromorphic Applications. IEEE Electron Device Lett. 2017, 38, 1220–1223. [Google Scholar] [CrossRef]

- Sun, W.; Choi, S.; Kim, B.; Park, J. Three-Dimensional (3D) Vertical Resistive Random-Access Memory (VRRAM) Synapses for Neural Network Systems. Materials 2019, 12, 3451. [Google Scholar] [CrossRef] [PubMed]

- Kim, B.; Jo, S.; Sun, W.; Shin, H. Analysis of the Memristor-Based Crossbar Synapse for Neuromorphic Systems. J. Nanosci. Nanotechnol. 2019, 19, 6703–6709. [Google Scholar] [CrossRef] [PubMed]

- Jo, S.; Sun, W.; Kim, B.; Kim, S.; Park, J.; Shin, H. Memristor Neural Network Training with Clock Synchronous Neuromorphic System. Micromachines 2019, 10, 384. [Google Scholar] [CrossRef] [PubMed]

- Sun, W.; Choi, S.; Kim, B.; Shin, H. Effect of Initial Synaptic State on Pattern Classification Accuracy of 3D Vertical Resistive Random Access Memory (VRRAM) Synapses. J. Nanosci. Nanotechnol. 2020, 20, 4730–4734. [Google Scholar] [CrossRef] [PubMed]

- Yakopcic, C.; Taha, T.M.; Subramanyam, G.; Pino, R.E. Generalized Memristive Device SPICE Model and its Application in Circuit Design. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2013, 32, 1201–1214. [Google Scholar] [CrossRef]

- Long, B.; Li, Y.; Jha, R. Switching Characteristics of Ru/HfO2/TiO2−x/Ru RRAM Devices for Digital and Analog Nonvolatile Memory Applications. IEEE Electron Device Lett. 2012, 33, 706–708. [Google Scholar] [CrossRef]

- Kuhn, K.J. Reducing Variation in Advanced Logic Technologies: Approaches to Process and Design for Manufacturability of Nanoscale CMOS. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 471–474. [Google Scholar]

- Kim, Y.; Seshadri, V.; Lee, D.; Liu, J.; Mutlu, O. A case for exploiting subarray-level parallelism (SALP) in DRAM. In Proceedings of the 39th Annual International Symposium on Computer Architecture (ISCA), Portland, OR, USA, 9–13 June 2012; pp. 368–379. [Google Scholar]

- Chang, K.K. Improving DRAM performance by parallelizing refreshes with accesses. In Proceedings of the IEEE 20th International Symposium on High Performance Computer Architecture (HPCA), Orlando, FL, USA, 15–19 February 2014; pp. 356–367. [Google Scholar]

- Sahoo, D.P.; Saha, S.; Mukhopadhyay, D.; Chakraborty, R.S.; Kapoor, H. Composite PUF: A new design paradigm for Physically Unclonable Functions on FPGA. In Proceedings of the IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), Arlington, VA, USA, 6–7 May 2014; pp. 50–55. [Google Scholar]

- Shibata, N.; Maejima, H. A 70 nm 16Gb 16-level-cell NAND Flash Memory. In Proceedings of the 2007 IEEE Symposium on VLSI Circuits, Kyoto, Japan, 14–16 June 2007; pp. 190–191. [Google Scholar]

- Hori, Y.; Yoshida, T.; Katashita, T.; Satoh, A. Quantitative and Statistical Performance Evaluation of Arbiter Physical Unclonable Functions on FPGAs. In Proceedings of the 2010 International Conference on Reconfigurable Computing and FPGAs, Quintana Roo, Mexico, 13–15 December 2010; pp. 298–303. [Google Scholar]

- Maiti, A.; Gunreddy, V.; Schaumont, P. A Systematic Method to Evaluate and Compare the Performance of Physical Unclonable Functions. In Embedded Systems Design with FPGAs; Athanas, P., Pnevmatikatos, D., Sklavos, N., Eds.; Springer: New York, NY, USA, 2013; pp. 245–267. [Google Scholar]

- Chen, A. Utilizing the Variability of Resistive Random Access Memory to Implement Reconfigurable Physical Unclonable Functions. IEEE Electron Device Lett. 2015, 36, 138–140. [Google Scholar] [CrossRef]

- Lee, G.S.; Kim, G.; Kwak, K.; Jeong, D.S.; Ju, H. Enhanced Reconfigurable Physical Unclonable Function Based on Stochastic Nature of Multilevel Cell RRAM. IEEE Trans. Electron Devices 2019, 66, 1717–1721. [Google Scholar] [CrossRef]

- Lim, D.; Lee, J.W.; Gassend, B.; Suh, G.E.; van Dijk, M.; Devadas, S. Extracting secret keys from integrated circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2005, 13, 1200–1205. [Google Scholar]

| Symbol | Value | Symbol | Value |

|---|---|---|---|

| 1 (V) | 1 (V) | ||

| 7 | 6 | ||

| b | 2 | 0.3 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, S.; Kim, D.; Choi, Y.; Sun, W.; Shin, H. Multibit-Generating Pulsewidth-Based Memristive-PUF Structure and Circuit Implementation. Electronics 2020, 9, 1446. https://doi.org/10.3390/electronics9091446

Choi S, Kim D, Choi Y, Sun W, Shin H. Multibit-Generating Pulsewidth-Based Memristive-PUF Structure and Circuit Implementation. Electronics. 2020; 9(9):1446. https://doi.org/10.3390/electronics9091446

Chicago/Turabian StyleChoi, Seoyeon, Dayoung Kim, Yunyeong Choi, Wookyung Sun, and Hyungsoon Shin. 2020. "Multibit-Generating Pulsewidth-Based Memristive-PUF Structure and Circuit Implementation" Electronics 9, no. 9: 1446. https://doi.org/10.3390/electronics9091446

APA StyleChoi, S., Kim, D., Choi, Y., Sun, W., & Shin, H. (2020). Multibit-Generating Pulsewidth-Based Memristive-PUF Structure and Circuit Implementation. Electronics, 9(9), 1446. https://doi.org/10.3390/electronics9091446