MFMIS Negative Capacitance FinFET Design for Improving Drive Current

Abstract

:1. Introduction

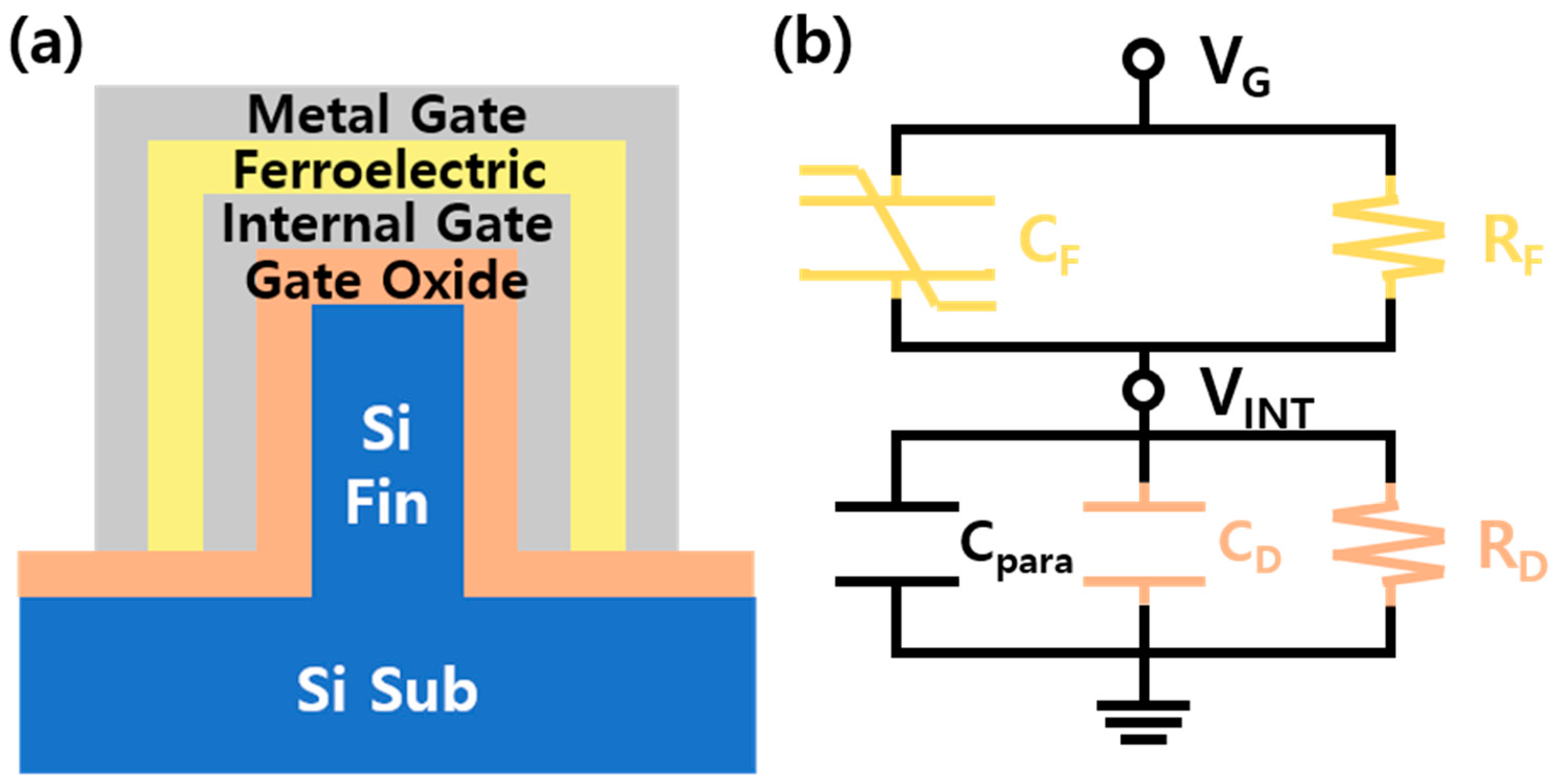

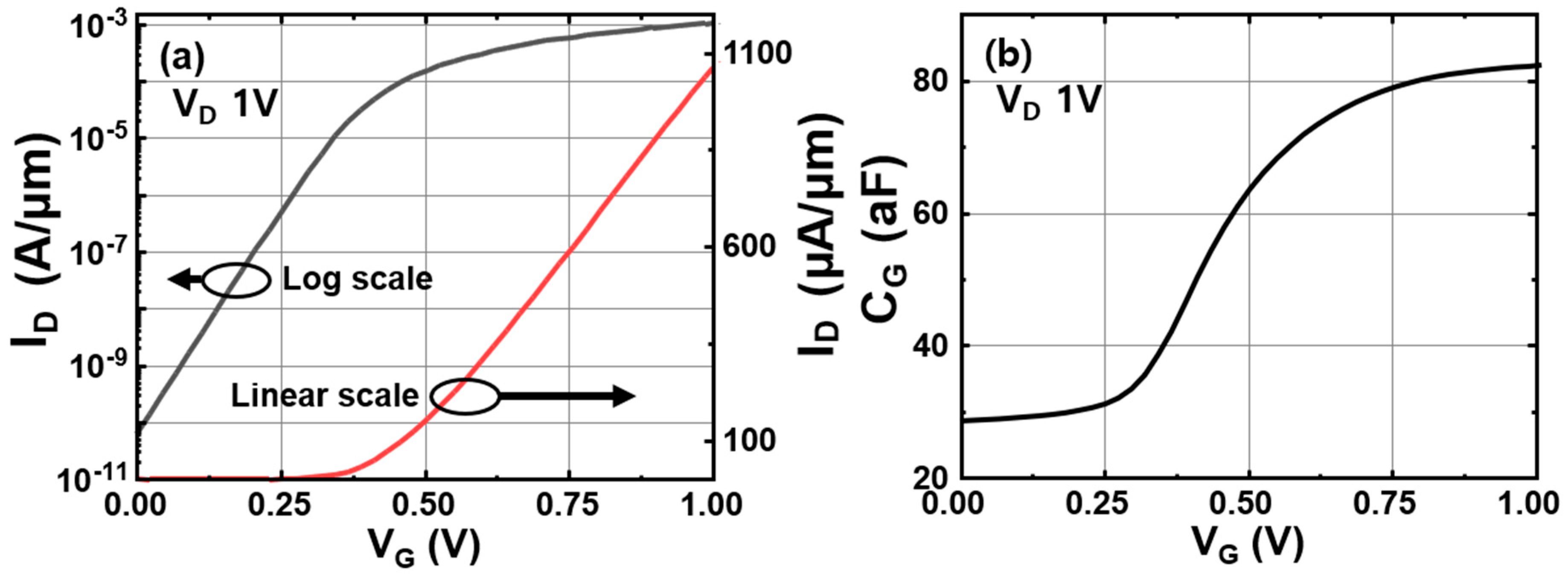

2. Simulation Method for MFMIS NC FinFET

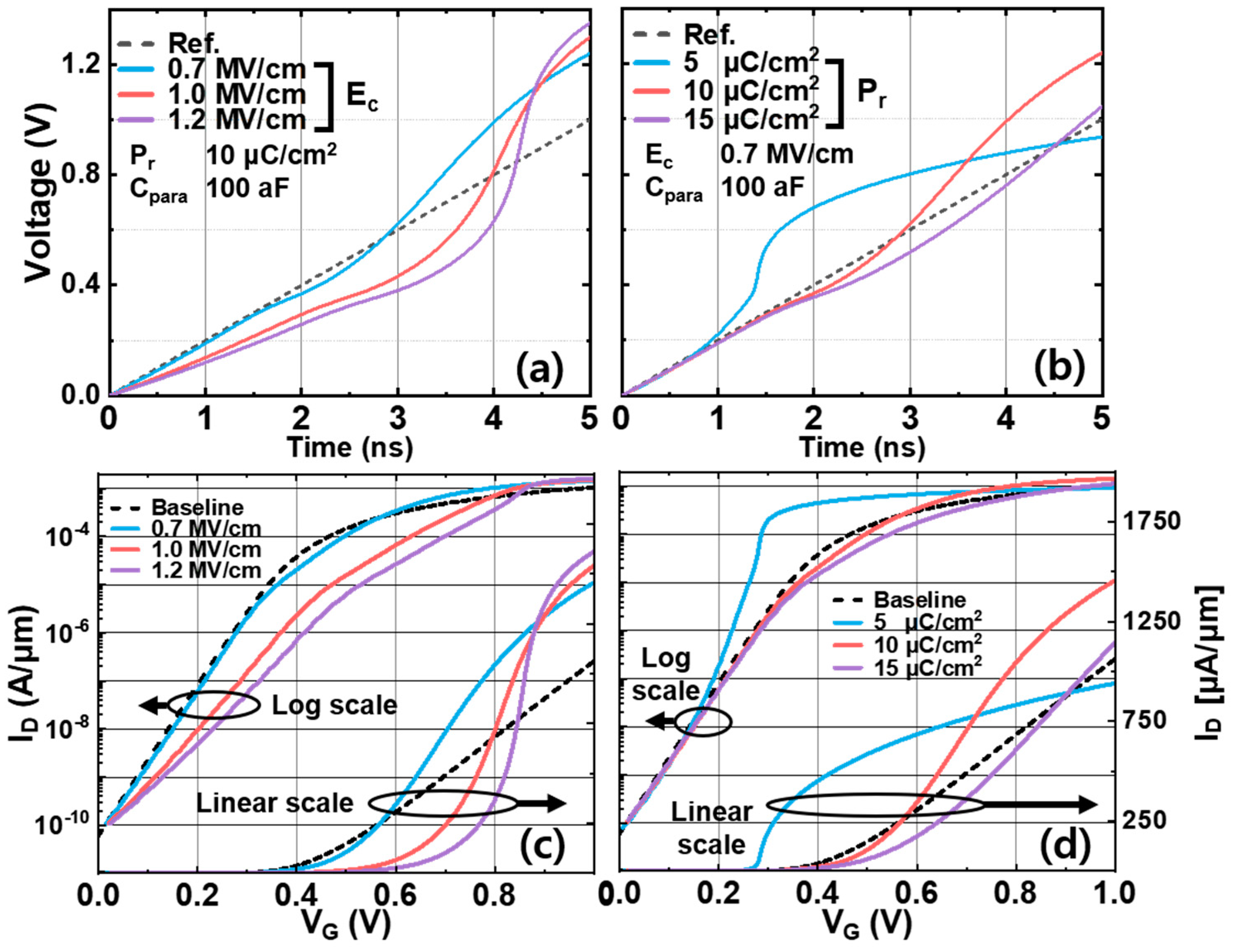

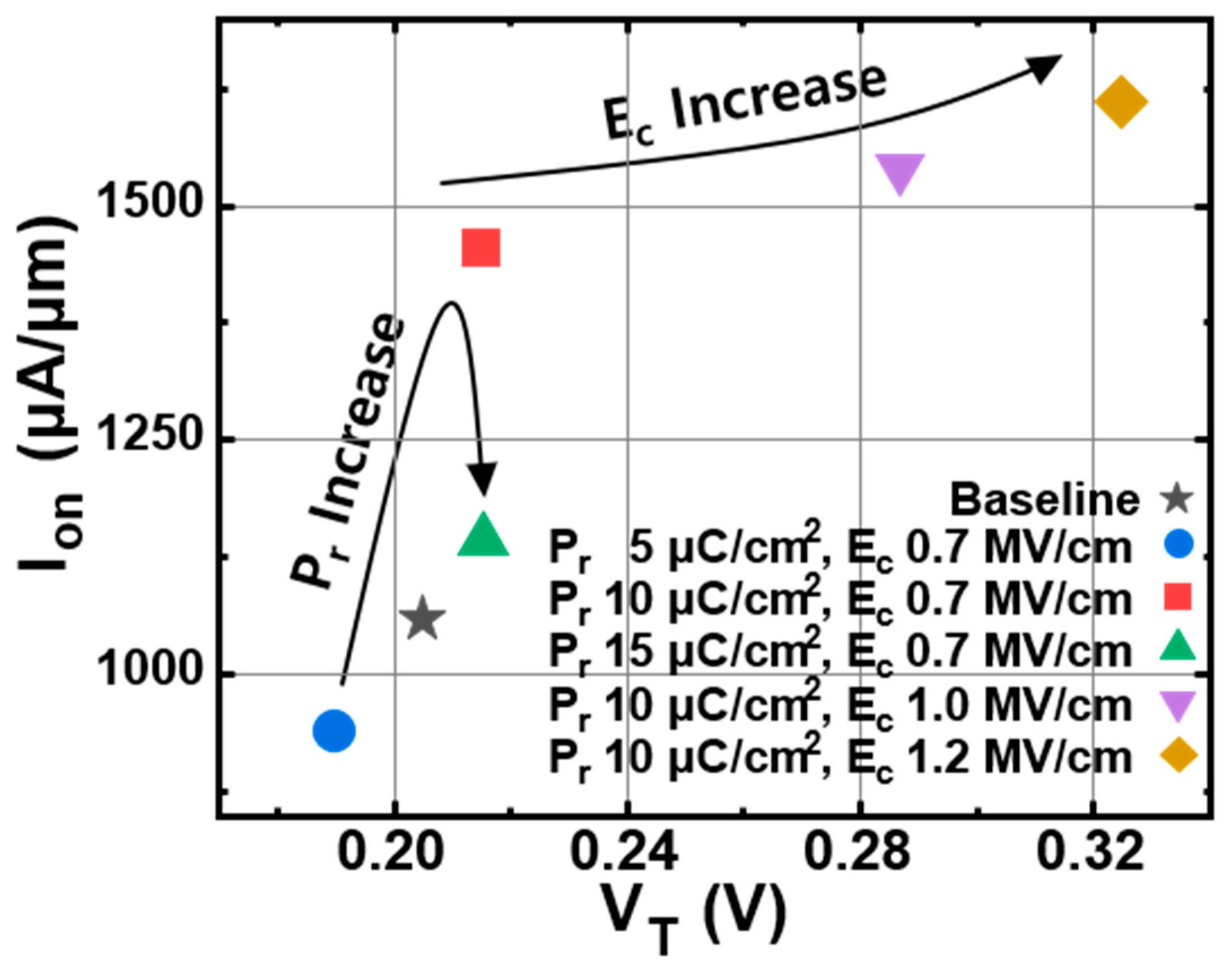

3. Effect of Ec, Pr, and Parasitic Capacitance on MFMIS NC FinFET

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Salahuddin, S.; Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 2008, 8, 405. [Google Scholar] [CrossRef] [PubMed]

- Choi, W.Y.; Park, B.; Lee, J.D.; Liu, T.K. Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743. [Google Scholar] [CrossRef]

- Choe, K.; Shin, C. Adjusting the Operating Voltage of an Nanoelectromechanical Relay Using Negative Capacitance. IEEE Trans. Electron Devices 2017, 64, 5270. [Google Scholar] [CrossRef]

- Nathanael, R.; Pott, V.; Kam, H.; Jeon, J.; Liu, T.K. 4-terminal relay technology for complementary logic. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009. [Google Scholar]

- Jo, J.; Choi, W.Y.; Park, J.-D.; Shim, J.W.; Yu, H.-Y.; Shin, C. Negative capacitance in organic/ferroelectric capacitor to implement steep switching MOS devices. Nano Lett. 2015, 15, 4553. [Google Scholar] [CrossRef] [PubMed]

- Jo, J.; Shin, C. Negative capacitance field effect transistor with hysteresis-free sub-60-mV/decade switching. IEEE Electron Device Lett. 2016, 37, 245. [Google Scholar] [CrossRef]

- Li, K.-S.; Chen, P.-G.; Lai, T.-Y.; Lin, C.-H.; Cheng, C.-C.; Chen, C.-C.; Wei, Y.-J.; Hou, Y.-F.; Liao, M.-H.; Lee, M.-H.; et al. Sub-60mV-swing negative-capacitance FinFET without hysteresis. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [Google Scholar]

- Zhou, H.; Kwon, D.; Sachid, A.B.; Liao, Y.; Chatterjee, K.; Tan, A.J.; Yadav, A.K.; Hu, C.; Salahuddin, S. Negative Capacitance, n-Channel, Si FinFETs: Bi-directional Sub-60 mV/dec, Negative DIBL, Negative Differential Resistance and Improved Short Channel Effect. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; p. 53. [Google Scholar]

- Kwon, D.; Chatterjee, K.; Tan, A.J.; Yadav, A.K.; Zhou, H.; Sachid, A.B.; Dos Reis, R.; Hu, C.; Salahuddin, S. Improved Subthreshold Swing and Short Channel Effect in FDSOI n-Channel Negative Capacitance Field Effect Transistors. IEEE Electron Device Lett. 2018, 39, 300. [Google Scholar] [CrossRef]

- Shin, J.; Shin, C. Experimental observation of zero DIBL in short-channel hysteresis-free ferroelectric-gated FinFET. Solid State. Electron. 2018, 153, 12. [Google Scholar] [CrossRef]

- Kim, T.; Jeon, S. Pulse switching study on the HfZrO ferroelectric films with high pressure annealing. IEEE Trans. Electron Devices 2018, 65, 1771. [Google Scholar] [CrossRef]

- Kobayashi, M.; Hiramoto, T. Device design guideline for steep slope ferroelectric FET using negative capacitance in sub-0.2V operation: Operation speed, material requirement and energy efficiency. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; p. T212. [Google Scholar]

- Khandelwal, S.; Duarte, J.; Khan, A.; Salahuddin, S.; Hu, C. Impact of parasitic capacitance and ferroelectric parameters on negative capacitance FinFET characteristics. IEEE Electron Device Lett. 2017, 38, 142. [Google Scholar] [CrossRef]

- Lin, C.; Khan, A.; Salahuddin, S.; Hu, C. Effects of the Variation of Ferroelectric Properties on Negative Capacitance FET Characteristics. IEEE Trans. Electron Devices 2016, 63, 2197. [Google Scholar] [CrossRef]

- Saha, A.K.; Sharma, P.; Dabo, I.; Datta, S.; Gupta, S.K. Ferroelectric transistor model based on self-consistent solution of 2D Poisson’s, non-equilibrium Green’s function and multi-domain Landau Khalatnikov equations. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017. [Google Scholar]

- Pahwa, G.; Agarwal, A.; Chauhan, Y.S. Numerical Investigation of Short-Channel Effects in Negative Capacitance MFIS and MFMIS Transistors: Above-Threshold Behavior. IEEE Trans. Electron Devices 2019, 66, 1591. [Google Scholar] [CrossRef]

- Khan, A.I.; Radhakrishna, U.; Chatterjee, K.; Salahuddin, S.; Antoniadis, D.A. Negative Capacitance Behavior in a Leaky Ferroelectric. IEEE Trans. Electron Devices 2016, 63, 4416. [Google Scholar] [CrossRef]

- Ando, T.; Sathaye, N.D.; Murali, K.V.R.M.; Cartier, E.A. On the Electron and Hole Tunneling in a HfO2 Gate Stack with Extreme Interfacial-Layer Scaling. IEEE Electron Device Lett. 2011, 32, 865. [Google Scholar] [CrossRef]

- Khan, A.I.; Radhakrishna, U.; Salahuddin, S.; Antoniadis, D. Work Function Engineering for Performance Improvement in Leaky Negative Capacitance FETs. IEEE Electron Device Lett. 2017, 38, 1335. [Google Scholar] [CrossRef]

- The International Roadmap for Devices and Systems (IRDS 2017). Available online: https://irds.ieee.org/roadmap-2017 (accessed on 1 August 2019).

| Device Parameter | Quantity | Device Parameter | Quantity |

|---|---|---|---|

| Gate Length, LG | 18 nm | Oxide Thickness 1, TOX | 3 nm |

| Spacer Thickness, LSP | 7 nm | Channel Doping, NSP | 1015 cm−3 |

| Fin Height, HFin | 50 nm | Source/Drain Doping, NSD | 1020 cm−3 |

| Fin Width, WFin | 7 nm | Ferroelectric Thickness, TF | 3 nm |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Min, J.; Shin, C. MFMIS Negative Capacitance FinFET Design for Improving Drive Current. Electronics 2020, 9, 1423. https://doi.org/10.3390/electronics9091423

Min J, Shin C. MFMIS Negative Capacitance FinFET Design for Improving Drive Current. Electronics. 2020; 9(9):1423. https://doi.org/10.3390/electronics9091423

Chicago/Turabian StyleMin, Jinhong, and Changhwan Shin. 2020. "MFMIS Negative Capacitance FinFET Design for Improving Drive Current" Electronics 9, no. 9: 1423. https://doi.org/10.3390/electronics9091423

APA StyleMin, J., & Shin, C. (2020). MFMIS Negative Capacitance FinFET Design for Improving Drive Current. Electronics, 9(9), 1423. https://doi.org/10.3390/electronics9091423