A 100 Gb/s Quad-Lane SerDes Receiver with a PI-Based Quarter-Rate All-Digital CDR

Abstract

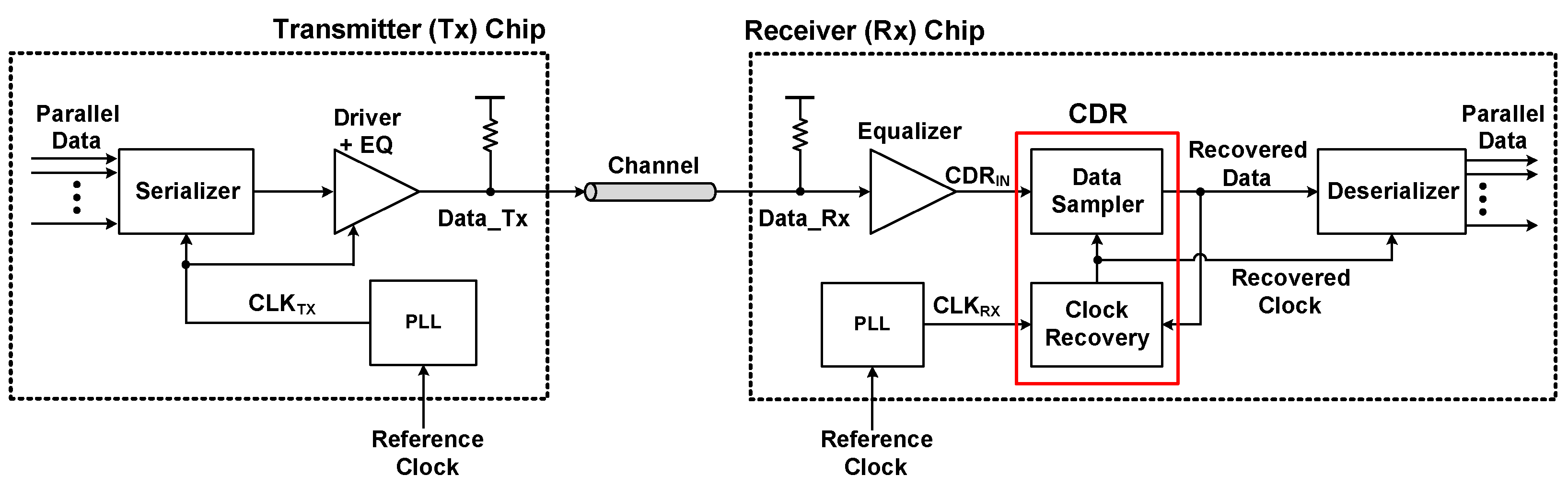

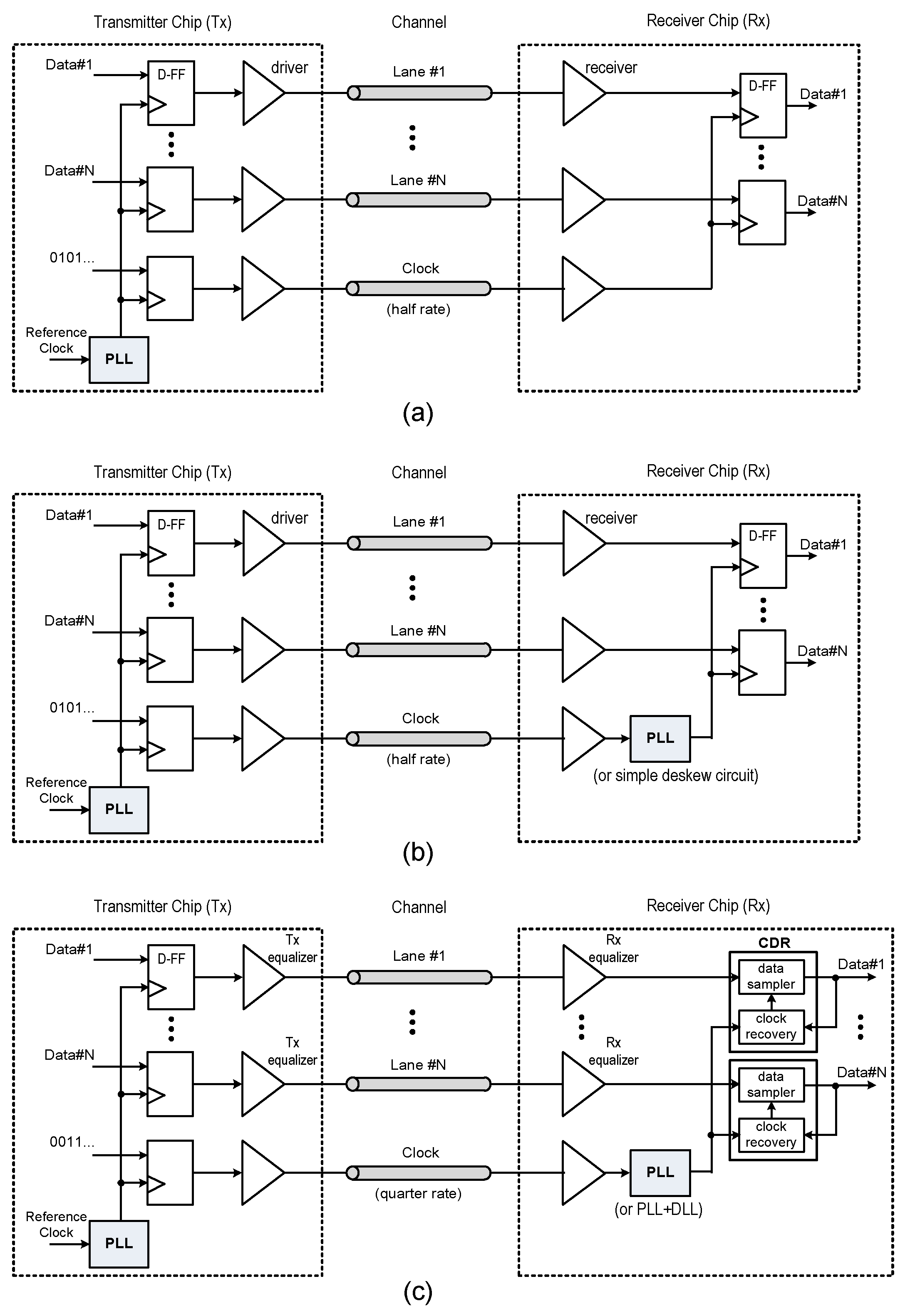

1. Introduction

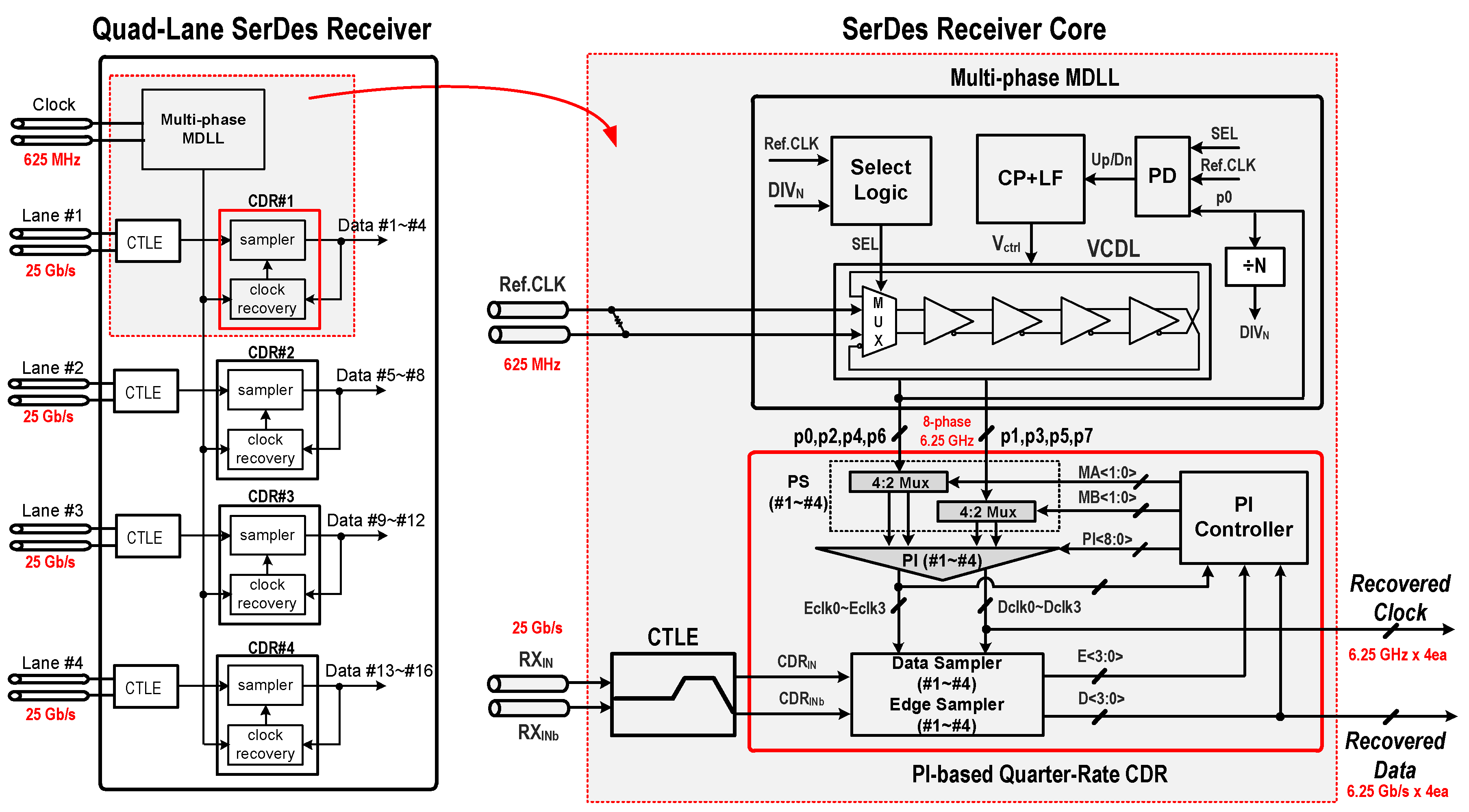

2. Proposed Multi-Lane SerDes Receiver Architecture

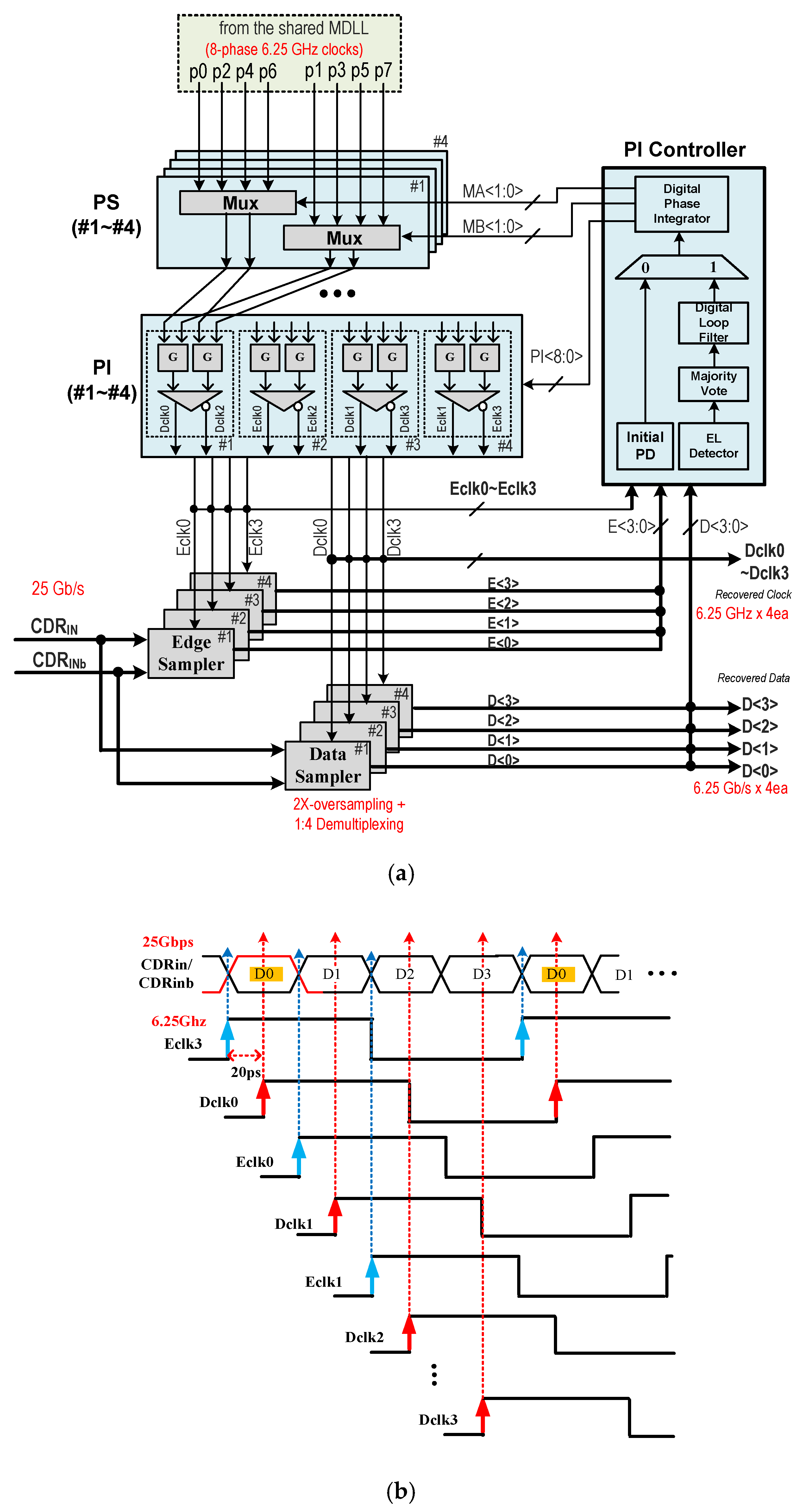

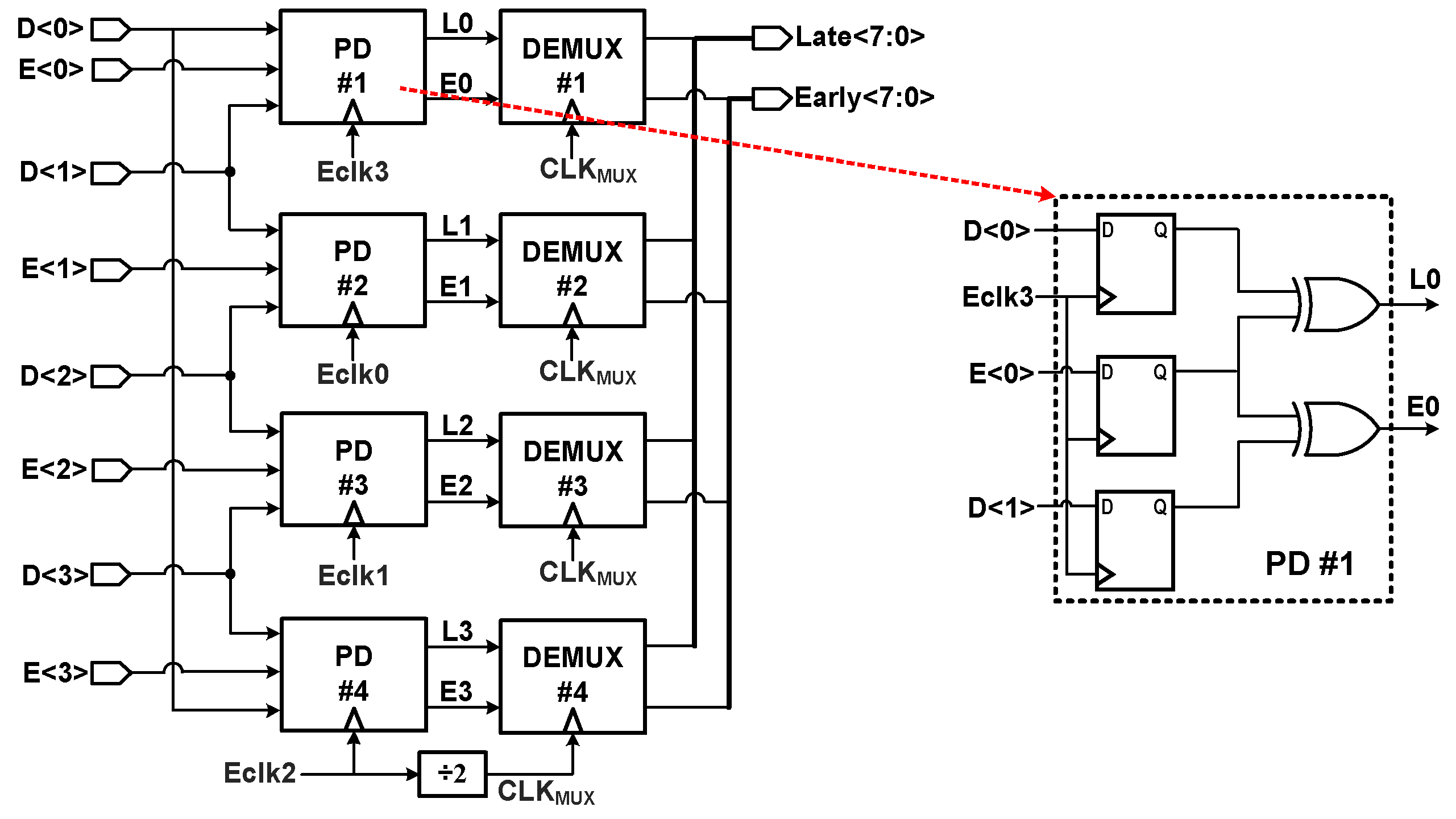

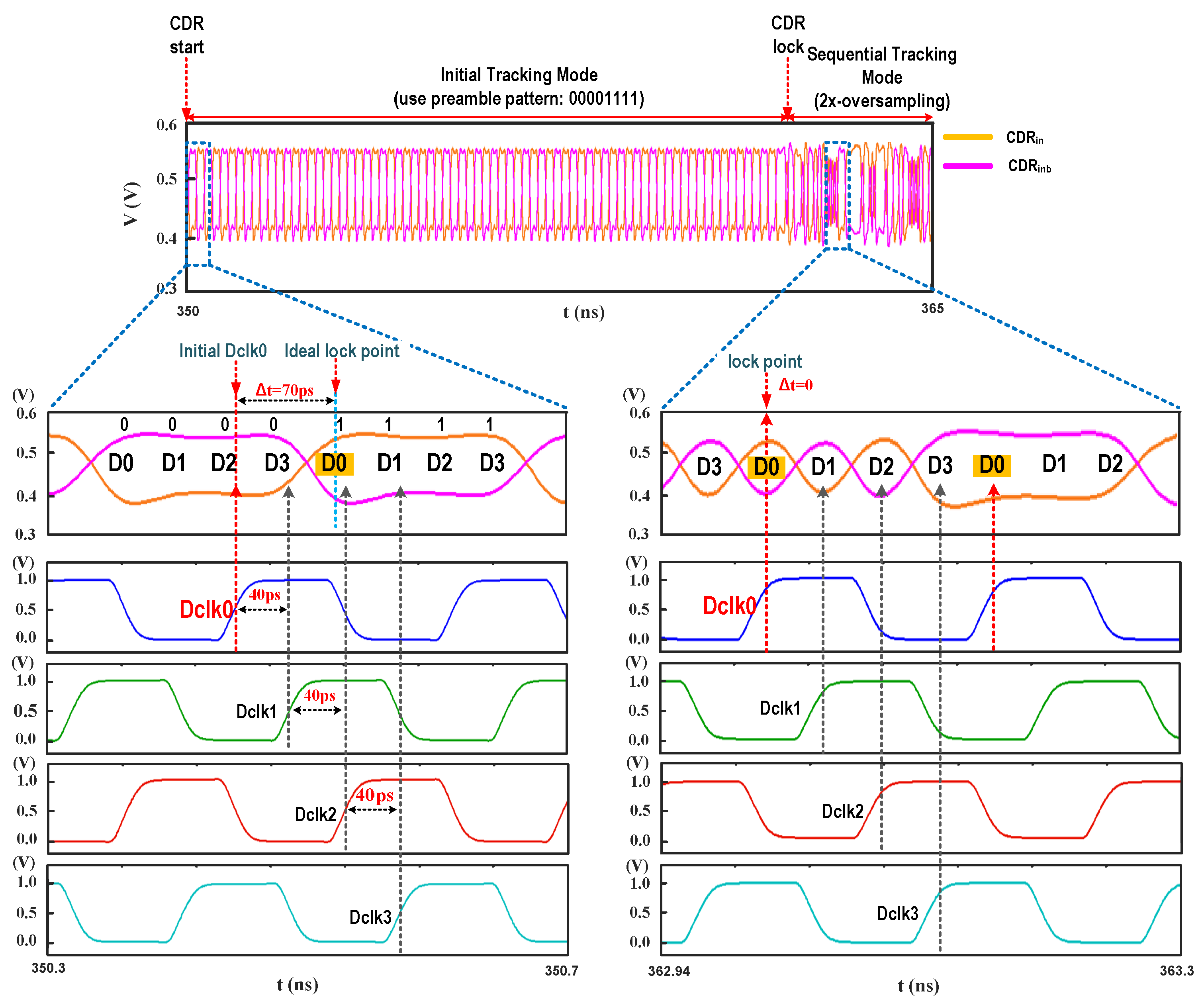

2.1. Proposed All-Digital PI-Based Quarter-Rate CDR Architecture

2.2. Proposed PI Controller

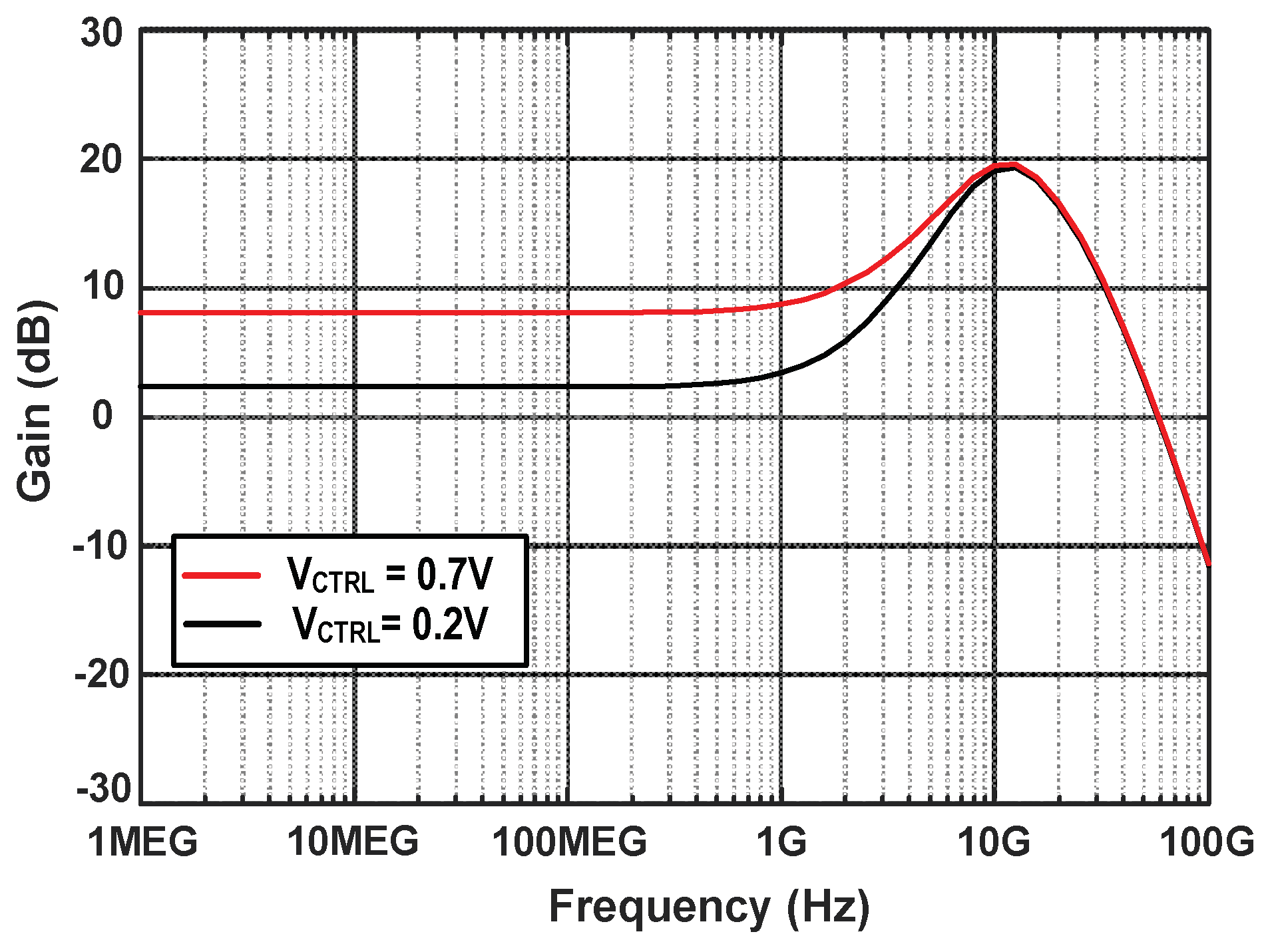

2.3. Proposed CTLE

2.4. Proposed Multi-Phase MDLL

3. Experimental Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Barroso, L.A.; Holzle, U. The case for energy-proportional computing. Computer 2008, 40, 33–37. [Google Scholar] [CrossRef]

- Chen, S.; Li, H.; Chiang, P.Y. A robust energy/area-efficient forwarded-clock receiver with all-digital clock and data recovery in 28-nm CMOS for high-density interconnects. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 578–586. [Google Scholar] [CrossRef]

- Guo, S.; Liu, T.; Zhang, T.; Xi, T.; Wu, G.; Gui, P.; Fan, Y.; Maung, W.; Morgan, M. A low-voltage low-power 25 Gb/s clock and data recovery with equalizer in 65 nm CMOS. In Proceedings of the 2015 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Phoenix, AZ, USA, 17–19 May 2015; pp. 307–310. [Google Scholar]

- Chung, S.H.; Kim, L.S. 1.22 mW/Gb/s 9.6 Gb/s data jitter mixing forwarded-clock receiver robust against power noise with 1.92 ns latency mismatch between data and clock in 65 nm CMOS. In Proceedings of the 2012 Symposium on VLSI Circuit (VLSIC), Honolulu, HI, USA, 13–15 June 2012; pp. 144–145. [Google Scholar]

- Kalantari, N.; Buckwalter, J.F. A multichannel serial link receiver with dual-loop clock-and-data recovery and channel equalization. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 60, 2920–2931. [Google Scholar] [CrossRef]

- Wu, G.; Huang, D.; Li, J.; Gui, P.; Liu, T.; Guo, S.; Wang, R.; Fan, Y.; Chakraborty, S.; Morgan, M. A 1-16 Gb/s all-digital clock and data recovery with a wideband high-linearity phase interpolator. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2511–2520. [Google Scholar] [CrossRef]

- Kwak, Y.H.; Kim, Y.; Hwang, S.; Kim, C. A 20 Gb/s clock and data recovery with a ping-pong delay line for unlimited phase shifting in 65 nm CMOS process. IEEE Trans. Circuits Syst. I: Regul. Pap. 2013, 60, 303–313. [Google Scholar] [CrossRef]

- Bueren, G.V.; Rodoni, L.; Jaeckel, H.; Brun, R.; Holzer, D.; Huber, A.; Schmatz, M. 5.75 to 44Gb/s quarter rate CDR with data rate selection in 90 nm bulk CMOS. In Proceedings of the ESSCIRC 2008—34th European Solid-State Circuit Conference, Edinburgh, UK, 15–19 September 2008; pp. 166–169. [Google Scholar]

- Hsieh, M.T.; Sobelman, G.E. Architectures for multi-gigabit wire-linked clock and data recovery. IEEE Circuits Syst. Mag. 2008, 8, 45–57. [Google Scholar] [CrossRef]

- Choi, W.S.; Anand, T.; Shu, G.; Elshazly, A.; Hanumolu, P.K. A burst-mode digital receiver with programmable input jitter filtering for energy proportional links. IEEE J. Solid-State Circuits 2015, 50, 737–748. [Google Scholar] [CrossRef]

- Su, C.; Chen, L.K.; Cheung, K.W. Theory of burst-mode receiver and its applications in optical multiaccess networks. J. Lightwave Technol. 1997, 15, 590–606. [Google Scholar]

- Verbeke, M.; Rombouts, P.; Ramon, H.; Verbist, J.; Bauwelinck, J.; Yin, X.; Torfs, G. A 25 Gb/s all-digital clock and data recovery circuit for burst-mode applications in PONs. J. Lightwave Technol. 2018, 36, 1503–1509. [Google Scholar] [CrossRef]

- Leibowitz, B.; Palmer, R.; Poulton, J.; Frans, Y.; Li, S.; Wilson, J.; Bucher, M.; Fuller, A.M.; Eyles, J.; Aleksic, M.; et al. A 4.3 GB/s mobile memory interface with power-efficient bandwidth scaling. IEEE J. Solid-State Circuits 2010, 45, 889–898. [Google Scholar] [CrossRef]

- Ziakas, D.; Baum, A.; Maddox, R.; Safranek, R. Intel® QuickPath interconnect architectural features supporting scalable system architectures. In Proceedings of the 18th IEEE Symposium on High Performance Interconnects, Mountain View, CA, USA, 18–20 August 2010; pp. 1–6. [Google Scholar]

- Loke, A.; Doyle, B.; Maheshwari, S.; Fischette, D.; Wang, C.; Wee, T.; Fang, E.S. An 8.0-Gb/s HyperTransport transceiver for 32-nm SOI-CMOS server processors. IEEE J. Solid-State Circuits 2012, 47, 2627–2642. [Google Scholar] [CrossRef]

- Zerbe, J.; Daly, B.; Luo, L.; Stonecypher, W.; Dettloff, W.; Eble, J.C.; Stone, T.; Ren, J.; Leibowitz, B.; Bucher, M.; et al. A 5 Gb/s link with matched source synchronous and common-mode clocking techniques. IEEE J. Solid-State Circuits 2011, 46, 974–985. [Google Scholar] [CrossRef]

- Casper, B.; Jaussi, J.; O’Mahony, F.; Mansuri, M.; Canagasaby, K.; Kennedy, J.; Yeung, E.; Mooney, R. A 20Gb/s forwarded clock transceiver in 90 nm CMOS. In Proceedings of the 2006 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 6–9 February 2006; pp. 263–272. [Google Scholar]

- Jaussi, J.E.; Balamurugan, G.; Johnson, D.R.; Casper, B.; Martin, A.; Kennedy, J.; Shanbhag, N.; Mooney, R. 8-Gb/s source-synchronous I/O link with adaptive receiver equalization, offset cancellation, and clock de-skew. IEEE J. Solid-State Circuits 2005, 40, 80–88. [Google Scholar] [CrossRef]

- O’Mahony, F.; Shekhar, S.; Mansuri, M.; Balamurugan, G.; Jaussi, J.E.; Kennedy, J.; Casper, B.; Allstot, D.J.; Mooney, R. A 27 Gb/s forwarded-clock I/O receiver using an injection-locked LC-DCO in 45nm CMOS. In Proceedings of the 2008 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 3–7 February 2008; pp. 452–627. [Google Scholar]

- Hossain, M.; Carusone, A.C. 7.4 Gb/s 6.8 mW source synchronous receiver in 65 nm CMOS. IEEE J. Solid-State Circuits 2011, 46, 1337–1348. [Google Scholar] [CrossRef]

- Dickson, T.O.; Liu, Y.; Rylov, S.V.; Agrawal, A.; Kim, S.; Hsieh, P.H.; Bulzacchelli, J.F.; Ferriss, M.; Ainspan, H.A.; Rylyakov, A. A 1.4 pJ/bit, power-scalable 16 × 12 Gb/s source-synchronous I/O with DFE receiver in 32 nm SOI CMOS technology. IEEE J. Solid-State Circuits 2015, 50, 1917–1931. [Google Scholar] [CrossRef]

- Reutemann, R.; Ruegg, M.; Keyser, F.; Bergkvist, J.; Dreps, D.; Toifl, T.; Schmatz, M. A 4.5 mW/Gb/s 6.4 Gb/s 22+1-lane source synchronous receiver core with optional cleanup PLL in 65 nm CMOS. IEEE J. Solid-State Circuits 2010, 45, 2850–2860. [Google Scholar] [CrossRef]

- Lv, F.; Zheng, X.; Zhao, F.; Wang, J.; Yue, S.; Wang, Z.; Cao, W.; He, Y.; Zhang, C.; Jiang, H.; et al. A power scalable 2–10 Gb/s PI-based clock data recovery for multilane applications. Microelectron. J. 2018, 82, 36–45. [Google Scholar] [CrossRef]

- Hwang, H.; Kim, J. A low-power 20 Gbps multi-phase MDLL-based digital CDR with receiver equalization. In Proceedings of the 2019 International SoC Design Conference (ISOCC), Jeju, Korea, 6–9 October 2019; pp. 42–43. [Google Scholar]

- Aprile, C.; Cevrero, A.; Francese, P.A.; Menolfi, C.; Braendli, M.; Kossel, M.; Morf, T.; Kull, L.; Oezkaya, I.; Leblebici, Y.; et al. An eight-lane 7-Gb/s/pin source synchronous single-ended RX with equalization and far-end crosstalk cancellation for backplane channels. IEEE J. Solid-State Circuits 2018, 53, 861–872. [Google Scholar] [CrossRef]

- Hossain, M.; Chen, E.H.; Navid, R.; Leibowitz, B.; Chou, A.; Li, S.; Park, M.J.; Ren, J.; Daly, B.; Su, B.; et al. A 4 × 40 Gb/s quad-lane CDR with shared frequency tracking and data dependent jitter filtering. In Proceedings of the 2014 Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014; pp. 1–2. [Google Scholar]

- Singh, U.; Garg, A.; Raghavan, B.; Huang, N.; Zhang, H.; Huang, Z.; Momtaz, A.; Cao, J. A 780 mW 4 × 28 Gb/s transceiver for 100 GbE gearbox PHY in 40 nm CMOS. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014. [Google Scholar]

- Kocaman, N.; Ali, T.; Rao, L.P.; Singh, U.; Abdul-Latif, M.; Liu, Y.; Hafez, A.A.; Park, H.; Vasani, A.; Huang, Z.; et al. A 3.8 mW/Gbps quad-channel 8.5–13 Gbps serial link with a 5 tap DFE and a 4 tap transmit FFE in 28 nm CMOS. IEEE J. Solid-State Circuits 2016, 51, 881–892. [Google Scholar]

- Rodoni, L.; Buren, G.V.; Huber, A.; Schmatz, M.; Jackel, H. A 5.75 to 44 Gb/s quarter rate CDR with data rate selection in 90 nm bulk CMOS. IEEE J. Solid-State Circuits 2009, 44, 1927–1941. [Google Scholar] [CrossRef]

- Navid, R.; Chen, E.H.; Hossain, M.; Leibowitz, B.; Ren, J.; Chou, C.A.; Daly, B.; Aleksic, M.; Su, B.; Li, S.; et al. A 40 Gb/s serial link transceiver in 28 nm CMOS technology. IEEE J. Solid-State Circuits 2015, 50, 814–827. [Google Scholar] [CrossRef]

- Ng, H.T.; Farjad-Rad, R.; Lee, M.E.; Dally, W.J.; Greer, T.; Poulton, J.; Edmondson, J.H.; Rathi, R.; Senthinathan, R. A second-order semidigital clock recovered circuit based on injection locking. IEEE J. Solid-State Circuits 2003, 38, 2101–2110. [Google Scholar]

- Zheng, X.; Zhang, C.; Lv, F.; Zhao, F.; Yuan, S.; Yue, S.; Wang, Z.; Wang, Z.; Li, F.; Wang, Z.; et al. A 40-Gb/s quarter-rate serdes transmitter and receiver chipset in 65-nm CMOS. IEEE J. Solid-State Circuits 2017, 52, 2963–2978. [Google Scholar] [CrossRef]

- Kim, J.; Shin, H. A low-power 3.52 Gbps SerDes with a MDLL frequency multiplier for high-speed on-chip networks. J. Semicond. Technol. Sci. 2018, 18, 658–666. [Google Scholar] [CrossRef]

- Alexander, J. Clock recovery from random binary signals. IET Electron. Lett. 1975, 11, 541–542. [Google Scholar] [CrossRef]

- Kaviani, K.; Amirkhany, A.; Huang, C.; Huang, C.; Le, P.; Beyene, W.; Madden, C.; Saito, K.; Sano, K.; Murugan, V.I.; et al. A 0.4-mW/Gb/s near-ground receiver front-end with replica transconductance termination calibration for a 16-Gb/s source-series terminated transceiver. IEEE J. Solid-State Circuits 2013, 48, 636–648. [Google Scholar] [CrossRef]

- Ku, J.; Bae, B.; Kim, J. A 13-Gbps low-swing low-power near-ground signaling transceiver. J. Inst. Electron. Inf. Eng. 2014, 51, 49–58. [Google Scholar]

- Lee, J. A 20 Gb/s adaptive equalizer in 0.13 μm CMOS technology. IEEE J. Solid-State Circuits 2006, 41, 2058–2066. [Google Scholar] [CrossRef]

- Han, S.; Lim, J.; Kim, J. An area-efficient multi-phase fractional-ratio clock frequency multiplier. J. Semicond. Technol. Sci. 2016, 16, 143–146. [Google Scholar] [CrossRef][Green Version]

- Kim, J.; Han, S. A fast-locking all-digital multiplying DLL for fractional-ratio dynamic frequency scaling. IEEE Trans. Circuits Syst. II 2018, 65, 276–280. [Google Scholar] [CrossRef]

| Reference | [5] | [28] | [29] | [32] | This Work |

|---|---|---|---|---|---|

| Process and supply | 130 nm/1.2 V | 28 m/1.0 V | 90 nm/1.0 V | 65 nm/1.2 V | 40 nm/1.0 V |

| Data rate (Gb/s) | 7 | 13 | 44 | 40 | 25 |

| CDR architecture | PI-based | PI-based | PI-based | PI-based | PI-based |

| Sampling rate | Baud-rate | Half-rate | Quarter-rate | Quarter-rate | Quarter-rate |

| DEMUXing ratio | 1:1 | 1:20 | 1:16 | 1:4 | 1:4 |

| Multi-phase generation | PLL (LC-VCO) | PLL (LC-VCO) | 8-phase DLL | 1/2 Divider | 8-phase MDLL |

| External reference clock frequency | 150 MHz | N/A | 10 GHz | 20 GHz | 625 MHz |

| CDR power (mW) | 13.7 | - | - | 159 | 34.2 |

| Multi-phase gen. power (mW) | 39.6 | 27 | - | 30 | 24.2 |

| Total power (mW) | 53.3 | 59 | 230 | 189 | 58.4 |

| Energy efficiency (pJ/bit) | 7.6 | 4.53 | 5.74 | 4.7 | 2.34 |

| Lock time | - | - | - | - | 12ns |

| Reference | [5] | [22] | [28] | This work |

|---|---|---|---|---|

| Process and supply | 130 nm/1.2 V | 65 nm/1.0 V | 28 m/1.0 V | 40 nm/1.0 V |

| CDR architecture | PI-based | PI-based | PI-based | PI-based |

| Equalization | CTLE | CTLE | CTLE + DFE | CTLE |

| Aggregate data rate (Gb/s) | 28 | 140.8 | 52 | 100 |

| Number of data channels | 4 | 22 | 4 | 4 |

| Data rate/channel (Gb/s) | 7 | 6.4 | 13 | 25 |

| Total Power (mW) | 271.5 | 635 | 155 | 241.8 |

| Energy Efficiency (pJ/bit) | 9.7 | 4.5 | 2.98 | 2.418 |

| Chip Area (mm2) | 2.41 | 2.96 | 0.226 1 | 0.351 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hwang, H.; Kim, J. A 100 Gb/s Quad-Lane SerDes Receiver with a PI-Based Quarter-Rate All-Digital CDR. Electronics 2020, 9, 1113. https://doi.org/10.3390/electronics9071113

Hwang H, Kim J. A 100 Gb/s Quad-Lane SerDes Receiver with a PI-Based Quarter-Rate All-Digital CDR. Electronics. 2020; 9(7):1113. https://doi.org/10.3390/electronics9071113

Chicago/Turabian StyleHwang, Heejae, and Jongsun Kim. 2020. "A 100 Gb/s Quad-Lane SerDes Receiver with a PI-Based Quarter-Rate All-Digital CDR" Electronics 9, no. 7: 1113. https://doi.org/10.3390/electronics9071113

APA StyleHwang, H., & Kim, J. (2020). A 100 Gb/s Quad-Lane SerDes Receiver with a PI-Based Quarter-Rate All-Digital CDR. Electronics, 9(7), 1113. https://doi.org/10.3390/electronics9071113