A Novel Power Decoupling Control Method to Eliminate the Double Line Frequency Ripple of Two Stage Single-Phase DC-AC Power Conversion Systems

Abstract

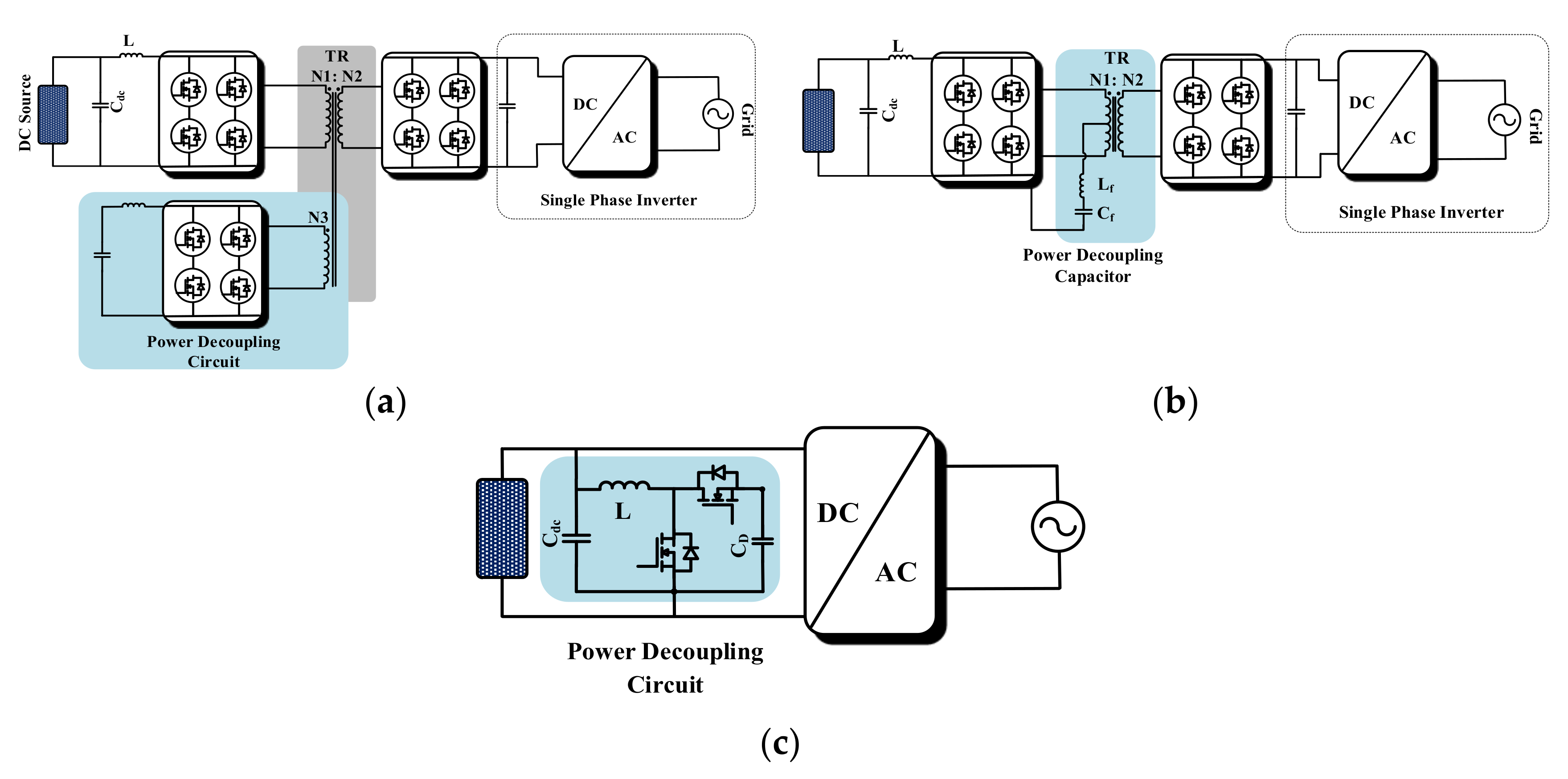

1. Introduction

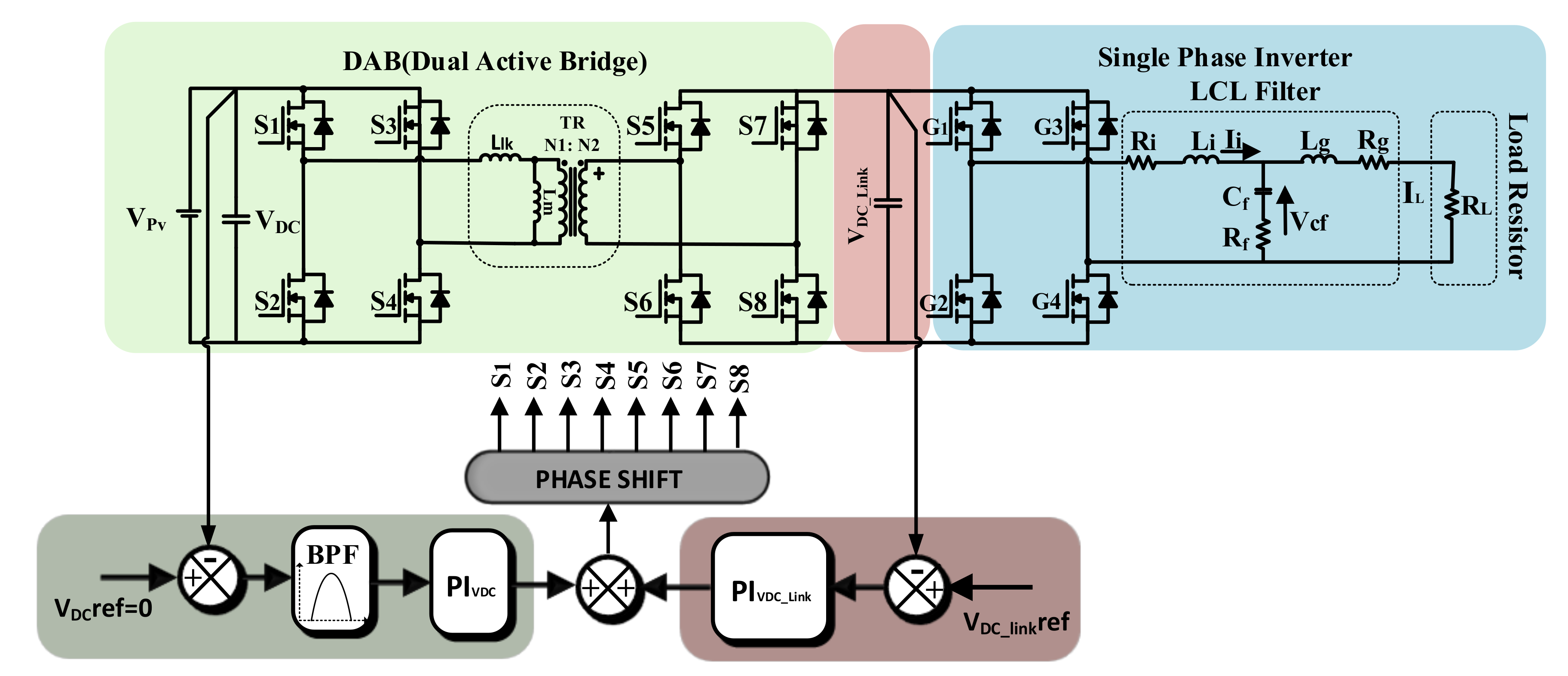

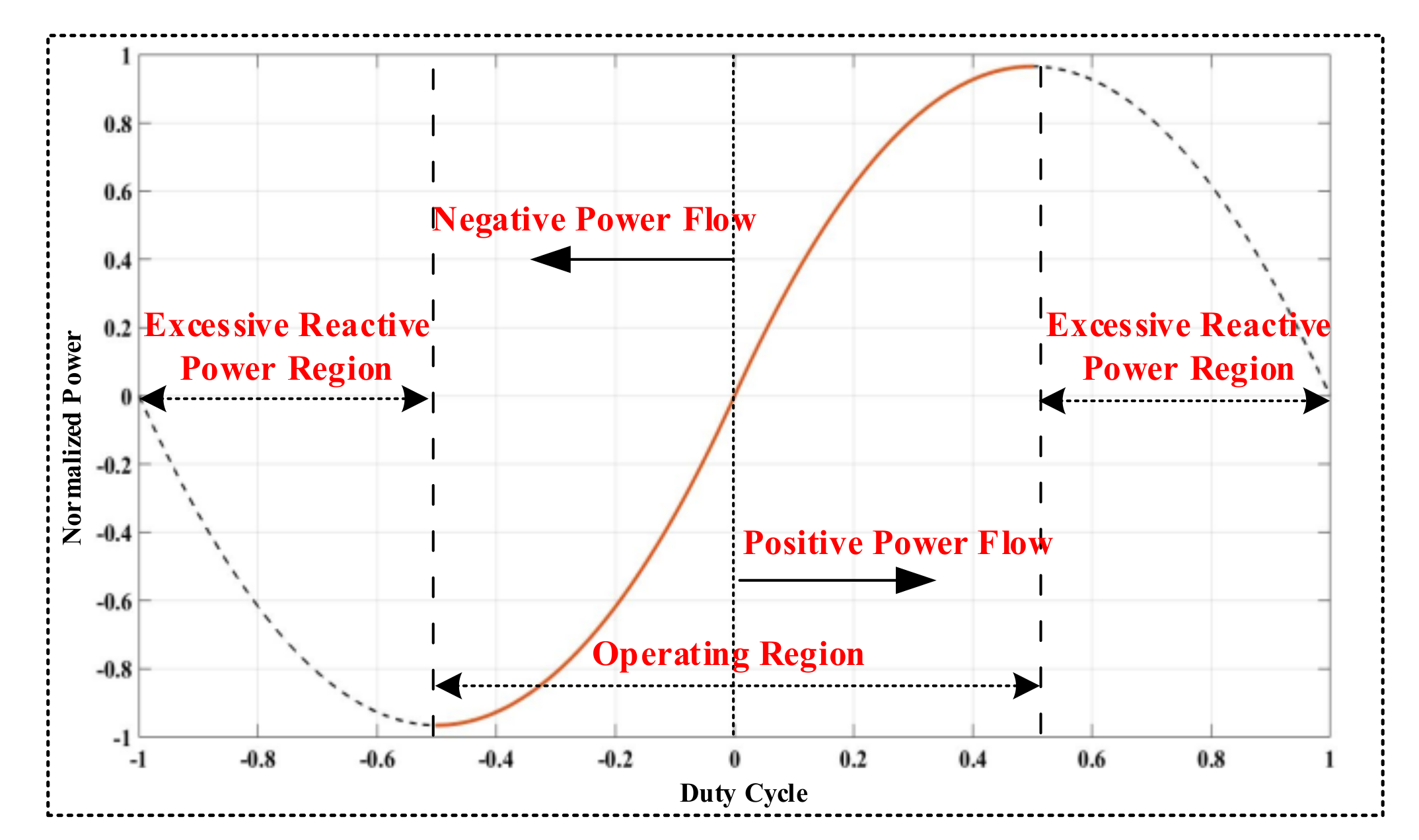

2. Double Line Frequency Ripple

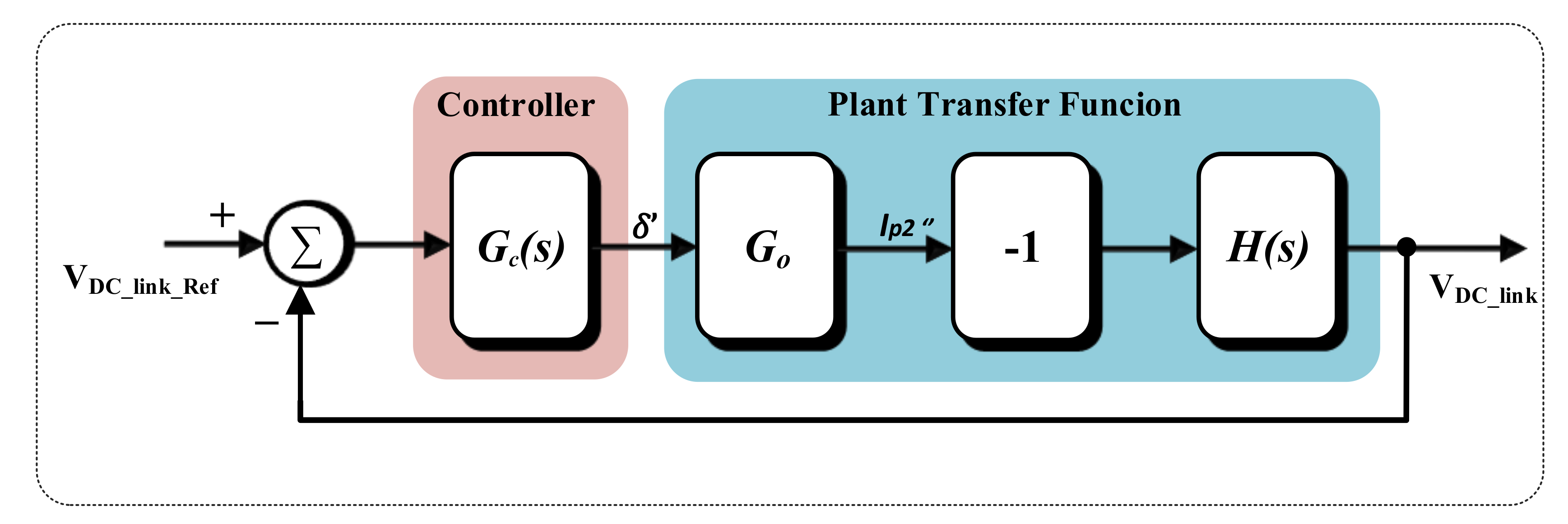

3. Simplified Modeling of DAB for Double Line Frequency Ripple Elimination

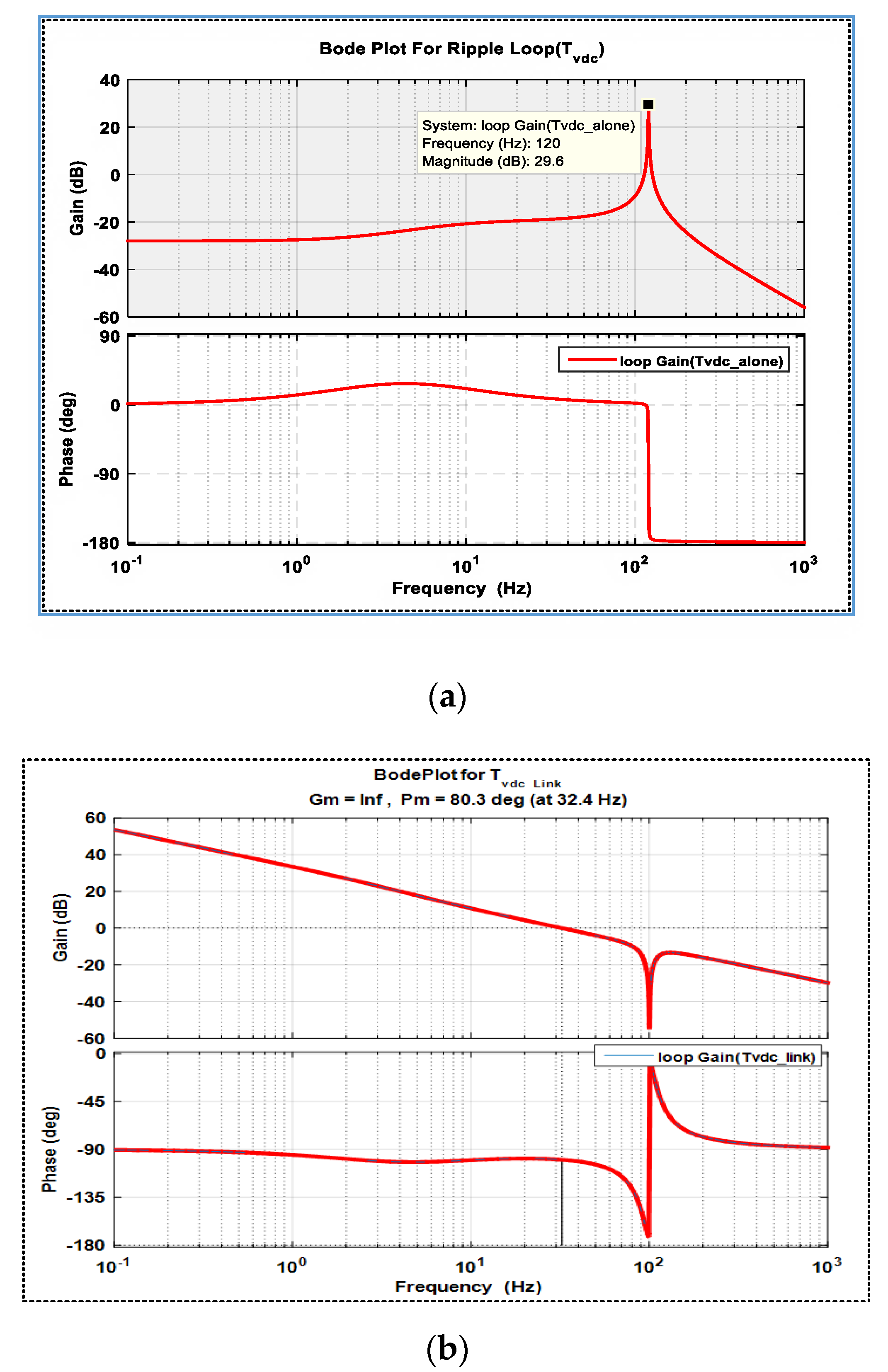

4. Design of the Controllers for DAB Converters Voltage Control and the Elimination of Double Line Frequency Ripple

5. Experimental and Simulation Results

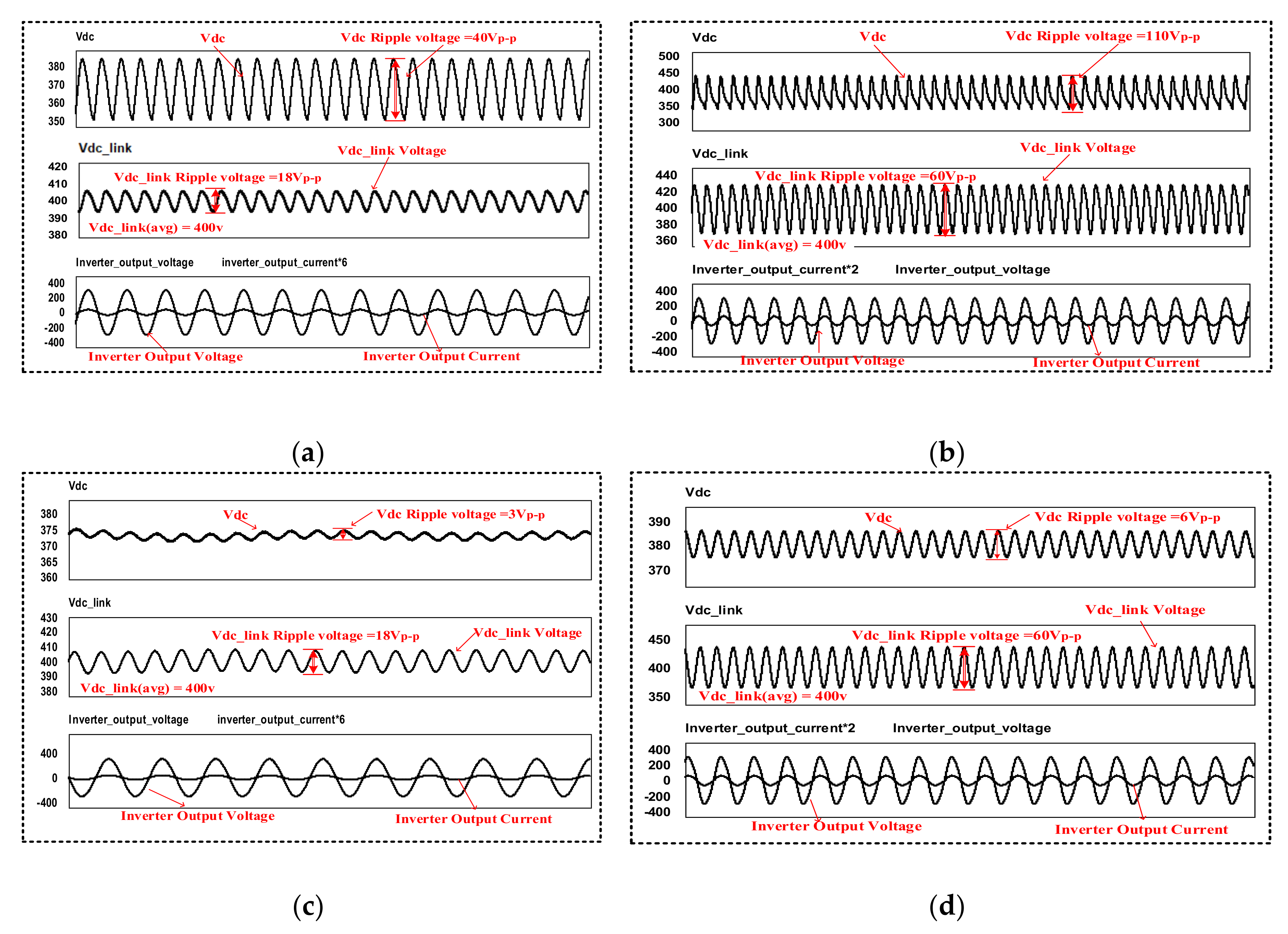

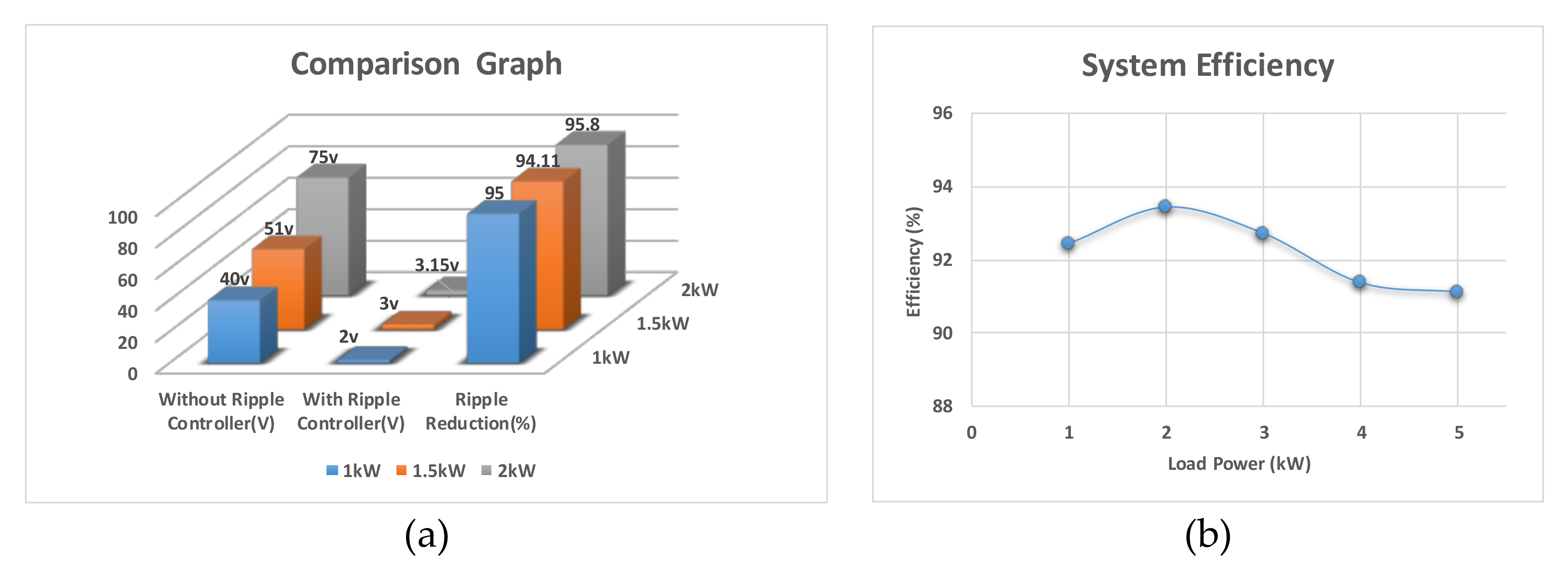

5.1. Simulation Results

5.2. Experimantal Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kjaer, S.; Pedersen, J.; Blaabjerg, F. A Review of Single-Phase Grid-Connected Inverters for Photovoltaic Modules. IEEE Trans. Ind. Appl. 2005, 41, 1292–1306. [Google Scholar] [CrossRef]

- Riedel, J.; Holmes, D.G.; McGrath, B.; Teixeira, C.A. Active Suppression of Selected DC Bus Harmonics for Dual Active Bridge DC-DC Converters. IEEE Trans. Power Electron. 2016, 32, 1. [Google Scholar] [CrossRef]

- Akagi, H.; Yamagishi, T.; Tan, N.M.L.; Kinouchi, S.-I.; Miyazaki, Y.; Koyama, M. Power-Loss Breakdown of a 750-V 100-kW 20-kHz Bidirectional Isolated DC–DC Converter Using SiC-MOSFET/SBD Dual Modules. IEEE Trans. Ind. Appl. 2014, 51, 420–428. [Google Scholar] [CrossRef]

- Segaran, D.; Holmes, D.G.; McGrath, B. High-performance bi-directional AC-DC converters for PHEV with minimised DC bus capacitance. In Proceedings of the IECON 2011 37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 7–10 November 2011; pp. 3620–3625. [Google Scholar]

- Antivachis, M.; Anderson, J.A.; Bortis, D.; Kolar, J.W. Analysis of a synergetically controlled two-stage three-phase DC/AC buck-boost converter. CPSS TPEA 2020, 5, 34–53. [Google Scholar] [CrossRef]

- Hu, H.; Harb, S.; Kutkut, N.; Batarseh, I.; Shen, Z.J. A Review of Power Decoupling Techniques for Microinverters With Three Different Decoupling Capacitor Locations in PV Systems. IEEE Trans. Power Electron. 2012, 28, 2711–2726. [Google Scholar] [CrossRef]

- Dod, S. Reliability Prediction of Electronic Equipment; MIL-HDBK-217D; Rome Air Development Center Griffss AFB: New York, NY, USA, 1982. [Google Scholar]

- Sun, Y.; Liu, Y.; Su, M.; Xiong, W.; Yang, J. Review of activepower decoupling topologies in single-phase systems. IEEE Trans. Power Electron. 2016, 31, 4778–4794. [Google Scholar]

- Ma, X.; Wang, B.; Zhao, F.; Qu, G.; Gao, D.; Zhou, Z. A high power low ripple high dynamic performance DC power supply based on thyristor converter and active filter. In Proceedings of the IEEE 2002 28th Annual Conference of the Industrial Electronics Society, IECON 02, Sevilla, Spain, 5–8 November 2003; Volume 2, pp. 1238–1242. [Google Scholar]

- Irfan, M.S.; Ahmed, A.; Park, J.-H.; Seo, C. Current-Sensorless Power-Decoupling Phase-Shift Dual-Half-Bridge Converter for DC–AC Power Conversion Systems Without Electrolytic Capacitor. IEEE Trans. Power Electron. 2017, 32, 3610–3622. [Google Scholar] [CrossRef]

- Liu, C.; Johnson, A.; Lai, J.-S. A novel three-phase high-power soft switched DC/DC converter for low voltage fuel cell applications. IEEE Trans. Ind. Appl. 2004, 3, 1365–1371. [Google Scholar] [CrossRef]

- Itoh, J.; Hayashi, F. Ripple Current Reduction of a Fuel Cell for a Single-Phase Isolated Converter Using a DC Active Filter with a Center Tap. IEEE Trans. Power Electron. 2010, 25, 550–556. [Google Scholar] [CrossRef]

- Liu, C.; Lai, J.-S. Low Frequency Current Ripple Reduction Technique with Active Control in a Fuel Cell Power System with Inverter Load. IEEE Trans. Power Electron. 2006, 22, 1429–1436. [Google Scholar] [CrossRef]

- Qian, Z.; Abdel-Rahman, O.; Hu, H.; Batarseh, I. An integrated three-port inverter for stand-alone PV applications. IEEE Energy Convers. Congr. Expo. 2010, 1471–1478. [Google Scholar] [CrossRef]

- Liu, D.; Li, H. A ZVS Bi-Directional DC–DC Converter for Multiple Energy Storage Elements. IEEE Trans. Power Electron. 2006, 21, 1513–1517. [Google Scholar] [CrossRef]

- Li, W.; Xiao, J.; Zhao, Y.; He, X. PWM Plus Phase Angle Shift (PPAS) Control Scheme for Combined Multiport DC/DC Converters. IEEE Trans. Power Electron. 2011, 27, 1479–1489. [Google Scholar] [CrossRef]

- Möhr, M.; Fuchs, F.-W. Current-Fed Full Bridge Converters for Fuel Cell Systems Connected to the Three Phase Grid. In Proceedings of the 2006 1st International Conference on Nano-Networks and Workshops, Paris, France, 6–10 November 2006; pp. 4313–4318. [Google Scholar]

- Cai, W.; Liu, B.; Duan, S.; Jiang, L. An Active Low-Frequency Ripple Control Method Based on the Virtual Capacitor Concept for BIPV Systems. IEEE Trans. Power Electron. 2013, 29, 1733–1745. [Google Scholar] [CrossRef]

- Hu, H.; Harb, S.; Fang, X.; Zhang, D.; Zhang, Q.; Shen, Z.J.; Batarseh, I. A Three-port Flyback for PV Microinverter Applications with Power Pulsation Decoupling Capability. IEEE Trans. Power Electron. 2012, 27, 3953–3964. [Google Scholar] [CrossRef]

- Hu, H.; Harb, S.; Kutkut, N.; Batarseh, I.; Shen, Z.J. Power decoupling techniques for micro-inverters in PV systems-a review. IEEE Energy Convers. Congr. Expo. 2010, 3235–3240. [Google Scholar] [CrossRef]

- Li, Q.; Wolfs, P.J. A Review of the Single Phase Photovoltaic Module Integrated Converter Topologies With Three Different DC Link Configurations. IEEE Trans. Power Electron. 2008, 23, 1320–1333. [Google Scholar] [CrossRef]

- Rodriguez, A.; Vazquez, A.; Lamar, D.G.; Hernando, M.M.; Sebastian, J. Different Purpose Design Strategies and Techniques to Improve the Performance of a Dual Active Bridge With Phase-Shift Control. IEEE Trans. Power Electron. 2015, 30, 790–804. [Google Scholar] [CrossRef]

- Demetriades, G.D. On Small-Signal Analysis and Control of the Single- and Dual-Active Bridge Topologies. Ph.D. Thesis, The Royal Institute of Technology, Stockholm, Sweden, 2005. [Google Scholar]

- Choi, W.; Howze, J.; Enjeti, P. Development of an equivalent circuit model of a fuel cell to evaluate the effects of inverter ripple current. J. Power Sources 2006, 158, 1324–1332. [Google Scholar] [CrossRef]

- Kim, W.; Duong, V.-H.; Nguyen, T.-T.; Choi, W. Analysis of the effects of inverter ripple current on a photovoltaic power system by using an AC impedance model of the solar cell. Renew. Energy 2013, 59, 150–157. [Google Scholar] [CrossRef]

- He, D.; Cai, W.; Yi, F. A power decoupling method with small capacitance requirement based on single-phase quasi-Z-source inverter for DC microgrid applications. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 2599–2606. [Google Scholar]

- Xu, S.; Shao, R.; Chang, L.; Mao, M. Single-Phase Differential Buck–Boost Inverter With Pulse Energy Modulation and Power Decoupling Control. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 2060–2072. [Google Scholar] [CrossRef]

- Liu, X.; Li, H.; Wang, Z. A Fuel Cell Power Conditioning System With Low-Frequency Ripple-Free Input Current Using a Control-Oriented Power Pulsation Decoupling Strategy. IEEE Trans. Power Electron. 2013, 29, 159–169. [Google Scholar] [CrossRef]

- Liu, Y.; Sun, Y.; Su, M. A Control Method for Bridgeless Cuk/Sepic PFC Rectifier to Achieve Power Decoupling. IEEE Trans. Ind. Electron. 2017, 64, 7272–7276. [Google Scholar] [CrossRef]

- Lyu, X.; Ren, N.; Li, Y.; Cao, N. A SiC-Based High Power Density Single-Phase Inverter With In-Series and In-Parallel Power Decoupling Method. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 893–901. [Google Scholar] [CrossRef]

- Wang, H.; Chung, H.S.-H.; Liu, W. Use of a Series Voltage Compensator for Reduction of the DC-Link Capacitance in a Capacitor-Supported System. IEEE Trans. Power Electron. 2013, 29, 1163–1175. [Google Scholar] [CrossRef]

- Tang, Y.; Blaabjerg, F.; Loh, P.C.; Jin, C.; Wang, P. Decoupling of Fluctuating Power in Single-Phase Systems Through a Symmetrical Half-Bridge Circuit. IEEE Trans. Power Electron. 2015, 30, 1855–1865. [Google Scholar] [CrossRef]

- Xia, Y.; Roy, J.; Ayyanar, R. A Capacitance-Minimized, Doubly Grounded Transformer less Photovoltaic Inverter With Inherent Active-Power Decoupling. IEEE Trans. Power Electron. 2017, 32, 5188–5201. [Google Scholar] [CrossRef]

- Roy, J.; Xia, Y.; Ayyanar, R.; Ayyanar, R. Half-Bridge Voltage Swing Inverter With Active Power Decoupling for Single-Phase PV Systems Supporting Wide Power Factor Range. IEEE Trans. Power Electron. 2019, 34, 7450–7461. [Google Scholar] [CrossRef]

- Shi, Y.; Li, R.; Xue, Y.; Li, H. High-Frequency-Link Based Grid-tied PV System with Small DC-link Capacitor and Low-frequency Ripple-free Maximum Power Point Tracking. IEEE Trans. Power Electron. 2015, 31, 1. [Google Scholar] [CrossRef]

| Designator | Parameters | Values |

|---|---|---|

| VDC | PV Simulator Voltage | 380 V |

| VDC_link | DC-Link Voltage | 400 Vrms |

| Vrms | Inverter Output Voltage | 220 Vrms |

| Po | Inverter Output Power | 5 kW |

| Component | Manufacturer | Part Number |

|---|---|---|

| Mosfet | Rohm | SCH2080 KE |

| Filim Capacitor | Panasonic | |

| Magnetic Core | Changsung | PQ72/52 |

| Gate Driver | Silicon Lab | Si8275 |

| Designator | Parameters | Values |

|---|---|---|

| CDC | DC-Source Capacitance | 200 µF |

| CDC_link | DC-Link Capacitance | 400 µF |

| CBlocking | DC-Blocking Capacitance | 8 µF |

| Llk | Leakage Inductance | 20.71 µH |

| n | Transformer turns ratio | 1:1 |

| Fs | Switching Frequency (DAB) | 100 kHz |

| Fg | Switching Frequency (Inverter) | 10 kHz |

| Input Capacitor Values | Input Capacitor Reduction (%) | Ripple Reduction at DC input (%) | DC Input Voltages (V) | Ripple at the DC-Link (Vp-p) | Power | Additional Hardware Required | C × V/Power (μF×kV/kW) | |

|---|---|---|---|---|---|---|---|---|

| [10] | 2 × 50 µF | 64 | NP 1 | 200 | 20 | 425 W | Yes | 47.05 |

| [18] | 100 µF | 74 | 94.3 | 400 | NP | 2 kW | Yes | 20 |

| [26] | 2 × 100 µF | 90 | 90 | 150 | 50 | 500 W | No | 60 |

| [27] | 2 × 30 µF | 90 | 50 | 100 | 150 | 400 W | No | 15 |

| [28] | 320 µF | 90.4 | 58.6 | 200 | 50 | 1 kW | No | 40 |

| [29] | 100 µF | 78 | NP 1 | 100 | 130 | 500 W | No | 20 |

| [30] | 100 µF | 89 | 68 | 450 | 10.5 | 2 kW | No | 22.5 |

| [31] | 120 µF | 82 | 92 | 400 | 10.8 | 1 kW | Yes | 48 |

| [32] | 2 × 90 µF | 74.21 | 91 | 380 | 10 | 1 kW | Yes | 68.4 |

| [33] | 9 × 5 µF | 68 | 97 | 1100 | 280 | 3 kW | No | 16.5 |

| [34] | 2 × 12 µF/30 µF | 97 | NP | 165 | 150 | 1 kW | No | 27 |

| [35] | 30/120/10 µF | 95 | 96 | 150 | 146 | 4 kW | Yes | 32 |

| (Proposed) | 2 × 100 µF | 96 | 95 | 380 | 60 | 5 kW | No | 15.2 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Amin, S.; Lee, H.-H.; Choi, W. A Novel Power Decoupling Control Method to Eliminate the Double Line Frequency Ripple of Two Stage Single-Phase DC-AC Power Conversion Systems. Electronics 2020, 9, 931. https://doi.org/10.3390/electronics9060931

Amin S, Lee H-H, Choi W. A Novel Power Decoupling Control Method to Eliminate the Double Line Frequency Ripple of Two Stage Single-Phase DC-AC Power Conversion Systems. Electronics. 2020; 9(6):931. https://doi.org/10.3390/electronics9060931

Chicago/Turabian StyleAmin, Saghir, Hyun-Hwa Lee, and Woojin Choi. 2020. "A Novel Power Decoupling Control Method to Eliminate the Double Line Frequency Ripple of Two Stage Single-Phase DC-AC Power Conversion Systems" Electronics 9, no. 6: 931. https://doi.org/10.3390/electronics9060931

APA StyleAmin, S., Lee, H.-H., & Choi, W. (2020). A Novel Power Decoupling Control Method to Eliminate the Double Line Frequency Ripple of Two Stage Single-Phase DC-AC Power Conversion Systems. Electronics, 9(6), 931. https://doi.org/10.3390/electronics9060931