Bias Temperature Instability Aware and Soft Error Tolerant Radiation Hardened 10T SRAM Cell

Abstract

1. Introduction

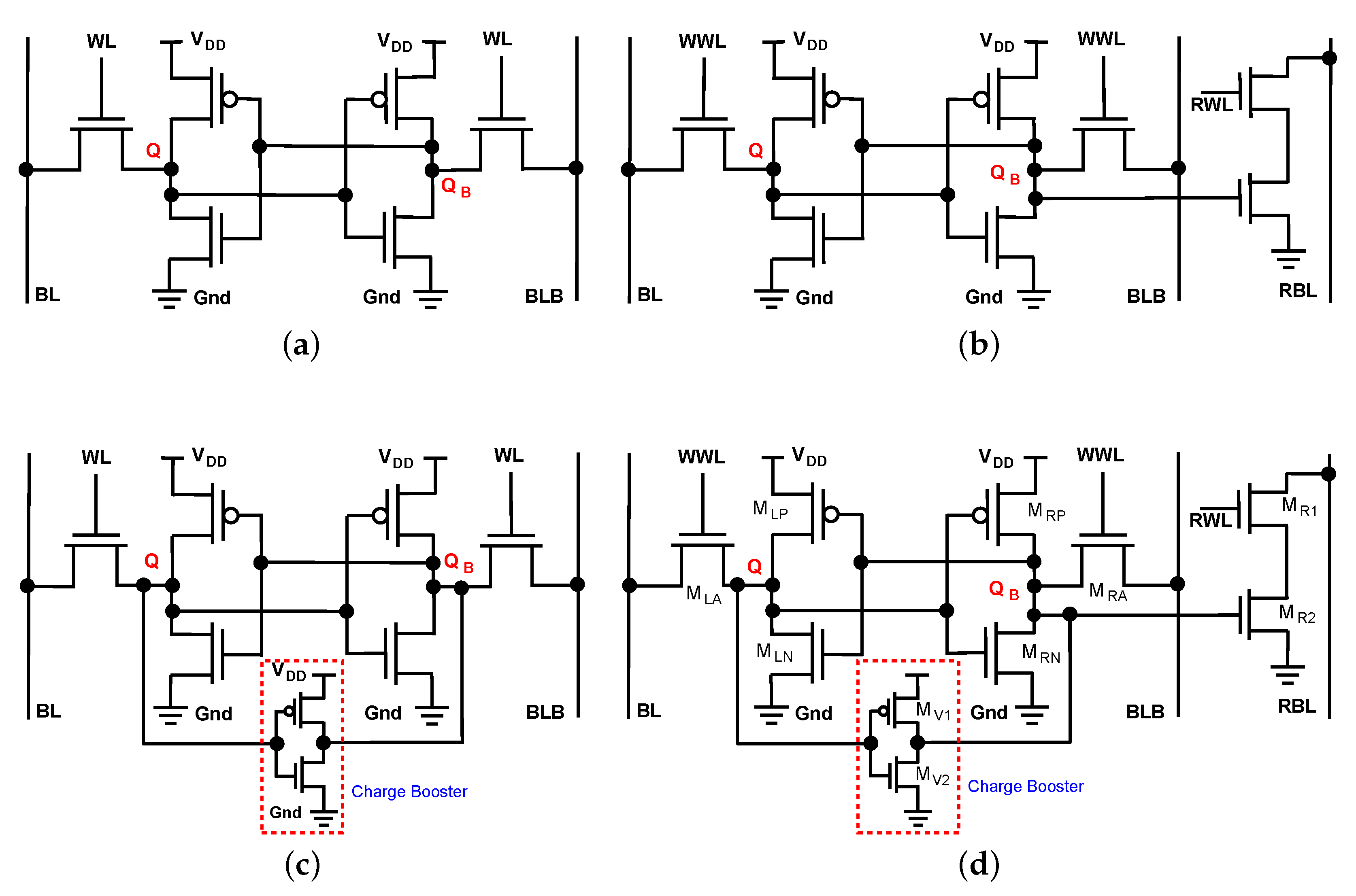

2. Proposed Radiation Hardened Asymmetric 10T SRAM Cell

- The charge booster circuit is added between the storage nodes which leads to a significant improvement of the critical charge of the cell.

- The read decoupled circuit is introduced to improve the RSNM of the proposed SRAM cell.

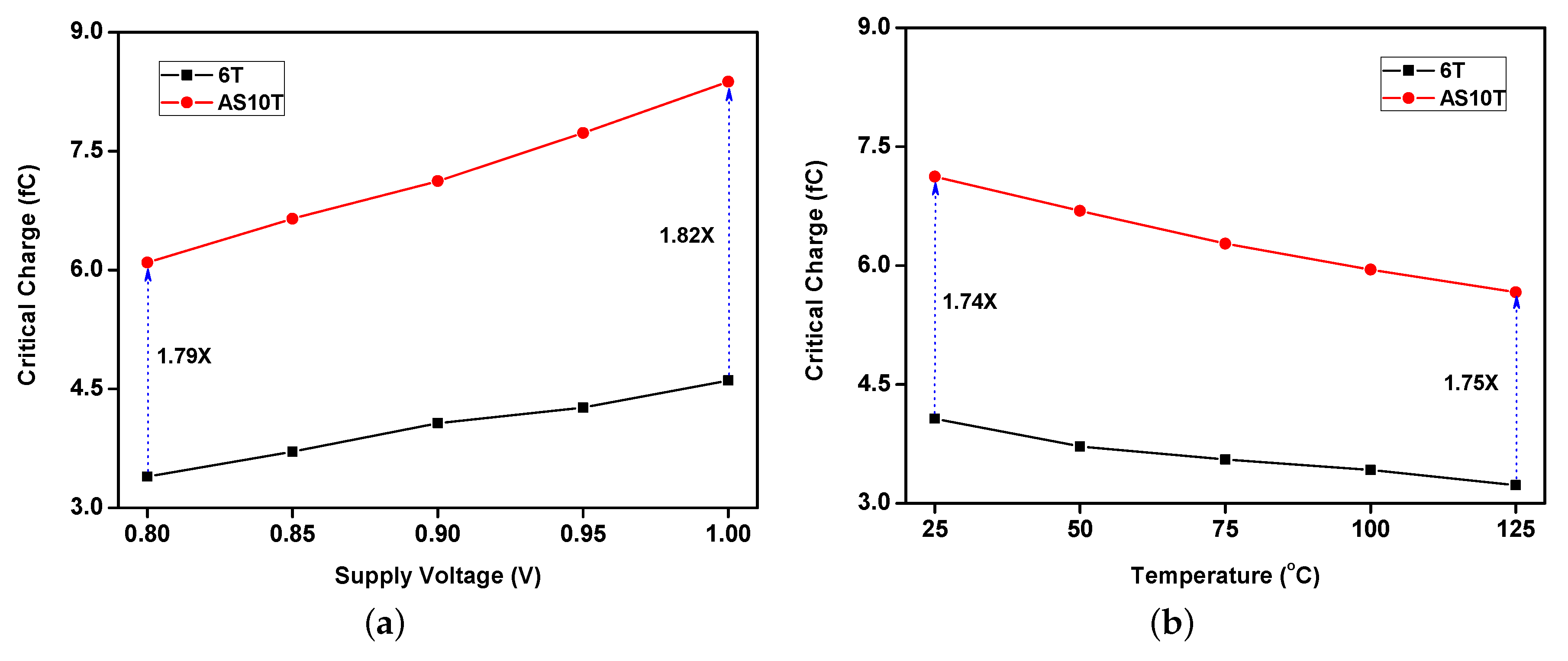

- A critical charge variation evaluation is discussed by considering different supply voltages and also temperature variation.

- We analyze the effect of BTI on the stability of the previously mentioned SRAM cells.

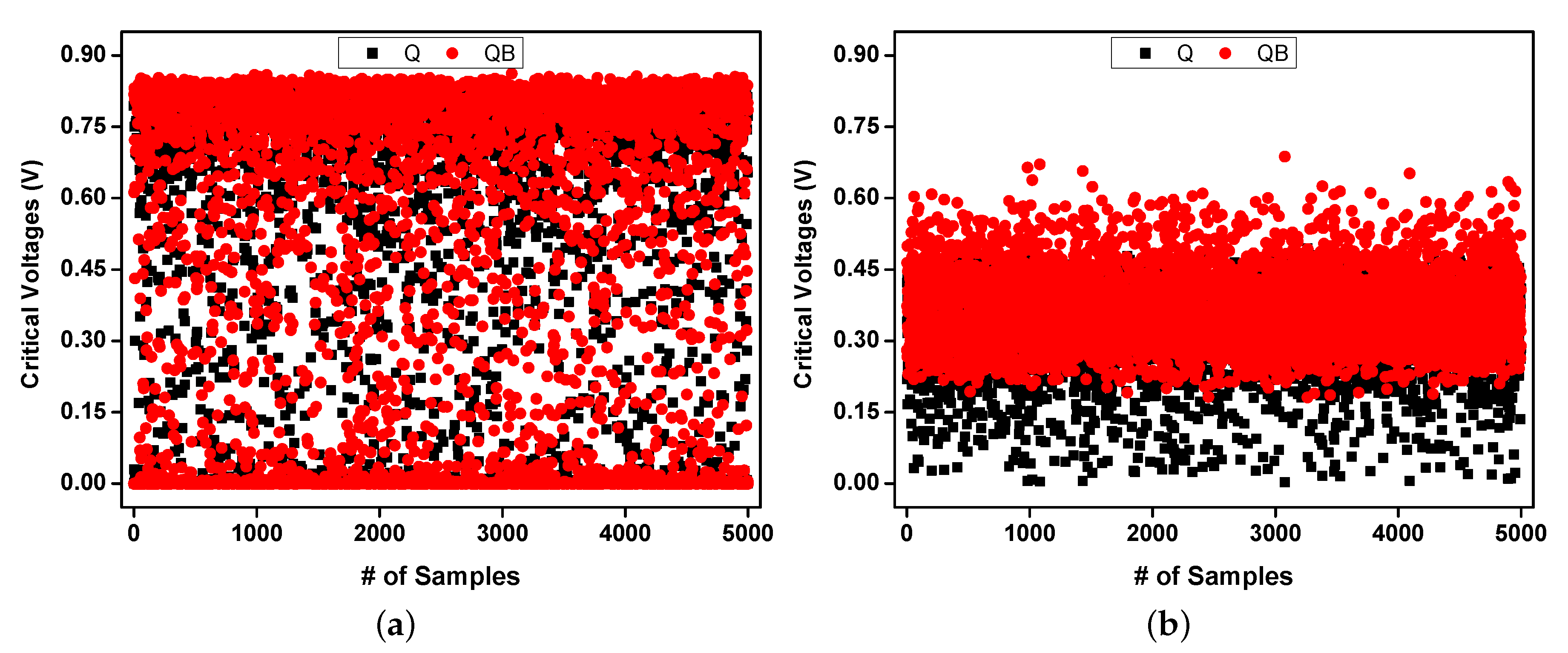

- Monte carlo simulations have been performed to analyze the effect of process variations on the considered cells.

3. Simulation Results and Discussion

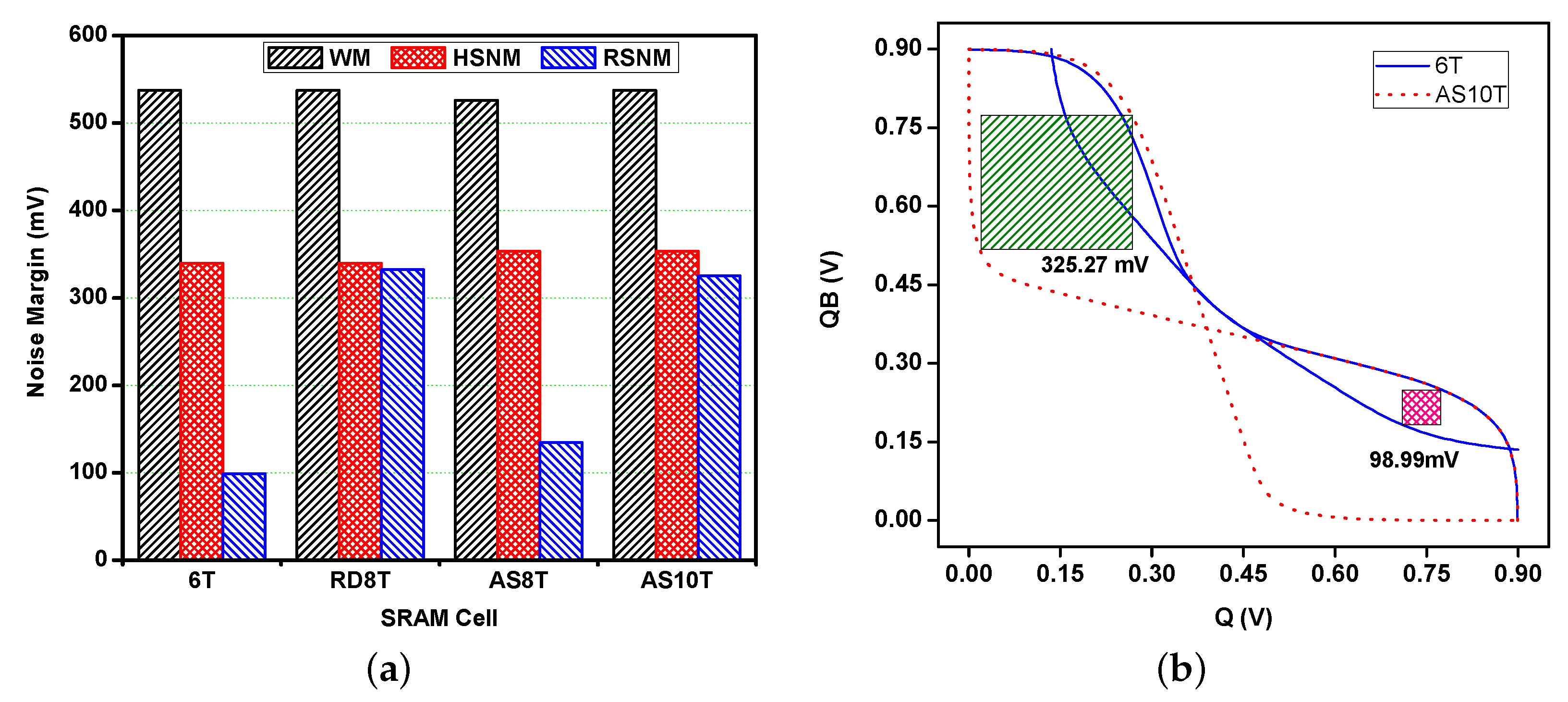

3.1. Stability Analysis

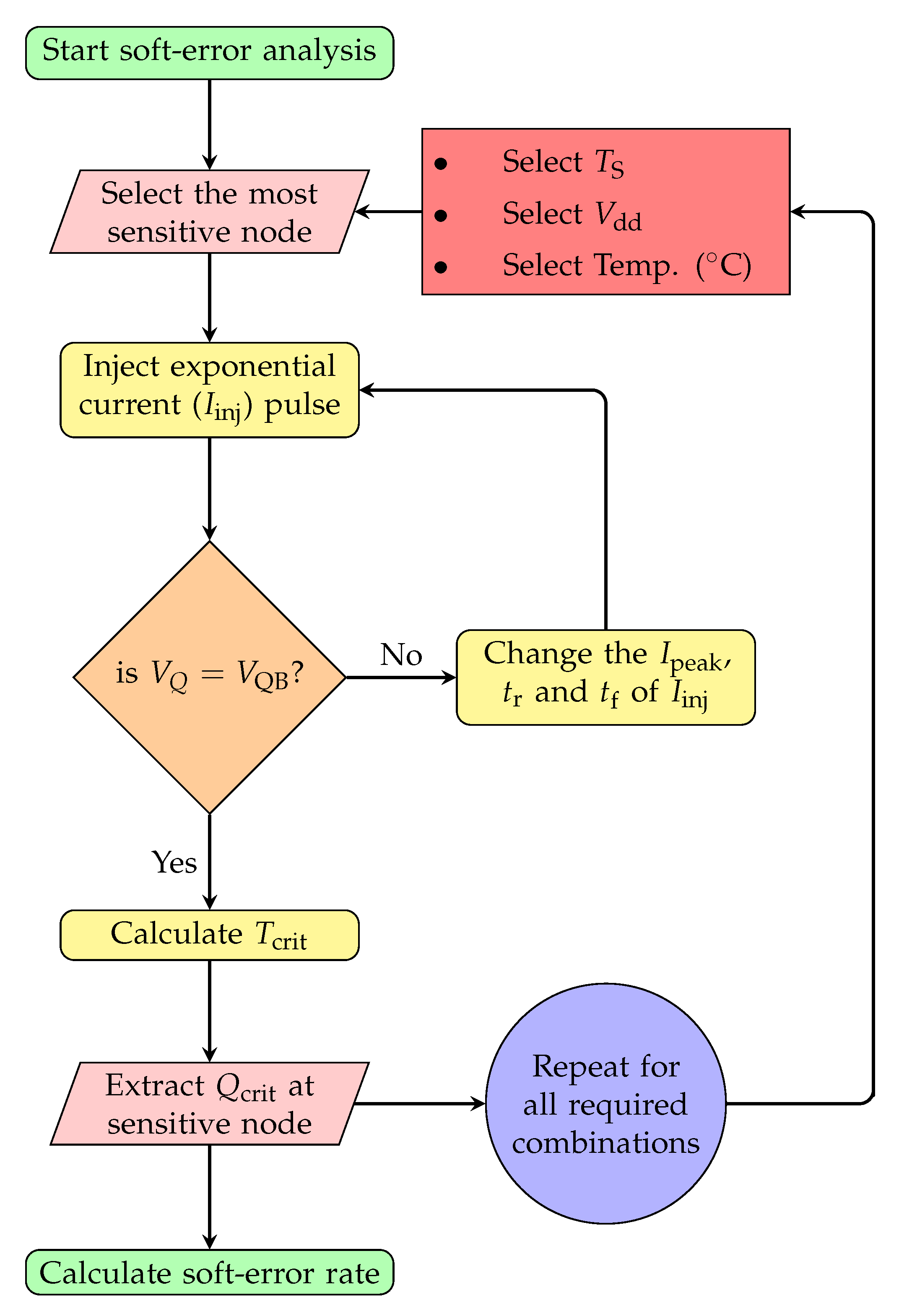

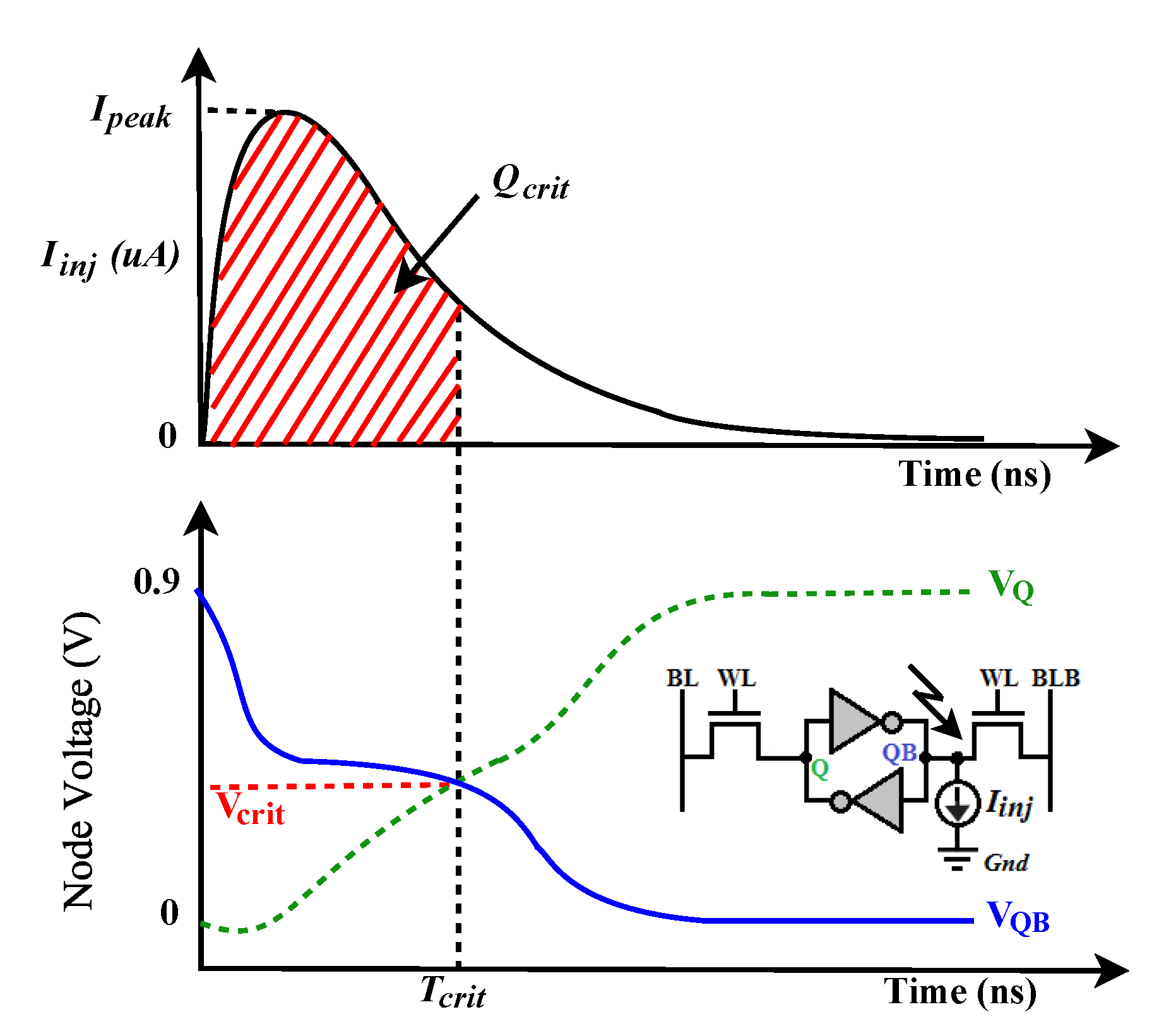

3.2. Critical Charge Analysis and Methodology

Effect of Supply Voltage Variation and Temperature Variation on the Critical Charge

3.3. Aging Effects on Performance of SRAM Cells

3.3.1. Effects on SRAM Stability

3.3.2. Effects on Critical Charge

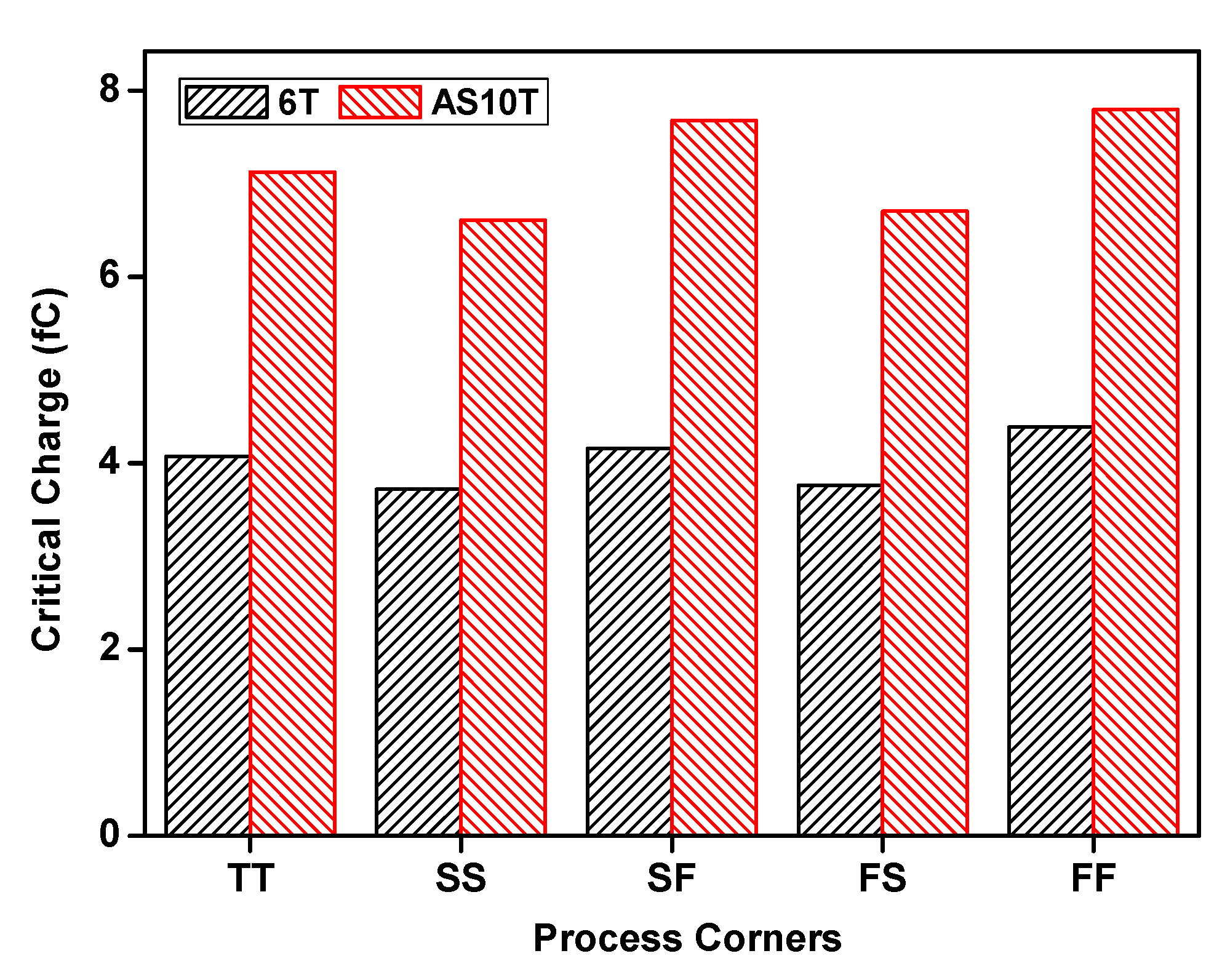

3.4. Process, Voltage and Temperature Variation Analysis

3.5. Power Consumption Analysis

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ferlet-Cavrois, V.; Massengill, L.W.; Gouker, P. Single event transients in digital CMOS—A review. IEEE Trans. Nucl. Sci. 2013, 60, 1767–1790. [Google Scholar] [CrossRef]

- Heidel, D.F.; Rodbell, K.P.; Oldiges, P.; Gordon, M.S.; Tang, H.H.K.; Cannon, E.H.; Plettner, C. Single-event-upset critical charge measurements and modeling of 65 nm silicon-on-insulator latches and memory cells. IEEE Trans. Nucl. Sci. 2006, 53, 3512–3517. [Google Scholar] [CrossRef]

- Rossi, D.; Omaña, M.; Metra, C.; Paccagnella, A. Impact of bias temperature instability on soft error susceptibility. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2015, 23, 743–751. [Google Scholar] [CrossRef]

- Chang, L.; Fried, D.M.; Hergenrother, J.; Sleight, J.W.; Dennard, R.H.; Montoye, R.K.; Sekaric, L.; McNab, S.J.; Topol, A.W.; Adams, C.D.; et al. Stable SRAM cell design for the 32 nm node and beyond. In Digest of Technical Papers Symposium on VLSI Technology; IEEE: Kyoto, Japan, 2005; pp. 128–129. [Google Scholar]

- Alouani, I.; Elsharkasy, W.M.; Eltawil, A.M.; Kurdahi, F.J.; Niar, S. AS8-static random access memory (SRAM): Asymmetric SRAM architecture for soft error hardening enhancement. IET Circuits Devices Syst. 2017, 11, 89–94. [Google Scholar] [CrossRef]

- Ahmad, S.; Alam, N.; Hasan, M. Pseudo differential multi-cell upset immune robust SRAM cell for ultra-low power applications. AEU-Int. J. Electron. Commun. 2018, 83, 366–375. [Google Scholar] [CrossRef]

- Kim, J.S.; Chang, I.J. We-quatro: Radiation-hardened SRAM cell with parametric process variation tolerance. IEEE Trans. Nucl. Sci. 2017, 64, 2489–2496. [Google Scholar]

- Sanvale, P.; Gupta, N.; Neema, V.; Shah, A.P.; Vishvakarma, S.K. An improved read-assist energy efficient single ended PPN based 10T SRAM cell for wireless sensor network. Microelectron. J. 2019, 92, 104611. [Google Scholar] [CrossRef]

- Predictive Technology Model (PTM). Available online: http://ptm.asu.edu/ (accessed on 12 December 2017).

- Synopsys. HSPICE User Guide: Simulation and Analysis 2010. Available online: https://www.ele.uri.edu/Courses/ele448/HspiceRef/hspice_sa.pdf (accessed on 2 December 2019).

- Jahinuzzaman, S.M.; Sharifkhani, M.; Sachdev, M. An analytical model for soft error critical charge of nanometric SRAMs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2009, 17, 1187–1195. [Google Scholar] [CrossRef]

- Lin, S.; Kim, Y.B.; Lombardi, F. Design and analysis of a 32 nm PVT tolerant CMOS SRAM cell for low leakage and high stability. Integr. VLSI J. 2010, 43, 176–187. [Google Scholar] [CrossRef]

- Shah, A.P.; Yadav, N.; Beohar, A.; Vishvakarma, S.K. On-chip Adaptive Body Bias for Reducing the Impact of NBTI on 6T SRAM Cells. IEEE Trans. Semicond. Manuf. 2018, 31, 242–249. [Google Scholar] [CrossRef]

| Operations | Control Signals | ||||

|---|---|---|---|---|---|

| BL | BLB | WWL | RWL | RBL | |

| Write 0 | 0 | 1 | 1 | 0 | 0 |

| Write 1 | 1 | 0 | 1 | 0 | 0 |

| Hold | × | × | 0 | 0 | 0 |

| Read | 1 | × | 1 | 1 | 1 |

| Stress | 6T | AS10T |

|---|---|---|

| No stress | 332.3 mV | 367.6 mV |

| NBTI | 325.2 mV | 360.6 mV |

| NBTI + PBTI | 318.2 mV | 353.5 mV |

| Stress Time | 6T | AS10T | ||

| (Years) | NBTI | BTI | NBTI | BTI |

| 0 | 4.07 | 4.07 | 7.12 | 7.12 |

| 1 | 3.88 | 3.83 | 7.08 | 7.07 |

| 2 | 3.84 | 3.78 | 7.07 | 7.06 |

| 3 | 3.81 | 3.75 | 7.06 | 7.05 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shah, A.P.; Waltl, M. Bias Temperature Instability Aware and Soft Error Tolerant Radiation Hardened 10T SRAM Cell. Electronics 2020, 9, 256. https://doi.org/10.3390/electronics9020256

Shah AP, Waltl M. Bias Temperature Instability Aware and Soft Error Tolerant Radiation Hardened 10T SRAM Cell. Electronics. 2020; 9(2):256. https://doi.org/10.3390/electronics9020256

Chicago/Turabian StyleShah, Ambika Prasad, and Michael Waltl. 2020. "Bias Temperature Instability Aware and Soft Error Tolerant Radiation Hardened 10T SRAM Cell" Electronics 9, no. 2: 256. https://doi.org/10.3390/electronics9020256

APA StyleShah, A. P., & Waltl, M. (2020). Bias Temperature Instability Aware and Soft Error Tolerant Radiation Hardened 10T SRAM Cell. Electronics, 9(2), 256. https://doi.org/10.3390/electronics9020256