Q-Factor Performance of 28 nm-Node High-K Gate Dielectric under DPN Treatment at Different Annealing Temperatures

Abstract

1. Introduction

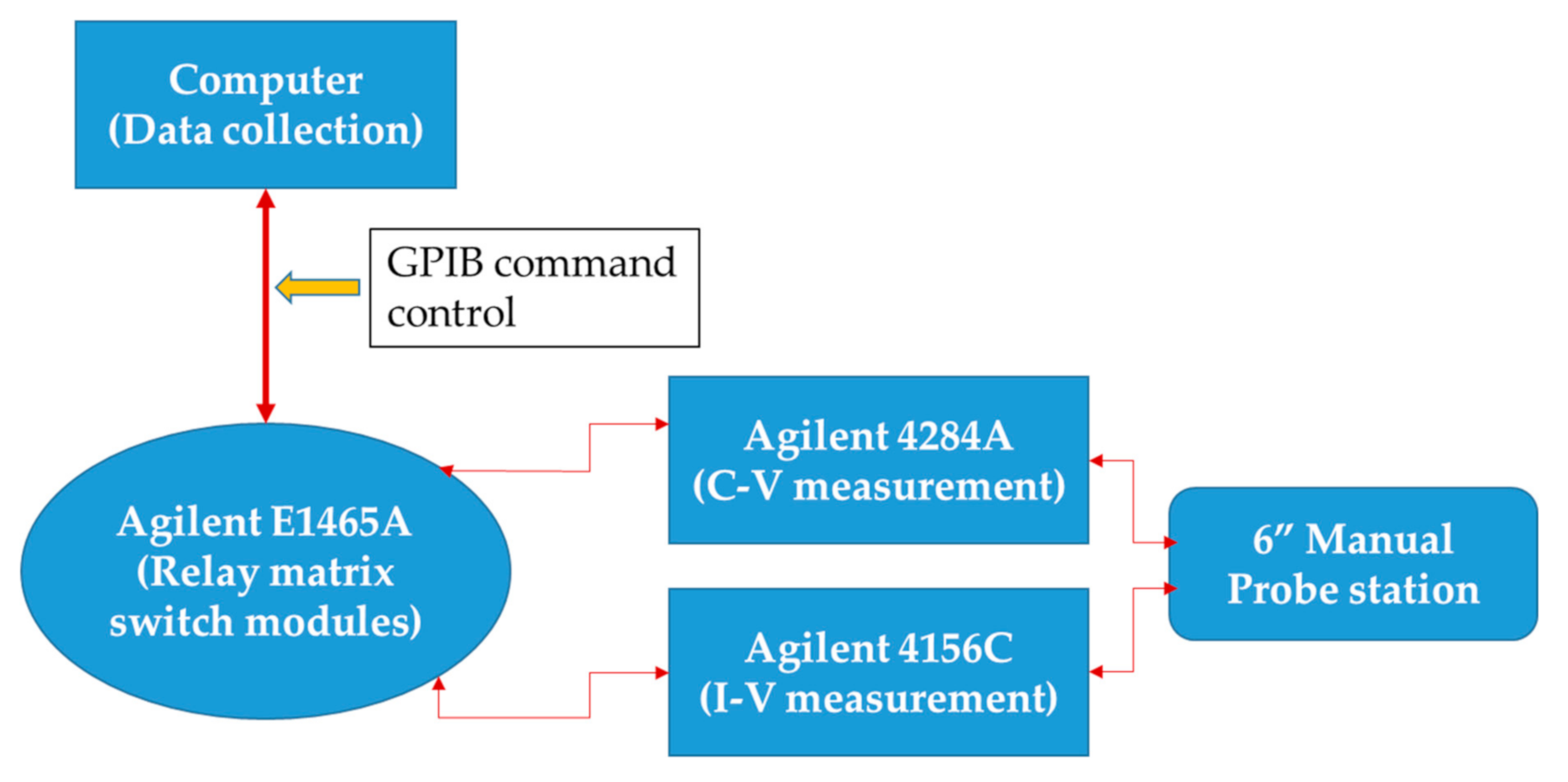

2. Measurement Setup for Gate Capacitance

3. Results

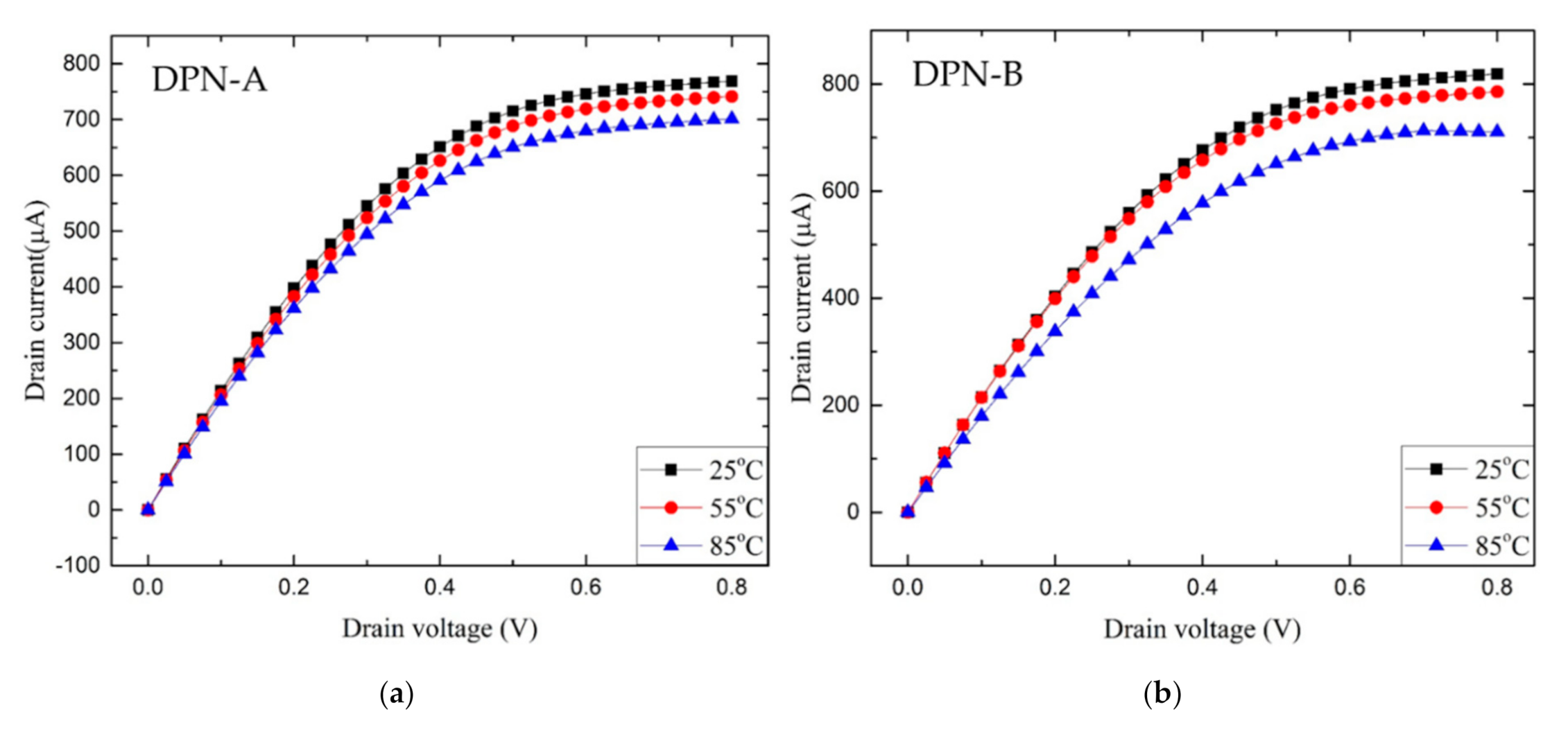

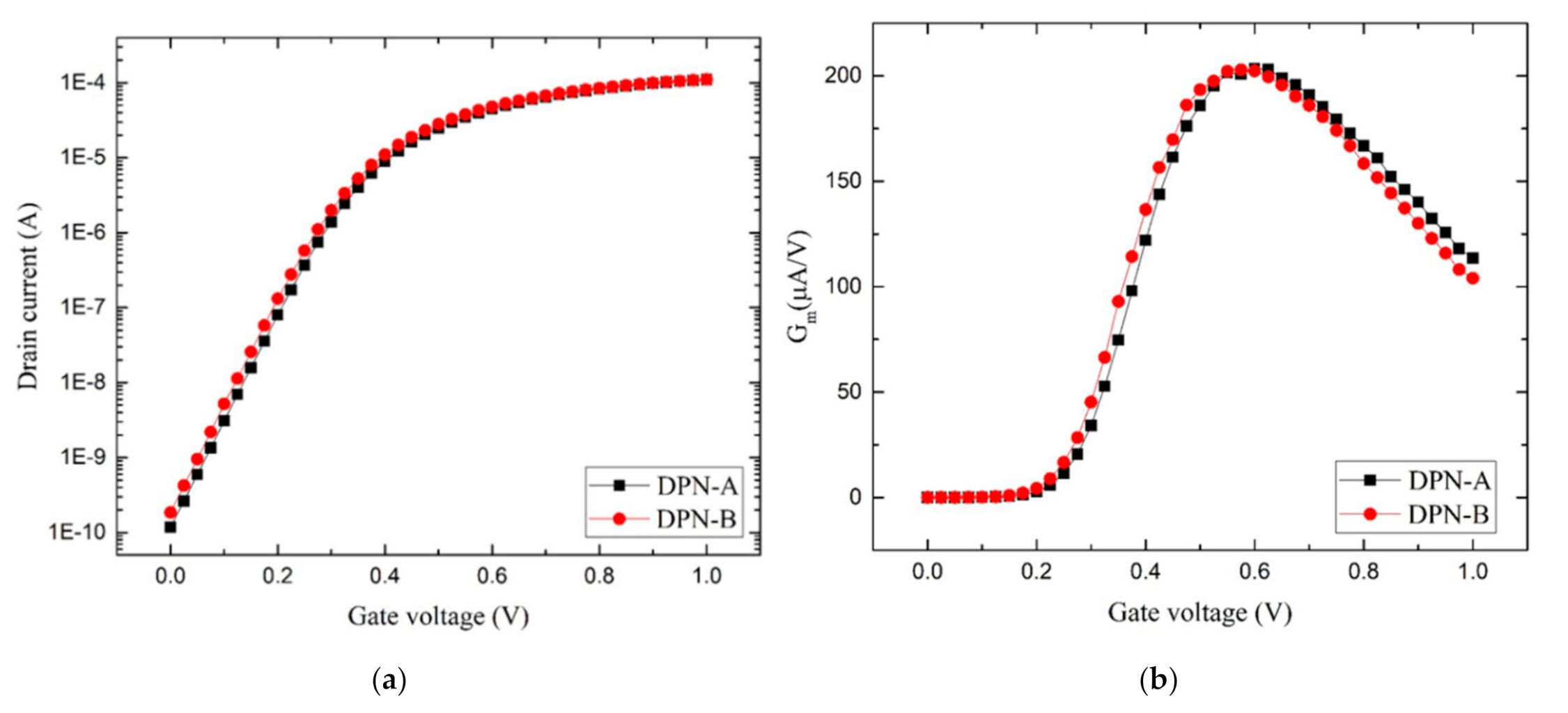

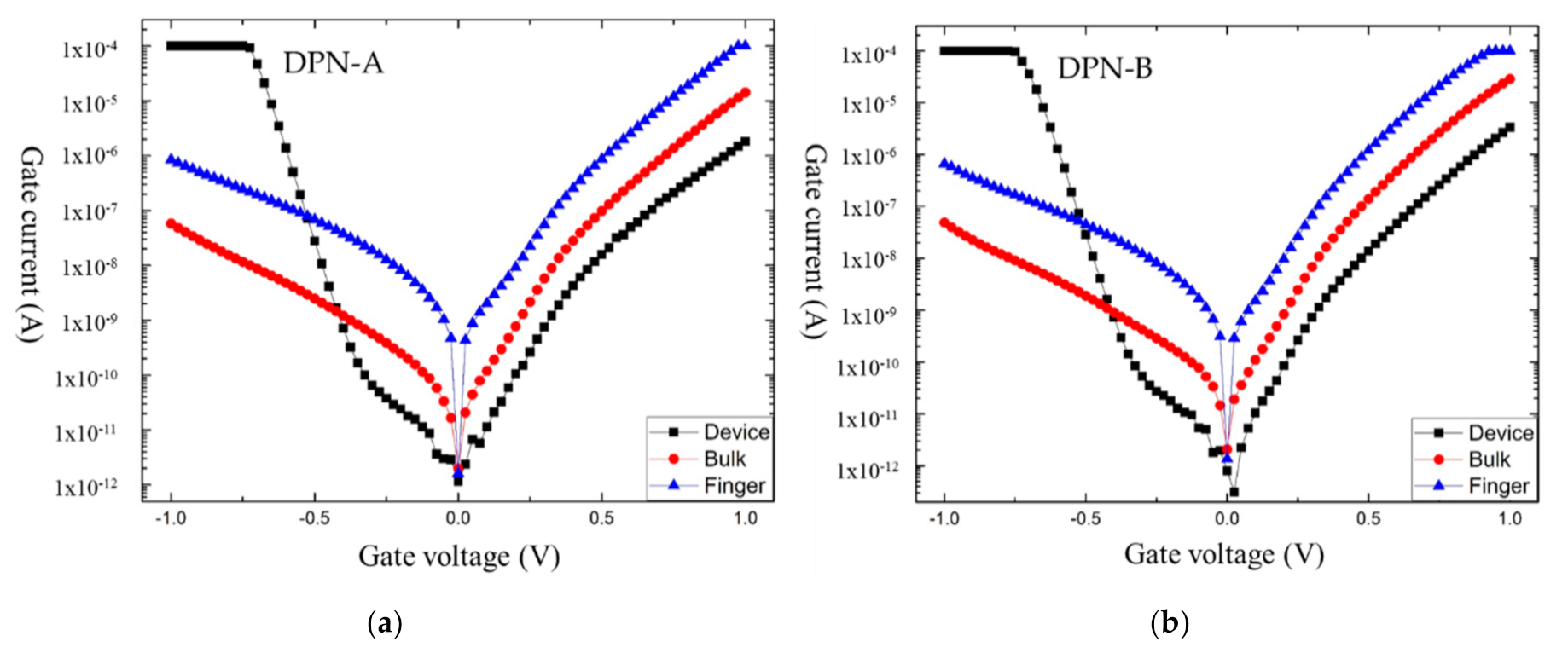

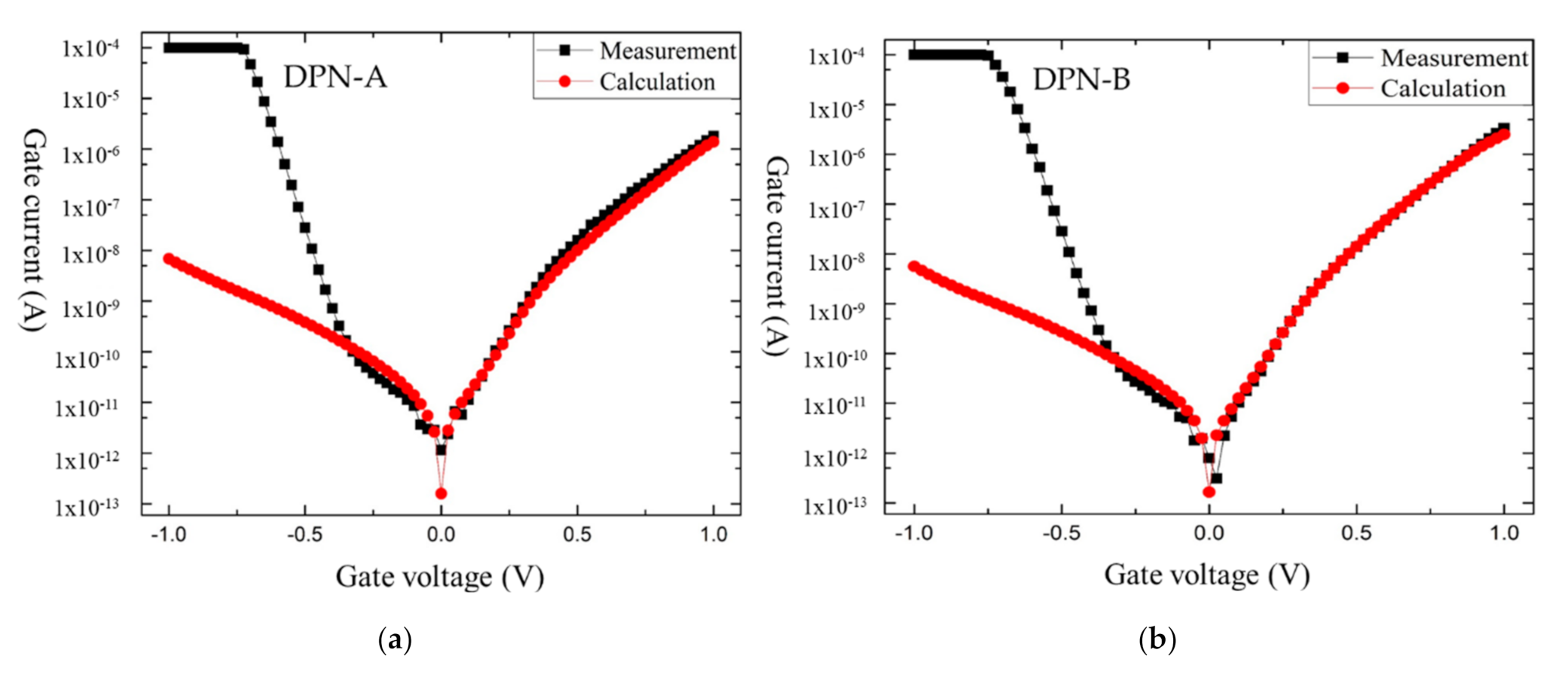

3.1. I–V Characteristics of N-Channel MOSFETs

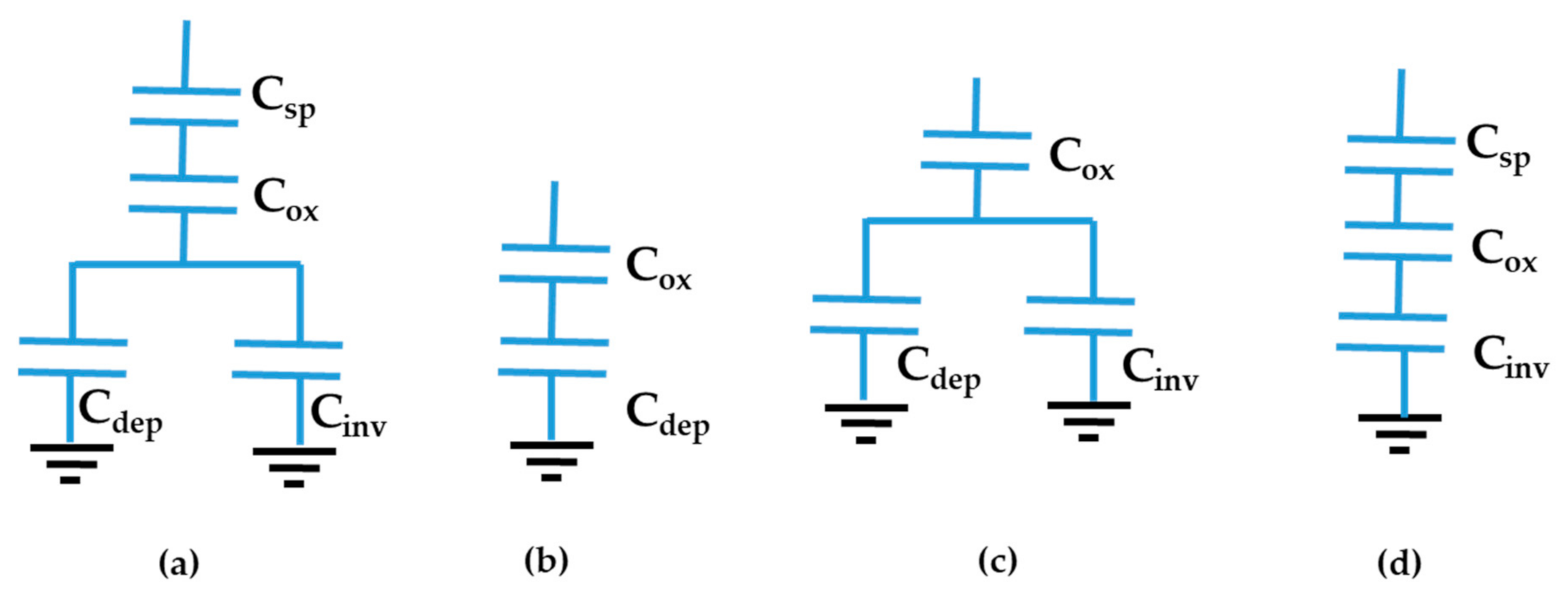

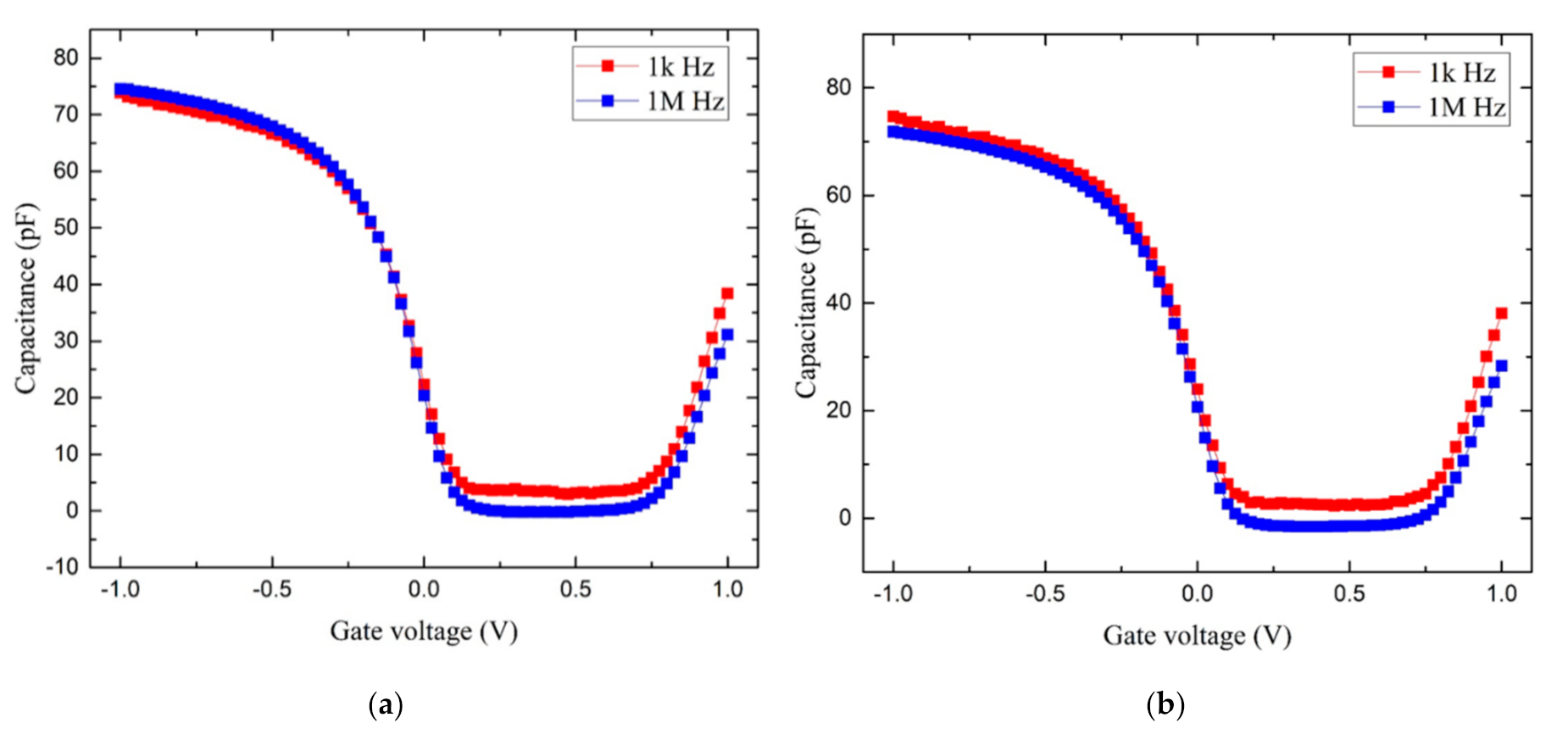

3.2. C–V Characteristics for Three Tested Devices

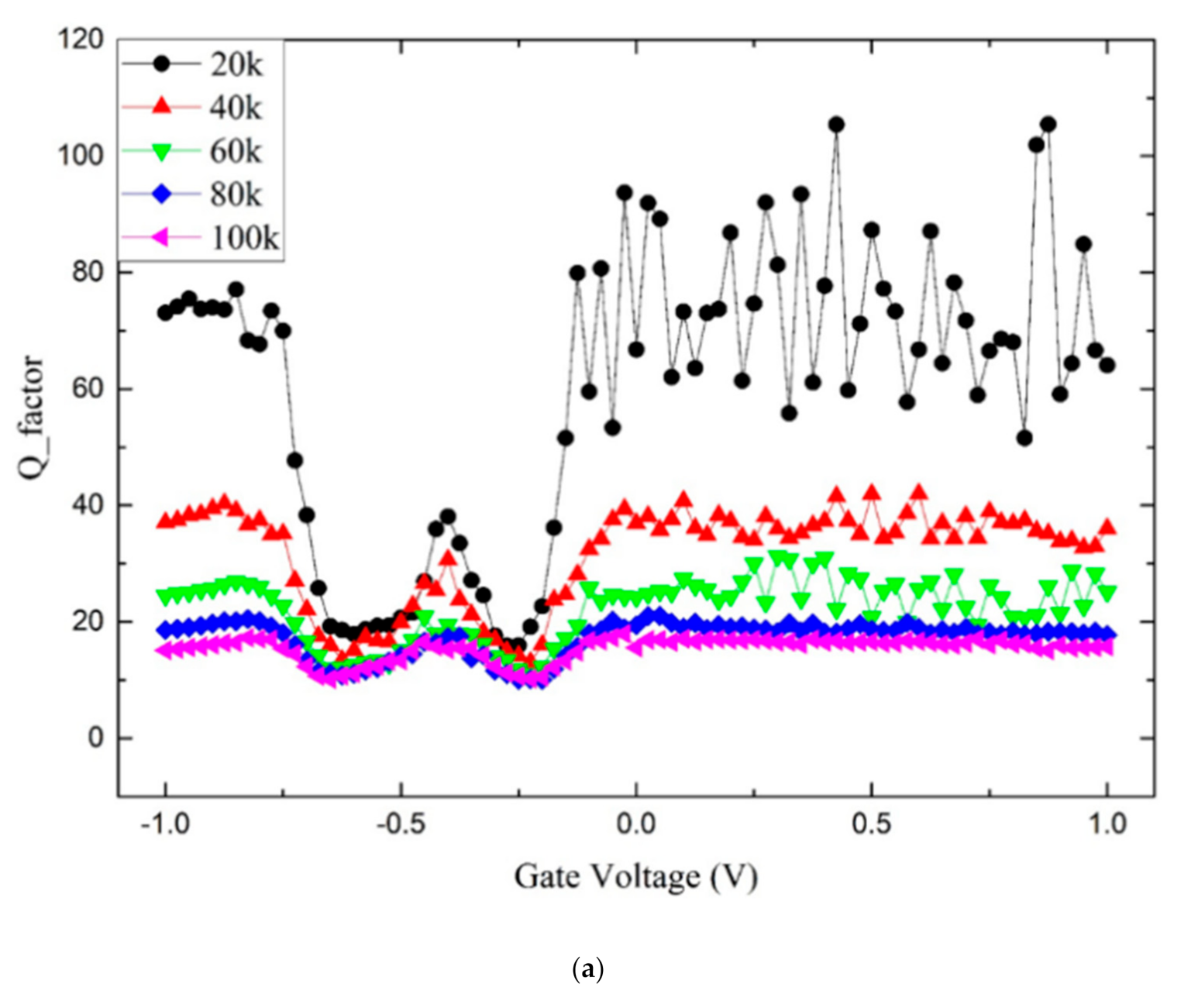

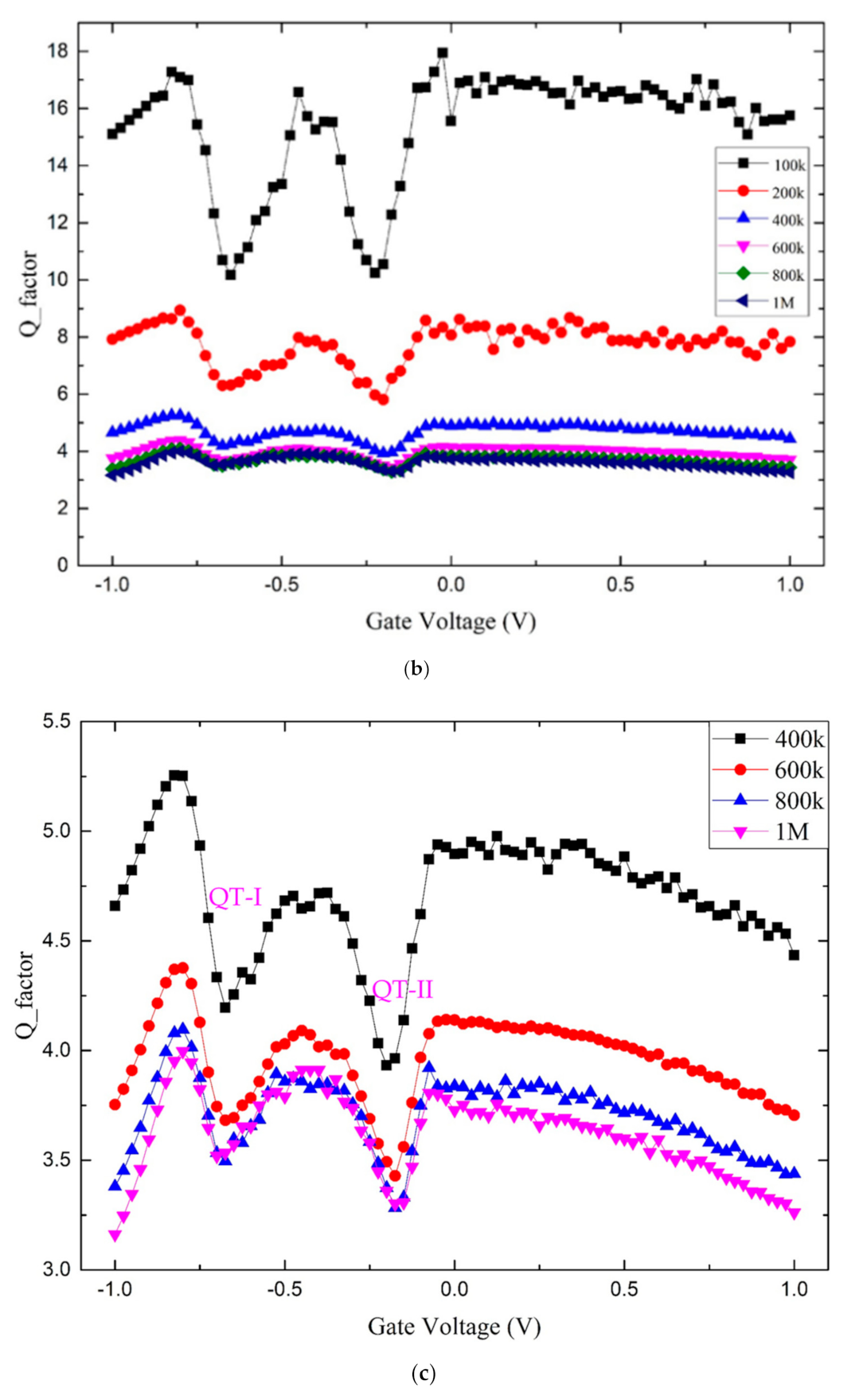

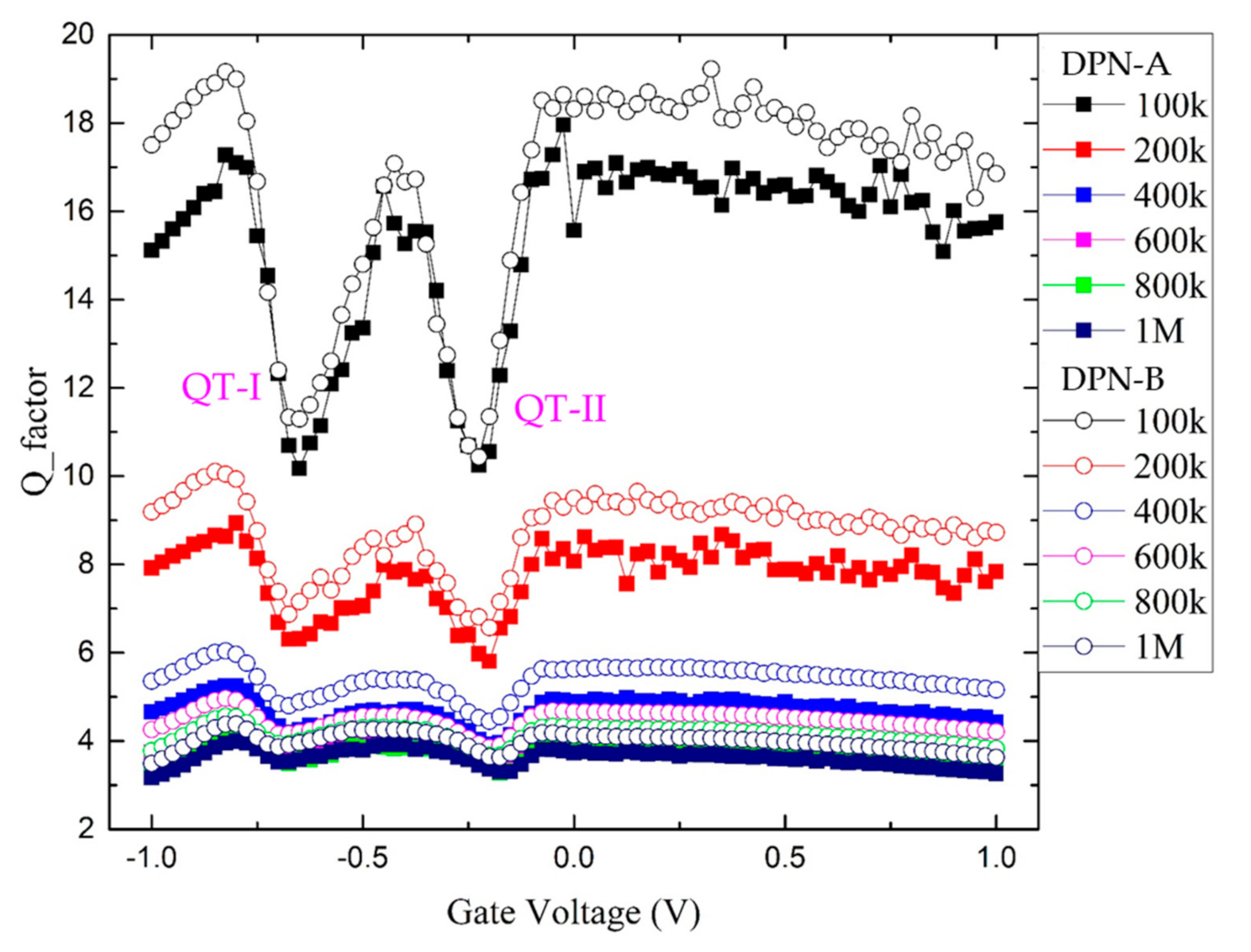

3.3. Q-Factor Performance in Frequency Response or Gate-Voltage Sweeping

4. Discussion

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Zheng, X.; Levine, D.; Shen, J.; Gogarten, S.M.; Laurie, C.; Weir, B.S. A high-performance computing toolset for relatedness and principal component analysis of SNP data. Bioinformatics 2012, 28, 3326–3328. [Google Scholar] [CrossRef] [PubMed]

- Russell, S.; Norvig, P. Artificial Intelligence: A Modern Approach, 4th ed.; Prentice Hall: New Jersey, NJ, USA, 2020; pp. 1–100. [Google Scholar]

- Noohani, M.Z.; Magsi, K.U. A review of 5G technology: Architecture, security and wide applications. Int. Res. J. Eng. Tech. 2020, 7, 1–32. [Google Scholar]

- Zheng, P.; Ni, L.M. Smart Phone and Next Generation Mobile Computing, 1st ed.; Elsevier: London, UK, 2006; pp. 1–97. [Google Scholar]

- Nordhoff, S.; Winter, J.D.; Kyriakidis, M.; Arem, B.V.; Happee, R. Acceptance of driverless vehicles: Results from a large cross-national questionnaire study. J. Adv. Transp. 2018, 2018, 1–22. [Google Scholar] [CrossRef]

- Patidar, S.; Rane, D.; Jain, P. A survey paper on cloud computing. In Proceedings of the IEEE 2nd International Conference on Advanced Computing & Communication Technologies, Rohtak, Haryana, India, 7–8 January 2012. [Google Scholar] [CrossRef]

- Hajare, R.; Lakshminarayana, C.; Sumanth, S.C.; Anish, A.R. Design and evaluation of FinFET based digital circuits for high speed ICs. In Proceedings of the IEEE International Conference on Emerging Research in Electronics, Computer Science and Technology (ICERECT), Mandya, India, 17–19 December 2015. [Google Scholar] [CrossRef]

- Kim, S.E.; Kang, T.; Oh, K.I.; Park, M.J.; Park, H.I.; Lim, I.G.; Lee, J.J. Energy management integrated circuit for multi-source energy harvesters in WBAN applications. Appl. Sci. 2018, 8, 1262–1279. [Google Scholar] [CrossRef]

- Kar, R.; Ramakrishna, K.; Mal, A.K.; Bhattacharjee, A.K. A novel and efficient approach for RC Delay evaluation of on-chip VLSI interconnect under current mode signaling technique. Int. J. Comp. Appl. 2010, 1, 64–67. [Google Scholar] [CrossRef]

- Fallah, F.; Pedram, M. Standby and active leakage current control and minimization in CMOS VLSI circuits. IEICE Trans. Electron 2005, E88–C, 509–519. [Google Scholar] [CrossRef]

- Eneman, G.; Verheyen, P.; Keersgieter, A.D.; Jurczak, M.; Meyer, K.D. Scalability of stress induced by contact-etch-stop layers: A simulation study. IEEE Trans. Electron Dev. 2007, 54, 1446–1453; [Google Scholar] [CrossRef]

- Lim, K.-Y.; Lee, H.; Ryu, C.; Seo, K.-I.; Kwon, U.; Kim, S.; Choi, J.; Oh, K.; Jeon, H.-K.; Song, C.; et al. Novel stress-memorization-technology (SMT) for high electron mobility enhancement of gate last high-k/metal gate devices. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010. [Google Scholar] [CrossRef]

- Yang, H.-C.; Li, C.-W.; Liao, W.-S.; Du, C.-K.; Wang, M.-C.; Yang, J.-M.; Lian, C.-W.; Liu, C.-H. The enhancement of MOSFET electric performance through strain engineering by refilled SiGe as Source and Drain. In Proceedings of the IEEE 5th International Nanoelectronics Conference (INEC), Singapore, 2–4 January 2013. [Google Scholar] [CrossRef]

- Silaghi, M.A. Dielectric Material; InTechOpen: London, UK, 2012. [Google Scholar]

- Gu, J.J.; Wu, Y.Q.; Ye, P.D. Effects of gate-last and gate-first process on deep submicron inversion-mode InGaAs n-channel metal-oxide-semiconductor field effect transistors. J. Appl. Phys. 2011, 109, 053709. [Google Scholar] [CrossRef]

- Baklanov, M.R.; Mogilnikov, K.P. Non-destructive characterization of porous low-k dielectric films. Microelectron. Eng. 2002, 64, 335–349. [Google Scholar] [CrossRef]

- Pisani, M.B.; Hibert, C.; Bouvet, D.; Beaud, P.; Ionescu, A.M. Copper/polyimide fabrication process for above-IC integration of high quality factor inductors. Microelectron. Eng. 2004, 73–74, 474–479. [Google Scholar] [CrossRef]

- Smith, B.W.; Fan, Y.; Slocum, M.; Zavyalova, L. 25 nm immersion lithography at 193 nm wavelength. In Proceedings of the SPIE Optical Microlithography XVIII, San Jose, CA, USA, 12 May 2005; Volume 5754. [Google Scholar] [CrossRef]

- Cho, M.; Ban, Y.; Pan, D.Z. Double patterning technology friendly detailed routing. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 10–13 November 2008. [Google Scholar] [CrossRef]

- Stulen, R.H. 13 nm extreme ultraviolet lithography. IEEE J. Quantum Electron. 1995, 1, 970–975. [Google Scholar] [CrossRef]

- Park, J.; Lee, S.G.; Vesters, Y.; Severi, J.; Kim, M.; De Simone, D.; Oh, H.-K.; Hur, S.-M. Molecular modeling of EUV photoresist revealing the effect of chain conformation on line-edge roughness formation. Polymers (Basel) 2019, 11, 1923. [Google Scholar] [CrossRef] [PubMed]

- Zhao, E.; Zhang, J.; Salman, A.; Subba, N.; Chan, J.; Marathe, A.; Beebe, S.; Taylor, K. Reliability challenges of high performance PD SOI CMOS with ultra-thin gate dielectrics. Solid State Electron. 2004, 48, 1703–1708. [Google Scholar] [CrossRef]

- Crupi, G.; Caddemi, A.; Schreurs, D.M.M.-P.; Wiatr, W.; Mercha, A. Microwave noise modeling of FinFETs. Solid State Electron. 2011, 56, 18–22. [Google Scholar] [CrossRef]

- Raskin, J.P.; Pailloncy, G.; Lederer, D.; Danneville, F.; Dambrine, G.; Decoutere, S.; Mercha, A.; Parvais, B. High-frequency noise performance of 60 nm gate-length FinFETs. IEEE Trans. Electron Dev. 2008, 55, 2718–2727. [Google Scholar] [CrossRef]

- Crupi, G.; Schreurs, D.M.M.-P.; Caddemi, A.; Angelov, I.; Homayouni, M.; Raffo, A.; Vannini, G.; Parvais, B. Purely analytical extraction of an improved nonlinear FinFET model including non-quasi-static effects. Microelectron. Eng. 2009, 86, 2283–2289. [Google Scholar] [CrossRef]

- Lederer, D.; Kilchytska, V.; Rudenko, T.; Collaert, N.; Flandre, D.; Dixit, A.; De Meyer, K.; Raskin, J.-P. FinFET analogue characterization from DC to 110 GHz. Solid State Electron. 2005, 49, 1488–1496. [Google Scholar] [CrossRef]

- Zhang, M.; Guo, Y.; Chen, J.; Zhang, J.; Tong, Y. Simulation investigation of the diffusion enhancement effects in FinFET with graded fin width. IEEE Trans. Nanotech. 2019, 18, 700–703. [Google Scholar] [CrossRef]

- Barraud, S.; Lapras, V.; Previtali, B.; Samson, M.P.; Lacord, J.; Martinie, S.; Jaud, M.-A.; Athanasiou, S.; Triozon, F.; Rozeau, O.; et al. Performance and design considerations for gate-all-around stacked-nanowires FETs. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017. [Google Scholar] [CrossRef]

- Lee, S.Y.; Kim, S.M.; Yoon, E.J.; Oh, C.W.; Chung, I.; Park, D.; Kim, K. A novel multi-bridge-channel MOSFET (MBCFET): Fabrication technologies and characteristics. IEEE Trans. Nanotech. 2004, 2, 253–257. [Google Scholar] [CrossRef]

- Lahtinen, K.; Maydannik, P.; Johansson, P.; Kääriäinen, T.; Cameron, D.C.; Kuusipalo, J. Utilisation of continuous atomic layer deposition process for barrier enhancement of extrusion-coated paper. Surf. Coat. Tech. 2011, 205, 3916–3922. [Google Scholar] [CrossRef]

- Lim, S.W.; Luo, T.Y.; Jiang, J. Mechanism of silicon dioxide decoupled plasma nitridation. Jpn. J. Appl. Phys. 2006, 45, L413. [Google Scholar] [CrossRef]

- Chang, H.W.; Huang, P.K.; Yeh, J.W.; Davison, A.; Tsau, C.H.; Yang, C.C. Influence of substrate bias, deposition temperature and post-deposition annealing on the structure and properties of multi-principal-component (AlCrMoSiTi)N coatings. Surf. Coat. Tech. 2008, 202, 3360–3366. [Google Scholar] [CrossRef]

- Abdelghany, M.; Szkopek, T. Extreme sub-threshold swing in tunneling relays. Appl. Phys. Lett. 2014, 104, 013509. [Google Scholar] [CrossRef]

- Lee, S.T.S.; Chung, H.S.-H.; Hui, S.Y. Use of saturable inductor to improve the dimming characteristics of frequency-controlled dimmable electronic ballasts. IEEE Trans. Power Electron. 2004, 19, 1653–1660. [Google Scholar] [CrossRef]

- Cao, Y.; Groves, R.A.; Huang, X.; Zamdmer, N.D.; Plouchart, J.O.; Wachnik, R.A.; King, T.J.; Hu, C. Frequency-Independent equivalent-circuit model for on-chip spiral inductors. IEEE J. Solid-State Circ. 2003, 38, 419–426. [Google Scholar] [CrossRef]

- Barzegar, S.; Mirzajani, H.; Ghavifekr, H.B. A new linearly tunable RF MEMS varactor with latching mechanism for low voltage and low power reconfigurable networks. Wirel. Pers. Commun. 2015, 83, 2249–2265. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics, 2nd ed.; Pearson: New York, NY, USA, 2012; pp. 1–155. [Google Scholar]

- Wang, S.J.; Sung, S.P.; Wang, M.C.; Huang, H.S.; Chen, S.Y.; Fan, S.K. Electrical stress probing recovery efficiency of 28 nm HK/MG nMOSFETs using decoupled plasma nitridation treatment. Vacuum 2018, 153, 117–121. [Google Scholar] [CrossRef]

- Hu, C. Modern Semiconductor Devices for Integrated Circuits, 1st ed.; Pearson: New York, NY, USA, 2010; pp. 175–307. [Google Scholar]

- Boucart, K.; Ionescu, A.M. Length scaling of the Double Gate Tunnel FET with a high-k gate dielectric. Solid State Electron. 2007, 51, 1500–1507. [Google Scholar] [CrossRef]

| Wafer Group | SiOx(IL) (Å) | HfOx/ZrOy/HfOx (Cycles) | Annealing Temperature (°C) | N2 |

|---|---|---|---|---|

| DPN-A | 9~12 | 10/4/10 | 700 | 8% |

| DPN-B | 9~12 | 10/4/10 | 900 | 8% |

| Wafer Group | Vth (V) | SS (mV/decade) |

|---|---|---|

| DPN-A | 0.328 | 67.7 |

| DPN-B | 0.305 | 69.6 |

| Group/Gate Leakage | IG_finger at −Vcc | IG_bulk at −Vcc | IG_finger at Vcc | IG_bulk at Vcc |

|---|---|---|---|---|

| DPN-A | −3.11 × 10−7 | −1.55 × 10−8 | 1.95 × 10−5 | 2.24 × 10−6 |

| DPN-B | −2.12 × 10−7 | −1.21 × 10−8 | 3.41 × 10−5 | 4.50 × 10−6 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, C.-W.; Wang, S.-J.; Hsieh, W.-C.; Chen, J.-M.; Jong, T.; Lan, W.-H.; Wang, M.-C. Q-Factor Performance of 28 nm-Node High-K Gate Dielectric under DPN Treatment at Different Annealing Temperatures. Electronics 2020, 9, 2086. https://doi.org/10.3390/electronics9122086

Chen C-W, Wang S-J, Hsieh W-C, Chen J-M, Jong T, Lan W-H, Wang M-C. Q-Factor Performance of 28 nm-Node High-K Gate Dielectric under DPN Treatment at Different Annealing Temperatures. Electronics. 2020; 9(12):2086. https://doi.org/10.3390/electronics9122086

Chicago/Turabian StyleChen, Chii-Wen, Shea-Jue Wang, Wen-Ching Hsieh, Jian-Ming Chen, Te Jong, Wen-How Lan, and Mu-Chun Wang. 2020. "Q-Factor Performance of 28 nm-Node High-K Gate Dielectric under DPN Treatment at Different Annealing Temperatures" Electronics 9, no. 12: 2086. https://doi.org/10.3390/electronics9122086

APA StyleChen, C.-W., Wang, S.-J., Hsieh, W.-C., Chen, J.-M., Jong, T., Lan, W.-H., & Wang, M.-C. (2020). Q-Factor Performance of 28 nm-Node High-K Gate Dielectric under DPN Treatment at Different Annealing Temperatures. Electronics, 9(12), 2086. https://doi.org/10.3390/electronics9122086