An Optimum Design of Clocked AC-DC Charge Pump Circuits for Vibration Energy Harvesting

Abstract

1. Introduction

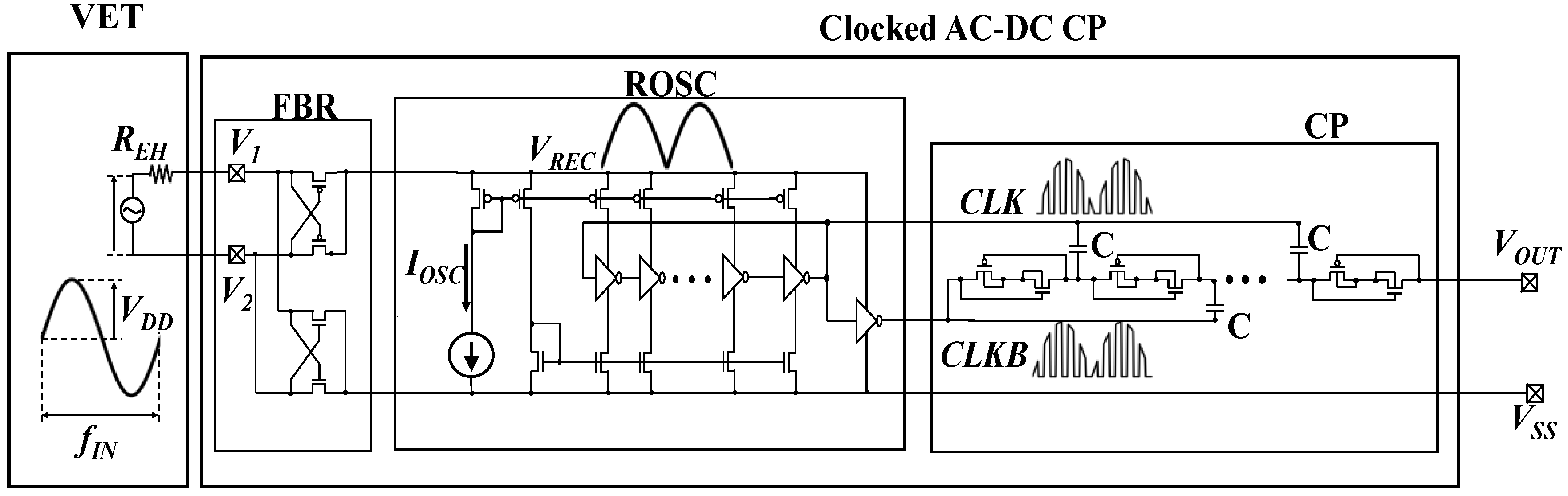

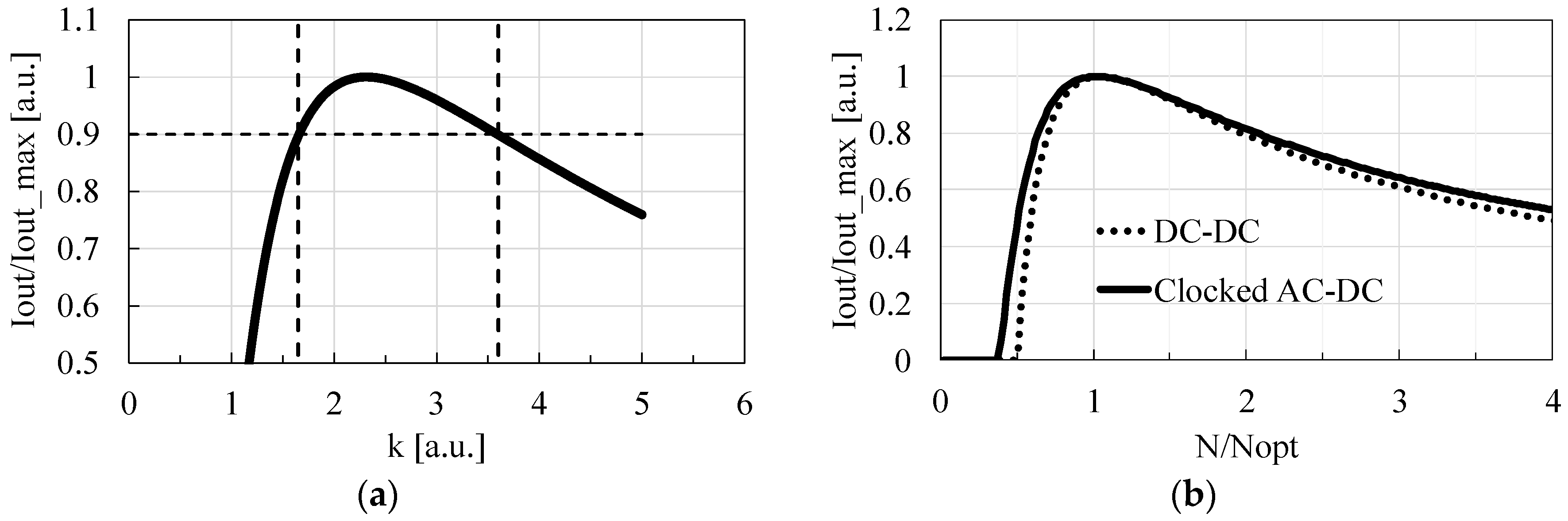

2. Optimum Design of Clocked AC-DC Charge Pumps

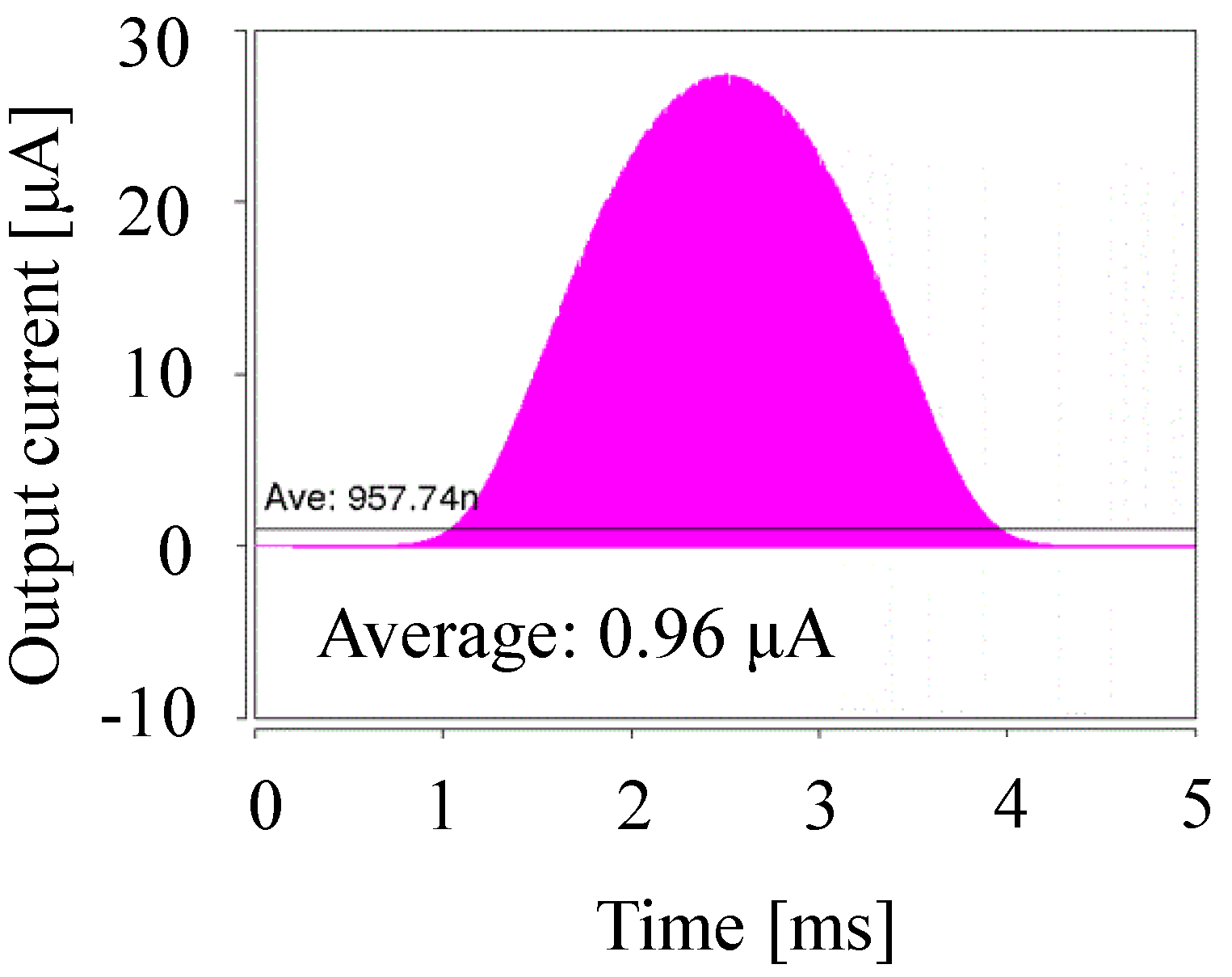

3. Validation of the Proposed Design

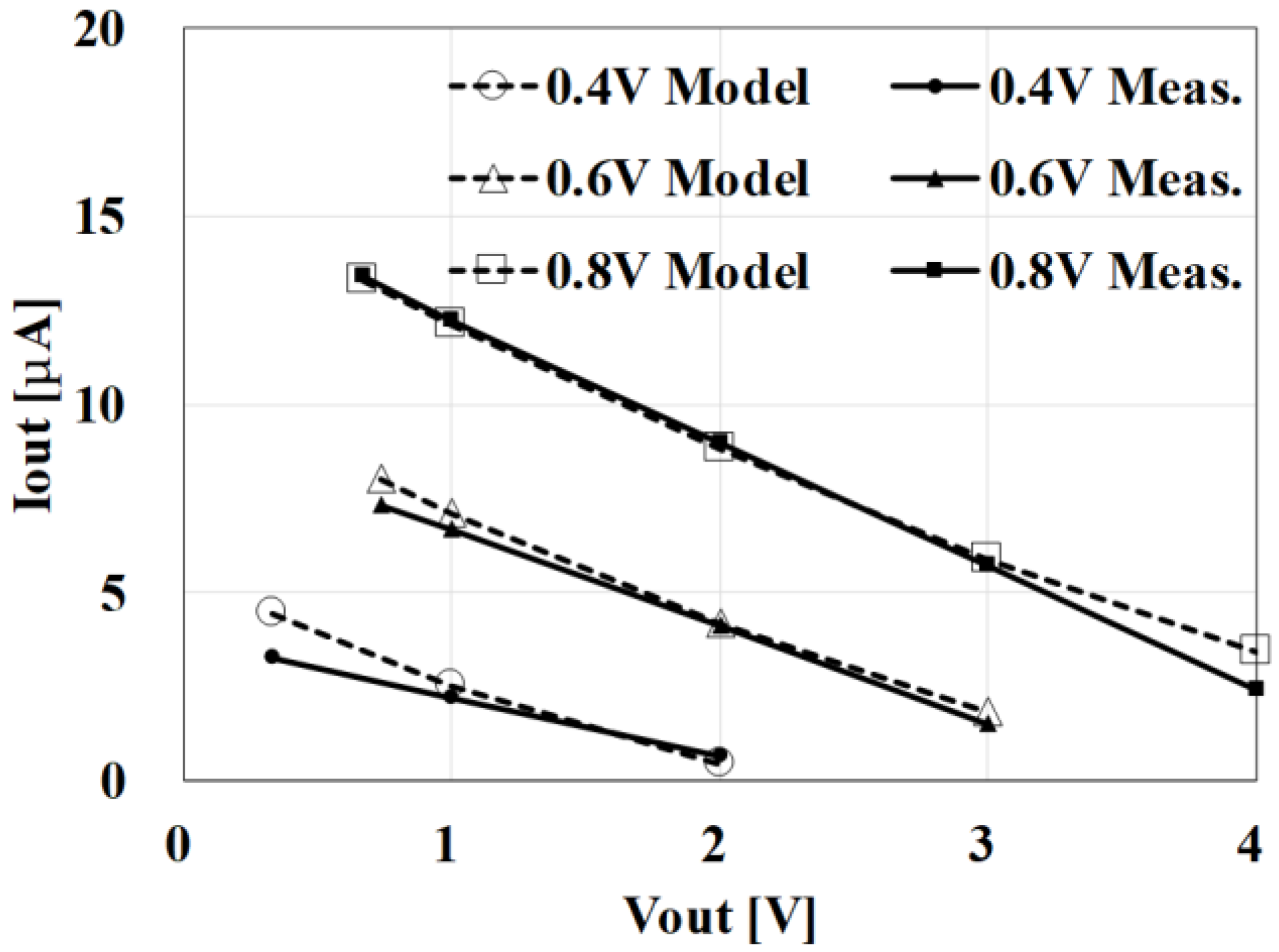

3.1. Validation of the Analytical IOUT-VOUT Equation

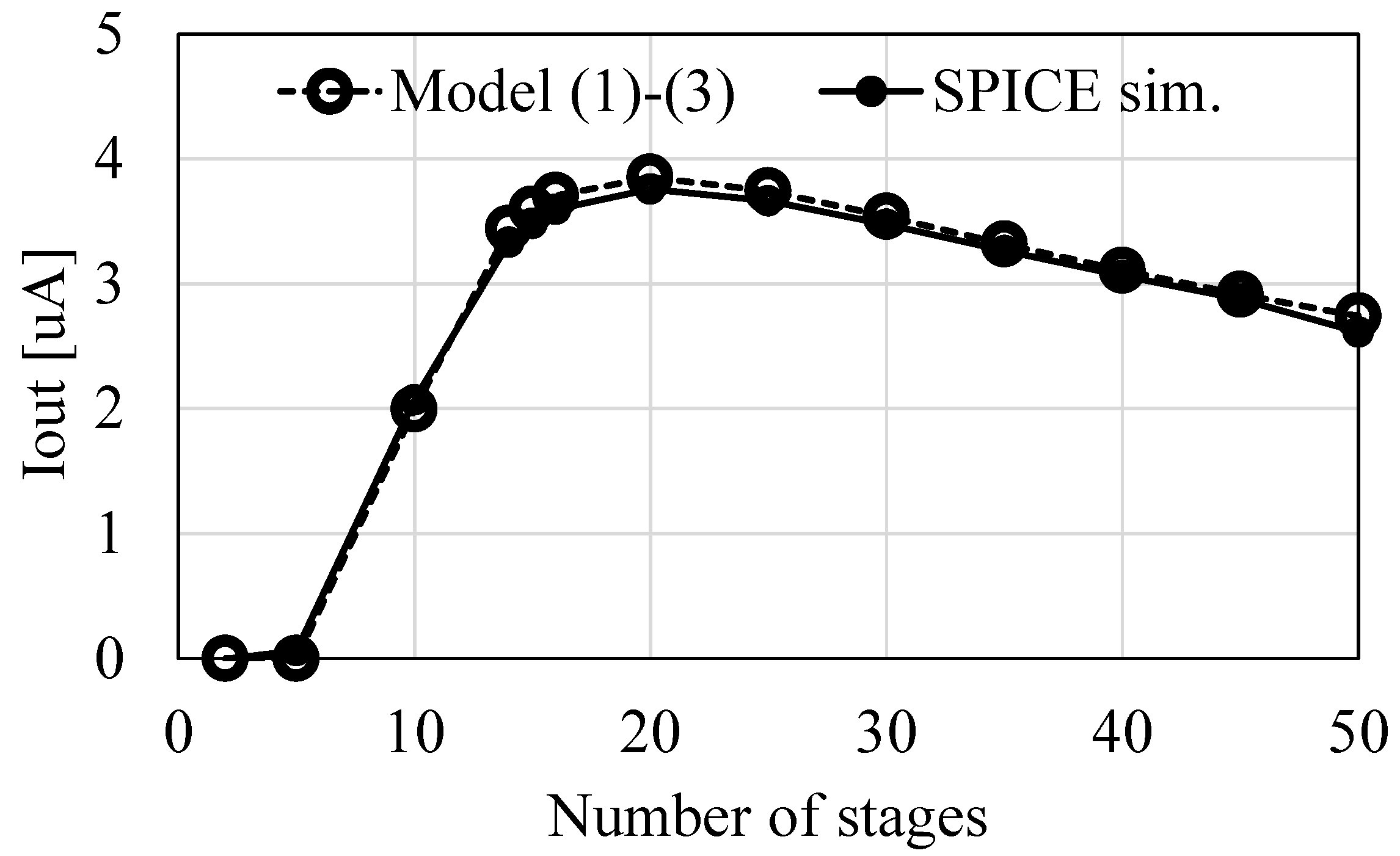

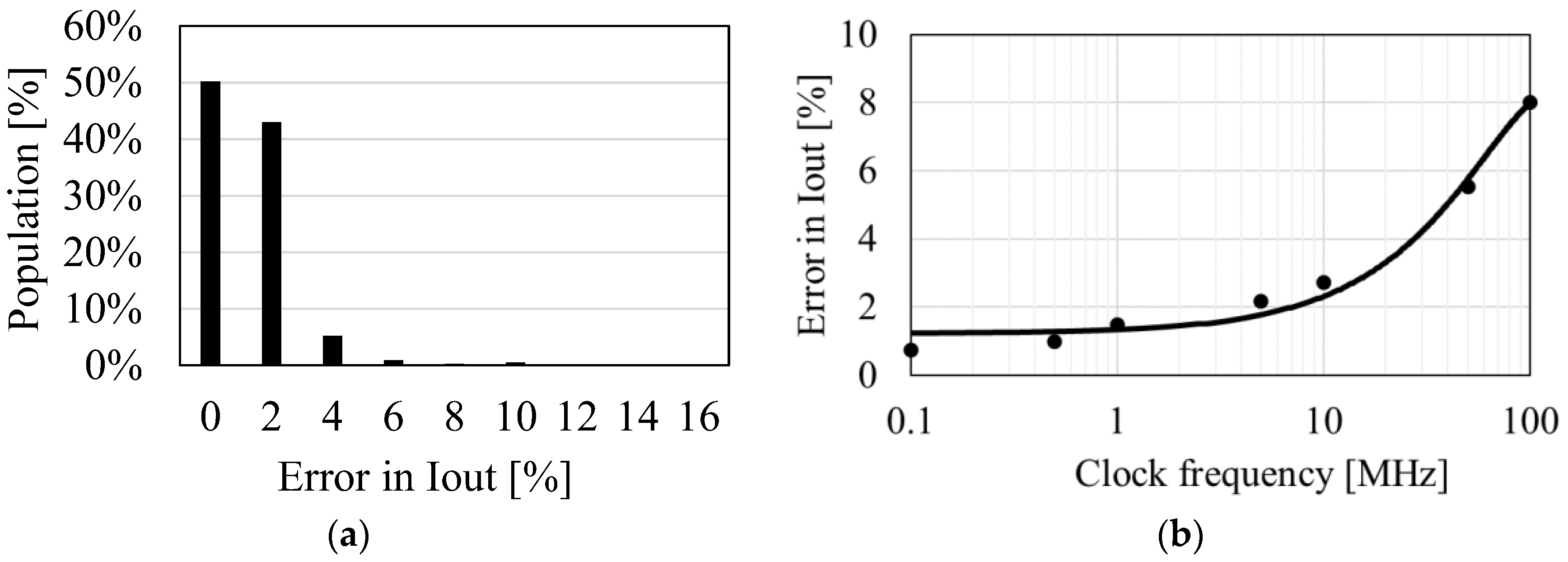

3.2. Validation of the Optimization Equation

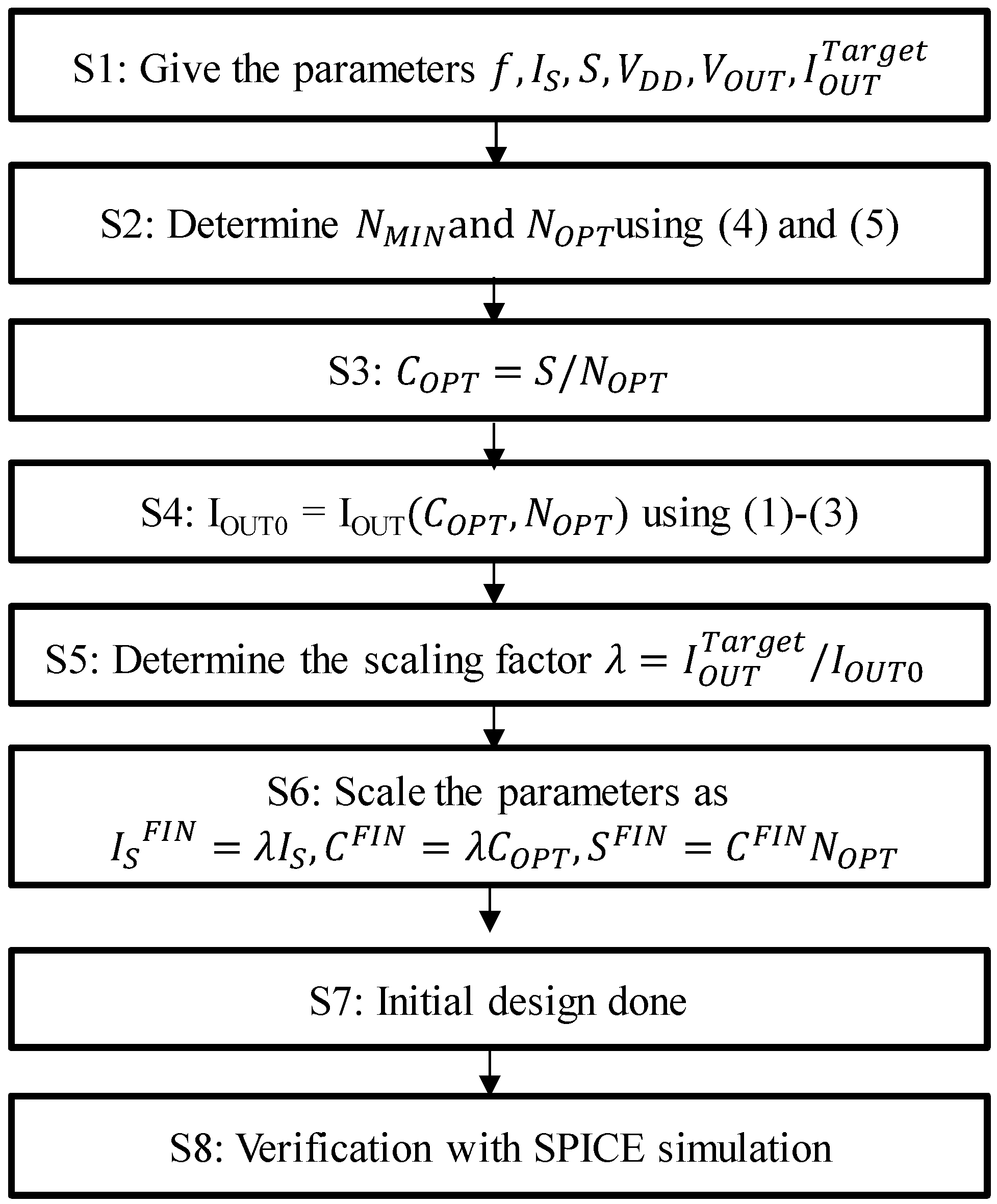

4. Design Flow of Clocked AC-DC Charge Pumps

5. Discussion

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Mitcheson, P.D.; Yeatman, E.M.; Rao, G.K.; Holmes, A.S.; Green, T.C. Energy Harvesting From Human and Machine Motion for Wireless Electronic Devices. Proc. IEEE 2008, 96, 1457–1486. [Google Scholar] [CrossRef]

- Manoli, Y. Energy harvesting from devices to systems. In Proceedings of the 2010 Proceedings of ESSCIRC, Sevilla, Spain, 14–16 September 2010; pp. 27–36. [Google Scholar]

- Chao, L.; Tsui, C.-Y.; Ki, W.-H. A Batteryless Vibration-based Energy Harvesting System for Ultra Low Power Ubiquitous Applications. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 1349–1352. [Google Scholar]

- Arakawa, Y.; Suzuki, Y.; Kasagi, N. Micro Seismic Power Generator Using Electret Polymer Film. Proc. PowerMEMS 2004, 187, 17. [Google Scholar]

- Ueno, T. Magnetostrictive vibrational power generator for battery-free IoT application. AIP Adv. 2019, 9, 035018. [Google Scholar] [CrossRef]

- Stanzione, S.; Van Liempd, C.; Van Schaijk, R.; Naito, Y.; Yazicioglu, R.F.; Van Hoof, C. A self-biased 5-to-60V input voltage and 25-to-1600µW integrated DC-DC buck converter with fully analog MPPT algorithm reaching up to 88% end-to-end efficiency. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2013; pp. 74–75. [Google Scholar] [CrossRef]

- Beeby, S.; Kazmierski, T.J. Energy Harvesting Systems: Principles, Modeling and Applications; Springer: Berlin/Heidelberg, Germany, 2010; Chapter 1. [Google Scholar]

- Rahimi, A.; Zorlu, O.; Külah, H.; Muhtaroglu, A. An interface circuit prototype for a vibration-based electromagnetic energy harvester. In Proceedings of the 2010 International Conference on Energy Aware Computing, Cairo, Egypt, 16–18 December 2010; pp. 1–4. [Google Scholar]

- Maurath, D.; Becker, P.F.; Spreemann, D.; Manoli, Y. Efficient Energy Harvesting With Electromagnetic Energy Transducers Using Active Low-Voltage Rectification and Maximum Power Point Tracking. IEEE J. Solid-State Circuits 2012, 47, 1369–1380. [Google Scholar] [CrossRef]

- Ulusan, H.; Gharehbaghi, K.; Zorlu, O.; Muhtaroglu, A.; Külah, H. A Fully Integrated and Battery-Free Interface for Low-Voltage Electromagnetic Energy Harvesters. IEEE Trans. Power Electron. 2014, 30, 3712–3719. [Google Scholar] [CrossRef]

- Wang, S.-W.; Ke, Y.-W.; Huang, P.-C.; Hsieh, P.-H. Electromagnetic Energy Harvester Interface Design for Wearable Applications. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 667–671. [Google Scholar] [CrossRef]

- Karthaus, U.; Fischer, M. Fully integrated passive uhf rfid transponder ic with 16.7-μ minimum rf input power. IEEE J. Solid-State Circuits 2003, 38, 1602–1608. [Google Scholar] [CrossRef]

- Papotto, G.; Carrara, F.; Palmisano, G. A 90-nm CMOS Threshold-Compensated RF Energy Harvester. IEEE J. Solid-State Circuits 2011, 46, 1985–1997. [Google Scholar] [CrossRef]

- Kawauchi, H.; Tanzawa, T. A clocked AC-DC voltage multiplier for increasing the power conversion efficiency in vibration energy harvesting. In Proceedings of the IEICE General Conference, Tokyo, Japan, 20–23 March 2018; Available online: http://hdl.handle.net/10297/00025812 (accessed on 20 March 2018).

- Kawauchi, H.; Tanzawa, T. A 2V 3.8µW Fully-Integrated Clocked AC-DC Charge Pump with 0.5 V 500 Ω Vibration Energy Harvester. In Proceedings of the 2019 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Bangkok, Thailand, 11–14 November 2019; pp. 329–332. [Google Scholar] [CrossRef]

- Shih, Y.; Otis, B.P. An Inductorless DC–DC Converter for Energy Harvesting With a 1.2-uW Bandgap-Referenced Output Controller. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 832–836. [Google Scholar] [CrossRef]

- Kim, J.; Kim, J.; Kim, C. A Regulated Charge Pump With a Low-Power Integrated Optimum Power Point Tracking Algorithm for Indoor Solar Energy Harvesting. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 802–806. [Google Scholar] [CrossRef]

- Peng, H.; Tang, N.; Yang, Y.; Heo, D. CMOS Startup Charge Pump with Body Bias and Backward Control for Energy Harvesting Step-Up Converters. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1618–1628. [Google Scholar] [CrossRef]

- Kim, J.; Mok, P.K.T.; Kim, C. A 0.15 V Input Energy Harvesting Charge Pump With Dynamic Body Biasing and Adaptive Dead-Time for Efficiency Improvement. IEEE J. Solid-State Circuits 2014, 50, 414–425. [Google Scholar] [CrossRef]

- Mondal, S.; Paily, R. An Efficient On-Chip Switched-Capacitor-Based Power Converter for a Microscale Energy Transducer. IEEE Trans. Circuits Syst. II Express Briefs 2015, 63, 254–258. [Google Scholar] [CrossRef]

- Liu, X.; Huang, L.; Ravichandran, K.; Sanchez-Sinencio, E. A Highly Efficient Reconfigurable Charge Pump Energy Harvester with Wide Harvesting Range and Two-Dimensional MPPT for Internet of Things. IEEE J. Solid-State Circuits 2016, 51, 1302–1312. [Google Scholar] [CrossRef]

- Goeppert, J.; Manoli, Y. Fully Integrated Startup at 70 mV of Boost Converters for Thermoelectric Energy Harvesting. IEEE J. Solid-State Circuits 2016, 51, 1716–1726. [Google Scholar] [CrossRef]

- Fuketa, H.; O’Uchi, S.-I.; Matsukawa, T. Fully Integrated, 100-mV Minimum Input Voltage Converter with Gate-Boosted Charge Pump Kick-Started by LC Oscillator for Energy Harvesting. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 392–396. [Google Scholar] [CrossRef]

- Tanzawa, T. An Analytical Model of Charge Pump DC-DC Voltage Multiplier Using Diodes. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 2017, 1137–1144. [Google Scholar] [CrossRef]

- Tanzawa, T. Design of DC-DC switched-capacitor voltage multiplier driven by DC energy transducer. In Proceedings of the 2014 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), Marseille, France, 7–10 December 2014; pp. 327–330. [Google Scholar]

- Tanzawa, T. An Optimum Design for Integrated Switched-Capacitor Dickson Charge Pump Multipliers with Area Power Balance. IEEE Trans. Power Electron. 2014, 29, 534–538. [Google Scholar] [CrossRef]

- Peters, C.; Kessling, O.; Henrici, F.; Ortmanns, M.; Manoli, Y. CMOS Integrated Highly Efficient Full Wave Rectifier. In Proceedings of the IEEE International Symposium on Circuits and System, New Orleans, LA, USA, 27–30 May 2007; pp. 2415–2418. [Google Scholar] [CrossRef]

- Haddad, P.-A.; Gosset, G.; Raskin, J.-P.; Flandre, D. Automated Design of a 13.56 MHz 19 µW Passive Rectifier With 72% Efficiency Under 10 µA load. IEEE J. Solid-state Circuits 2016, 51, 1290–1301. [Google Scholar] [CrossRef]

- Tokuda, S.; Tanzawa, T. Toward a Minimum-Operating-Voltage Design of DC-DC Charge Pump Circuits for Energy Harvesting. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Tanzawa, T. A Behavior Model of an On-Chip High Voltage Generator for Fast, System-Level Simulation. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2011, 20, 2351–2355. [Google Scholar] [CrossRef]

- Ye, J.; Tanzawa, T. An Optimum Circuit Design of clocked AC-DC charge pumps. In Proceedings of the IEICE General Conference, Higashihiroshima, Japan, 17–20 March 2020; Available online: http://hdl.handle.net/10297/00027066 (accessed on 17 March 2020).

- Levacq, D.; Liber, C.; Dessard, V.; Flandre, D. Composite ULP diode fabrication, modelling and applications in multi-Vth FD SOI CMOS technology. Solid-State Electron. 2004, 48, 1017–1025. [Google Scholar] [CrossRef]

| Design Parameters | Maximum | Minimum |

|---|---|---|

| f | 100 MHz | 100 kHz |

| VDD | 0.7 V | 0.5 V |

| VOUT | 3.5 V | 1.5 V |

| IS | 100 nA | 5 nA |

| S | 1 nF | 1 pF |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ye, J.; Tanzawa, T. An Optimum Design of Clocked AC-DC Charge Pump Circuits for Vibration Energy Harvesting. Electronics 2020, 9, 2031. https://doi.org/10.3390/electronics9122031

Ye J, Tanzawa T. An Optimum Design of Clocked AC-DC Charge Pump Circuits for Vibration Energy Harvesting. Electronics. 2020; 9(12):2031. https://doi.org/10.3390/electronics9122031

Chicago/Turabian StyleYe, Jinming, and Toru Tanzawa. 2020. "An Optimum Design of Clocked AC-DC Charge Pump Circuits for Vibration Energy Harvesting" Electronics 9, no. 12: 2031. https://doi.org/10.3390/electronics9122031

APA StyleYe, J., & Tanzawa, T. (2020). An Optimum Design of Clocked AC-DC Charge Pump Circuits for Vibration Energy Harvesting. Electronics, 9(12), 2031. https://doi.org/10.3390/electronics9122031