High-PSRR Wide-Range Supply-Independent CMOS Voltage Reference for Retinal Prosthetic Systems

Abstract

1. Introduction

2. Methods

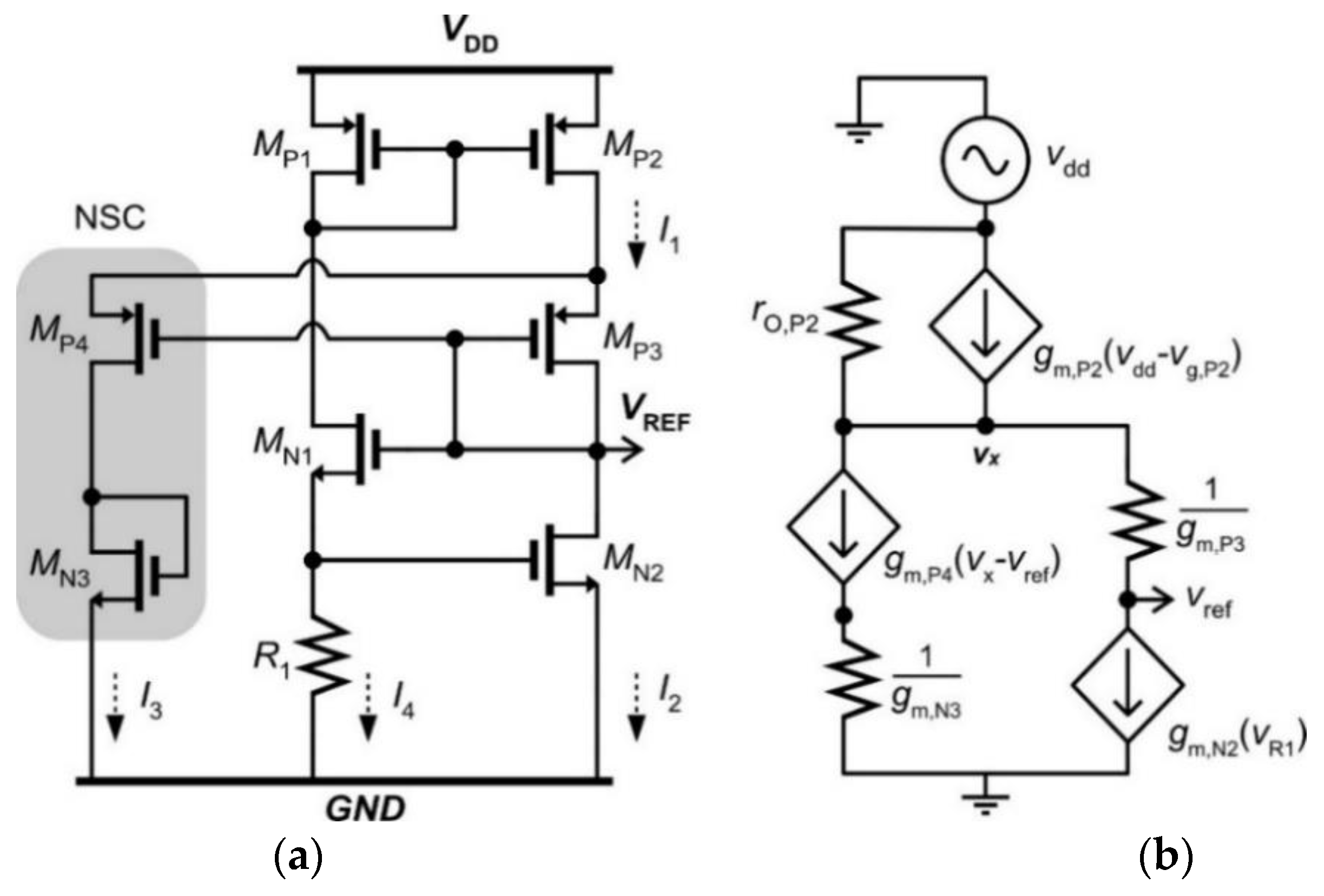

2.1. Static Analysis

2.2. Dynamic Analysis

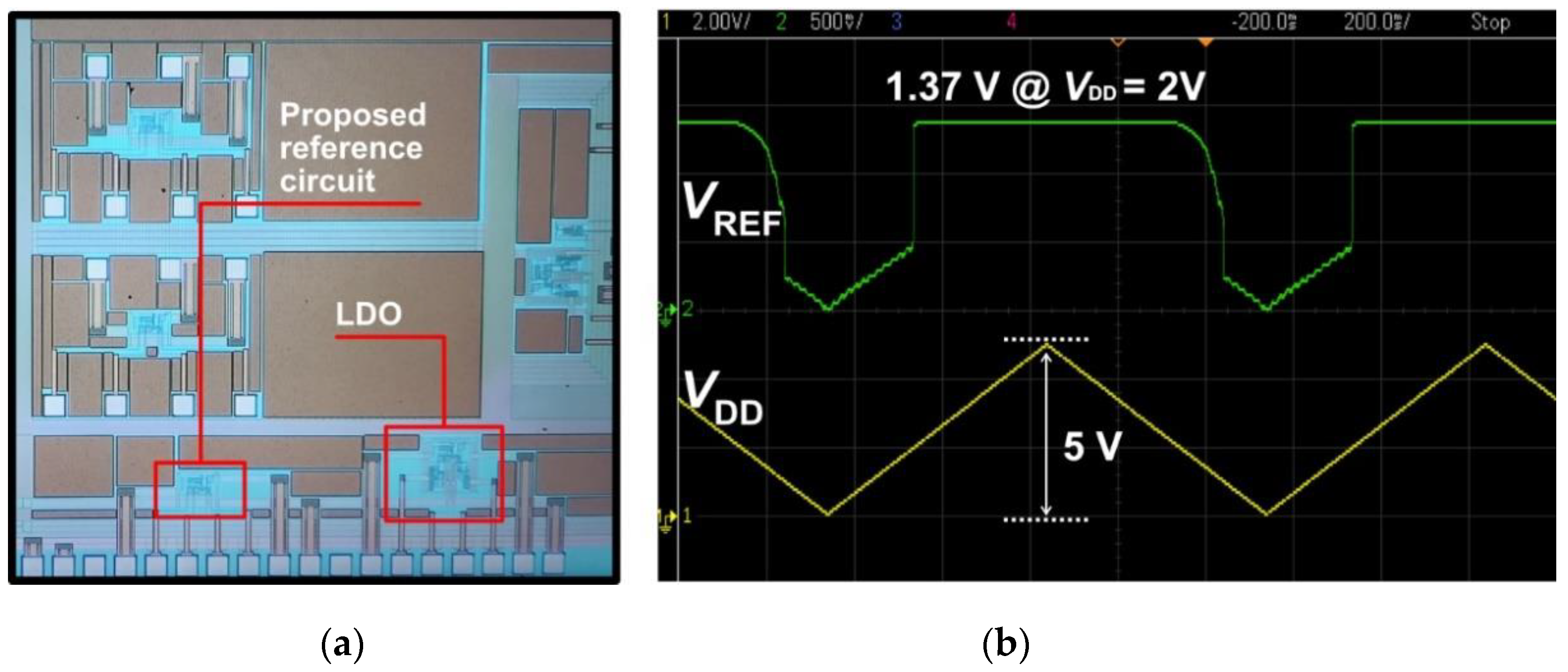

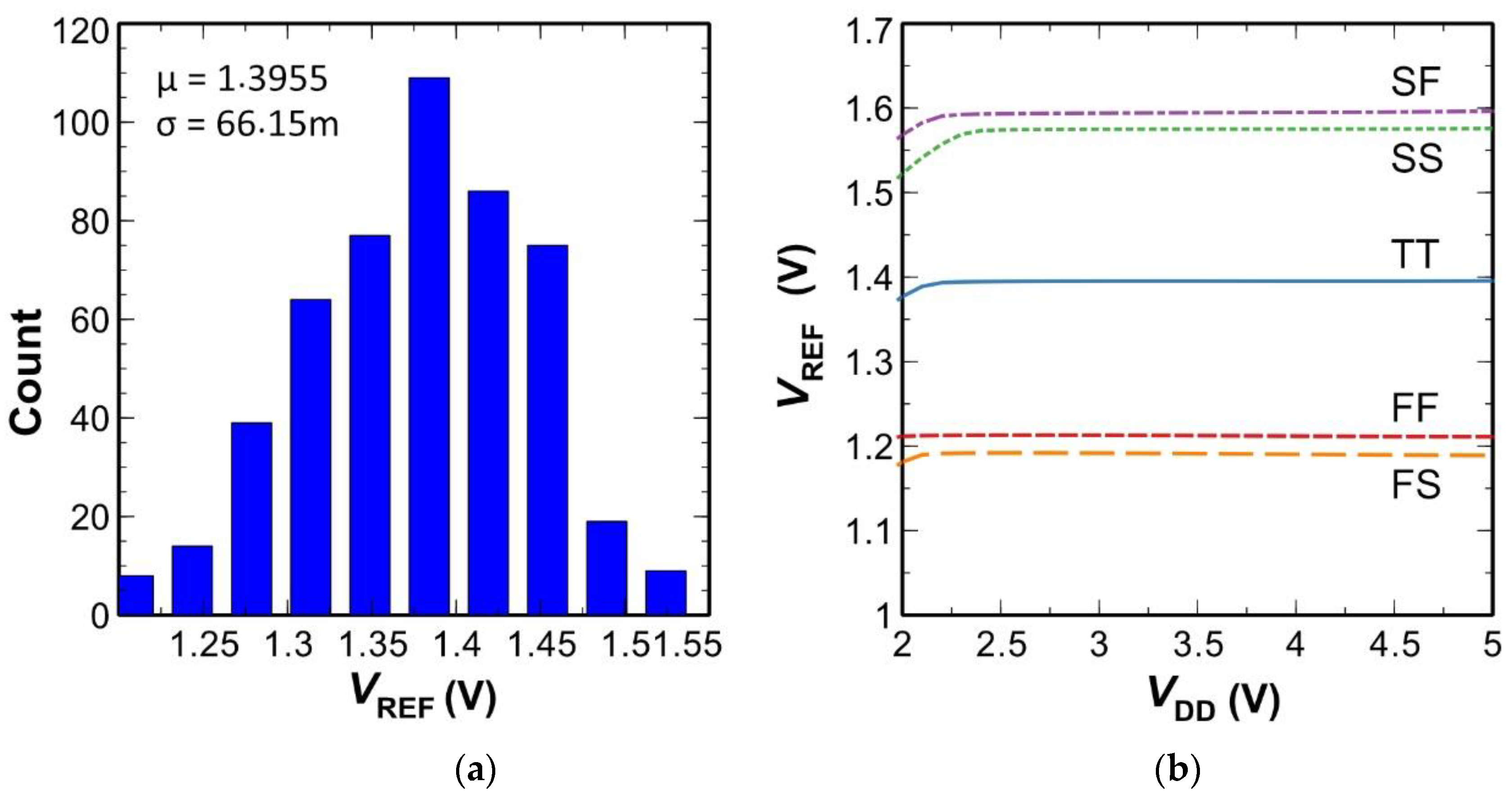

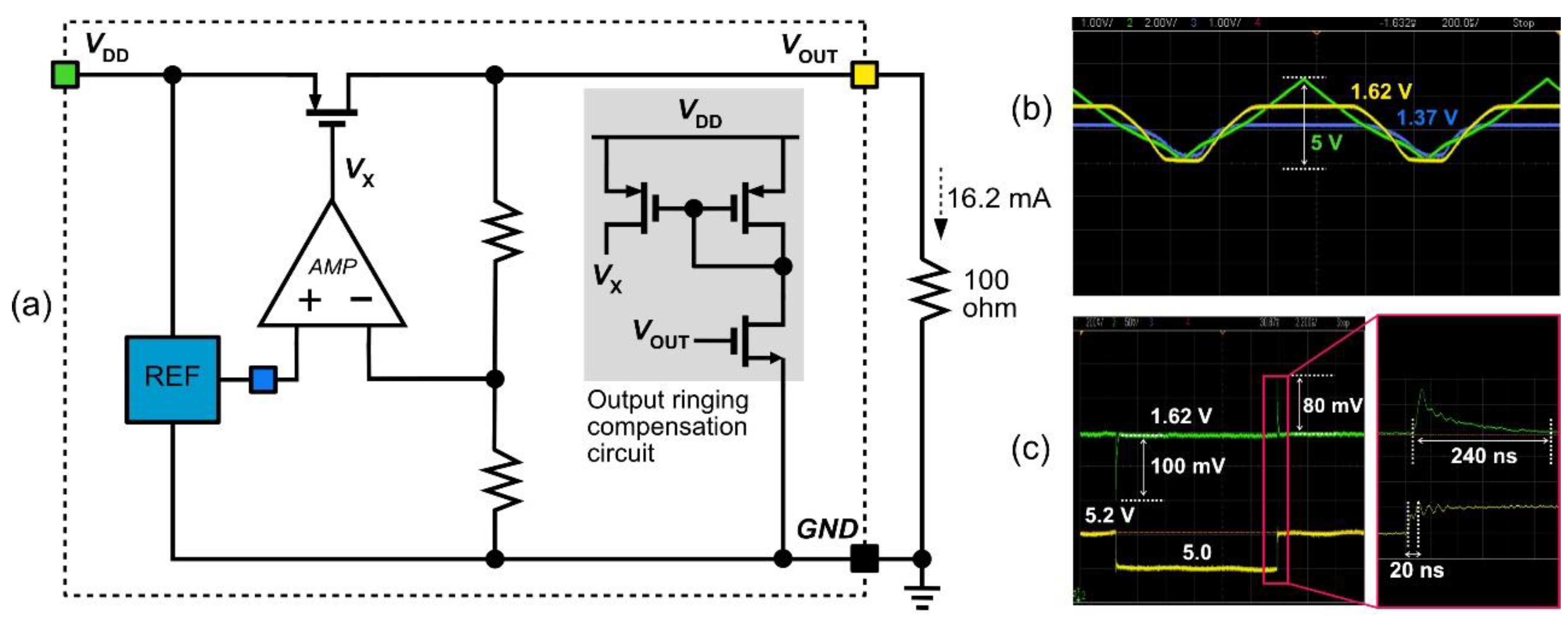

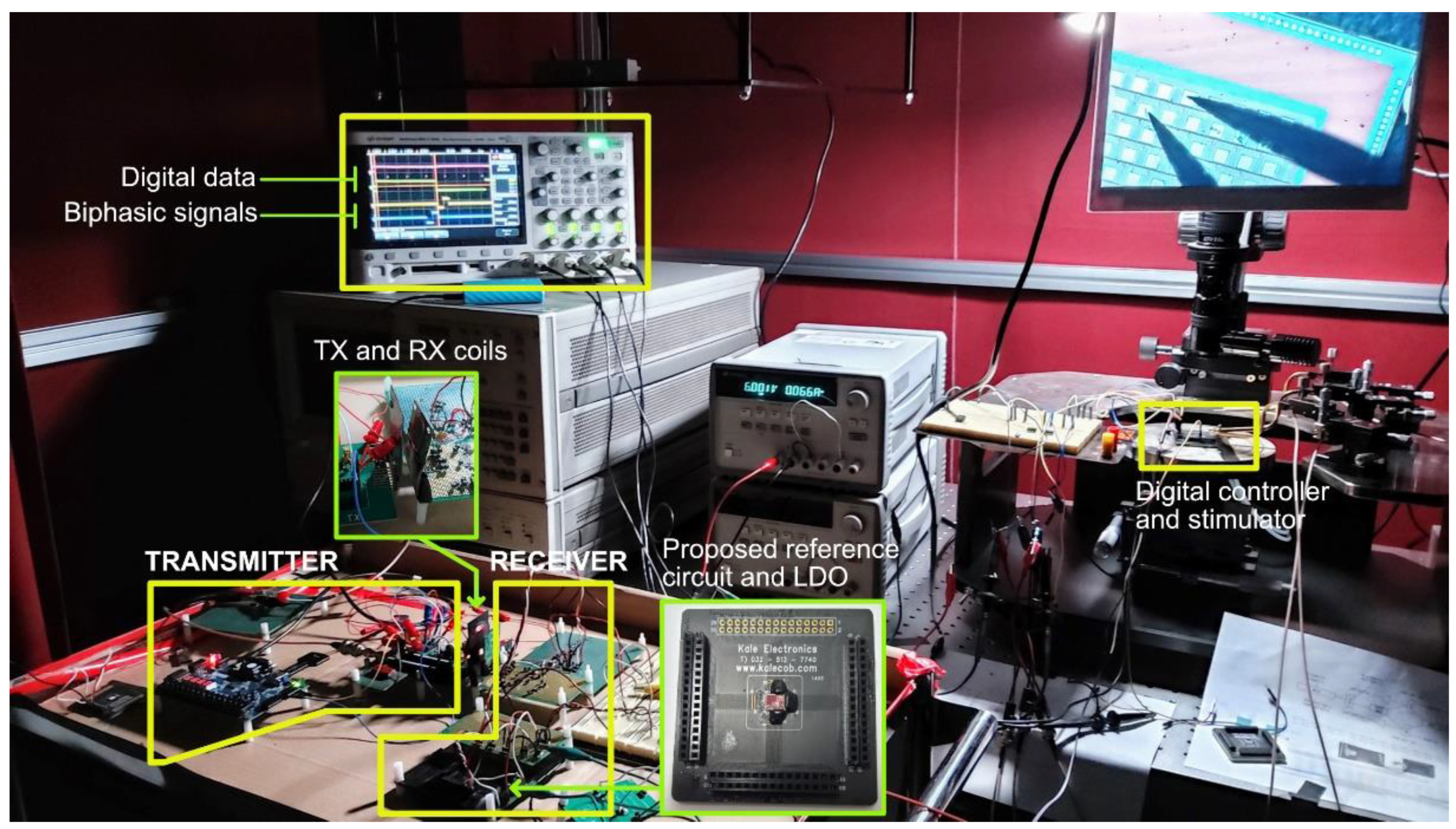

3. Simulation and Measurement Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Lee, B.; Kiani, M.; Ghovanloo, M. A Triple-Loop Inductive Power Transmission System for Biomedical Applications. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 138–148. [Google Scholar] [CrossRef] [PubMed]

- Jegadeesan, R.; Nag, S.; Agarwal, K.; Member, S. Enabling Wireless Powering and Telemetry for Peripheral Nerve Implants. IEEE J. Biomed. Health Inform. 2015, 19, 958–970. [Google Scholar] [CrossRef] [PubMed]

- Lo, Y.-K.; Chen, K.; Gad, P.; Liu, W. An On-Chip Multi-Voltage Power Converter with Leakage Current Prevention Using 0.18 um High-Voltage CMOS Process. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 163–174. [Google Scholar] [CrossRef] [PubMed]

- Ha, S.; Khraiche, M.L.; Akinin, A.; Jing, Y.; Damle, S.; Kuang, Y.; Bauchner, S.; Lo, Y.-H.; Freeman, W.R.; Silva, G.A.; et al. Towards high-resolution retinal prostheses with direct optical addressing and inductive telemetry. J. Neural Eng. 2016, 13, 056008. [Google Scholar] [CrossRef] [PubMed]

- Goetz, G.A.; Palanker, D.V. Electronic approaches to restoration of sight. Rep. Prog. Phys. 2016, 79, 096701. [Google Scholar] [CrossRef] [PubMed]

- Lin, T.-C.; Chang, H.-M.; Hsu, C.-C.; Hung, K.-H.; Chen, Y.-T.; Chen, S.-Y.; Chen, S.-J. Retinal prostheses in degenerative retinal diseases. J. Chin. Med. Assoc. 2015, 78, 501–505. [Google Scholar] [CrossRef] [PubMed]

- Wu, C.-Y.; Tseng, C.-K.; Liao, J.-H.; Chiao, C.-C.; Chu, F.-L.; Tsai, Y.-C.; Ohta, J.; Noda, T. CMOS 256-Pixel/480-Pixel Photovoltaic-Powered Subretinal Prosthetic Chips with Wide Image Dynamic Range and Bi/Four-Directional Sharing Electrodes and Their Ex Vivo Experimental Validations With Mice. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3273–3283. [Google Scholar] [CrossRef]

- Kuo, P.H.; Wong, O.-Y.; Tzeng, C.-K.; Wu, P.-W.; Chiao, C.C.; Chen, P.-H.; Tsai, Y.-C.; Chu, F.-L.; Ohta, J.; Tokuda, T.; et al. Improved Charge Pump Design and Ex Vivo Experimental Validation of CMOS 256-Pixel Photovoltaic-Powered Subretinal Prosthetic Chip. IEEE Trans. Biomed. Eng. 2020, 67, 1490–1504. [Google Scholar] [CrossRef] [PubMed]

- Özmert, E.; Arslan, U. Retinal Prostheses and Artificial Vision. Turk. J. Ophthalmol. 2019, 49, 213–219. [Google Scholar] [CrossRef] [PubMed]

- Kang, H.; Abbasi, W.H.; Kim, S.-W.; Kim, J. Fully Integrated Light-Sensing Stimulator Design for Subretinal Implants. Sensors 2019, 19, 536. [Google Scholar] [CrossRef] [PubMed]

- Kim, J.; Basham, E.; Pedrotti, K.D. Geometry-based optimization of radio-frequency coils for powering neuroprosthetic implants. Med. Biol. Eng. Comput. 2013, 123–134. [Google Scholar] [CrossRef] [PubMed]

- Zawawi, R.B.A.; Abbasi, W.H.; Kim, S.-H.; Choi, H.; Kim, J. Wide-Supply-Voltage-Range CMOS Bandgap Reference for In Vivo Wireless Power Telemetry. Energies 2020, 13, 2986. [Google Scholar] [CrossRef]

- Gray, P.; Meyer, R. Analysis and Design of Analog Integrated Circuits, 5th ed.; John Wiley and Sons: Hoboken, NJ, USA, 2010. [Google Scholar]

- Zhou, Z.-K.; Shi, Y.; Wang, Y.; Li, N.; Xiao, Z.; Wang, Y.; Liu, X.; Wang, Z.; Zhang, B. A Resistorless High-Precision Compensated CMOS Bandgap Voltage Reference. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 428–437. [Google Scholar] [CrossRef]

- Chi-Wa, U.; Zeng, W.-L.; Law, M.-K.; Lam, C.-S.; Martins, R.P. A 0.5-V Supply, 36 nW Bandgap Reference With 42 ppm/°C Average Temperature Coefficient Within −40 °C to 120 °C. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3656–3669. [Google Scholar]

- Kim, M.; Cho, S.H. A 0.0082-mm², 192-nW Single BJT Branch Bandgap Reference in 0.18-μm CMOS. IEEE Solid State Circuits Lett. 2020, 3, 426–429. [Google Scholar]

- Sodagar, A.; Najafi, K. A wide-range supply-independent CMOS voltage reference for telemetry-powering applications. In Proceedings of the 9th International Conference on Electronics, Circuits and Systems, Dubrovnik, Croatia, 15–18 September 2002; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2003; Volume 1, pp. 401–404. [Google Scholar]

| Component | Parameter | Component | Parameter |

|---|---|---|---|

| MP1, MP2 | W = 4 µm, L = 1 µm, m = 50 | MN2 | W = 25 µm, L = 3 µm, m = 4 |

| MP3 | W = 1.15 µm, L = 1 µm, m = 1 | MN3 | W = 4 µm, L = 1 µm, m = 20 |

| MP4 | W = 4 µm, L = 1 µm, m = 9 | R1 | 70 kΩ |

| MN1 | W = 4 µm, L = 1 µm, m = 10 |

| Parameter | [14] | [15] | [16] | [17] | This Work |

|---|---|---|---|---|---|

| Supply voltage range (V) | 2 to 5 | 0.5 to 1 | 1.3 to 1.8 | 2.6 to 12 (2.4 to 20) * | 2.1 to 5 (2.4 to 30) * |

| Reference output voltage (V) | 1.14055 | 0.495 | 1.17 | 1.6 | 1.37 |

| Line regulation (mV/V) | 2 | 3.2 | 0.35 | 0.957 (0.511) * | 3.45 (0.39) * |

| PSRR (dB) | −61 | −50 | −52 | −60 (−59.2) * | −93 (−112) * |

| Chip Area (mm2) | 0.0396 | 0.0522 | 0.082 | - | 0.0131 |

| Technology (µm) | 0.35 | 0.065 | 0.18 | 1.6 | 0.35 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zawawi, R.B.A.; Choi, H.; Kim, J. High-PSRR Wide-Range Supply-Independent CMOS Voltage Reference for Retinal Prosthetic Systems. Electronics 2020, 9, 2028. https://doi.org/10.3390/electronics9122028

Zawawi RBA, Choi H, Kim J. High-PSRR Wide-Range Supply-Independent CMOS Voltage Reference for Retinal Prosthetic Systems. Electronics. 2020; 9(12):2028. https://doi.org/10.3390/electronics9122028

Chicago/Turabian StyleZawawi, Ruhaifi Bin Abdullah, Hojong Choi, and Jungsuk Kim. 2020. "High-PSRR Wide-Range Supply-Independent CMOS Voltage Reference for Retinal Prosthetic Systems" Electronics 9, no. 12: 2028. https://doi.org/10.3390/electronics9122028

APA StyleZawawi, R. B. A., Choi, H., & Kim, J. (2020). High-PSRR Wide-Range Supply-Independent CMOS Voltage Reference for Retinal Prosthetic Systems. Electronics, 9(12), 2028. https://doi.org/10.3390/electronics9122028