An Experimental Study of Building Blocks of Lattice-Based NIST Post-Quantum Cryptographic Algorithms

Abstract

1. Introduction

1.1. Existing Implementations of NIST PQC Algorithms

1.2. Limitations in the Existing Implementations of NIST PQC Algorithms

- In [19,20,23,24], an HLS approach has been used to evaluate area and power constraints while abstracting their essential building blocks and functions (e.g., memory instances, arithmetic operators, logical operators, hash functions, etc.). While HLS allows for a fast architectural evaluation, we opt not to make use of HLS in our study since HLS still is more convenient for FPGA-based implementations where BRAMs can be easily inferred. In ASICs, this method still presents some enormous challenges as the tools have no direct interface to proprietary memory compilers.

- The performance of a crypto-system often depends on the performance of the utilized multiplier. The functional C/C++ routines of multipliers written in reference implementations of the selected NIST PQC algorithms, when submitted to an HLS tool, yield an architecture where the input and output parameters are uint16_t/uint32_t/uint64_t [7,8,9,10,11,12,13,14,15,16,17,18]. Such a solution might not be optimal in terms of latency, even if it brings a decrease in area and power [19,20,23,24]. To fully understand the design space, actual input and output operand sizes of arithmetic operators have to be identified.

1.3. Our Contributions

- To identify the essential building blocks, we have defined a set of rules (see Section 2) which allows us to fairly assess each reference implementation to (1) estimate the required memory sizes, (2) identify large arithmetic operators (i.e., multipliers), and (3) to identify the utilized hashing functions.

- Area and power values for read-only memory (ROM) and random-access memory (RAM) instances are calculated using specific memory compilers provided by a partner foundry. Naturally, ROMs allow only read operations while RAMs allow both read and write operations. The target technology is 65 nm bulk CMOS with a “low-power” flavor (details are provided in Section 3.1 and Section 4.1).

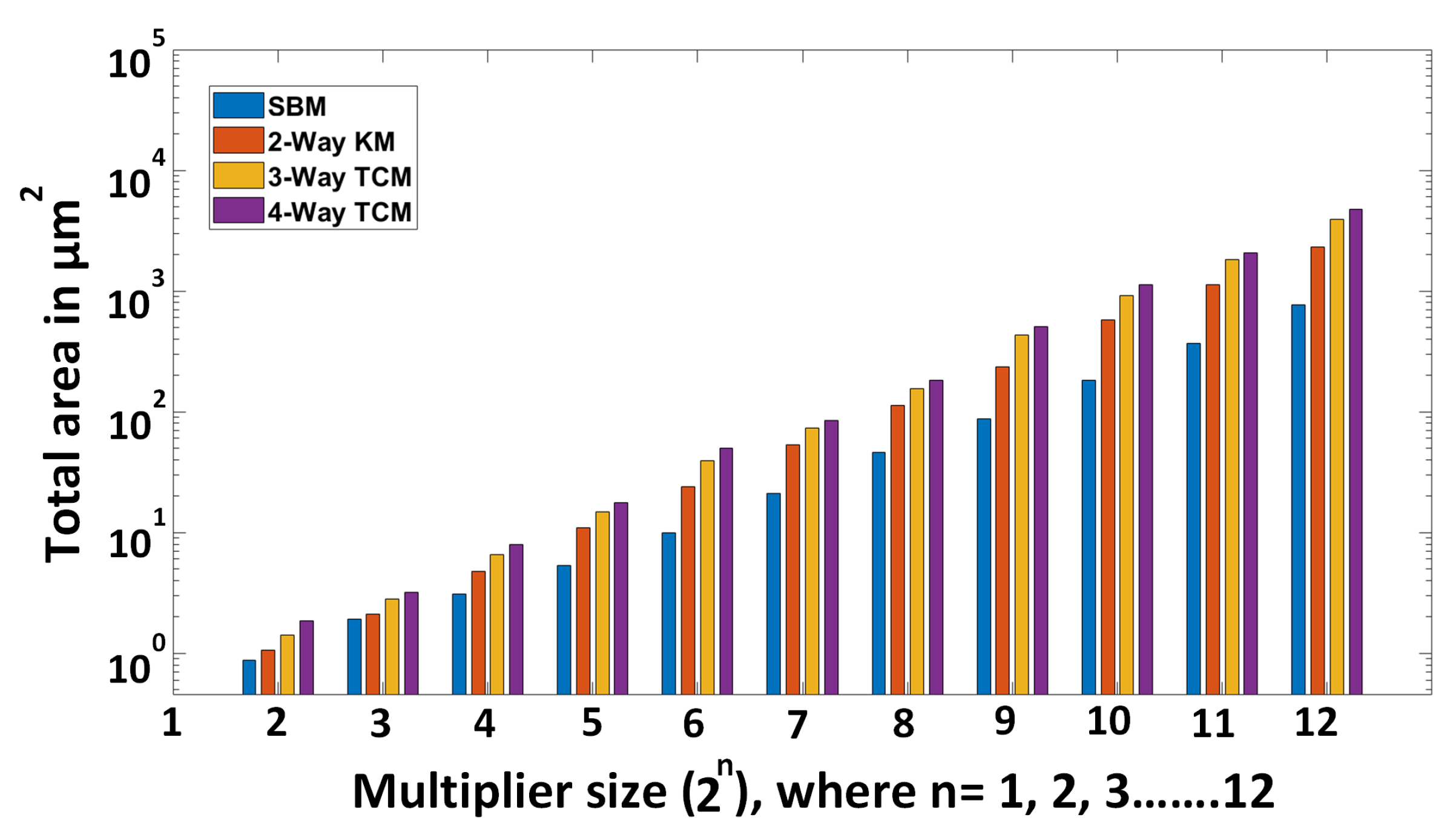

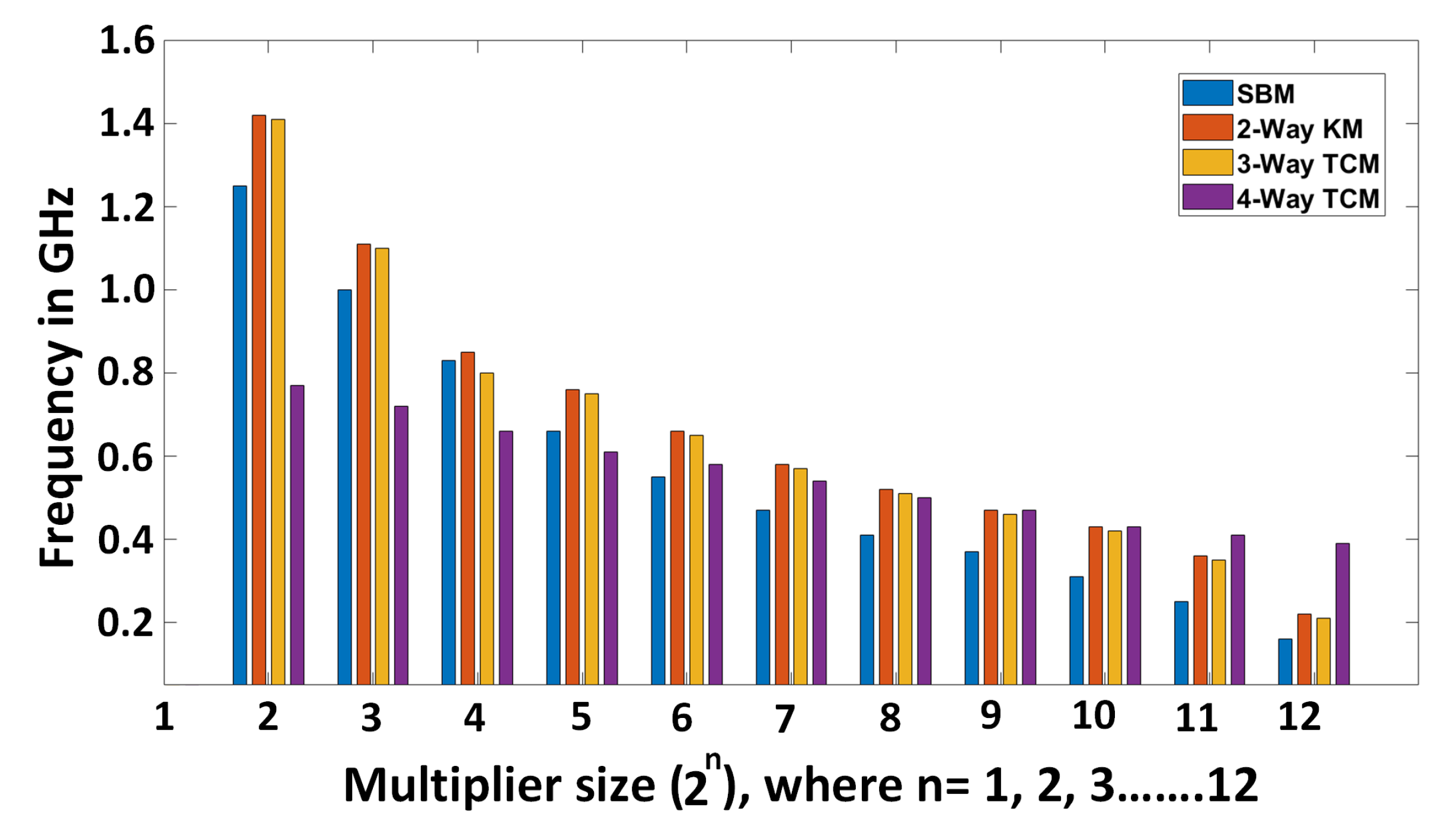

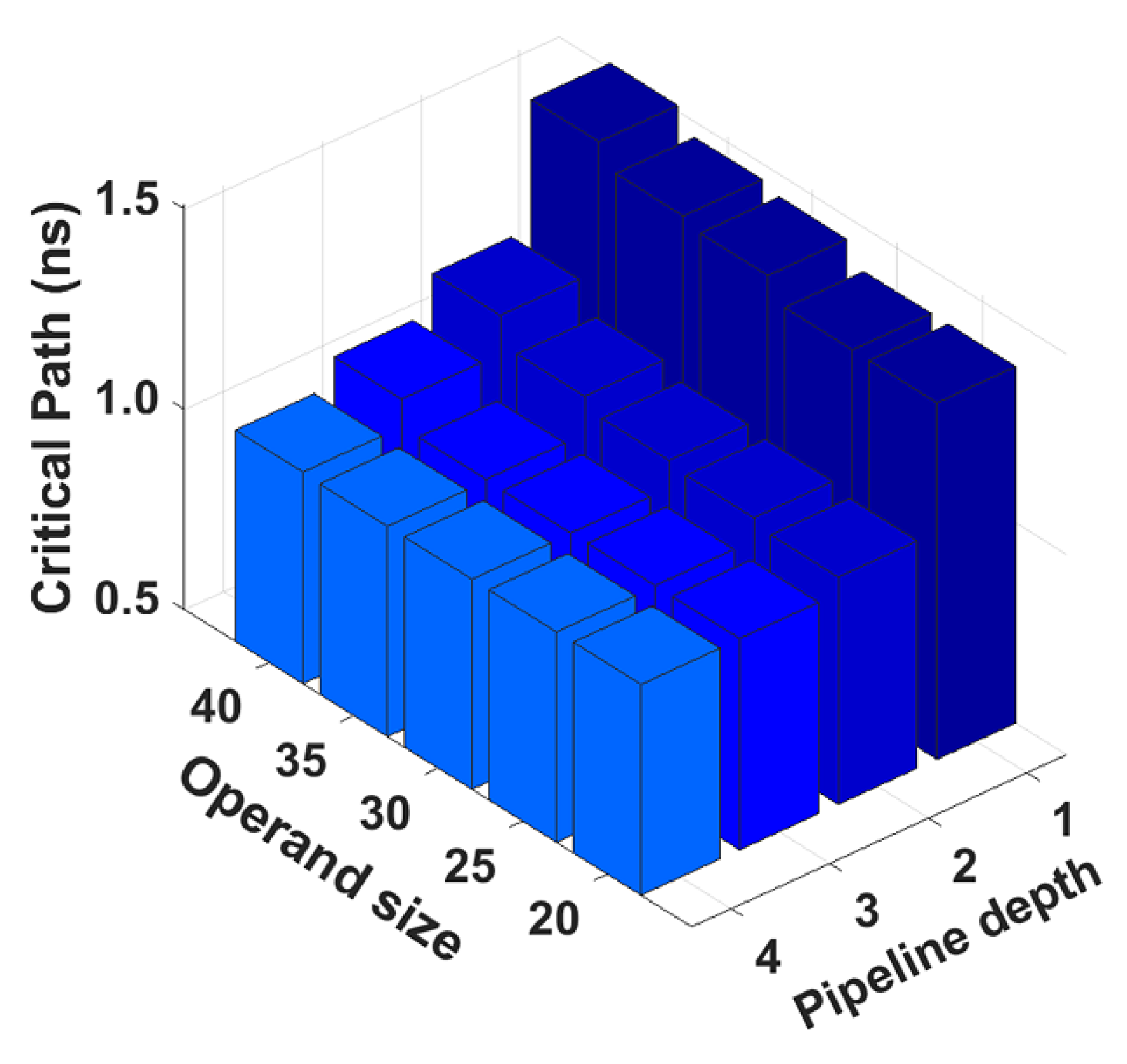

- Amongst the identified arithmetic operators, we focus on the multipliers as they are often large and a bottleneck for the performance. Therefore, to calculate the actual hardware costs, we have developed Verilog RTL models for the multipliers (Schoolbook, 2-Way Karatsuba, 3-Way Toom-Cook, and 4-Way Toom-Cook) and synthesized several variants of them using a commercial standard cell library (details are provided in Section 3.2 and Section 4.2). Furthermore, we have shown performance trends for the aforementioned multiplier architectures over different input operand lengths ( to ) in terms of power, area, and clock frequency (see Appendix A).

- We have developed code in Verilog RTL for the identified hash functions (total = 10) according to their required input and output lengths (details are given in Section 3.3 and Section 4.3).

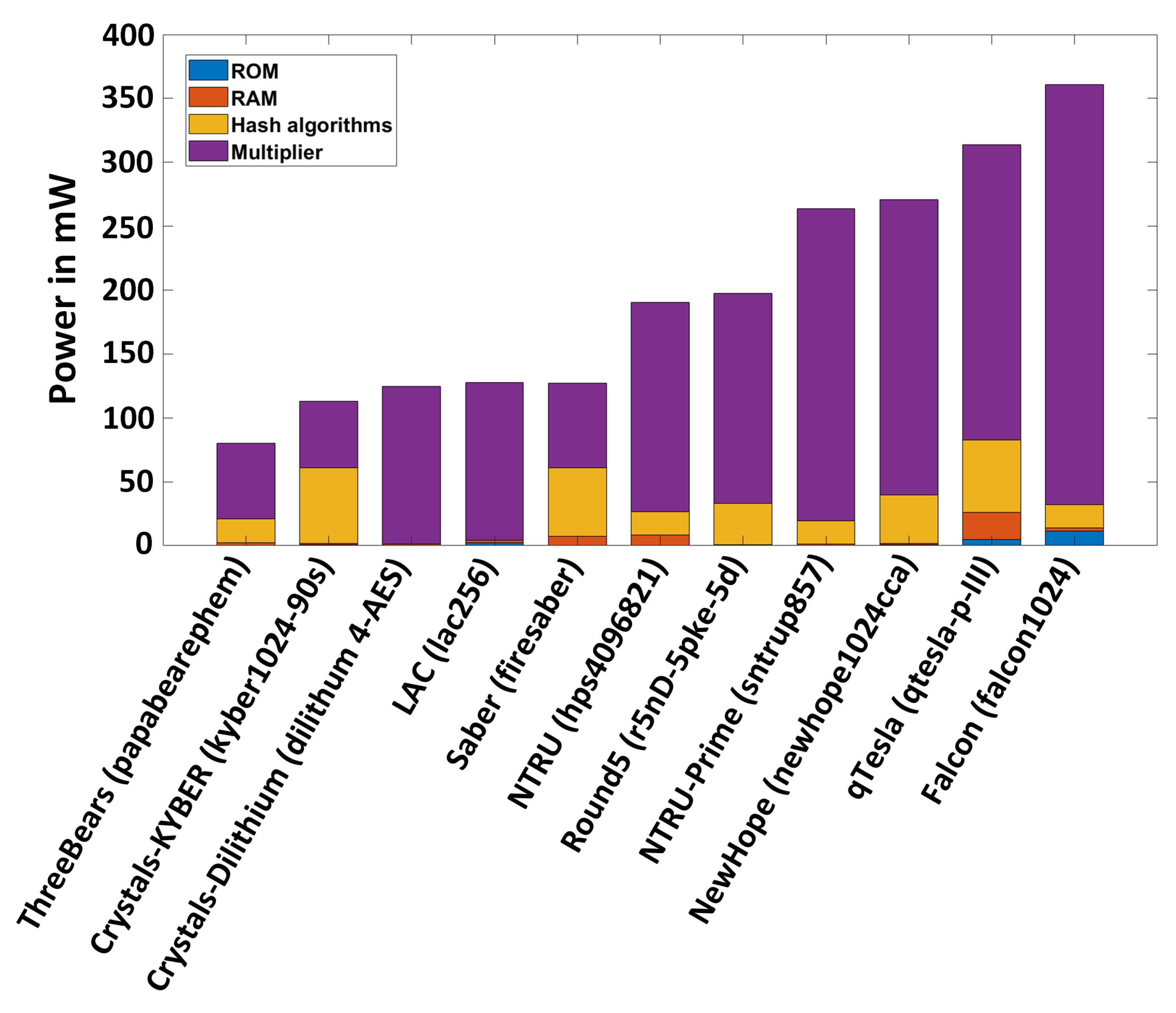

- Finally, we put all the building blocks together and compile results for the combined memory/logic footprints of each studied algorithm. The motivation for this effort is not to serve as a benchmarking measure. Instead, we provide this comparison to demonstrate that the block-by-block deconstruction has merit.

2. Principles Definition

2.1. Inclusion-Exclusion Principles

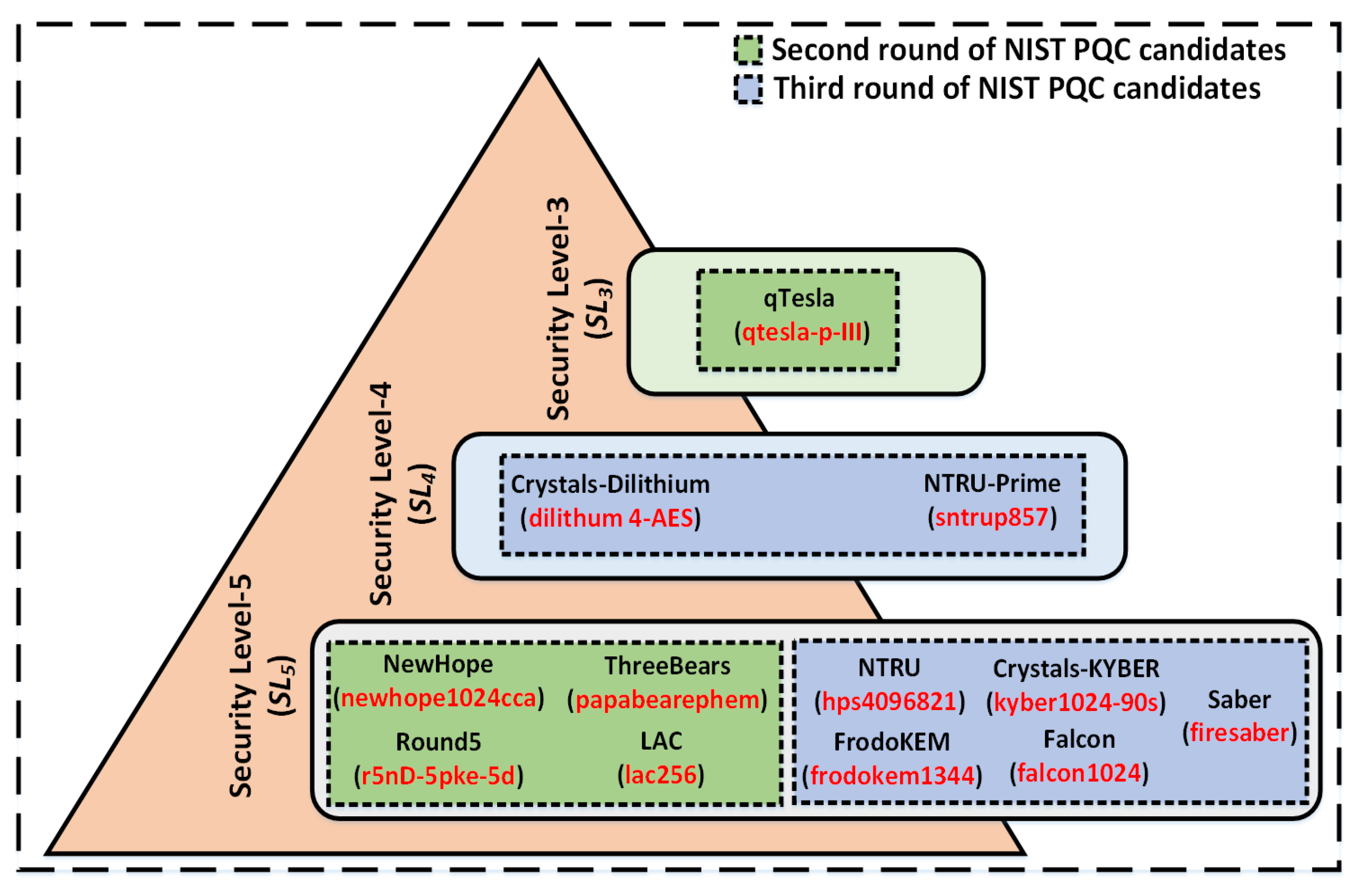

- Participation in the NIST competition. Include only algorithms that were considered on the NIST competition for standardization.

- Underlying cryptographic primitive. Include only algorithms that are built on the security problems of lattice-based cryptography.

- Security levels. For each studied algorithm, we consider only the parameters that determine the highest security level.

- Purpose of the algorithm. For each particular algorithm, there might be a number of implementations, either for encryption/decryption or key encapsulations/establishments. We opt not to include all these as they serve inherently different purposes. Instead, we consider only the encryption/decryption implementations.

2.2. Selection of Algorithms

2.3. Calculation of Memory and Operand Sizes

3. Assessment of Building Blocks of the Selected NIST PQC Candidates

3.1. Memory Estimations according to the Defined Criteria

3.2. Common Arithmetic Operators and Operand Sizes

3.3. Hashing Algorithms

4. Implementing Building Blocks in ASIC

4.1. Memory Characteristics

4.2. Implementation of Identified Multipliers

4.3. Implementation of Identified Hash Algorithms

5. Evaluation of NIST PQC Algorithms as Hardware Accelerators

5.1. Comparison to State-of-the-Art Implementations

5.2. Limitations of this Work

- Table 2 lists many of the identified arithmetic operators, but our analysis focuses on multiplication as we consider it to be more challenging than other operations. This is not enough to generate a functional crypto accelerator, but it ought to be enough to capture the characteristics of it. There are various other operators, including transformations from one domain to another, that are required for a complete implementation of a lattice-based crypto accelerator.

- For each particular algorithm, there is a number of reference models that target different security levels. For each studied algorithm, we consider only the reference model with the highest security level. This approach might be overkill for several applications that would otherwise be satisfied with an AES-128 equivalent level of security.

- Results for area and power are collected after logic synthesis. However, an accelerator still has to go through physical synthesis, where many additional cells are added and routing resources have to be accounted for.

- We make assumptions based on reference implementations that were submitted to NIST for standardization. As the name implies, these are reference implementations and may not be optimized for the sake of readability.

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Appendix A. Area, Power, and Frequency Trends for Different Multipliers

Appendix A.1. SBM, 2-Way KM, 3-Way, and 4-Way TCM Multipliers

Appendix A.2. NTT Multiplier

Appendix A.3. Summary of the Multipliers Trend

References

- Shor, P.W. Polynomial-time algorithms for prime factorization and discrete logarithms on a quantum computer. SIAM J. Comput. 1999, 26, 1484–1509. [Google Scholar] [CrossRef]

- Moody, D.; Alagic, G.; Apon, D.C.; Cooper, D.A.; Dang, Q.H.; Kelsey, J.M.; Liu, Y.K.; Miller, C.A.; Peralta, R.C.; Perlner, R.A.; et al. Status Report on the Second Round of the NIST Post-Quantum Cryptography Standardization Process; NIST Interagency/Internal Report (NISTIR)—8309; NIST Interagency: Gaithersburg, MD, USA, 2020.

- NIST. Post-Quantum Cryptography, Round 2 Submissions. 2020. Available online: https://csrc.nist.gov/projects/post-quantum-cryptography/round-2-submissions (accessed on 20 April 2020).

- Chuang, Y.; Fan, C.; Tseng, Y. An Efficient Algorithm for the Shortest Vector Problem. IEEE Access 2018, 6, 61478–61487. [Google Scholar] [CrossRef]

- Khalid, A.; Oder, T.; Valencia, F.; O’ Neill, M.; Güneysu, T.; Regazzoni, F. Physical Protection of Lattice-Based Cryptography: Challenges and Solutions. In Proceedings of the 2018 on Great Lakes Symposium on VLSI; GLSVLSI ’18; Association for Computing Machinery: New York, NY, USA, 2018; pp. 365–370. [Google Scholar] [CrossRef]

- Alwen, J.; Krenn, S.; Pietrzak, K.; Wichs, D. Learning with Rounding, Revisited. In Advances in Cryptology—CRYPTO 2013; Canetti, R., Garay, J.A., Eds.; Springer: Berlin/Heidelberg, Germany, 2013; pp. 57–74. [Google Scholar]

- Alkim, E.; Bos, J.W.; Ducas, L.; Longa, P.; Mironov, I.; Naehrig, M.; Nikolaenko, V.; Peikert, C.; Raghunathan, A.; Stebila, D.; et al. FrodoKEM Learning with Errors Key Encapsulation Algorithm. 2020. Available online: https://frodokem.org/files/FrodoKEM-specification-20200930.pdf (accessed on 18 April 2020).

- Alkim, E.; Avanzi, R.; Bos, J.; Ducas, L.; de la Piedra, A.; Pöppelmann, T.; Schwabe, P.; Stebila, D.; Albrecht, M.R.; Orsini, E.; et al. NewHope. 2020. Available online: https://newhopecrypto.org (accessed on 12 May 2020).

- Avanzi, R.; Bos, J.; Ducas, L.; Kiltz, E.; Lepoint, T.; Lyubashevsky, V.; Schanck, J.M.; Schwabe, P.; Seiler, G.; Stehle, D. CRYSTALS-KYBER. 2020. Available online: https://pq-crystals.org (accessed on 11 April 2020).

- Hamburg, M. Post-Quantum Cryptography Proposal: ThreeBears. 2020. Available online: https://sourceforge.net/projects/threebears/ (accessed on 13 March 2020).

- Lu, X.; Liu, Y.; Jia, D.; Xue, H.; He, J.; Zhang, Z.; Liu, Z.; Yang, H.; Li, B.; Wang, K. LAC: Practical Ring-LWE Based Public-KeyEncryption with Byte-Level Modulus. Available online: https://eprint.iacr.org/2018/1009.pdf (accessed on 9 March 2020).

- Chen, C.; Danba, O.; Hoffstein, J.; Hülsing, A.; Rijneveld, J.; Saito, T.; Schanck, J.M.; Schwabe, P.; Whyte, W.; Xagawa, K.; et al. NTRU. 2020. Available online: https://ntru.org (accessed on 14 May 2020).

- Akleylek, S.; Alkim, E.; Bindel, N.; Buchmann, J.; Eaton, E.; Gutoski, G.; Krämer, J.; Longa, P.; Polat, H.; Ricardini, J.E.; et al. Submission to NIST’s Post-Quantum project (2nd Round): Lattice-Based Digital Signature Scheme qTESLA. 2020. Available online: https://qtesla.org/wp-content/uploads/2020/04/qTESLA_round2_14.04.2020.pdf (accessed on 29 March 2020).

- Fouque, P.A.; Hoffstein, J.; Kirchner, P.; Lyubashevsky, V.; Pornin, T.; Prest, T.; Ricosset, T.; Seiler, G.; Whyte, W.; Zhang, Z. Falcon: Fast-Fourier Lattice-Based Compact Signatures over NTRU Specifications v1.1. 2020. Available online: https://falcon-sign.info (accessed on 14 April 2020).

- Bernstein, D.J.; Chuengsatiansup, C.; Lange, T.; van Vredendaal, C. NTRU Prime: Round 2–20190330. 2020. Available online: https://ntruprime.cr.yp.to (accessed on 4 May 2020).

- Baan, H.; Bhattacharya, S.; Fluhrer, S.; Garcia-Morchon, O.; Laarhoven, T.; Player, R.; Rietman, R.; Saarinen, M.J.O.; Tolhuizen, L.; Torre-Arce, J.L.; et al. Round5: KEM and PKE Based on (Ring) Learning with Rounding. 2020. Available online: https://round5.org (accessed on 8 April 2020).

- D’Anvers, J.P.; Karmakar, A.; Roy, S.S.; Vercauteren, F. SABER: Mod-LWR Based KEM (Round 2 Submission). 2020. Available online: https://www.esat.kuleuven.be/cosic/pqcrypto/saber/ (accessed on 7 March 2020).

- Ducas, L.; Kiltz, E.; Lepoint, T.; Lyubashevsky, V.; Schwabe, P.; Seiler, G.; Stehlé, D. CRSTALS-Dilithium. 2019. Available online: https://tches.iacr.org/index.php/TCHES/article/view/839 (accessed on 10 February 2020).

- Soni, D.; Basu, K.; Nabeel, M.; Karri, R. A hardware evaluation study of NIST Post-quantum cryptographic signature schemes. In Proceedings of the Second PQC Standardization Conference, Santa Barbara, CA, USA, 22–24 August 2019; pp. 1–4. [Google Scholar]

- Farahmand, F.; Dang, V.B.; Andrzejczak, M.; Gaj, K. Implementing and benchmarking seven round 2 lattice-based key encapsulation mechanisms using a software/hardware codesign approach. In Proceedings of the Second PQC Standardization Conference, Santa Barbara, CA, USA, 22–24 August 2019; pp. 1–36. [Google Scholar]

- Wang, W.; Tian, S.; Jungk, B.; Bindel, N.; Longa, P.; Szefer, J. Parameterized Hardware Accelerators for Lattice-Based Cryptography and Their Application to the HW/SW Co-Design of qTESLA. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2020, 3, 123–151. [Google Scholar]

- Zhang, N.; Yang, B.; Chen, C.; Yin, S.; Wei, S.; Liu, L. Highly Efficient Architecture of NewHope-NIST on FPGA using Low-Complexity NTT/INTT. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2020, 2, 49–72. [Google Scholar] [CrossRef]

- Basu, K.; Soni, D.; Nabeel, M.; Karri, R. NIST Post-Quantum Cryptography- A Hardware Evaluation Study. Cryptology ePrint Archive, Report 2019/047. 2019. Available online: https://eprint.iacr.org/2019/047 (accessed on 27 January 2020).

- Soni, D.; Nabeel, M.; Basu, K.; Karri, R. Power, Area, Speed, and Security (PASS) Trade-Offs of NIST PQC Signature Candidates Using a C to ASIC Design Flow. In Proceedings of the 2019 IEEE 37th International Conference on Computer Design (ICCD), Abu Dhabi, UAE, 17–20 November 2019; pp. 337–340. [Google Scholar]

- Banerjee, U.; Ukyab, T.S.; Chandrakasan, A.P. Sapphire: A Configurable Crypto-Processor for Post-Quantum Lattice-based Protocols. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2019, 4, 17–61. [Google Scholar] [CrossRef]

- Xin, G.; Han, J.; Yin, T.; Zhou, Y.; Yang, J.; Cheng, X.; Zeng, X. VPQC: A Domain-Specific Vector Processor for Post-Quantum Cryptography Based on RISC-V Architecture. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 2672–2684. [Google Scholar] [CrossRef]

- Strömbergson, J. A Verilog Implementation of the Symmetric Block Cipher AES (NIST FIPS 197). Available online: https://github.com/secworks/aes (accessed on 5 March 2020).

- Liu, W.; Fan, S.; Khalid, A.; Rafferty, C.; O’Neill, M. Optimized Schoolbook Polynomial Multiplication for Compact Lattice-Based Cryptography on FPGA. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 2459–2463. [Google Scholar] [CrossRef]

- Kashif, M.; Cicek, I.; Imran, M. A Hardware Efficient Elliptic Curve Accelerator for FPGA Based Cryptographic Applications. In Proceedings of the 2019 11th International Conference on Electrical and Electronics Engineering (ELECO), Bursa, Turkey, 28–30 November 2019; pp. 362–366. [Google Scholar]

- Bodrato, M. Towards Optimal Toom-Cook Multiplication for Univariate and Multivariate Polynomials in Characteristic 2 and 0. In Arithmetic of Finite Fields; Carlet, C., Sunar, B., Eds.; Springer: Berlin/Heidelberg, Germany, 2007; pp. 116–133. [Google Scholar]

- Longa, P.; Naehrig, M. Speeding up the Number Theoretic Transform for Faster Ideal Lattice-Based Cryptography. In Cryptology and Network Security; Foresti, S., Persiano, G., Eds.; Springer International Publishing: Cham, Switzerland, 2016; pp. 124–139. [Google Scholar]

- Walter, C.D. Montgomery’s Multiplication Technique: How to Make It Smaller and Faster. In Cryptographic Hardware and Embedded Systems; Koç, Ç.K., Paar, C., Eds.; Springer: Berlin/Heidelberg, Germany, 1999; pp. 80–93. [Google Scholar]

- Weimerskirch, A.; Paar, C. Generalizations of the Karatsuba Algorithm for Efficient Implementations. IACR Cryptol. EPrint Arch. 2006, 2006, 224. [Google Scholar]

- Harvey, D. Faster arithmetic for number-theoretic transforms. J. Symb. Comput. 2014, 60, 113–119. [Google Scholar] [CrossRef]

- Sinha Roy, S.; Turan, F.; Jarvinen, K.; Vercauteren, F.; Verbauwhede, I. FPGA-Based High-Performance Parallel Architecture for Homomorphic Computing on Encrypted Data. In Proceedings of the 2019 IEEE International Symposium on High Performance Computer Architecture (HPCA), Washington, DC, USA, 16–20 February 2019; pp. 387–398. [Google Scholar]

- Rafferty, C.; O’Neill, M.; Hanley, N. Evaluation of Large Integer Multiplication Methods on Hardware. IEEE Trans. Comput. 2017, 66, 1369–1382. [Google Scholar] [CrossRef]

- NIST. Computer Security Division—Computer Security Resource Center. 2016. Available online: https://csrc.nist.gov (accessed on 3 August 2020).

- Rijndael. AES (Rijndael) IP Core, 2002. A Ultra-Compact Advanced Encryption Standard (AES, FIPS-197) Core. Available online: http://www.ipcores.com/aes_ip_core.htm (accessed on 15 March 2020).

- Imran, M.; Rashid, M. Architectural review of polynomial bases finite field multipliers over GF(2m). In Proceedings of the2017 International Conference on Communication, Computing and Digital Systems (C-CODE), Islamabad, Pakistan, 8–9 March 2017; pp. 331–336. [Google Scholar]

- Roma, C.; Tai, C.E.A.; Hasan, M.A. Energy Consumption of Round 2 Submissions for NIST PQC Standards. Available online: http://cacr.uwaterloo.ca/techreports/2019/cacr2019-03.pdf (accessed on 18 June 2020).

- Huang, W.L.; Chen, J.P.; Yang, B.Y. Power Analysis on NTRU Prime. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2020, 1, 123–151. [Google Scholar]

| Algorithm | RAM | ROM | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| n | p | q | r | s | Totalsize (Kbytes) | n | p | q | r | s | Totalsize (Kbytes) | |

| NTRU-Prime (sntrup857) | 1 | 256 | 8 | 0.256 | 0.256 | 0.448 | - | - | - | - | - | - |

| 1 | 24 | 64 | 0.192 | 0.192 | - | - | - | - | - | - | ||

| FrodoKEM (frodokem1344) | 3 | 10752 | 16 | 21.504 | 64.512 | 65.152 | - | - | - | - | - | - |

| 5 | 64 | 16 | 0.128 | 0.640 | - | - | - | - | - | - | ||

| Saber (firesaber) | 1 | 32 | 8 | 0.032 | 0.032 | 1.888 | - | - | - | - | - | - |

| 2 | 32 | 16 | 0.064 | 0.128 | - | - | - | - | - | - | ||

| 1 | 128 | 8 | 0.128 | 0.128 | - | - | - | - | - | - | ||

| 1 | 128 | 16 | 0.256 | 0.256 | - | - | - | - | - | - | ||

| 1 | 64 | 8 | 0.064 | 0.064 | - | - | - | - | - | - | ||

| 1 | 64 | 16 | 0.128 | 0.128 | - | - | - | - | - | - | ||

| 1 | 4 | 512 | 0.256 | 0.256 | - | - | - | - | - | - | ||

| 1 | 4 | 1024 | 0.512 | 0.512 | - | - | - | - | - | - | ||

| 1 | 4 | 256 | 0.128 | 0.128 | - | - | - | - | - | - | ||

| 1 | 4 | 512 | 0.256 | 0.256 | - | - | - | - | - | - | ||

| NTRU (hps4096821) | 14 | 821 | 16 | 1.642 | 22.988 | 22.988 | - | - | - | - | - | - |

| ThreeBears (papabearephem) | 1 | 40 | 8 | 0.040 | 0.040 | 3.409 | - | - | - | - | - | - |

| 1 | 1584 | 8 | 1.584 | 1.584 | - | - | - | - | - | - | ||

| 1 | 1697 | 8 | 1.697 | 1.697 | - | - | - | - | - | - | ||

| 1 | 24 | 8 | 0.024 | 0.024 | - | - | - | - | - | - | ||

| 2 | 32 | 8 | 0.032 | 0.064 | - | - | - | - | - | - | ||

| Round5 (r5nD-5pke-5d) | 2 | 16 | 8 | 0.016 | 0.032 | 0.064 | - | - | - | - | - | - |

| 1 | 32 | 8 | 0.032 | 0.032 | - | - | - | - | - | - | ||

| Crystals-Dilithium (dilithium4-AES) | 3 | 256 | 32 | 1.024 | 3.072 | 3.072 | - | - | - | - | - | - |

| Crystals-KYBER (kyber1024-90s) | 5 | 256 | 16 | 0.512 | 2.560 | 2.816 | 2 | 128 | 16 | 0.256 | 0.512 | 0.512 |

| 1 | 128 | 16 | 0.256 | 0.256 | - | - | - | - | - | |||

| NewHope (newhope1024cca) | 8 | 1024 | 16 | 2.048 | 16.384 | 16.384 | 4 | 1024 | 16 | 2.048 | 8.192 | 8.192 |

| LAC (lac256) | 1 | 2080 | 8 | 2.080 | 2.080 | 4.560 | 2 | 512 | 16 | 1.024 | 2.048 | 22.528 |

| 1 | 1056 | 8 | 1.056 | 1.056 | 1 | 5120 | 32 | 20.480 | 20.480 | |||

| 1 | 1024 | 8 | 1.424 | 1.424 | - | - | - | - | - | |||

| qTesla (qtesla-p-III) | 1 | 2048 | 8 | 2.048 | 2.048 | 152.576 | 1 | 444 | 32 | 1.776 | 1.776 | 22.000 |

| 1 | 9600 | 32 | 38.400 | 38.400 | 1 | 224 | 64 | 1.792 | 1.792 | |||

| 1 | 10,240 | 32 | 49.960 | 40.960 | 2 | 2048 | 36 | 9.216 | 18.432 | |||

| 1 | 1408 | 32 | 5.632 | 5.632 | - | - | - | - | - | |||

| 4 | 2048 | 64 | 16.384 | 65.536 | - | - | - | - | - | |||

| Falcon (falcon1024) | 5 | 1024 | 16 | 2.048 | 10.240 | 22.744 | 1 | 540 | 64 | 4.320 | 4.320 | 12.160 |

| 6 | 521 | 32 | 2.084 | 12.504 | 1 | 1080 | 16 | 2.160 | 2.160 | |||

| - | - | - | - | - | 2 | 31 | 64 | 0.248 | 0.496 | |||

| - | - | - | - | - | 2 | 27 | 64 | 0.216 | 0.432 | |||

| - | - | - | - | - | 2 | 30 | 64 | 0.240 | 0.480 | |||

| - | - | - | - | - | 2 | 1024 | 16 | 2.048 | 4.096 | |||

| - | - | - | - | - | 2 | 32 | 16 | 0.512 | 1.024 | |||

| - | - | - | - | - | 2 | 64 | 16 | 1.024 | 2.048 | |||

| - | - | - | - | - | 2 | 1024 | 8 | 1.024 | 2.048 | |||

| - | - | - | - | - | 2 | 256 | 8 | 0.256 | 0.512 | |||

| - | - | - | - | - | 2 | 512 | 8 | 0.512 | 1.024 | |||

| Algorithm (Reference Model) | Details of Arithmetic Operators and Operand Lengths (in Bits) | |||||

|---|---|---|---|---|---|---|

| Operators | Function Name (Method) | Input/Output Operands | ||||

| OP1 | OP2 | OP3 | OP4 | |||

| NTRU-Prime (sntrup857) | A × B | Rq_mult_small() (SBM) | 12,176 | 6088 | - | 12,176 |

| Rq_mult() (SBM) | 6088 | 6088 | - | 6088 | ||

| FrodoKEM (frodokem1344) | frodo_mul_add_as_plus_e() (SBM) | 172,032 | 172,032 | 128 | 172,032 | |

| frodo_mul_add _sa_plus_e() (SBM) | 172,032 | 172,032 | 128 | 172,032 | ||

| frodo_mul_add _sb_plus_e() (SBM) | 172,032 | 172,032 | 128 | 128 | ||

| frodo_mul _bs() (SBM) | 172,032 | 172,032 | 128 | 128 | ||

| poly_add() (SBM) | 128 | 128 | - | 128 | ||

| poly_sub() (SBM) | 128 | 128 | - | 128 | ||

| Saber (firesaber) | karatsuba_simple() (KM) | 4096 | 4096 | - | 4096 | |

| toom_cook_4way() (TCM) | 4096 | 4096 | - | 4096 | ||

| NTRU(hps4096821) | poly_Rq_mul() (KM) | 11,216 | 11,216 | - | 11,216 | |

| poly_Sq_mul() (TCM) | 11,216 | 11,216 | - | 11,216 | ||

| poly_S3_inv() (Almost algo) | 11,216 | - | - | 11,216 | ||

| ThreeBears (papabearephem) | += | mac() (2-Way KM) | 3120 | 3120 | - | 3120 |

| Round5 (r5nD-5pke-5d) | ringmul_p() (SBM) | 15,136 | 6208 | - | 7840 | |

| ringmul_p() (SBM) | 15,136 | 6208 | - | 15,136 | ||

| Crystals-Dilithium (dilithium4-AES) | poly_add() (SBM) | 8192 | 8192 | - | 8192 | |

| poly_sub() (SBM) | 8192 | 8192 | - | 8192 | ||

| poly_pointwise_invmontgomery() (NTT) | 8192 | 8192 | - | 8192 | ||

| Crystals-KYBER (kyber1024-90s) | poly_basemul() (NTT) | 3072 | 3072 | - | 3072 | |

| poly_add() (SBM) | 3072 | 3072 | - | 3072 | ||

| poly_sub() (SBM) | 3072 | 3072 | - | 3072 | ||

| NewHope (newhope1024cca) | poly_mul _pointwise() (NTT) | 16,384 | 16,384 | - | 16,384 | |

| poly_add() (SBM) | 128 | 128 | - | 128 | ||

| poly_sub() (SBM) | 128 | 128 | - | 128 | ||

| LAC (lac256) | poly_aff() (SBM) | 8192 | 8192 | 8192 | 8192 | |

| + C | poly_mul() (SBM) | 8192 | 8192 | 32 | 8192 | |

| qTesla (qtesla-p-III) | poly_mul() (NTT) | 16,384 | 16,384 | - | 16,384 | |

| poly_add() (SBM) | 16,384 | 16384 | - | 16,384 | ||

| poly_sub_reduce() (SBM) | 16,384 | 16,384 | - | 16,384 | ||

| Falcon (falcon1024) | mq_poly_sub() (SBM) | 24,576 | 24,576 | - | 24,576 | |

| mq_poly_montymul_ntt() (Mont) | 24,576 | 24,576 | - | 24,576 | ||

| mq_montymul() (Mont) | 32 | 32 | 32 | 32 | ||

| Algorithm (Reference Model) | Name of the Hashing Method Utilized |

|---|---|

| NTRU-Prime (sntrup857) | SHA2-512 |

| FrodoKEM (frodokem1344) | AES-128 (or) SHAKE-128 for matrix generation, SHAKE-128 (or) SHAKE-256 for key generation/encryption |

| Saber (firesaber) | SHAKE-128, SHA3-256 and SHA3-512 |

| NTRU (hps4096821) | SHA3-256 |

| ThreeBears (papabearephem) | cSHAKE-256 |

| Round5 (r5nD-5pke-5d) | cSHAKE-256 and AES-256 |

| Crystals-Dilithium (dilithium4-AES) | SHAKE-128 and SHAKE-256 |

| Crystals-KYBER (kyber1024-90s) | AES-256, SHA2-256, SHA2-512 and SHAKE-256 |

| NewHope (newhope1024cca) | SHAKE-128 and SHAKE-256 |

| LAC (lac256) | - |

| qTesla (qtesla-p-III) | SHAKE-256, cSHAKE-128 and cSHAKE-256 |

| Falcon (falcon1024) | SHAKE-256 |

| Area and Power Calculation of RAMs | Area and Power Calculation of ROMs | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 2–15 Algorithm | Input | Dimension (m) | Total Area (mm) * | Power Consumption | Input | Dimension (m) | Total Area (mm) * | Power Consumption | ||||||

| p | q | W | H | Static (W) | Dynamic (W × F) | p | q | W | H | Static (W) | Dynamic (W × F) | |||

| NTRU-Prime | 256 | 8 | 112.8 | 160.5 | 0.1087 | 0.331 | 8.307 | - | - | - | - | - | - | - |

| 24 | 64 | 79.2 | 161.5 | 0.0768 | 0.331 | 5.488 | - | - | - | - | - | - | - | |

| FrodoKEM | 10,752 | 16 | 311.1 | 59.1 | 0.0184 | 0.213 | 22.656 | - | - | - | - | - | - | - |

| 64 | 16 | 109.5 | 59.1 | 0.0065 | 0.084 | 6.613 | - | - | - | - | - | - | - | |

| Saber | 32 | 8 | 75.9 | 55.1 | 0.0042 | 0.056 | 3.832 | - | - | - | - | - | - | - |

| 32 | 16 | 109.5 | 55.1 | 0.0121 | 0.112 | 6.452 | - | - | - | - | - | - | - | |

| 128 | 8 | 75.9 | 67.1 | 0.0051 | 0.076 | 4.149 | - | - | - | - | - | - | - | |

| 128 | 16 | 109.5 | 67.1 | 0.0174 | 0.103 | 6.932 | - | - | - | - | - | - | - | |

| 64 | 8 | 75.9 | 59.1 | 0.0045 | 0.062 | 3.938 | - | - | - | - | - | - | - | |

| 64 | 16 | 109.5 | 59.1 | 0.0065 | 0.084 | 6.613 | - | - | - | - | - | - | - | |

| 4 | 512 | 647.1 | 55.1 | 0.0357 | 0.376 | 13.083 | - | - | - | - | - | - | - | |

| 4 | 1024 | 647.1 | 55.1 | 0.0357 | 0.376 | 5.758 | - | - | - | - | - | - | - | |

| 4 | 256 | 647.1 | 55.1 | 0.0357 | 0.376 | 7.156 | - | - | - | - | - | - | - | |

| 4 | 512 | 647.1 | 55.1 | 0.0357 | 0.376 | 13.083 | - | - | - | - | - | - | - | |

| NTRU | 821 | 16 | 112.8 | 156.5 | 0.2473 | 0.319 | 82.280 | - | - | - | - | - | - | - |

| ThreeBears | 40 | 8 | 75.9 | 56.1 | 0.0043 | 0.057 | 3.859 | - | - | - | - | - | - | - |

| 1584 | 8 | 79.2 | 253.9 | 0.0201 | 0.399 | 6.772 | - | - | - | - | - | - | - | |

| 1697 | 8 | 79.2 | 268.9 | 0.0213 | 0.426 | 6.978 | - | - | - | - | - | - | - | |

| 24 | 8 | 75.9 | 55.1 | 0.0042 | 0.056 | 3.832 | - | - | - | - | - | - | - | |

| 32 | 8 | 75.9 | 55.1 | 0.0042 | 0.056 | 3.832 | - | - | - | - | - | - | - | |

| Round5 | 16 | 8 | 75.9 | 55.1 | 0.0042 | 0.056 | 3.832 | - | - | - | - | - | - | - |

| 32 | 8 | 75.9 | 55.1 | 0.0042 | 0.056 | 3.832 | - | - | - | - | - | - | - | |

| Crystals-Dilithium | 256 | 32 | 176.7 | 83.1 | 0.0441 | 0.216 | 12.762 | - | - | - | - | - | - | - |

| Crystals-KYBER | 256 | 16 | 109.5 | 83.1 | 0.0729 | 0.141 | 7.156 | 128 | 16 | 85.7 | 36.2 | 0.0062 | 0.175 | 5.541 |

| 128 | 16 | 109.5 | 67.1 | 0.0074 | 0.103 | 6.932 | - | - | - | - | - | - | - | |

| NewHope | 1024 | 16 | 112.8 | 181.5 | 0.1639 | 0.379 | 8.624 | 1024 | 16 | 85.7 | 80.4 | 0.0276 | 0.310 | 8.455 |

| LAC | 2080 | 8 | 183.7 | 32.8 | 0.0121 | 0.628 | 7.563 | 512 | 16 | 85.7 | 55.1 | 0.0094 | 0.232 | 7.0224 |

| 1056 | 8 | 79.2 | 186.3 | 0.0148 | 0.285 | 5.874 | 5120 | 32 | 128.7 | 308.3 | 0.0397 | 1.281 | 17.750 | |

| 1024 | 8 | 79.2 | 181.5 | 0.0144 | 0.279 | 5.758 | - | - | - | - | - | - | - | |

| qTesla | 2048 | 8 | 79.2 | 312.7 | 0.0248 | 0.319 | 11.553 | 444 | 32 | 128.7 | 52.0 | 0.0067 | 0.266 | 11.553 |

| 9600 | 32 | 180.0 | 312.7 | 0.2815 | 1.050 | 69.676 | 224 | 64 | 214.6 | 40.9 | 0.0088 | 0.316 | 17.9650 | |

| 10,240 | 32 | 180.0 | 312.7 | 0.2815 | 1.050 | 87.096 | 2048 | 36 | 139.4 | 137.2 | 0.0383 | 0.600 | 17.089 | |

| 1408 | 32 | 180.0 | 231.1 | 0.0416 | 0.756 | 15.661 | - | - | - | - | - | - | - | |

| 2048 | 64 | 314.4 | 312.7 | 0.3934 | 1.784 | 30.560 | - | - | - | - | - | - | - | |

| Falcon | 1024 | 16 | 112.8 | 181.5 | 0.0205 | 0.379 | 8.624 | 540 | 64 | 214.6 | 56.7 | 0.0122 | 0.364 | 22.329 |

| 521 | 32 | 180.0 | 118.7 | 0.1287 | 0.454 | 13.83 | 1080 | 16 | 85.7 | 89.8 | 0.0077 | 0.379 | 8.520 | |

| - | - | - | - | - | - | - | 31 | 64 | 214.6 | 31.4 | 0.0135 | 0.288 | 15.190 | |

| - | - | - | - | - | - | - | 27 | 64 | 214.6 | 31.4 | 0.0135 | 0.288 | 15.190 | |

| - | - | - | - | - | - | - | 30 | 64 | 214.6 | 31.4 | 0.0135 | 0.288 | 15.190 | |

| - | - | - | - | - | - | - | 1024 | 16 | 85.7 | 80.4 | 0.0138 | 0.309 | 8.455 | |

| - | - | - | - | - | - | - | 32 | 16 | 85.7 | 31.4 | 0.0054 | 0.160 | 5.121 | |

| - | - | - | - | - | - | - | 64 | 16 | 85.7 | 33.0 | 0.0057 | 0.165 | 5.272 | |

| - | - | - | - | - | - | - | 1024 | 8 | 64.2 | 80.4 | 0.0103 | 0.309 | 8.455 | |

| - | - | - | - | - | - | - | 256 | 8 | 64.2 | 42.5 | 0.0055 | 0.174 | 3.988 | |

| - | - | - | - | - | - | - | 512 | 8 | 64.2 | 55.1 | 0.0071 | 0.232 | 7.022 | |

| Algorithms (Operand Sizes in Bits) | Combinational Cells | Sequential Cells | Area (mm) | Dynamic Power (W) | Leakage Power (W) |

|---|---|---|---|---|---|

| NTRU-Prime (6088 × 6088) | 435,073 | 12,189 | 0.8389 | 100,510.6 | 125.3402 |

| NTRU-Prime (12,176 × 6088) | 750,152 | 18,278 | 1.4124 | 144,073.8 | 202.0082 |

| FrodoKEM * (172,032 × 172,032) | - | 2,329,421 | 22.1505 | 51,177,810 | 629.637 |

| Saber (4096 × 4096) | 206,941 | 8205 | 0.4599 | 66,433.2 | 42.4874 |

| NTRU (11,216 × 11,216) | 821,229 | 22,446 | 1.5602 | 163,509.7 | 207.3250 |

| ThreeBears (3120 × 3120) | 141,422 | 6252 | 0.3192 | 58,829.7 | 30.8762 |

| Round5 (15,136 × 6208) | 902,623 | 21,358 | 1.6785 | 164,367.2 | 230.1910 |

| Crystals-Dilithium (8192 × 8192) | 592,155 | 16,398 | 1.1251 | 123,343.3 | 139.4685 |

| Crystals-KYBER (3072 × 3072) | 131,973 | 6156 | 0.3069 | 51,800.5 | 31.9299 |

| NewHope (16,384 × 16,384) | 1,302,689 | 32,783 | 2.4760 | 230,704.9 | 446.6865 |

| LAC (8192 × 8192) | 592,155 | 16,398 | 1.1251 | 123,343.3 | 139.4685 |

| qTesla (16,384 × 16,384) | 1,302,689 | 32,783 | 2.4760 | 230,704.9 | 446.6865 |

| Falcon (32 × 32) | 1001 | 70 | 0.0024 | 581.5 | 0.2499 |

| Falcon (24,576 × 24,576) | 2,926,129 | 49,167 | 5.4670 | 327,836.5 | 1410.9000 |

| Algorithms | Hash Functions (Total = 10) | Area (mm) | Dynamic Power (W) | Leakage Power (W) |

|---|---|---|---|---|

| NTRU-Prime | SHA2-512 | 0.0732 | 18,003.4 | 1.6227 |

| FrodoKEM | AES-128 | 0.0225 | 6415.5 | 0.3062 |

| SHAKE-256 | 0.1056 | 18,568.4 | 3.6235 | |

| Saber | SHAKE-128 | 0.1101 | 19,379.2 | 3.1528 |

| SHA3-256 | 0.1062 | 18,568.1 | 4.2955 | |

| SHA3-512 | 0.0984 | 15,927.1 | 3.2830 | |

| NTRU | SHA3-256 | 0.1062 | 18,568.1 | 4.2955 |

| ThreeBears | cSHAKE-256 | 0.1055 | 18,568.4 | 3.6235 |

| Round5 | cSHAKE-256 | 0.1055 | 18,568.4 | 3.6235 |

| AES-256 | 0.0395 | 13,562.1 | 0.4472 | |

| Crystals-Dilithium | SHAKE-128 | 0.1103 | 19,649.9 | 4.4626 |

| SHAKE-256 | 0.1056 | 18,556.2 | 3.5285 | |

| Crystals-KYBER | AES-256 | 0.0395 | 13,562.1 | 0.4472 |

| SHA2-256 | 0.0362 | 8881.4 | 0.4671 | |

| SHA2-512 | 0.0732 | 18,003.4 | 1.6227 | |

| SHAKE-256 | 0.1055 | 18,568.4 | 3.6235 | |

| NewHope | SHAKE-128 | 0.1103 | 19,649.9 | 4.4626 |

| SHAKE-256 | 0.1055 | 18,555.9 | 3.4193 | |

| LAC | - | - | - | - |

| qTesla | SHAKE-256 | 0.1056 | 18,568.4 | 3.6235 |

| cSHAKE-128 | 0.1103 | 19,649.9 | 4.4626 | |

| cSHAKE-256 | 0.1055 | 18,568.4 | 3.6235 | |

| Falcon | SHAKE-256 | 0.1056 | 18,559.8 | 3.4941 |

| Reference | Implemented Accelerator | SLi | Clk. Period (ns) | Freq. (MHz) | Total Area (m) | Total Power (mW) |

|---|---|---|---|---|---|---|

| [23] | Crystals-KYBER | 1 | 5.0 | 200 | 3,378,515 | 39.21 |

| NewHope | 1 | 5.9 | 168.6 | 3,208,999 | 38.02 | |

| NTRU | 1 | 5.8 | 169.5 | 1,246,869 | 14.30 | |

| Saber | 3 | 7.2 | 137.75 | 4,774,529 | 54.49 | |

| Crystals-Dilithium | 1 | 6.3 | 157.7 | 4,774,529 | 51.24 | |

| [24] | qTesla | 1 | 5.0 | 200 | 3,450,765 | 16.08 |

| Crystals-Dilithium | 1 | 5.0 | 200 | 3,677,434 | 11.31 | |

| This work | Crystals-KYBER | 5 | 5.0 | 200 | 596,300 (−82%) | 47.39 (+21%) |

| NewHope | 5 | 5.93 | 168.6 | 2,384,120 (−26%) | 98.54 (+159%) | |

| NTRU | 5 | 5.89 | 169.5 | 1,642,730 (+32%) | 78.85 (+451%) | |

| Saber | 5 | 7.3 | 137.75 | 834,200 (−82%) | 42.14 (−23%) | |

| Crystals-Dilithium | 4 | 6.34 | 157.7 | 1,153,800 (−76%) | 50.94 (−1%) | |

| qTesla | 3 | 5.0 | 200 | 3,348,300 (−3%) | 156.44 (873%) | |

| Crystals-Dilithium | 4 | 5.0 | 200 | 1,165,100 (−68%) | 69.41 (513%) | |

| This work (digitized multiplier) | qTesla (8 digits) | 3 | 5.0 | 200 | 2,187,300 (−37%) | 137.29 (754%) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Imran, M.; Abideen, Z.U.; Pagliarini, S. An Experimental Study of Building Blocks of Lattice-Based NIST Post-Quantum Cryptographic Algorithms. Electronics 2020, 9, 1953. https://doi.org/10.3390/electronics9111953

Imran M, Abideen ZU, Pagliarini S. An Experimental Study of Building Blocks of Lattice-Based NIST Post-Quantum Cryptographic Algorithms. Electronics. 2020; 9(11):1953. https://doi.org/10.3390/electronics9111953

Chicago/Turabian StyleImran, Malik, Zain Ul Abideen, and Samuel Pagliarini. 2020. "An Experimental Study of Building Blocks of Lattice-Based NIST Post-Quantum Cryptographic Algorithms" Electronics 9, no. 11: 1953. https://doi.org/10.3390/electronics9111953

APA StyleImran, M., Abideen, Z. U., & Pagliarini, S. (2020). An Experimental Study of Building Blocks of Lattice-Based NIST Post-Quantum Cryptographic Algorithms. Electronics, 9(11), 1953. https://doi.org/10.3390/electronics9111953