Parameters Design and Optimization of a High Frequency, Interleaved, Dual-Buck, Bidirectional, Grid-Connected Converter

Abstract

:1. Introduction

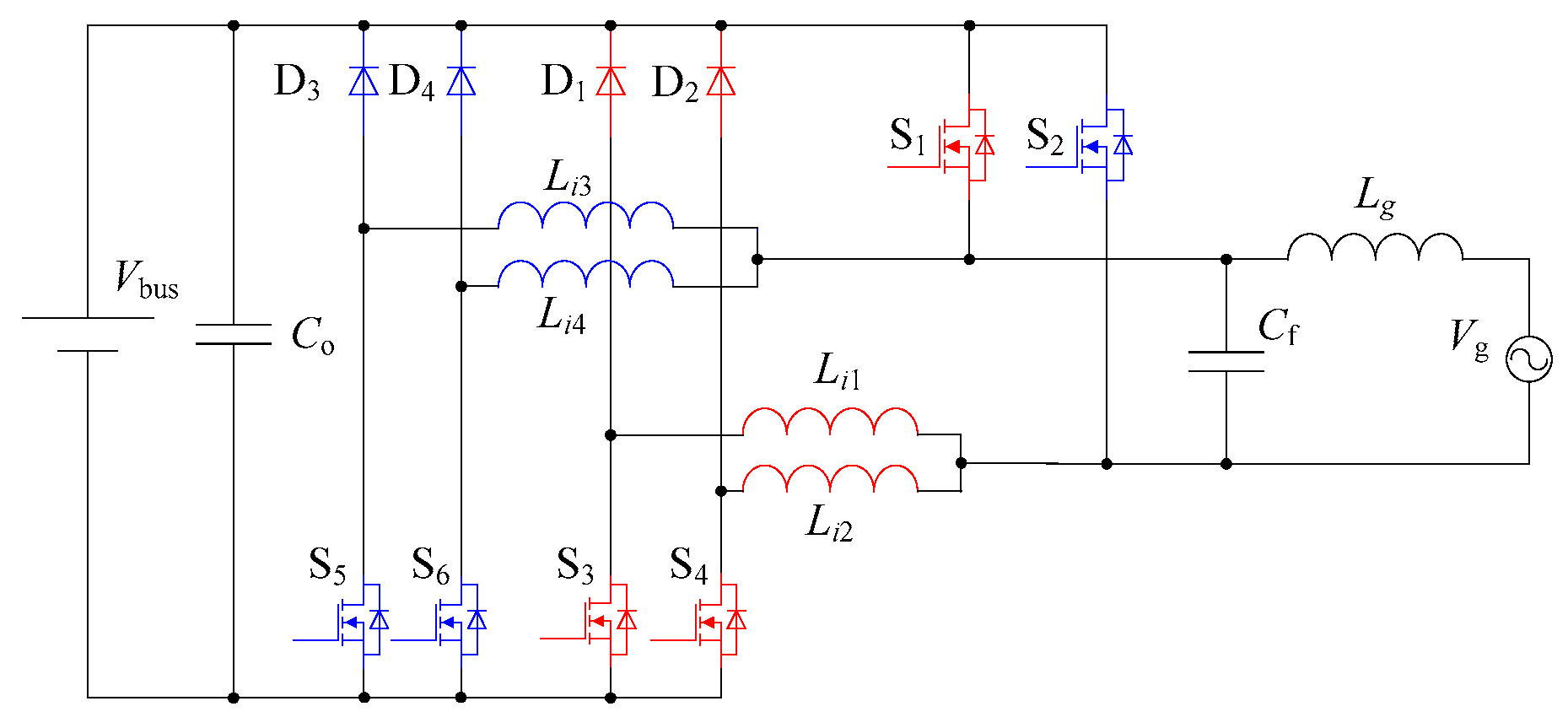

2. Topology Description and Operation Principles

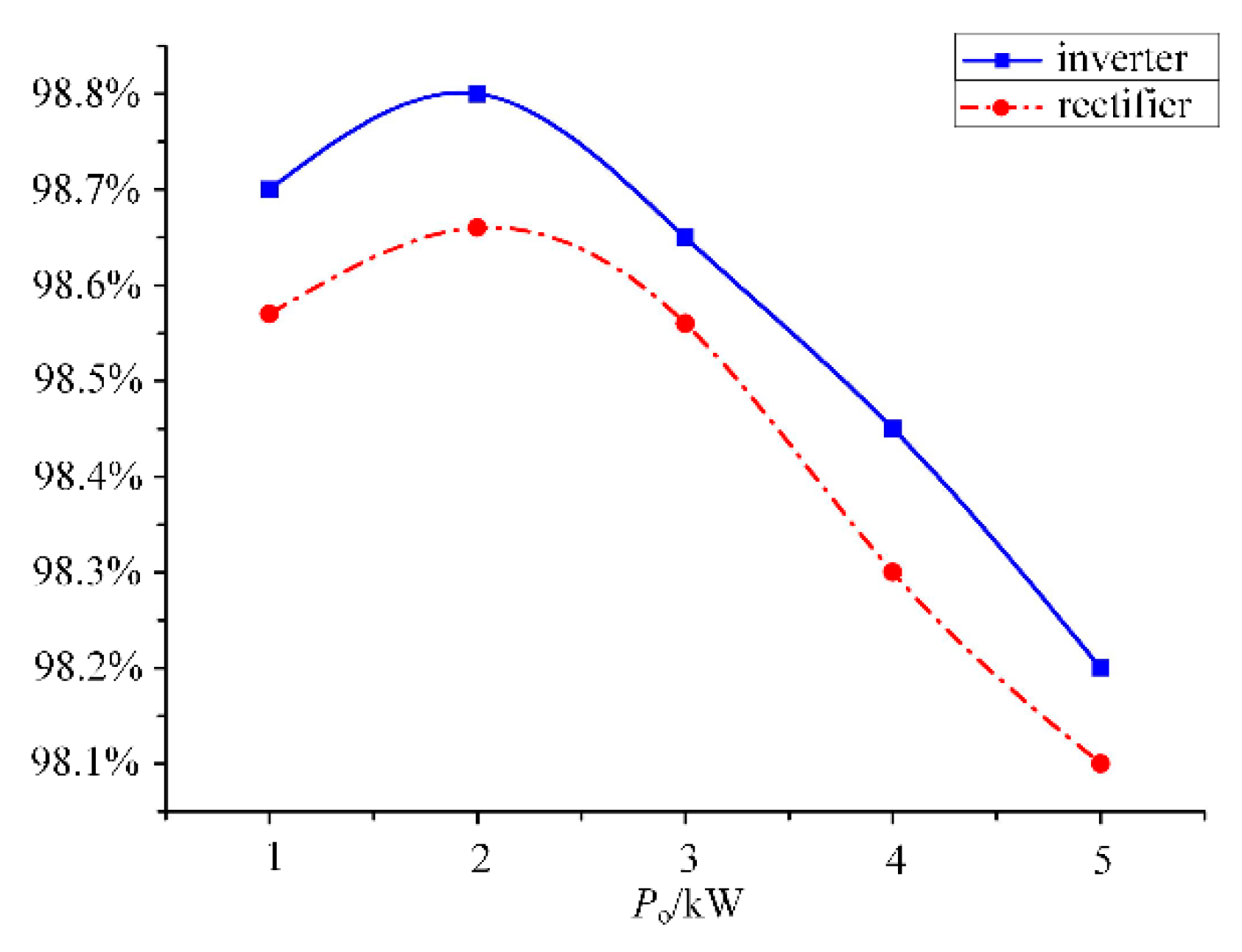

2.1. Topology Description

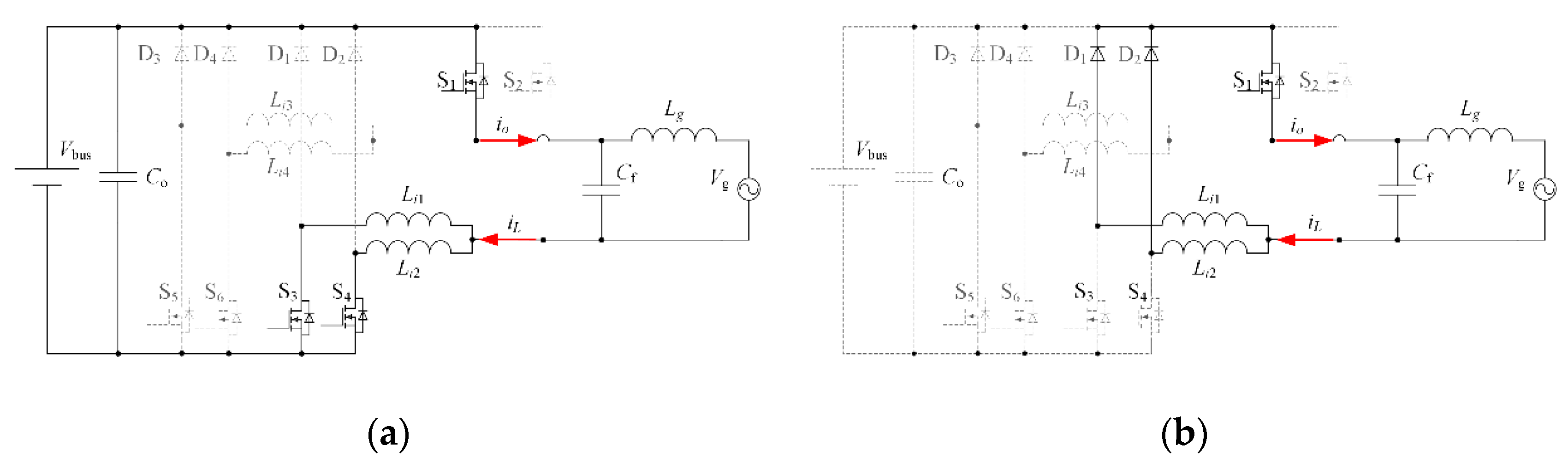

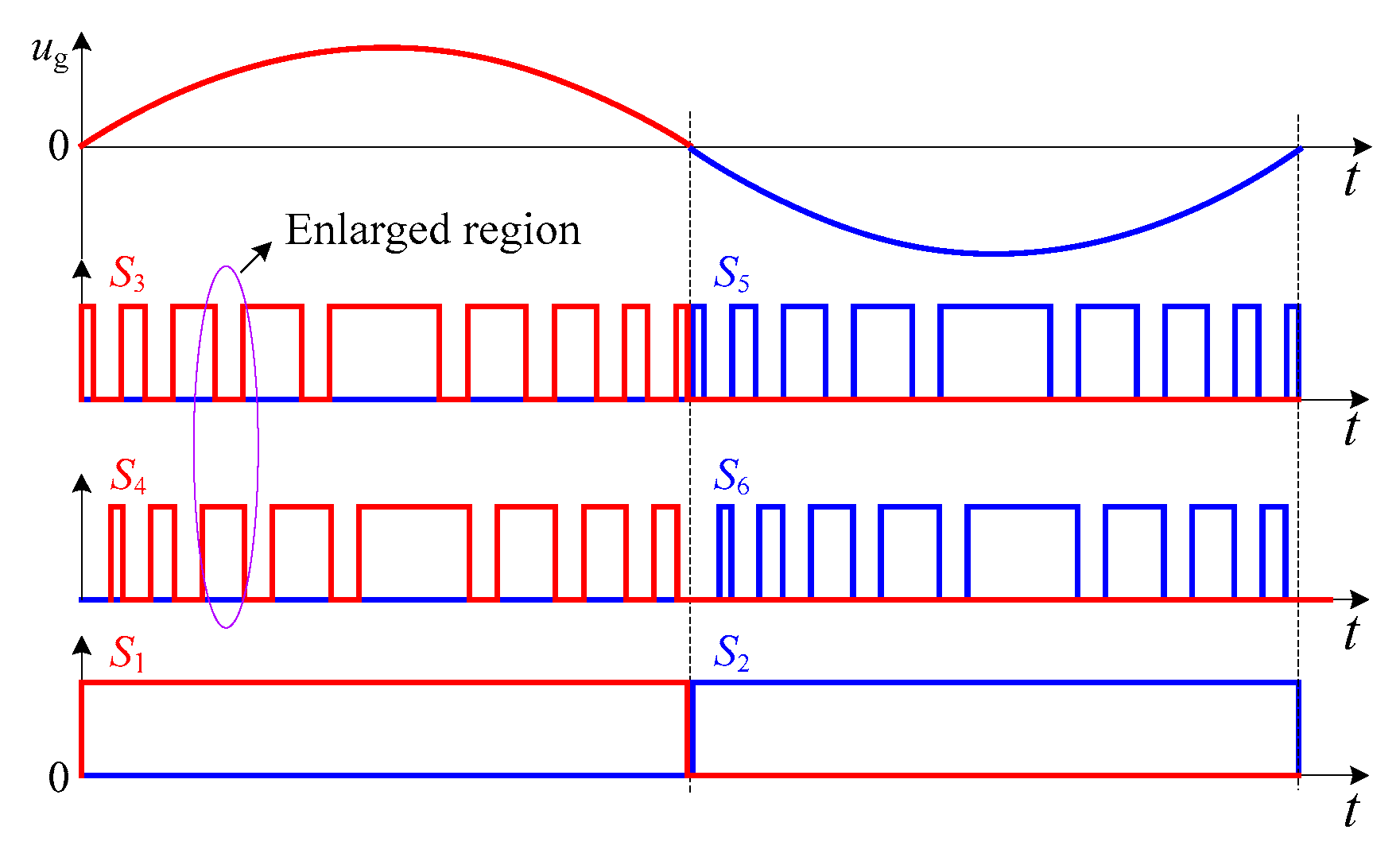

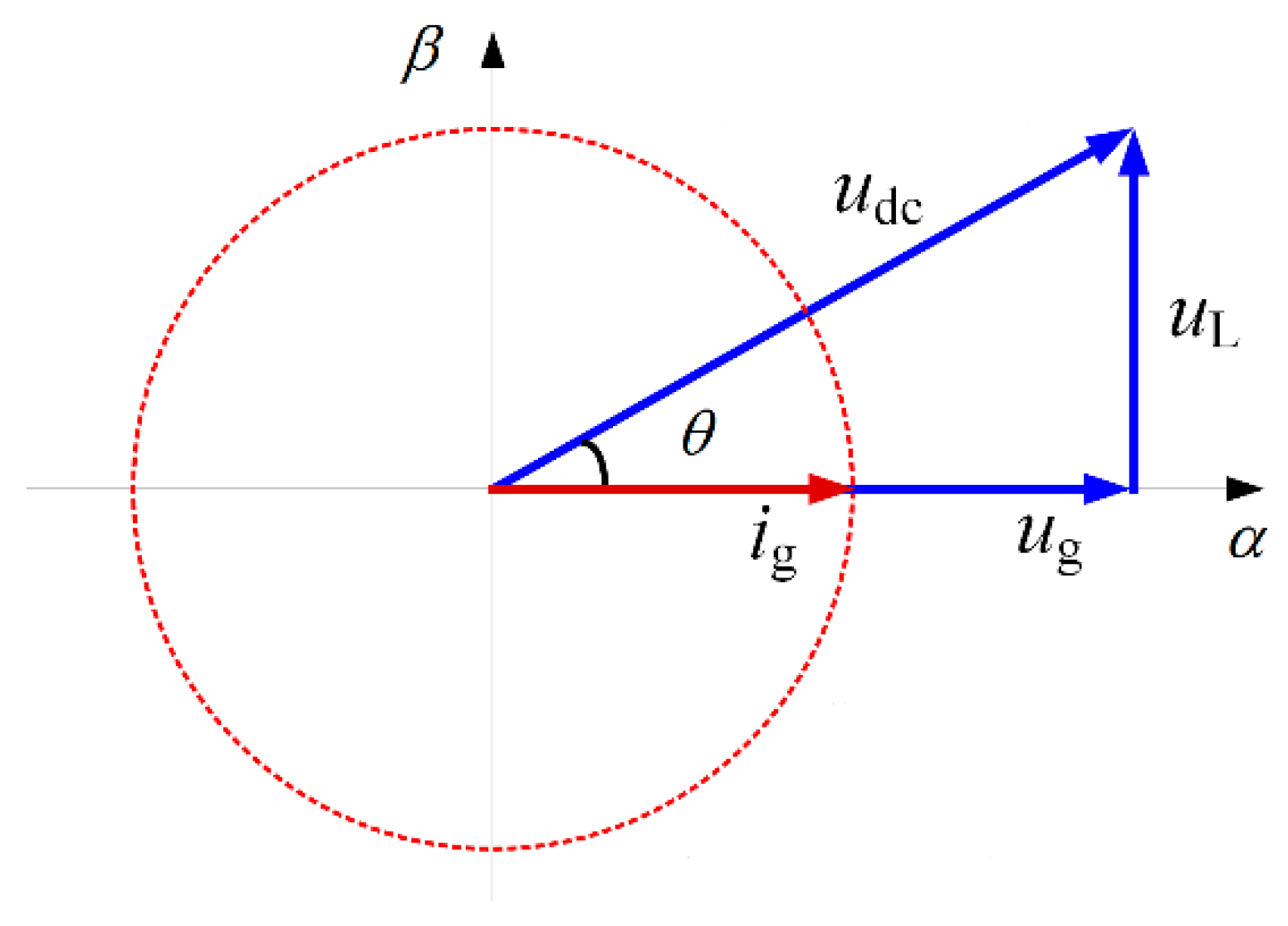

2.2. Operation Principles

- (1)

- All devices in the topology are ideal.

- (2)

- Compared with the grid current, the current of output capacitor Cf is small enough to be ignored.

- (3)

- The circuit is in a steady state.

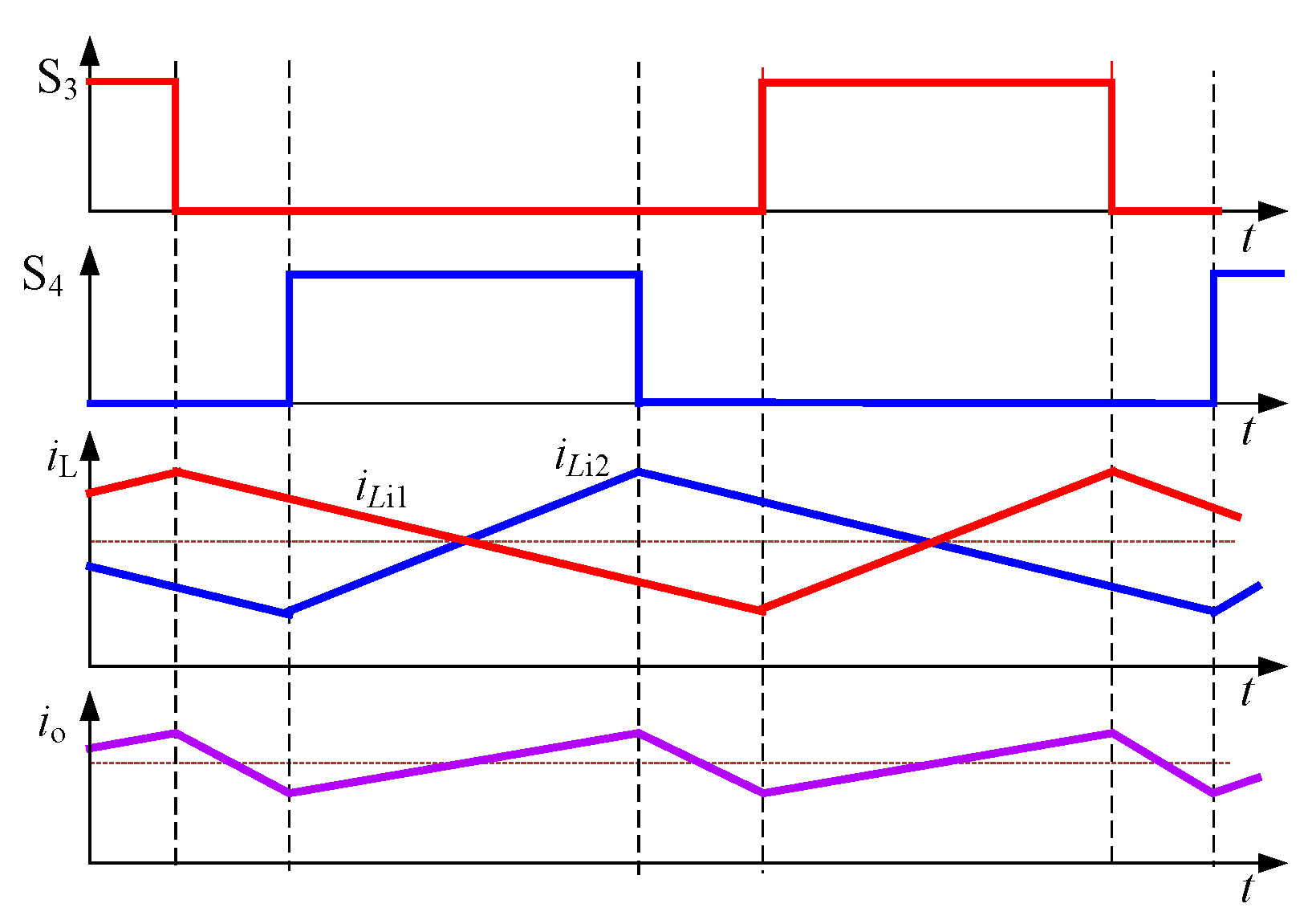

2.3. Ripple Analysis

3. Parameter Design

3.1. Parameter Selection

3.1.1. Preliminary Range of Filter Inductance

3.1.2. Preliminary Range of Filter Capacitance

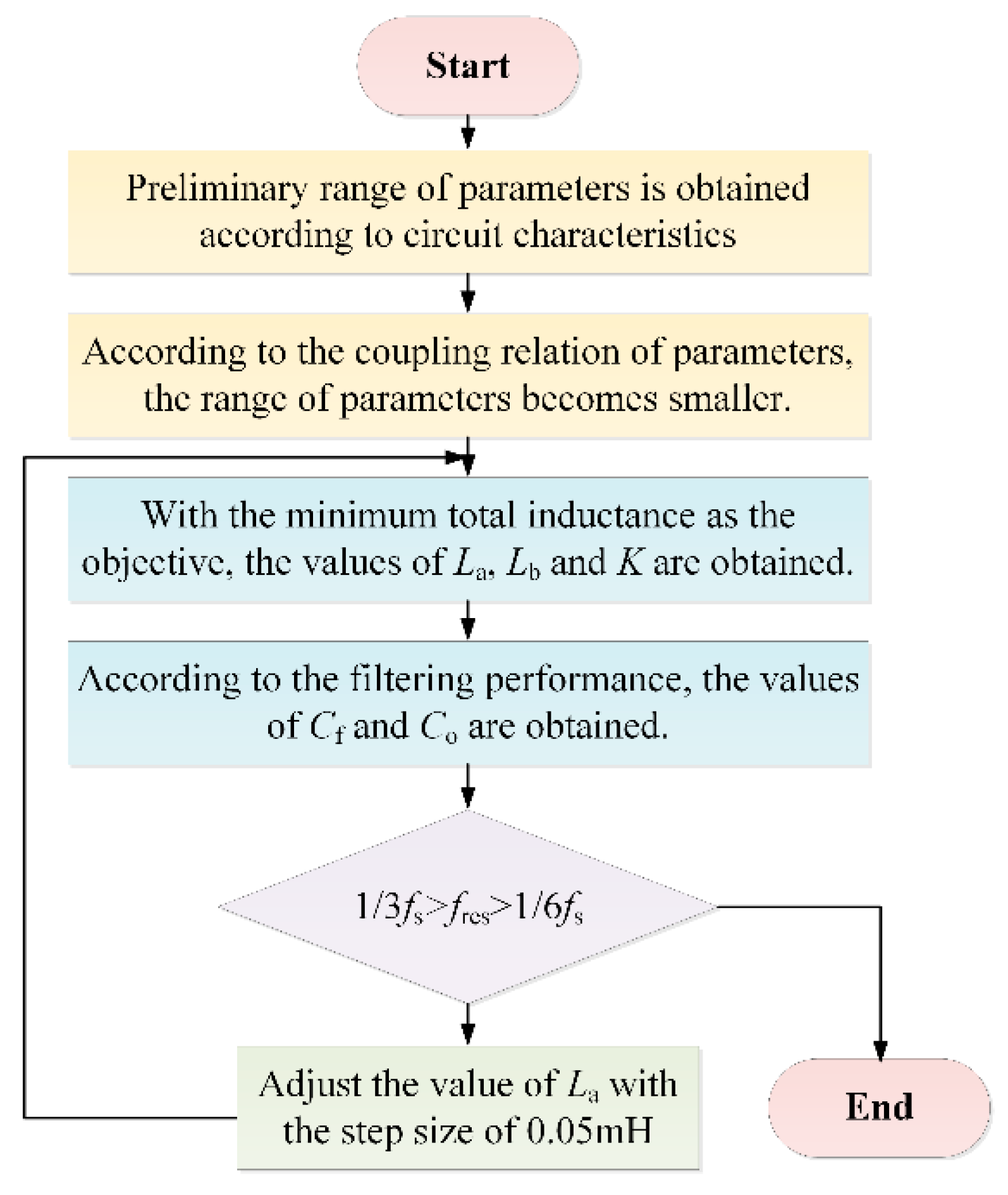

3.2. Parameter Optimization

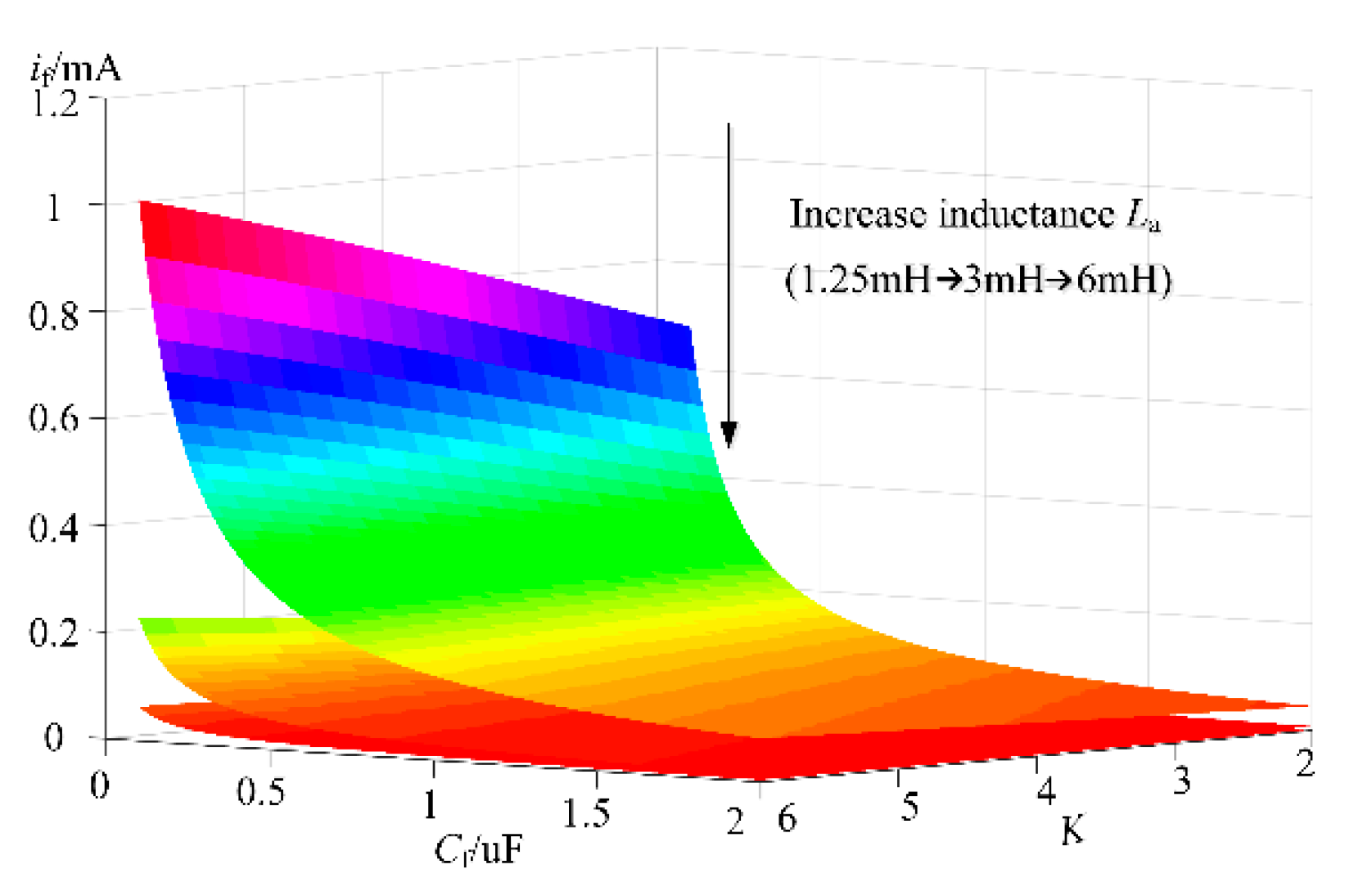

3.2.1. Range Optimization of Inductance Ratio

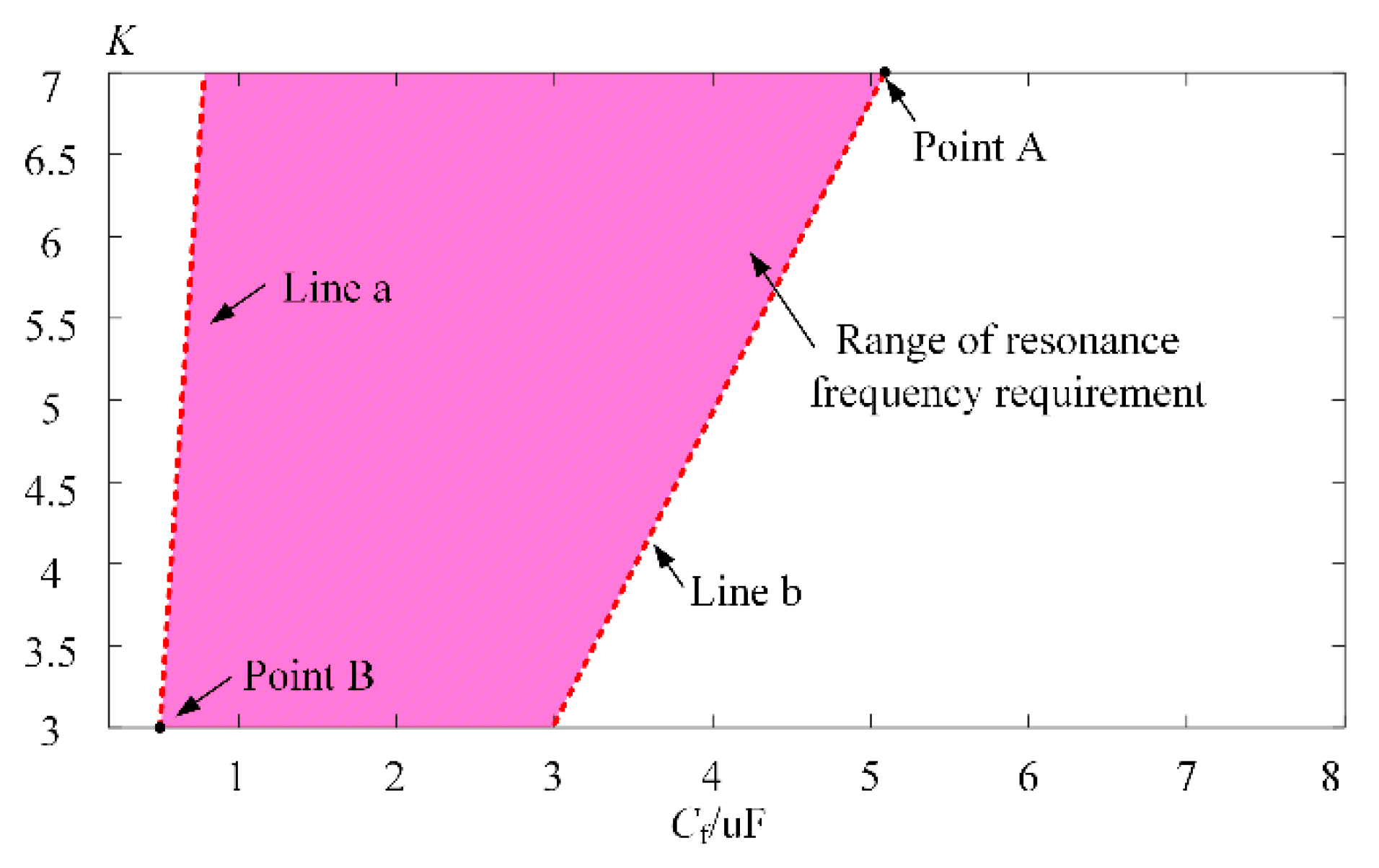

3.2.2. Range Optimization of Capacitance

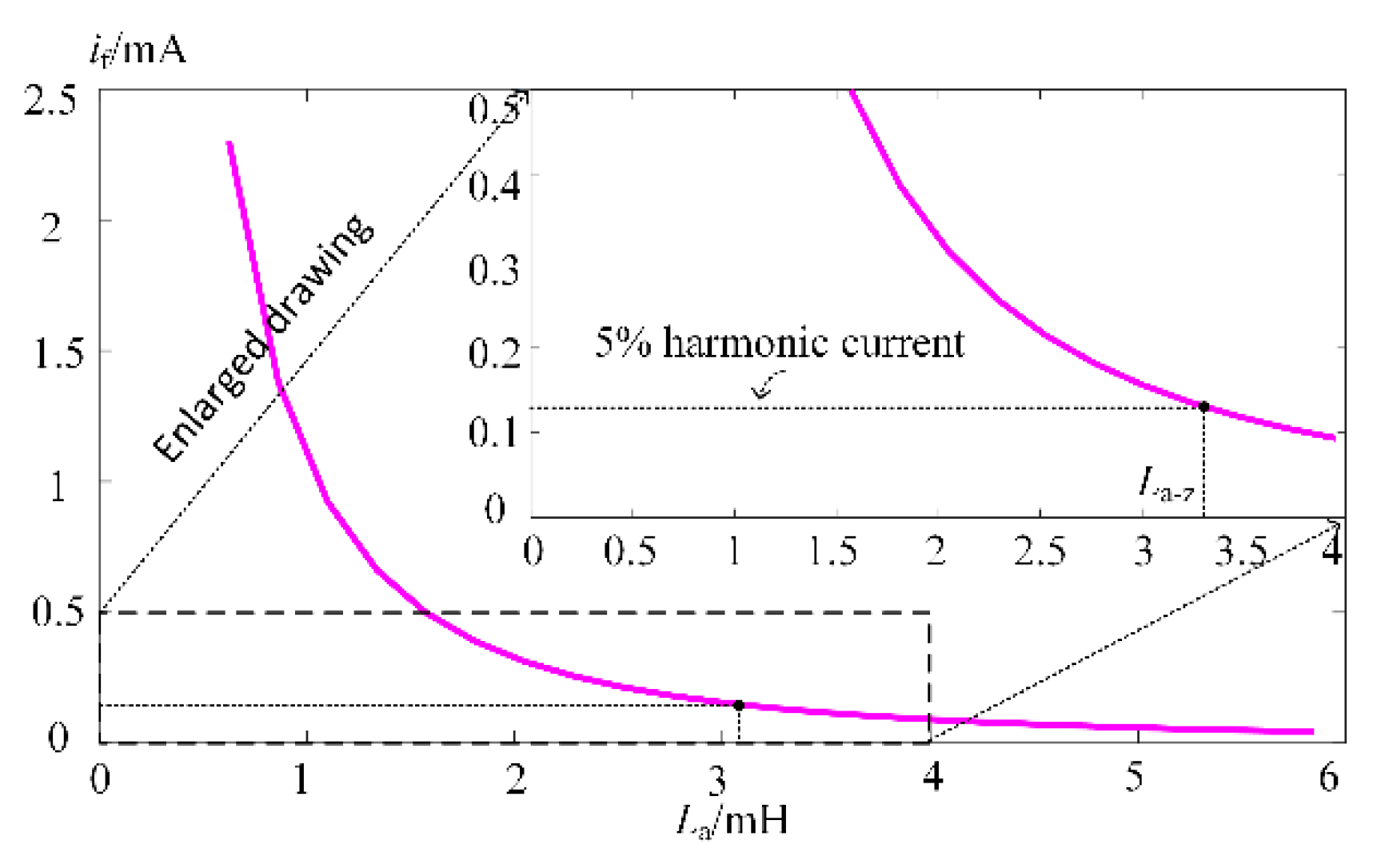

3.2.3. Range Optimization of Inductance

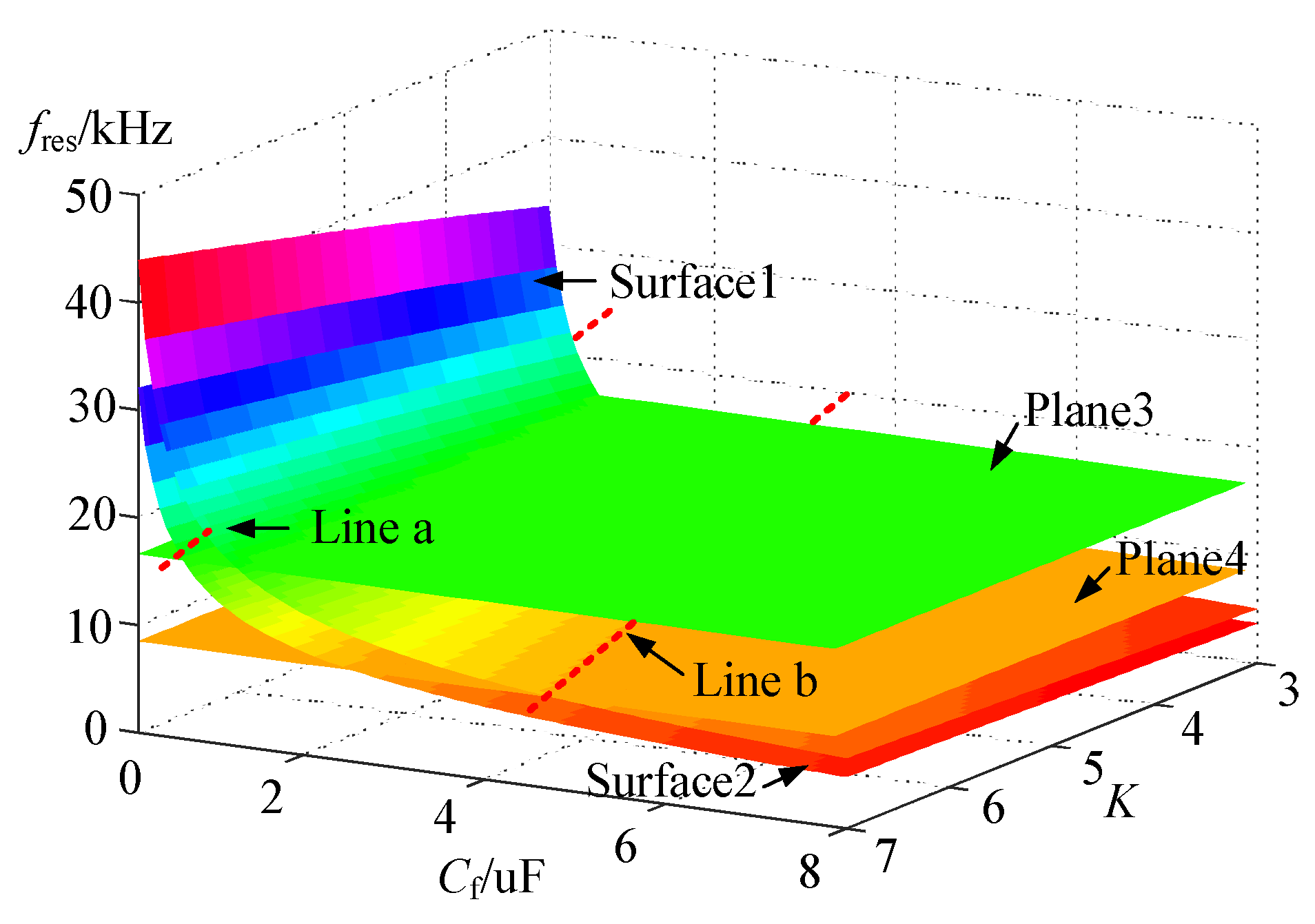

3.3. Stability Analysis

3.3.1. Stability in the Inverter State

3.3.2. Stability in the Rectifier State

3.4. Performance Index

3.4.1. Power Density Performance Index

3.4.2. Filtering Performance Index

3.4.3. Stability Performance Index

3.4.4. Performance Index Priority

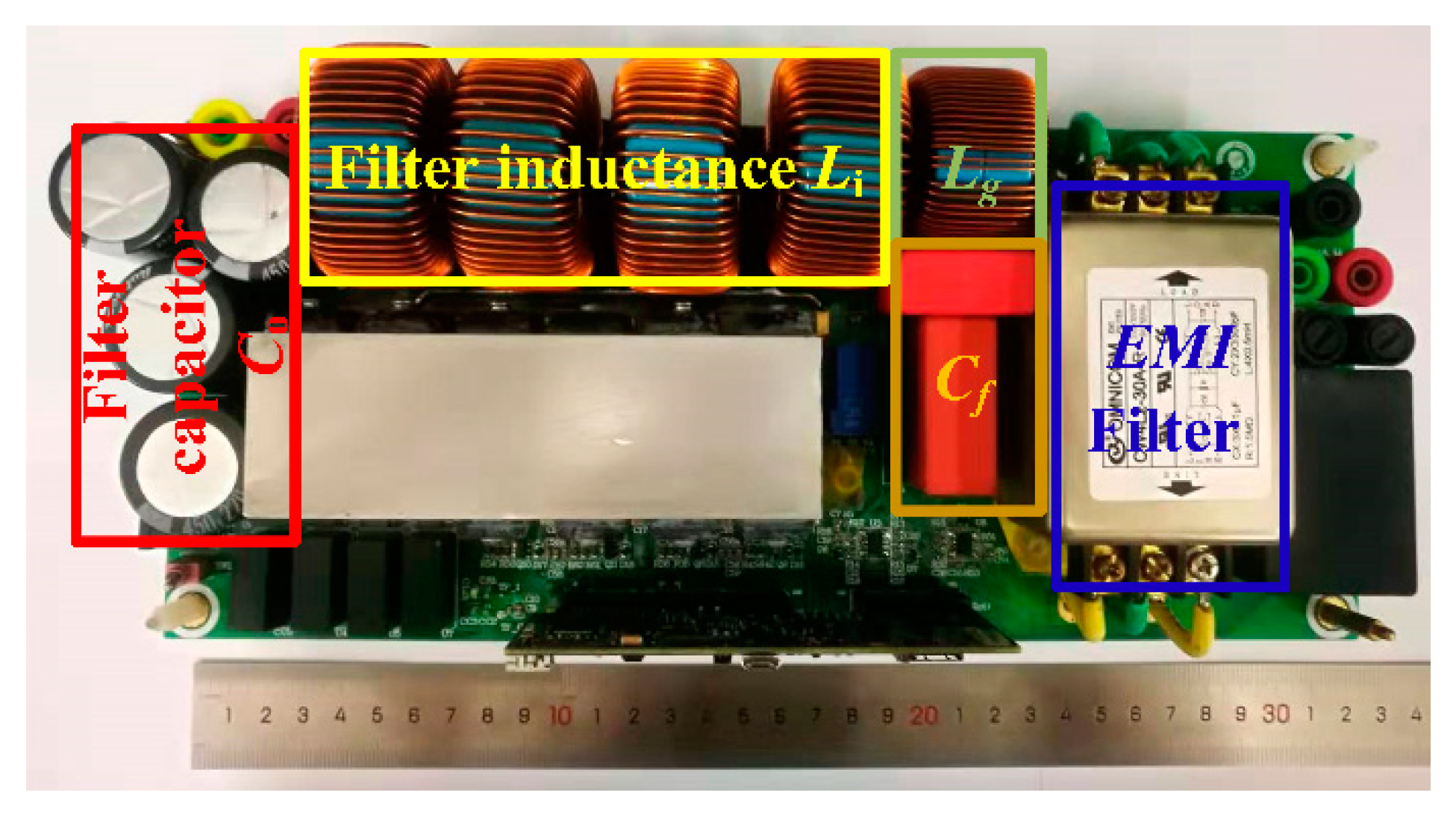

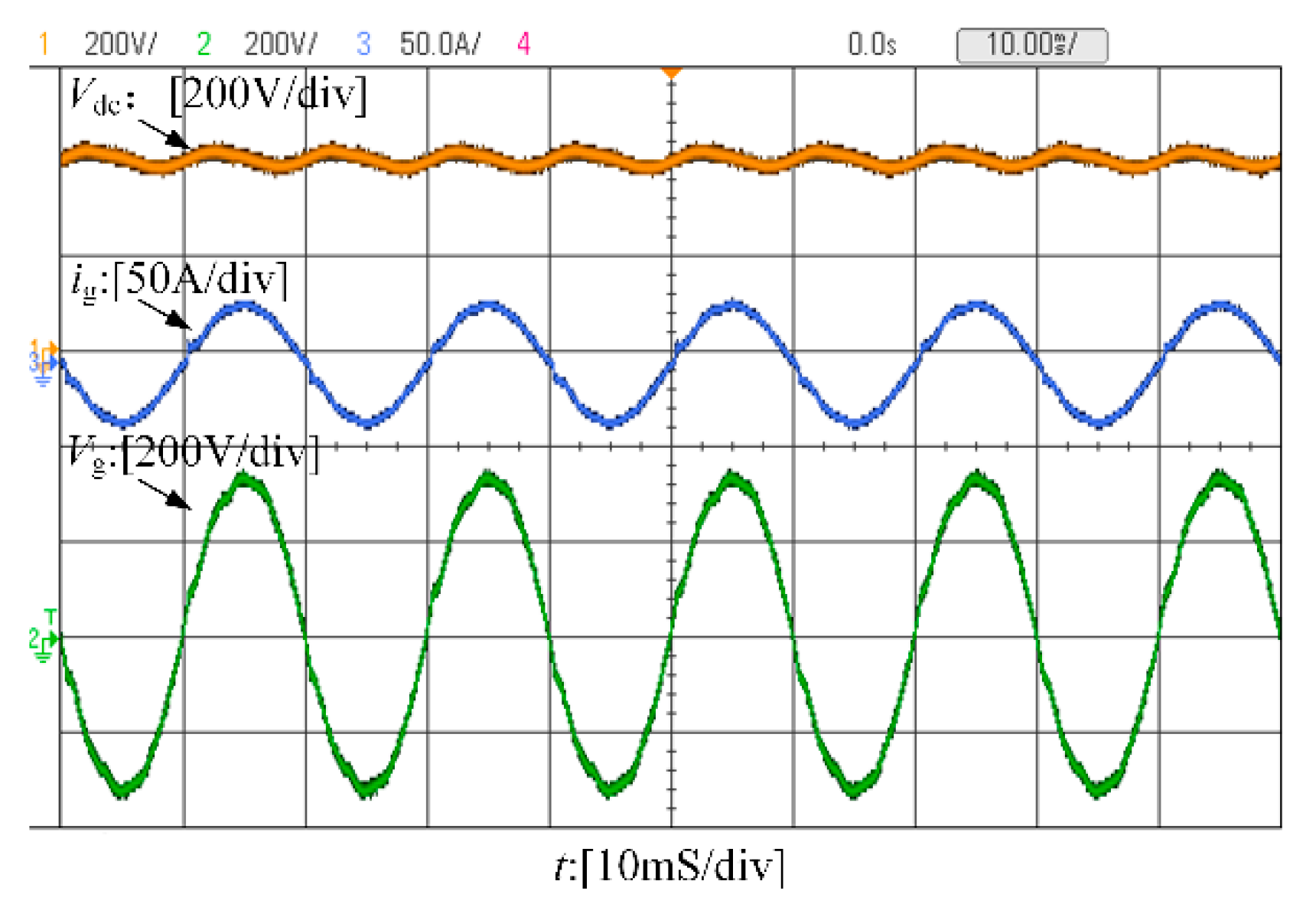

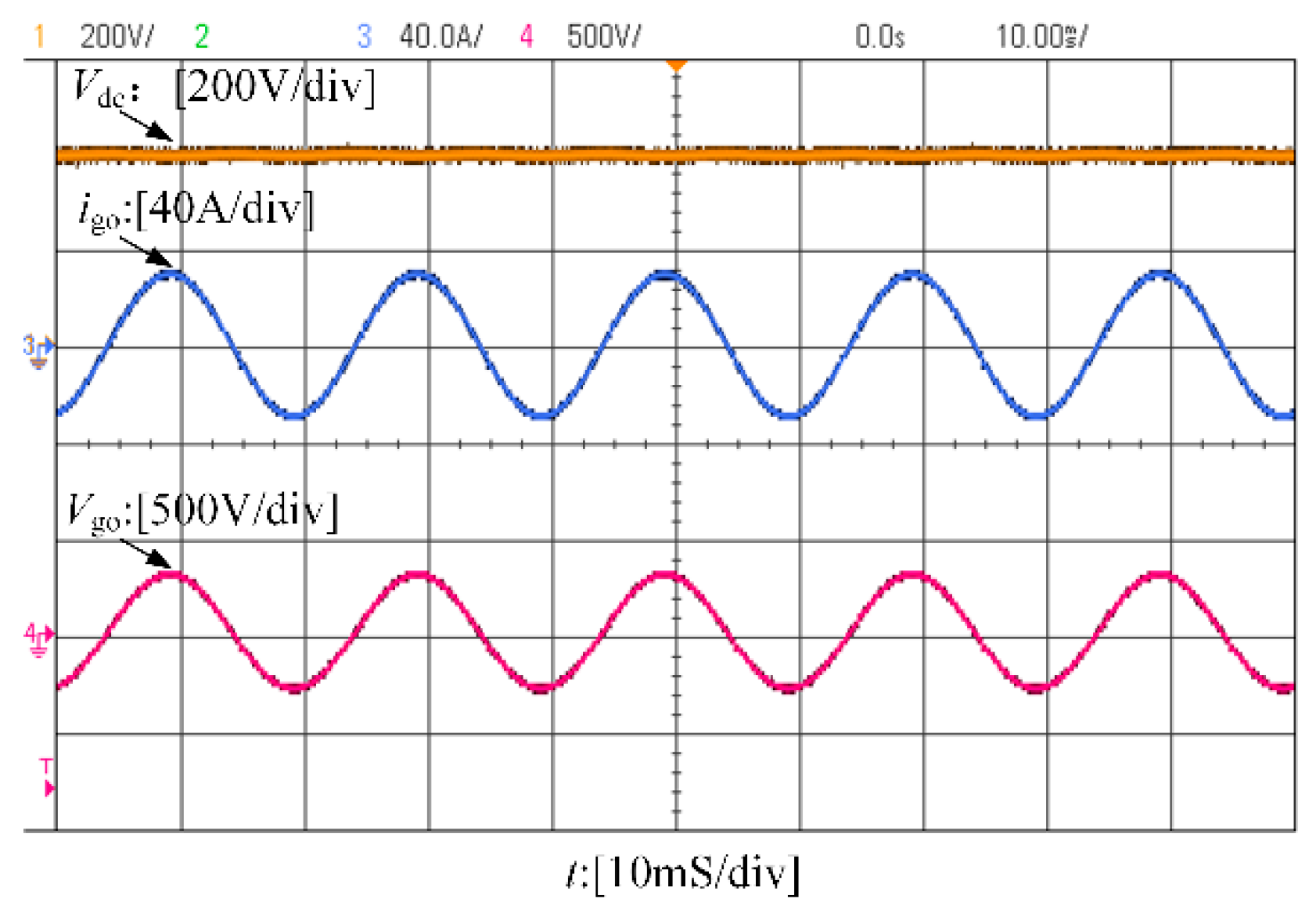

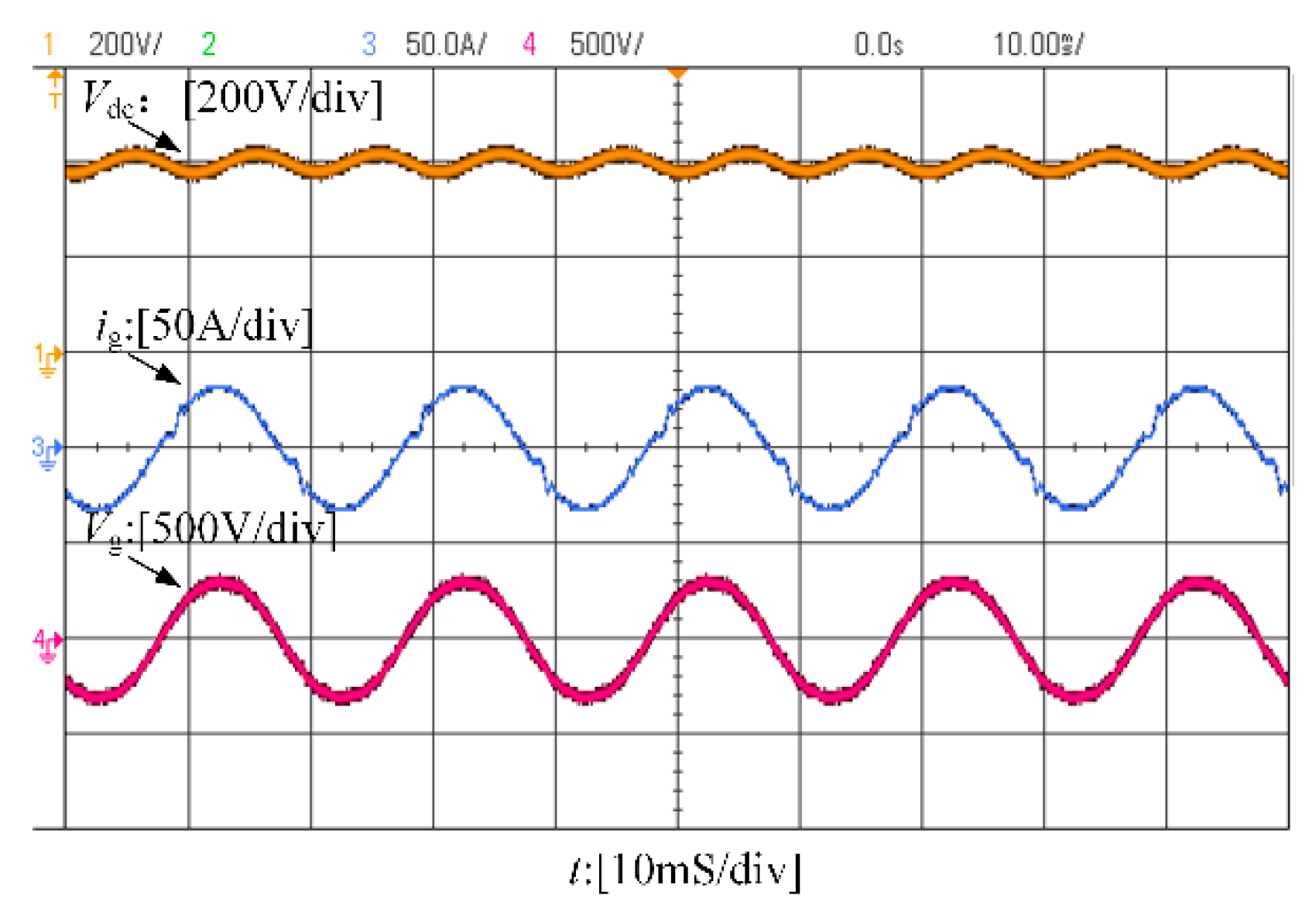

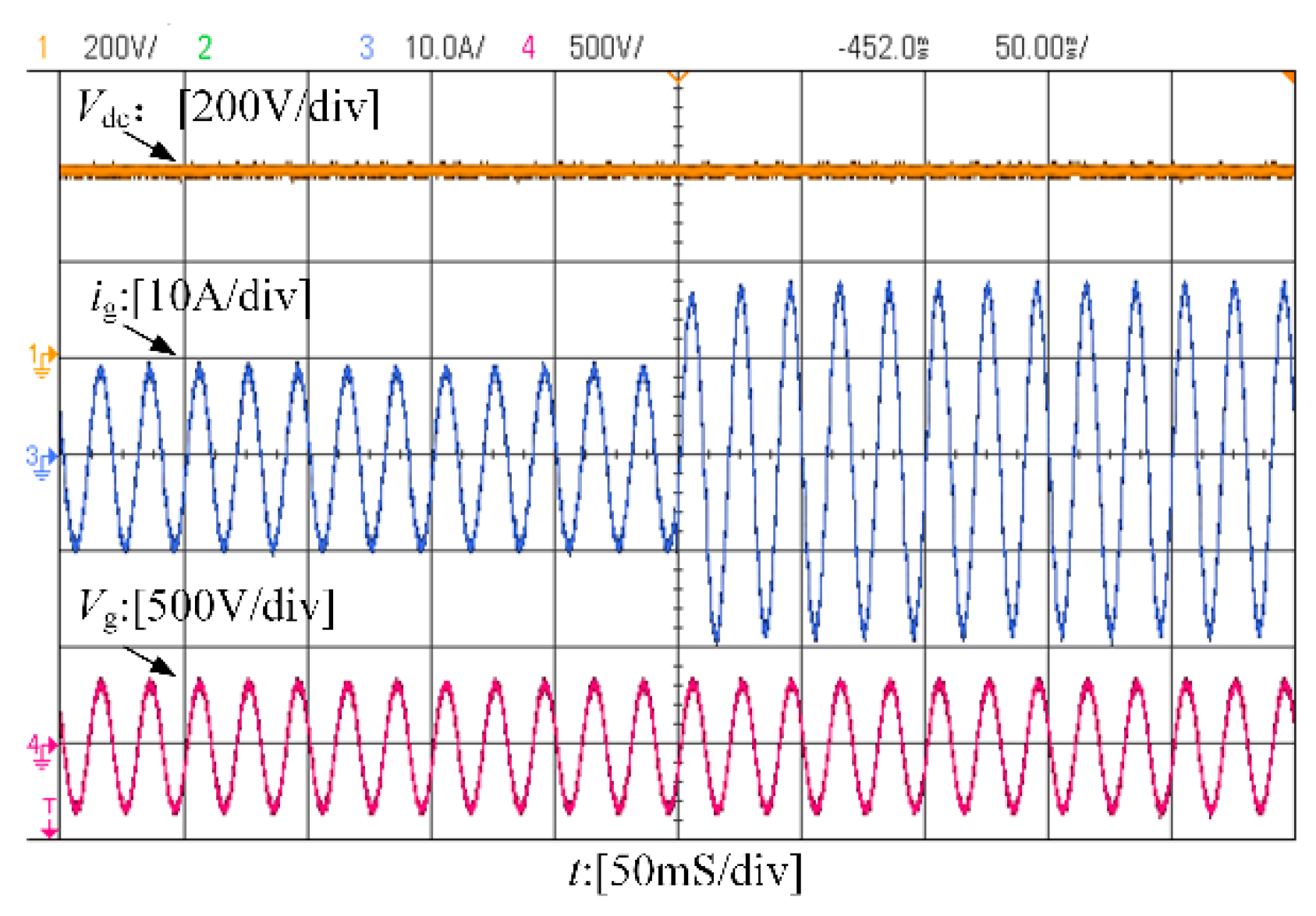

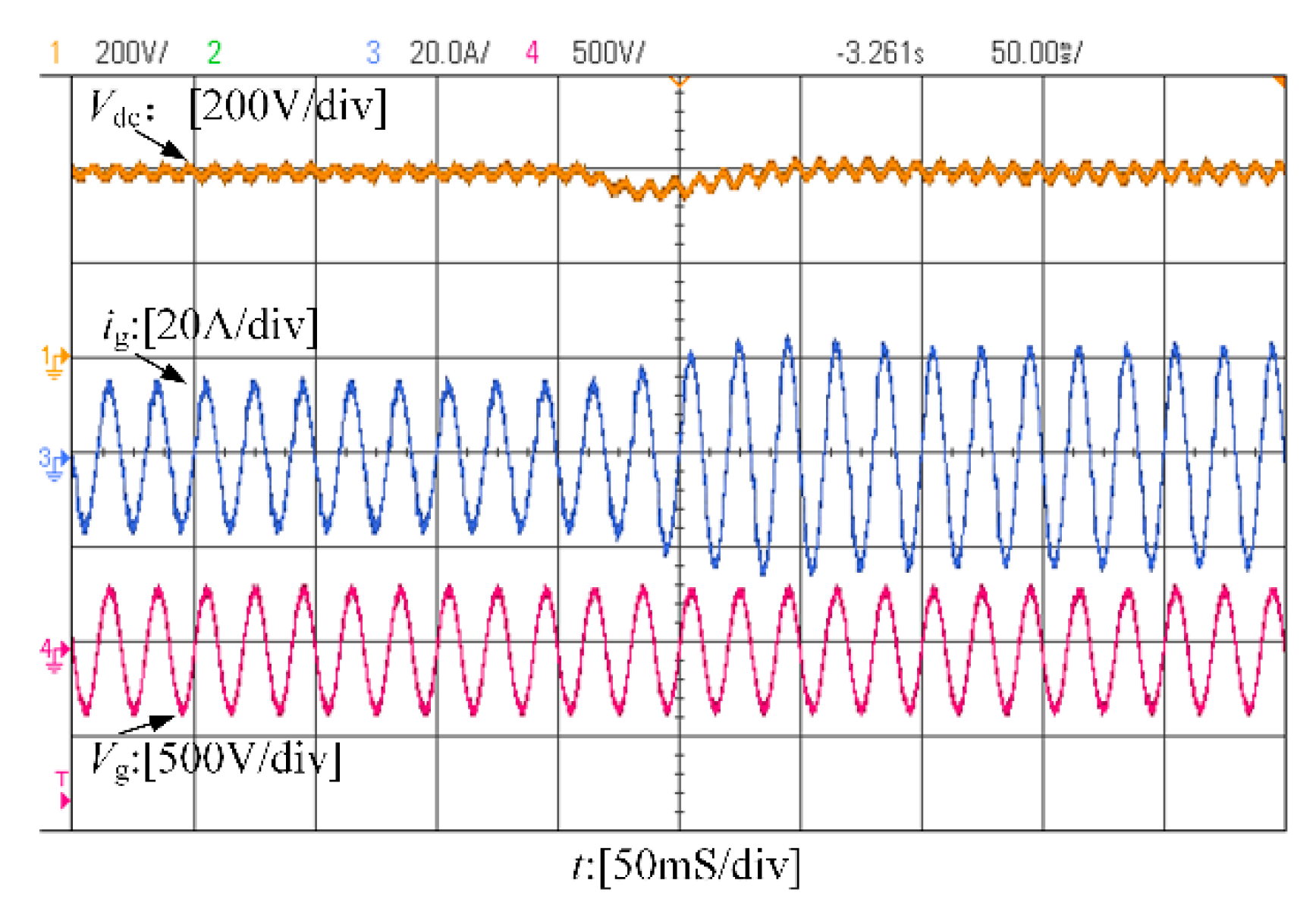

4. Experimental Result

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zhang, C.; Jiang, D.; Zhang, X.; Chen, J.; Ruan, C.; Liang, Y. The Study of a Battery Energy Storage System Based on the Hexagonal Modular Multilevel Direct AC/AC Converter (Hexverter). IEEE Access 2018, 6, 43343–43355. [Google Scholar] [CrossRef]

- Vavilapalli, S.; Subramaniam, U.; Padmanaban, S.; Ramachandaramurthy, V.K. Design and Real-Time Simulation of an AC Voltage Regulator Based Battery Charger for Large-Scale PV-Grid Energy Storage Systems. IEEE Access 2017, 5, 25158–25170. [Google Scholar] [CrossRef]

- Li, R.; Wang, W.; Xia, M. Cooperative Planning of Active Distribution System With Renewable Energy Sources and Energy Storage Systems. IEEE Access 2018, 6, 5916–5926. [Google Scholar] [CrossRef]

- Liu, Y.; Su, M.; Liu, F.; Zheng, M.; Liang, X.; Xu, G.; Sun, Y. Single-Phase Inverter With Wide Input Voltage and Power Decoupling Capability. IEEE Access 2019, 7, 16870–16879. [Google Scholar] [CrossRef]

- Ohnuma, Y.; Orikawa, K.; Itoh, J. A Single-Phase Current-Source PV Inverter With Power Decoupling Capability Using an Active Buffer. IEEE Trans. Ind. Appl. 2015, 51, 531–538. [Google Scholar] [CrossRef]

- Xu, S.; Shao, R.; Chang, L. Single-phase voltage source inverter with voltage-boosting and power decoupling capabilities. In Proceedings of the IEEE 8th International Symposium on Power Electronics for Distributed Generation Systems, Florianopolis, Brazil, 17–20 April 2017. [Google Scholar]

- Chen, C.; Chen, Y.; Tan, Y.; Fang, J.; Luo, F.; Kang, Y. On the Practical Design of a High Power Density SiC Single-Phase Uninterrupted Power Supply System. IEEE Trans. Ind. Inf. 2017, 13, 2704–2716. [Google Scholar] [CrossRef]

- Ahsanuzzaman, S.M.; Prodić, A.; Johns, D.A. An Integrated High-Density Power Management Solution for Portable Applications Based on a Multioutput Switched-Capacitor Circuit. IEEE Trans. Power Electron. 2016, 31, 4305–4323. [Google Scholar] [CrossRef]

- Gambhir, A.; Mishra, S.K.; Joshi, A. Power Frequency Harmonic Reduction and its Redistribution for Improved Filter Design in Current-Fed Switched Inverter. IEEE Trans. Ind. Electron. 2019, 66, 4319–4333. [Google Scholar] [CrossRef]

- Wang, R.; Wang, F.; Boroyevich, D.; Burgos, R.; Lai, R.; Ning, P.; Rajashekara, K. A High Power Density Single-Phase PWM Rectifier With Active Ripple Energy Storage. IEEE Trans. Power Electron. 2011, 26, 1430–1443. [Google Scholar] [CrossRef]

- Nguyen, T.-T.; Cha, H.; Nguyen, B.L.-H.; Kim, H.-G. Novel T-type Dual-Buck Inverter with Minimum Number of Inductors. In Proceedings of the 2018 International Power Electronics Conference (IPEC 2018), Niigata, Japan, 20–24 May 2018; pp. 1046–1050. [Google Scholar]

- Hong, F.; Liu, J.; Ji, B.; Zhou, Y.; Wang, J.; Wang, C. Single Inductor Dual Buck Full-Bridge Inverter. IEEE Trans. Ind. Electron. 2015, 62, 4869–4877. [Google Scholar] [CrossRef]

- Yang, F.; Ge, H.; Yang, J.; Dang, R.; Wu, H. A Family of Dual-Buck Inverters With an Extended Low-Voltage DC-Input Port for Efficiency Improvement Based on Dual-Input Pulsating Voltage-Source Cells. IEEE Trans. Power Electron. 2018, 33, 3115–3128. [Google Scholar] [CrossRef]

- Nguyen, B.L.-H.; Cha, H.; Kim, H. Single-Phase Six-Switch Dual-Output Inverter Using Dual-Buck Structure. IEEE Trans. Power Electron. 2018, 33, 7894–7903. [Google Scholar] [CrossRef]

- Hong, F.; Liu, J.; Ji, B.; Zhou, Y.; Wang, J.; Wang, C. Interleaved Dual Buck Full-Bridge Three-Level Inverter. IEEE Trans. Power Electron. 2016, 31, 964–974. [Google Scholar] [CrossRef]

- Khan, A.A.; Cha, H. Dual-Buck-Structured High-Reliability and High-Efficiency Single-Stage Buck–Boost Inverters. IEEE Trans. Ind. Electron. 2018, 65, 3176–3187. [Google Scholar] [CrossRef]

- Meng, Z.; Wang, Y.-F.; Yang, L.; Li, W. High Frequency Dual-Buck Full-Bridge Inverter Utilizing a Dual-Core MCU and Parallel Algorithm for Renewable Energy Applications. Energies 2017, 10, 402. [Google Scholar] [CrossRef]

- Jiao, Y.; Lee, F.C. LCL Filter Design and Inductor Current Ripple Analysis for a Three-Level NPC Grid Interface Converter. IEEE Trans. Power Electron. 2015, 30, 4659–4668. [Google Scholar] [CrossRef]

- Zheng, X.; Xiao, L.; Lei, Y.; Wang, Z. Optimisation of LCL filter based on closed-loop total harmonic distortion calculation model of the grid-connected inverter. IEEE Trans. Power Electron. 2015, 8, 860–868. [Google Scholar] [CrossRef]

- Wu, T.F.; Misra, M.; Lin, L.C.; Hsu, C.W. An Improved Resonant Frequency Based Systematic LCL Filter Design Method for Grid-Connected Inverter. IEEE Trans. Ind. Electron. 2017, 64, 6412–6421. [Google Scholar] [CrossRef]

- Liu, Q.; Peng, L.; Kang, Y.; Tang, S.; Wu, D.; Qi, Y. A Novel Design and Optimization Method of an LCL Filter for a Shunt Active Power Filter. IEEE Trans. Ind. Electron. 2014, 61, 4000–4010. [Google Scholar] [CrossRef]

- Franklin, G.F. Feedback Control of Dynamic Systems, 2nd ed.; Addison-Wesley Longman: Boston, MA, USA, 1993. [Google Scholar]

- Zhou, L.; Zhou, X.; Chen, Y.; Lv, Z.; He, Z.; Wu, W.; Yang, L.; Yan, K.; Luo, A.; Guerrero, J.M. Inverter-Current-Feedback Resonance-Suppression Method for LCL-Type DG System to Reduce Resonance-Frequency Offset and Grid-Inductance Effect. IEEE Trans. Ind. Electron. 2018, 65, 7036–7048. [Google Scholar] [CrossRef]

- Wang, J.; Yan, J.D.; Jiang, L.; Zou, J. Delay-Dependent Stability of Single-Loop Controlled Grid-Connected Inverters with LCL Filters. IEEE Trans. Power Electron. 2016, 31, 743–757. [Google Scholar] [CrossRef]

- Parker, S.G.; McGrath, B.P.; Holmes, D.G. Regions of Active Damping Control for LCL Filters. IEEE Trans. Ind. Appl. 2014, 50, 424–432. [Google Scholar]

| Performance Index | Inductance (La/Lb) | Capacitance (Cf/Co) | Inductance Ratio K |

|---|---|---|---|

| Power Density | Inverse proportion | \ | Inverse proportion |

| Filtering | Proportion | Proportion | Inverse proportion |

| Stability | Inverse proportion | Inverse proportion | Proportion |

| Components | Values |

|---|---|

| Filter inductance Li | 0.5 mH |

| Filter inductance Lg | 0.167 mH |

| Filter capacitor Cf | 0.75 uF (WIMA film capacitor) |

| Filter capacitor Co | 880 uF(Rubycon) |

| Rated power | 5 kW |

| DC voltage | 400 V |

| AC voltage | 220 V(Valid value) |

| Switching frequency | 50 kHz |

| DSP | TMS320F28377D (Texas Instruments) |

| Power switches S1-S6 | CREE C3M0016120K |

| Diodes D1-D4 | CREE C3D30065D |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cui, Y.; Wang, Y.; Ma, X. Parameters Design and Optimization of a High Frequency, Interleaved, Dual-Buck, Bidirectional, Grid-Connected Converter. Electronics 2019, 8, 973. https://doi.org/10.3390/electronics8090973

Cui Y, Wang Y, Ma X. Parameters Design and Optimization of a High Frequency, Interleaved, Dual-Buck, Bidirectional, Grid-Connected Converter. Electronics. 2019; 8(9):973. https://doi.org/10.3390/electronics8090973

Chicago/Turabian StyleCui, Yulu, Yifeng Wang, and Xiaoyong Ma. 2019. "Parameters Design and Optimization of a High Frequency, Interleaved, Dual-Buck, Bidirectional, Grid-Connected Converter" Electronics 8, no. 9: 973. https://doi.org/10.3390/electronics8090973

APA StyleCui, Y., Wang, Y., & Ma, X. (2019). Parameters Design and Optimization of a High Frequency, Interleaved, Dual-Buck, Bidirectional, Grid-Connected Converter. Electronics, 8(9), 973. https://doi.org/10.3390/electronics8090973