A CMOS W-Band Amplifier with Tunable Neutralization Using a Cross-Coupled MOS–varactor Pair

Abstract

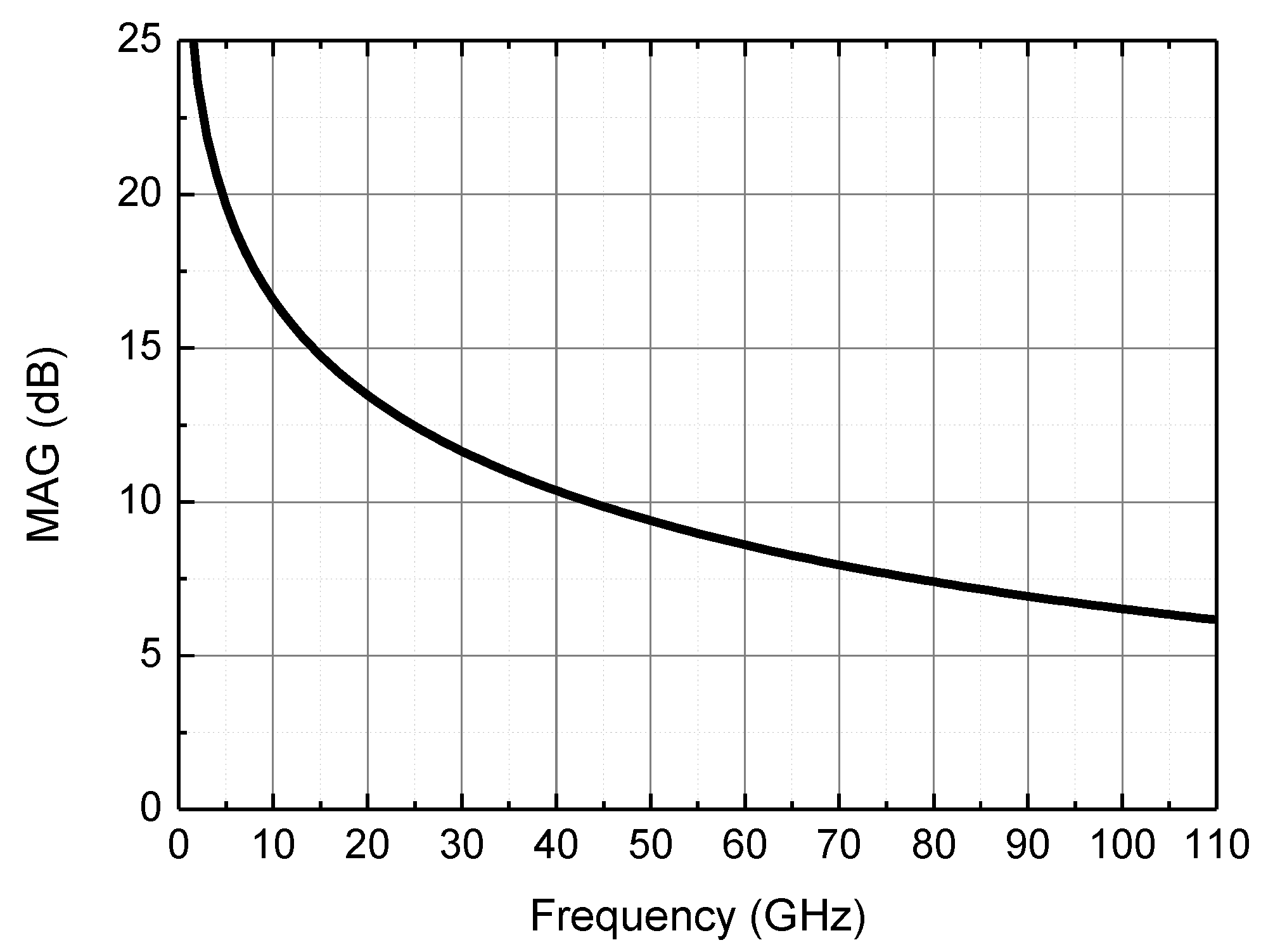

:1. Introduction

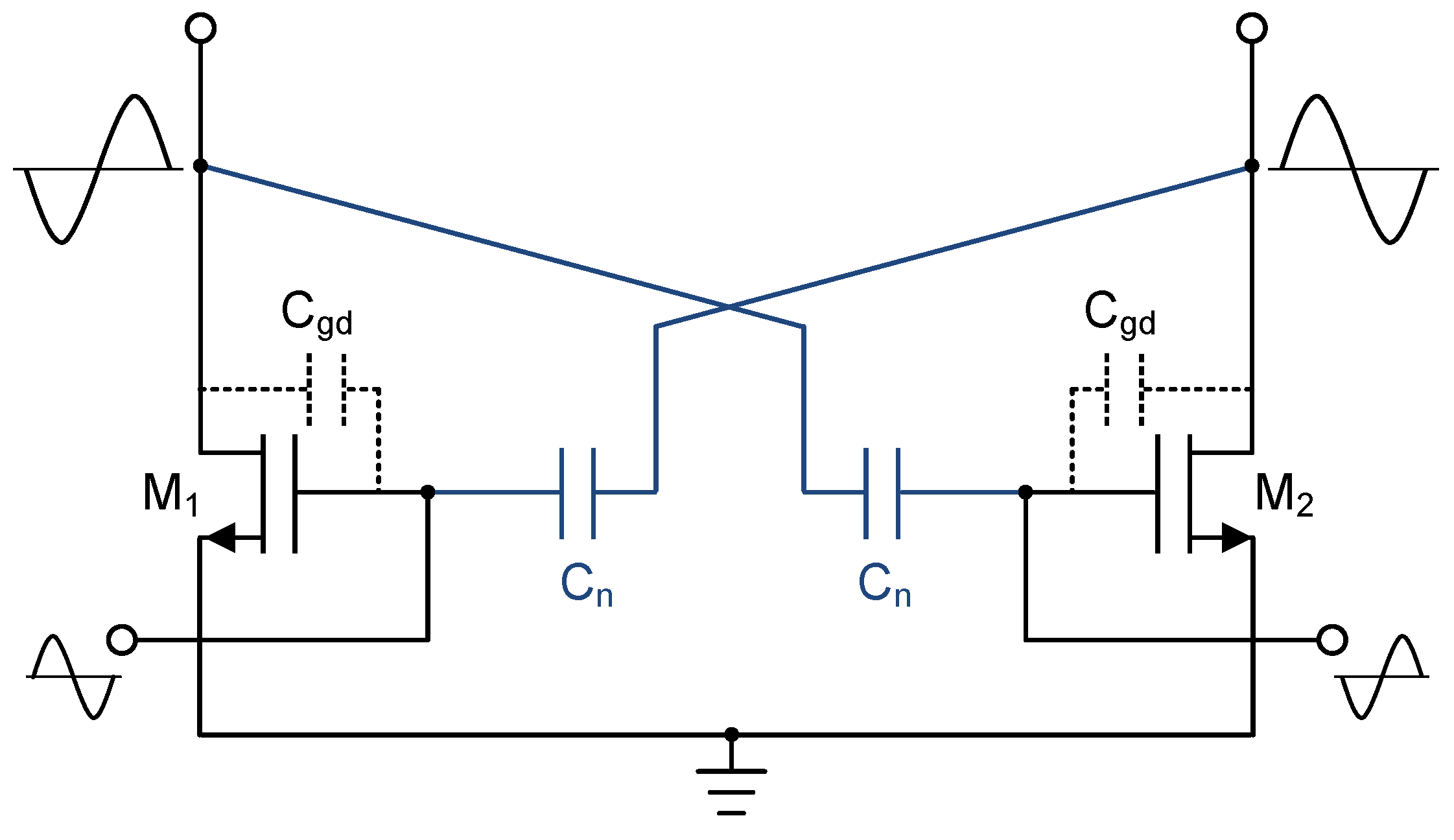

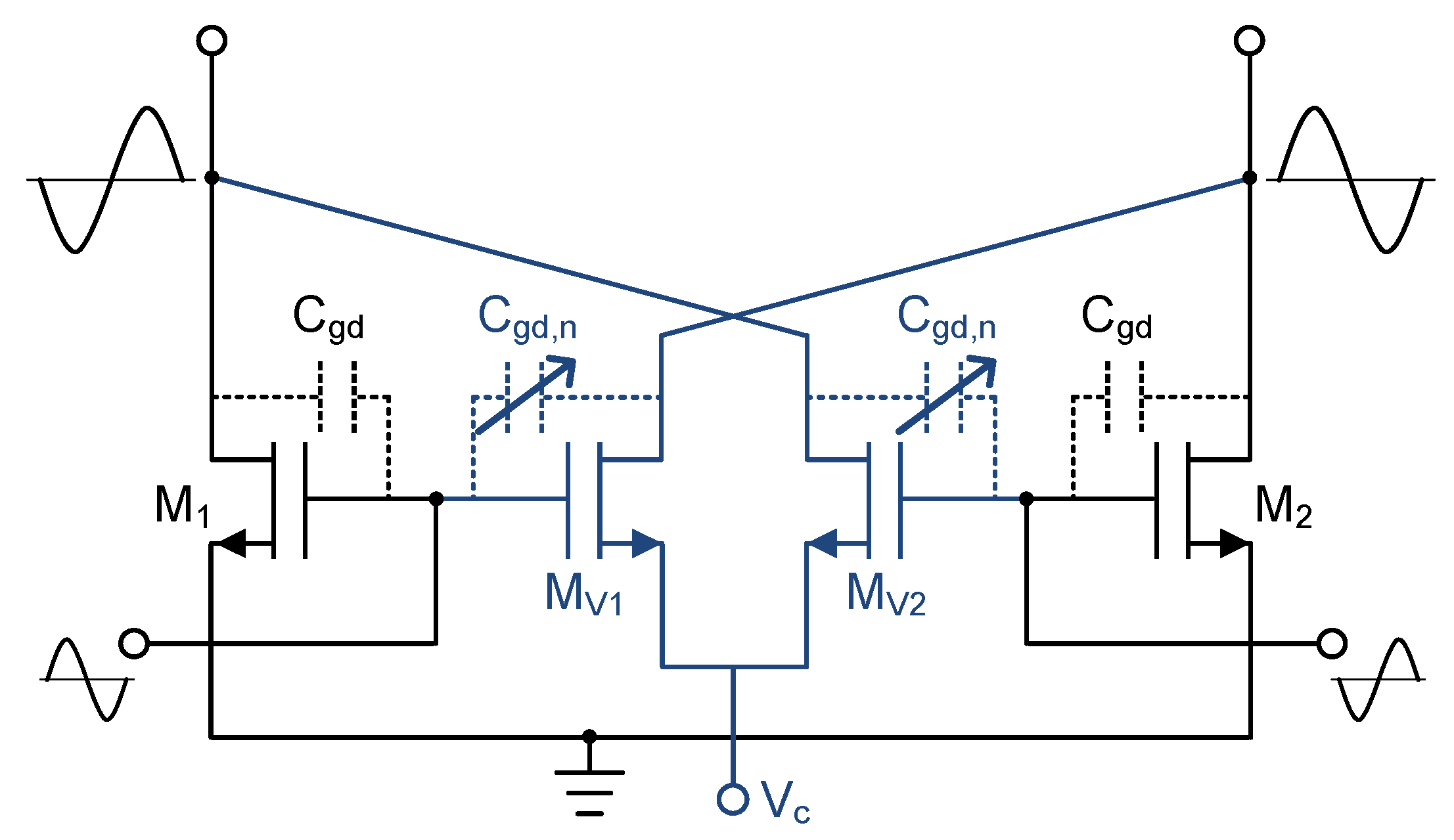

2. Conventional and Proposed Neutralization Techniques

2.1. Conventional Neutralization Techniques

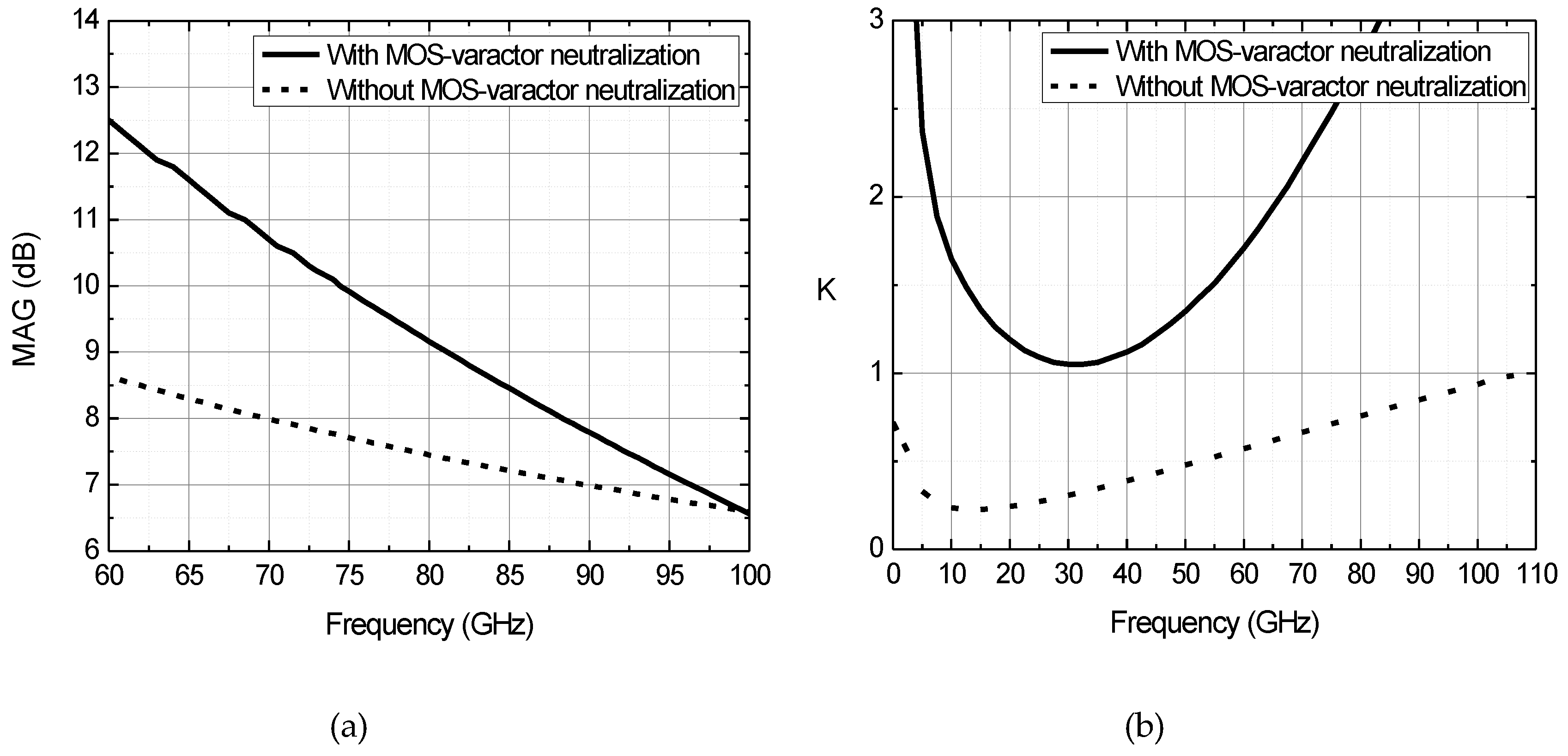

2.2. Proposed Tunable Neutralization Technique

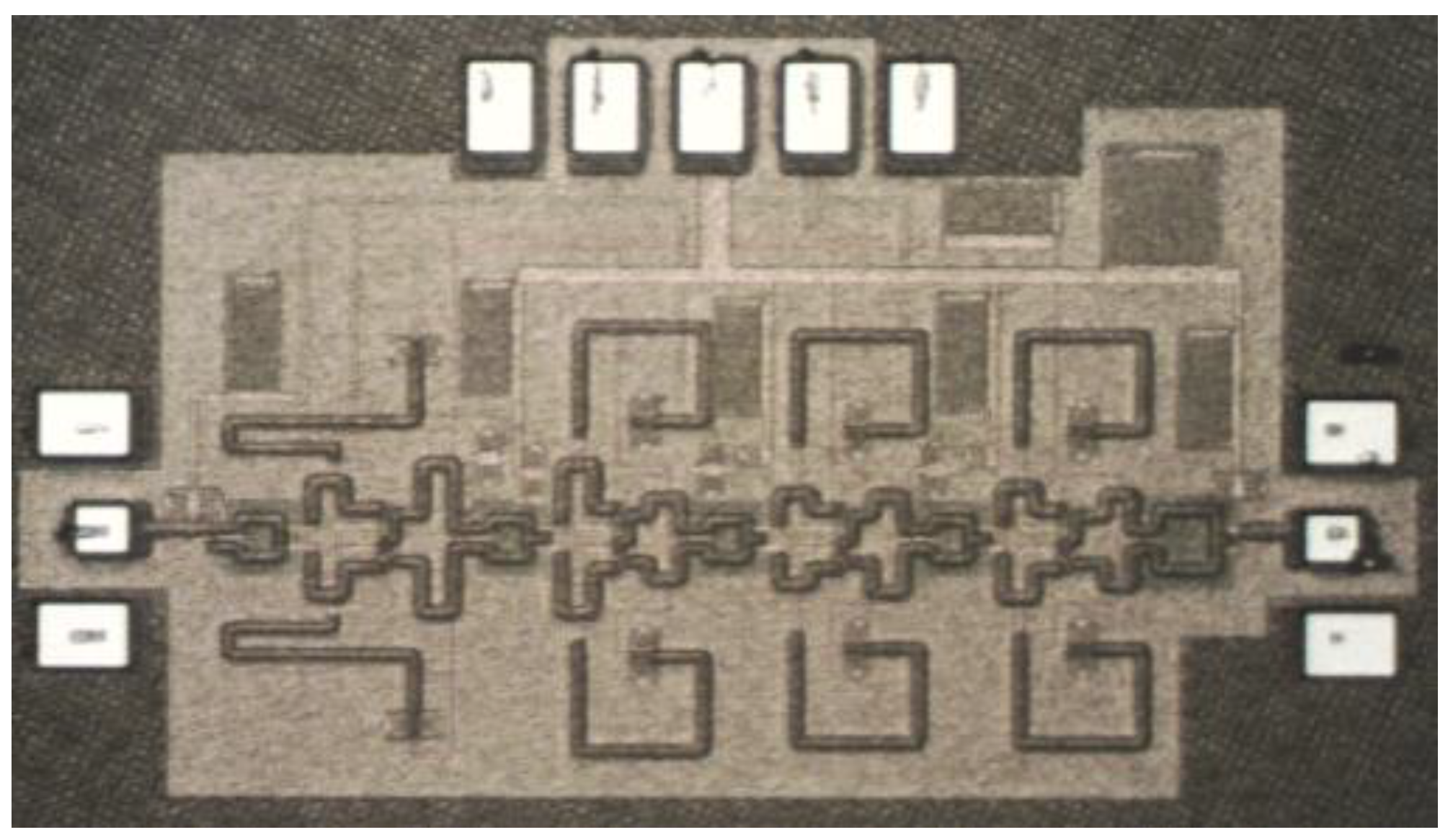

3. Design of CMOS W-Band Amplifier with Tunable Neutralization

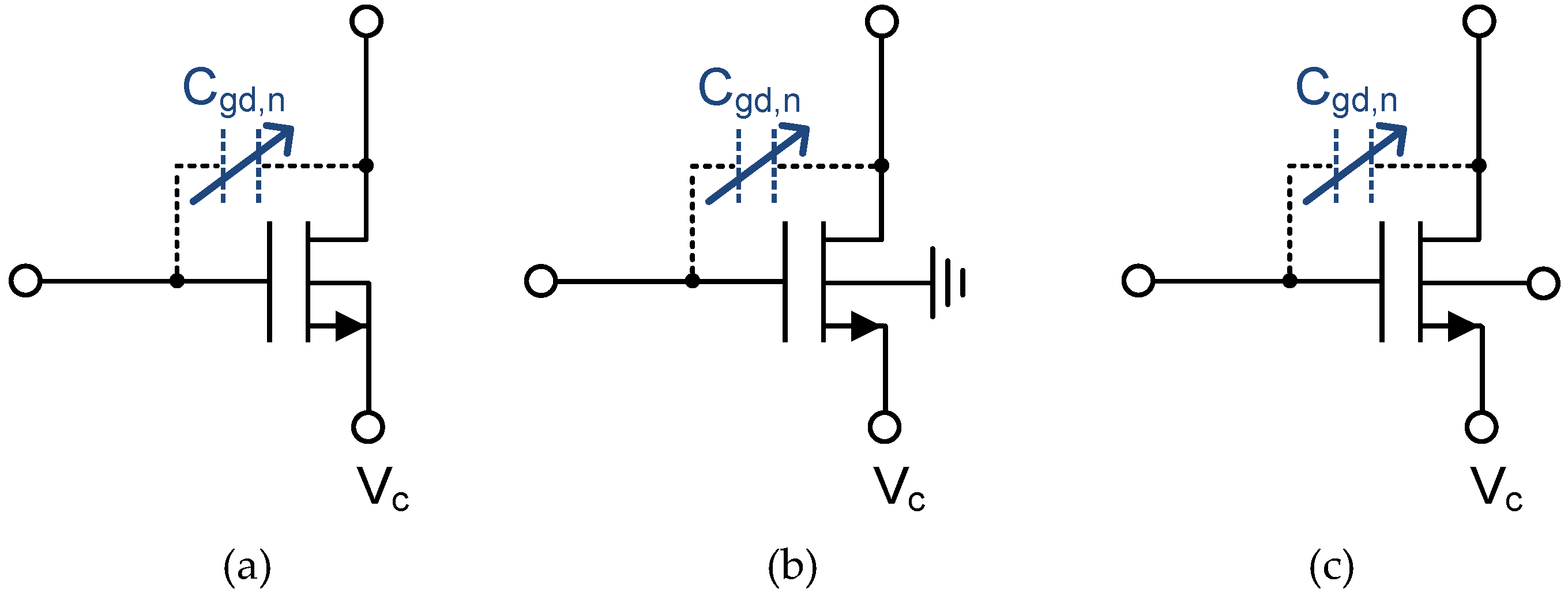

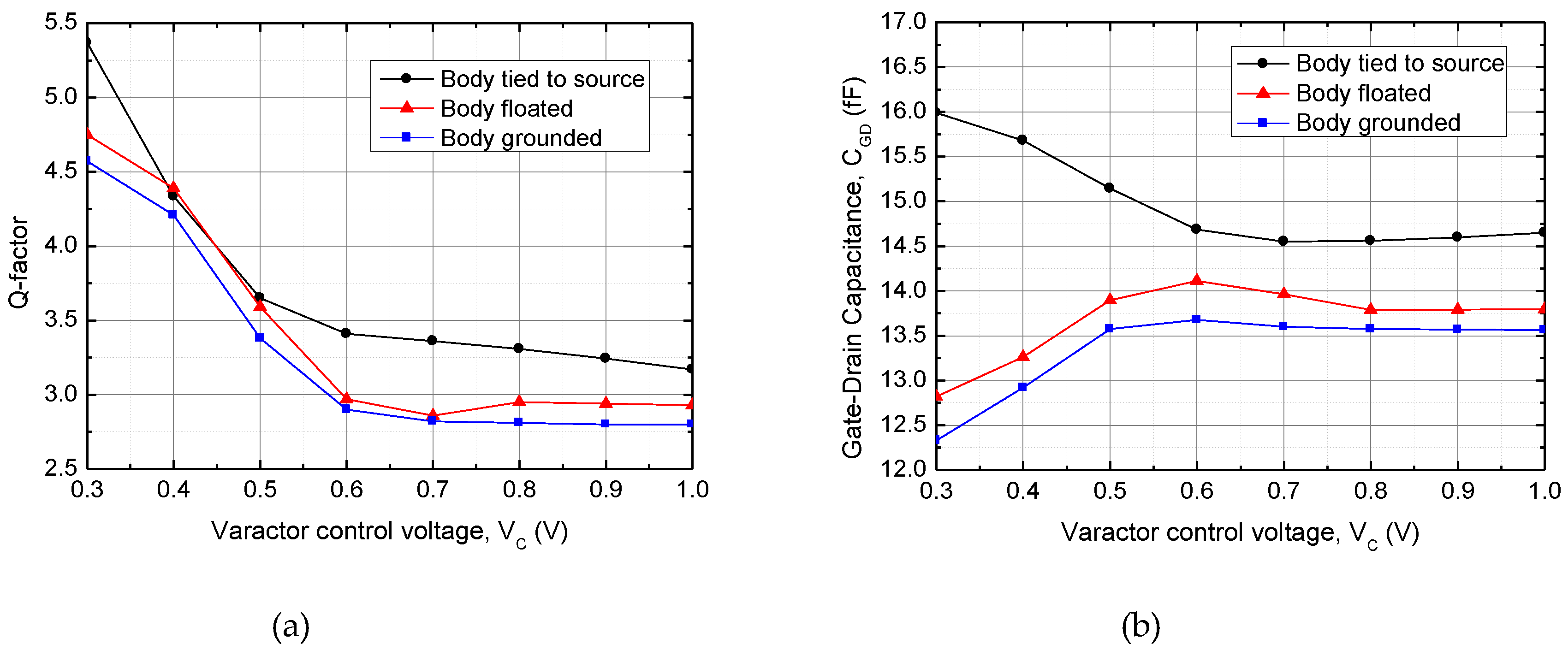

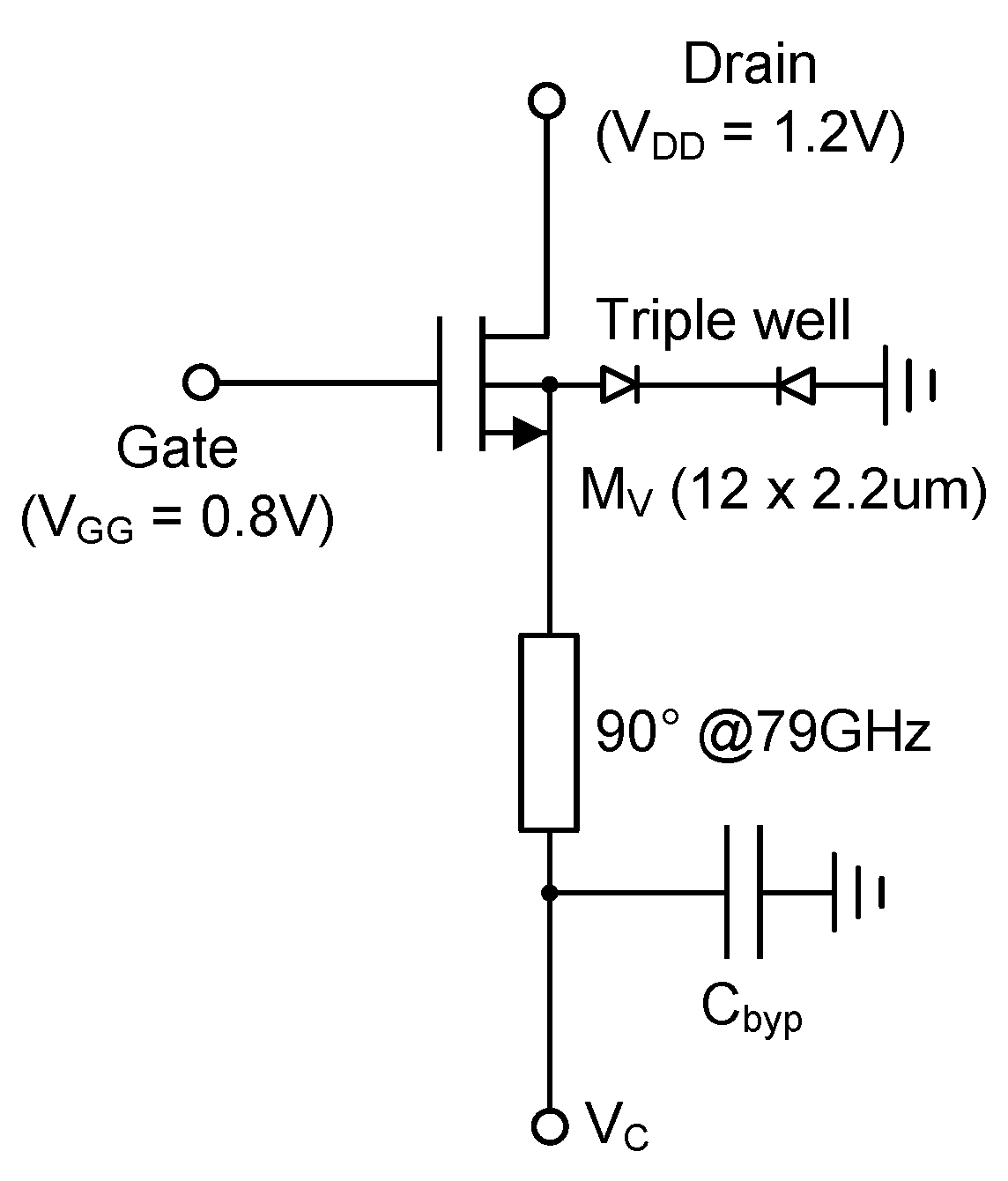

3.1. Implementation of MOS−Varactor

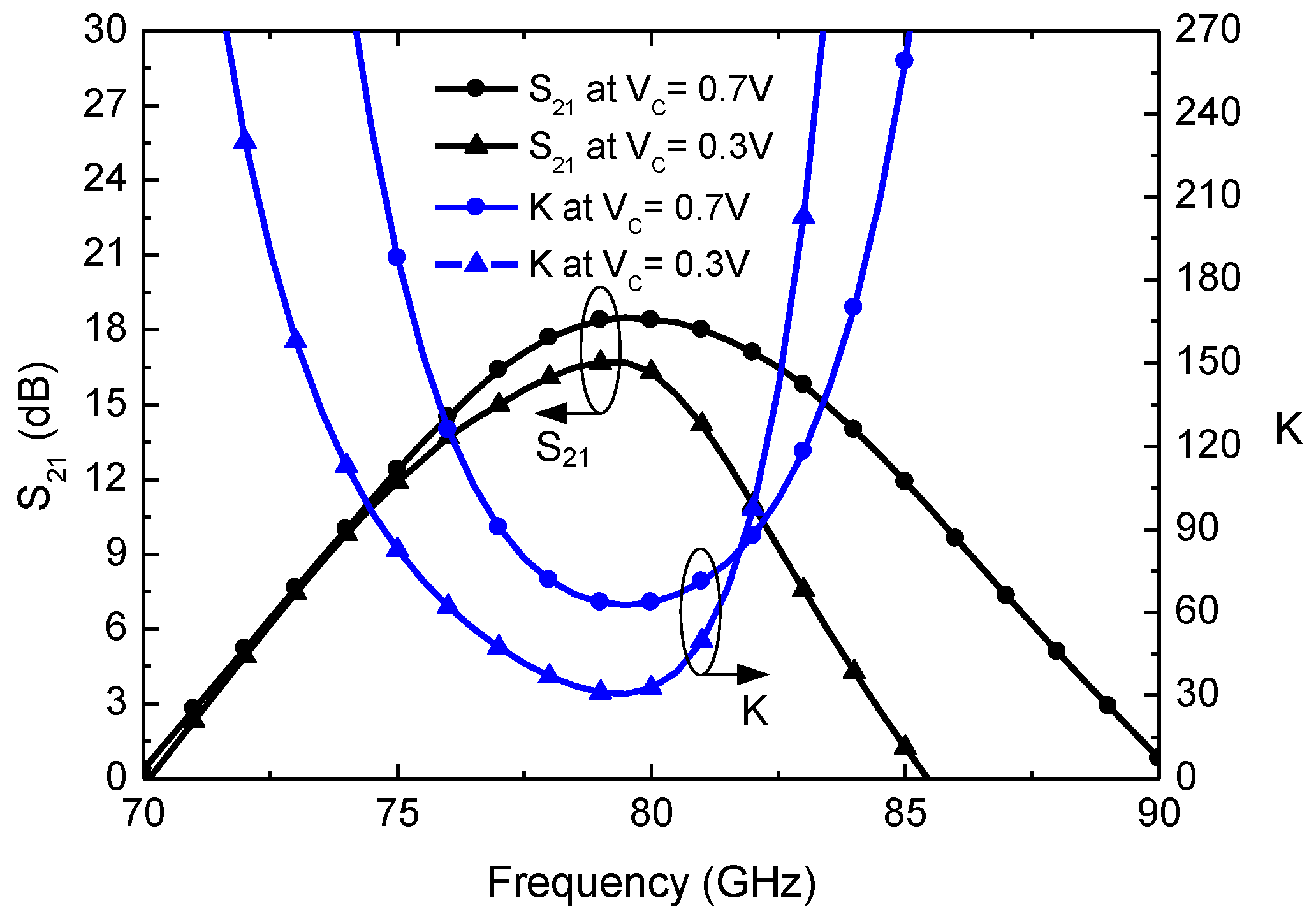

3.2. W-Band Amplifier Design with Tunable Neutralization

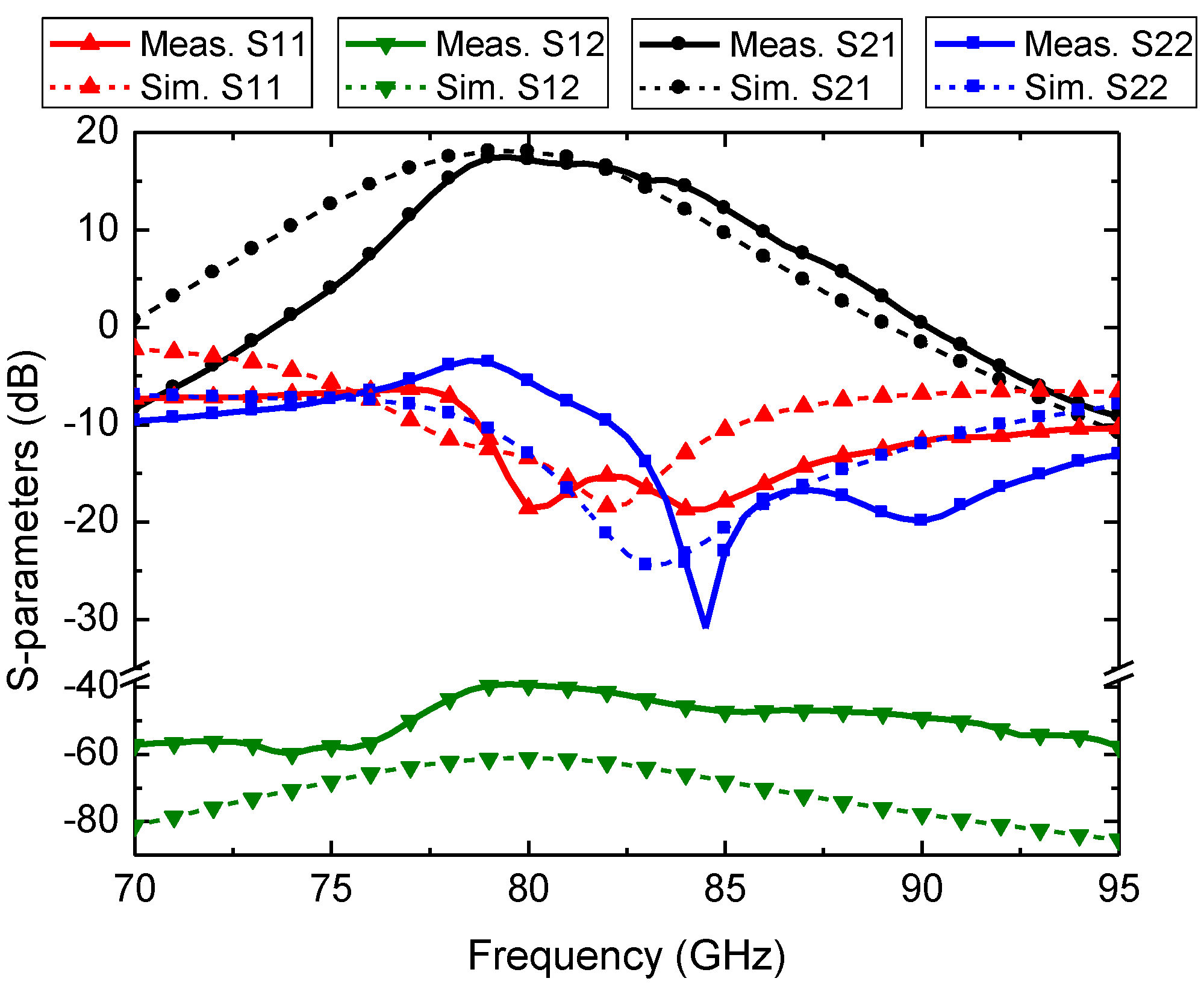

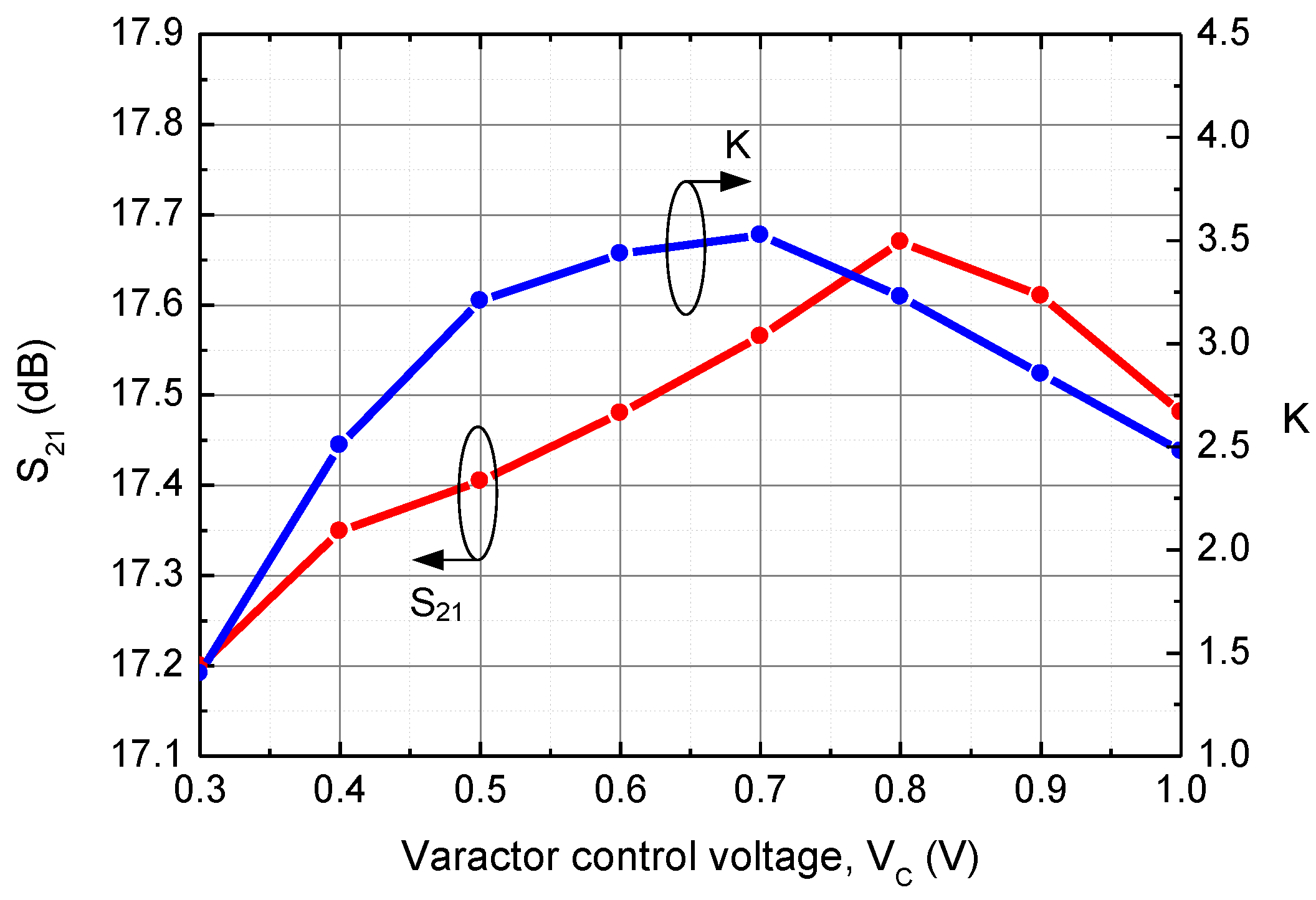

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ebrahimi, N.; Wu, P.-Y.; Bagheri, M.; Buckwalter, J.F. A 71-86 GHz phased-array transceiver using wideband injection-locked oscillator phase-shifters. IEEE Trans. Microw. Theory Technol. 2017, 65, 346–361. [Google Scholar] [CrossRef]

- Mitomo, T.; Ono, N.; Hoshino, H.; Yoshihara, Y.; Watanabe, I.; Seto, I. A 77 GHz 90 nm CMOS transceiver for FMCW radar applications. IEEE J. Solid-State Circuits 2010, 45, 928–937. [Google Scholar] [CrossRef]

- Zhou, L.; Wang, C.-C.; Chen, Z.; Heydari, P. A W-band CMOS receiver chipset for millimeter-wave radiometer systems. IEEE J. Solid-State Circuits 2011, 46, 378–391. [Google Scholar] [CrossRef]

- Oka, S.; Togo, H.; Kukutsu, N.; Nagatsuma, T. Latest trends in millimeter-wave imaging technology. Prog. Electromagn. Res. Lett. 2008, 1, 197–204. [Google Scholar] [CrossRef]

- Choi, W.; Jung, G.; Kim, J.; Kwon, Y. Scalable small-signal modeling of RF CMOS FET based on 3-D EM-based extraction of parasitic effects and its application to millimeter-wave amplifier design. IEEE Trans. Microw. Theory Technol. 2009, 57, 3345–3353. [Google Scholar] [CrossRef]

- Crupi, G.; Schreurs, D.M.M.-P.; Caddemi, A. Effects of gate-length scaling on microwave MOSFET performance. Electronics 2017, 6, 62. [Google Scholar] [CrossRef]

- Yoo, J.; Rieh, J.-S. CMOS 120 GHz phase-locked loops based on two different VCO topologies. J. Electromagn. Eng. Sci. 2017, 17, 98–104. [Google Scholar] [CrossRef]

- Guo, S.; Xi, T.; Gui, P.; Zhang, J.; Choi, W.; Kenneth, K.O.; Fan, Y.; Huang, D.; Gu, R.; Morgan, M. 54 GHz CMOS LNAs with 3.6 dB NF and 28.2 dB gain using transformer feedback Gm-boosting technique. In Proceedings of the 2014 IEEE Asian Solid-State Circuits Conference, KaoHsiung, Taiwan, 10–12 November 2014. [Google Scholar]

- Cohen, E.; Degani, O.; Ritter, D. A wideband gain-boosting 8mW LNA with 23dB gain and 4dB NF in 65nm CMOS process for 60 GHz applications. In Proceedings of the 2012 IEEE Radio Frequency Integrated Circuits Symposium, Montreal, QC, Canada, 17–19 June 2012. [Google Scholar]

- Chan, W.L.; Long, J.R. A 58–65 GHz neutralized CMOS power amplifier with PAE above 10% at 1-V supply. IEEE J. Solid-State Circuits 2010, 45, 554–564. [Google Scholar] [CrossRef]

- Wang, Z.; Chiang, P.; Nazari, P.; Wang, C.; Chen, Z.; Heydari, P. A CMOS 210-GHz fundamental transceiver with OOK modulation. IEEE J. Solid-State Circuits 2014, 49, 564–580. [Google Scholar] [CrossRef]

- Deferm, N.; Reynaert, P. A 100 GHz transformer-coupled fully differential amplifier in 90 nm CMOS. In Proceedings of the 2010 IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, USA, 23–25 May 2010. [Google Scholar]

- Minami, R.; Matsushita, K.; Asada, H.; Okada, K.; Matsuzawa, A. A 60 GHz CMOS power amplifier using varactor cross-coupling neutralization with adaptive bias. In Proceedings of the 2011 Asia-Pacific Microwave Conference, Melbourne, VIC, Australia, 5–8 December 2011. [Google Scholar]

- Ali, S.N.; Agarwal, P.; Renaud, L.; Molavi, R.; Mirabbasi, S.; Pande, P.P.; Heo, D. A 40% PAE frequency-reconfigurable CMOS power amplifier with tunable gate–drain neutralization for 28-GHz 5G radios. IEEE Trans. Microw. Theory Technol. 2018, 66, 2231–2245. [Google Scholar] [CrossRef]

- Pozar, D.M. Microwave Engineering, 4th ed.; Wiley: Hoboken, NJ, USA, 2012; pp. 558–570. [Google Scholar]

- Li, Y.-A.; Hung, M.-H.; Huang, S.-J.; Lee, J. A fully integrated 77GHz FMCW radar system in 65nm CMOS. In Proceedings of the 2010 IEEE international Solid-State Circuits Conference, San Francisco, CA, USA, 7–11 February 2010. [Google Scholar]

- Le, H.V.; Duong, H.T.; Ta, C.M.; Huynh, A.T.; Evans, R.J.; Skafidas, E. A 77-GHz CMOS low noise amplifier for automotive radar. In Proceedings of the 2012 IEEE International Symposium on Radio Frequency Integration Technology, Singapore, 21–23 November 2012. [Google Scholar]

- Khanpour, M.; Tang, K.W.; Garcia, P.; Voinigescu, S.P. A wideband W-band receiver front-end in 65-nm CMOS. IEEE J. Solid-State Circuits 2008, 43, 1717–1730. [Google Scholar] [CrossRef]

- Lee, C.J.; Lee, H.J.; Lee, J.G.; Jang, T.H.; Park, C.S. A W-band CMOS low power wideband low noise amplifier with 22 dB gain and 3 dB bandwidth of 20 GHz. In Proceedings of the 2015 IEEE Asia-Pacific Microwave Conference, Nanjing, China, 6–9 December 2015. [Google Scholar]

- Mineyama, A.; Kawano, Y.; Sato, M.; Suzuki, T.; Hara, N.; Joshin, K. A millimeter-wave CMOS low noise amplifier using transformer neutralization techniques. In Proceedings of the 2011 Asia-Pacific Microwave Conference, Melbourne, VIC, Australia, 5–8 December 2011. [Google Scholar]

- Chuang, L.; Reza, M.; Arthur, H.-M.; Van, R.; Paul, V.-Z. A 107GHz LNA in 65nm CMOS with inductive neutralization and slow-wave transmission lines. In Proceedings of the 2012 19th IEEE Symposium on Communications and Vehicular Technology (SCVT), Eindhoven, The Netherland, 16 November 2012. [Google Scholar]

| Ref. | Technology | Frequency (GHz) | Gain (dB) | 3-dB BW (GHz) | PDC (mW) | Chip size (mm2) | Neutralization |

|---|---|---|---|---|---|---|---|

| [16] | 65-nm CMOS | 77 | 17.5 | - | 30 | - | - |

| [17] | 65-nm CMOS | 77 | 11 | 3 * | 25.8 | 0.3 | - |

| [18] | 65-nm CMOS | 80 | 13.5 | 19 | 47 | - | - |

| [19] | 65-nm CMOS | 84 | 22 | 20 | 21 | 0.45 | - |

| [3] | 65-nm CMOS | 86 | 15 | 12 | 42 | - | - |

| [20] | 65-nm CMOS | 79 | 9.4 | 15 | 9.7 | 0.38 | Fixed |

| [12] | 65-nm CMOS | 99 | 11 | 11 | 94 | 0.87 | Fixed |

| [21] | 65-nm CMOS | 107 ** | 10.2 ** | 16 ** | 28.2 ** | - | Fixed |

| This work | 65-nm CMOS | 79 | 17.5 | 6.5 | 56.7 | 0.85 | Tunable |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yook, B.; Park, K.; Park, S.; Lee, H.; Kim, T.; Park, J.S.; Jeon, S. A CMOS W-Band Amplifier with Tunable Neutralization Using a Cross-Coupled MOS–varactor Pair. Electronics 2019, 8, 537. https://doi.org/10.3390/electronics8050537

Yook B, Park K, Park S, Lee H, Kim T, Park JS, Jeon S. A CMOS W-Band Amplifier with Tunable Neutralization Using a Cross-Coupled MOS–varactor Pair. Electronics. 2019; 8(5):537. https://doi.org/10.3390/electronics8050537

Chicago/Turabian StyleYook, Byungho, Kwangwon Park, Seungwon Park, Hyunkyu Lee, Taehoon Kim, Jong Sung Park, and Sanggeun Jeon. 2019. "A CMOS W-Band Amplifier with Tunable Neutralization Using a Cross-Coupled MOS–varactor Pair" Electronics 8, no. 5: 537. https://doi.org/10.3390/electronics8050537

APA StyleYook, B., Park, K., Park, S., Lee, H., Kim, T., Park, J. S., & Jeon, S. (2019). A CMOS W-Band Amplifier with Tunable Neutralization Using a Cross-Coupled MOS–varactor Pair. Electronics, 8(5), 537. https://doi.org/10.3390/electronics8050537