Towards Silicon Carbide VLSI Circuits for Extreme Environment Applications

Abstract

1. Introduction

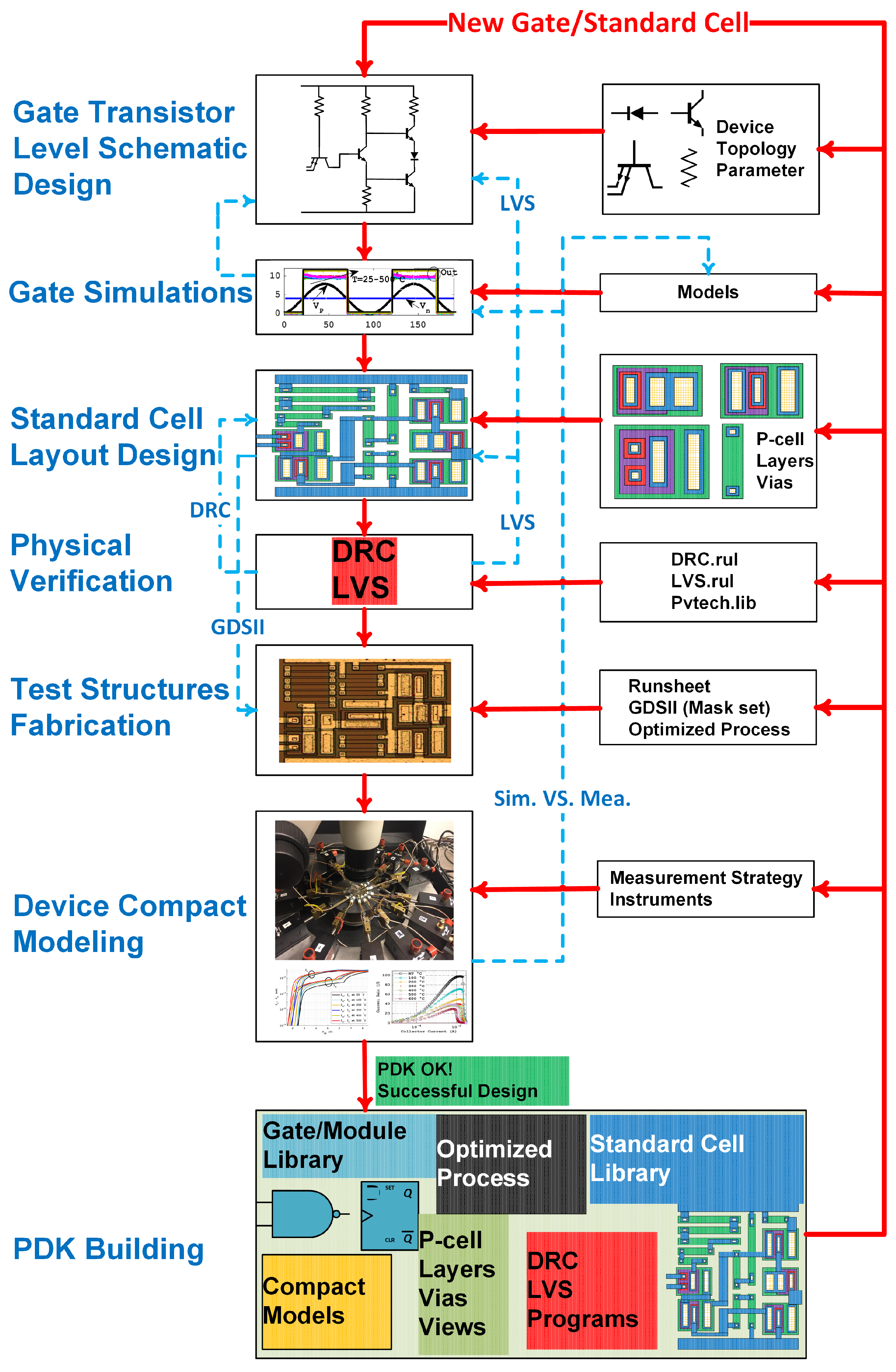

2. Methodology

2.1. Development of Process Design Kit

2.1.1. Gate Library (Gate Transistor Level Schematic Design)

2.1.2. Gate Library Simulations

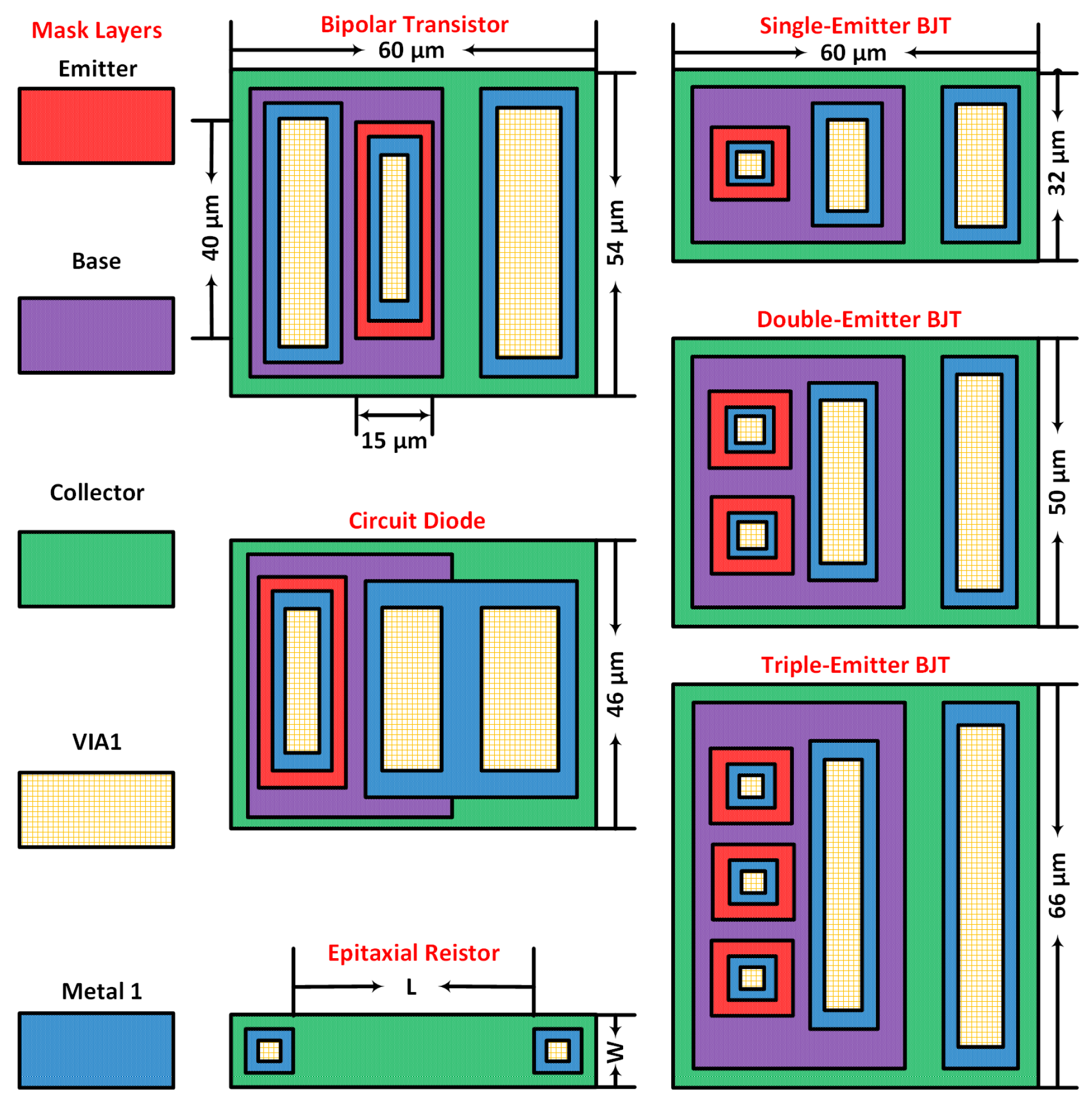

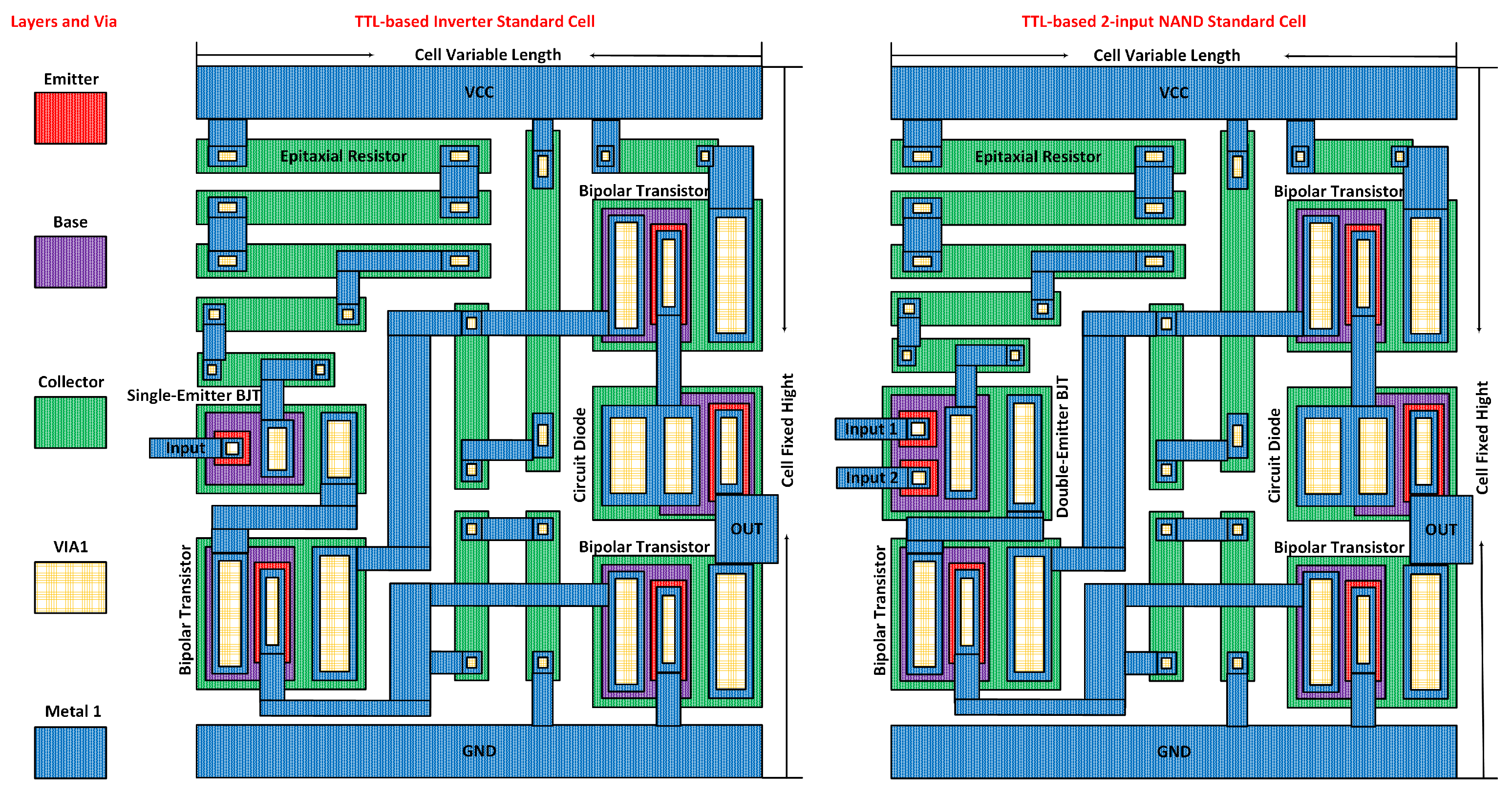

2.1.3. Standard Cell Layout Design and Library

2.1.4. Physical Verification

2.1.5. Test-structures HT Measurements and Modeling

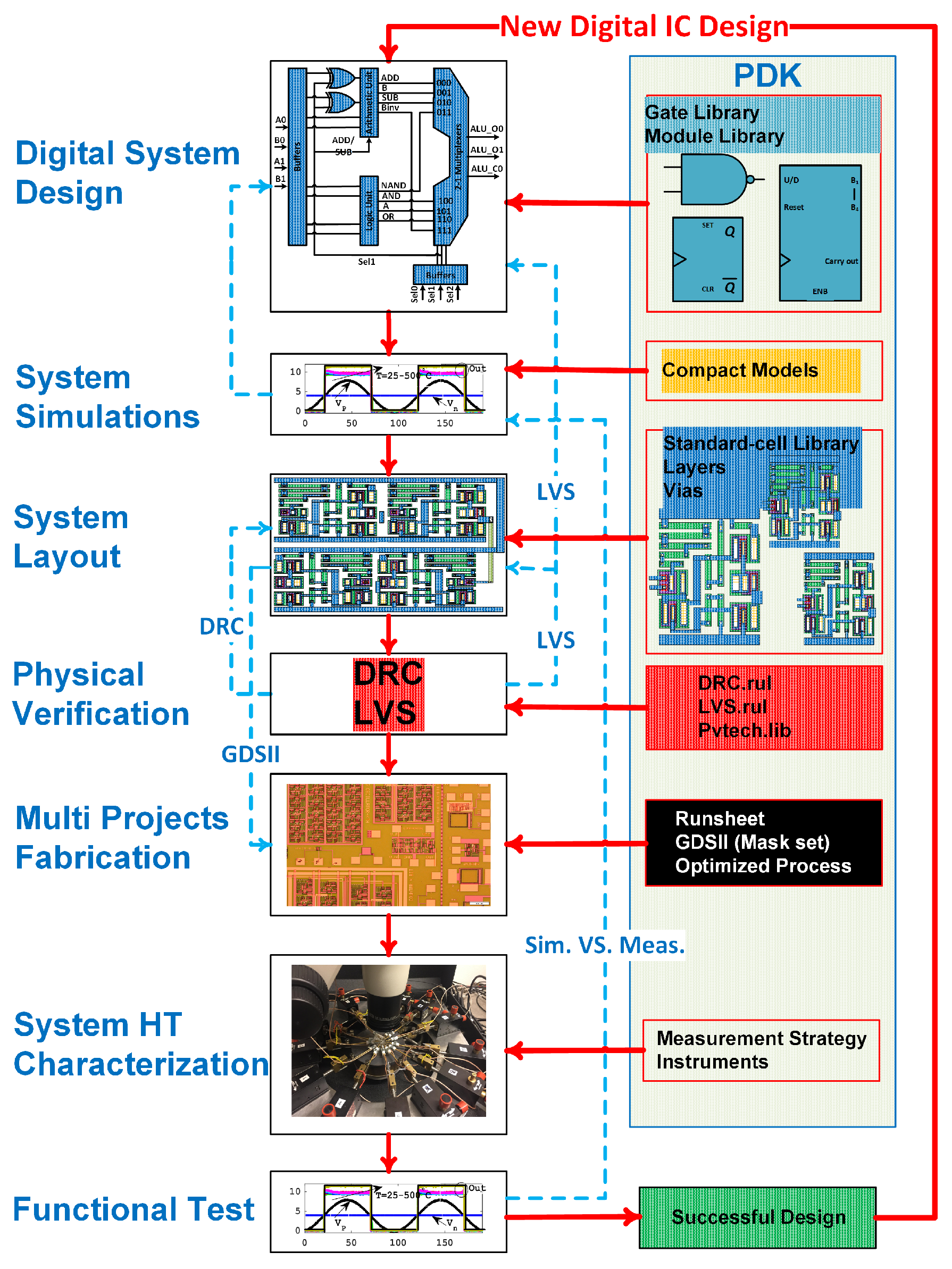

2.2. Digital ICs Realization with SiC TTL PDK

2.2.1. Digital Circuit Design

2.2.2. Layout Implementation and Verification

2.2.3. Fabrication

2.2.4. Measurement Setup

3. Results

3.1. Device Design and Characterization

3.1.1. N-P-N Bipolar Transistor

3.1.2. SiC BJT HT Characteristics Analysis for Designing the TTL-Based Digital Circuits

3.1.3. Resistors Realized in the Collector Layer

3.2. SiC TTL Digital Gates

3.2.1. TTL Inverter Design and Characterization

3.2.2. PDK Gates HT Characterization

3.3. SiC TTL-Based Combinational ICs

3.3.1. Decoder and Multiplexer

3.3.2. 1-Bit Adder

3.3.3. Arithmetic and Logic Unit (ALU)

3.4. SiC TTL-Based Sequential ICs

3.4.1. Data-type Flip-Flop (DFF)

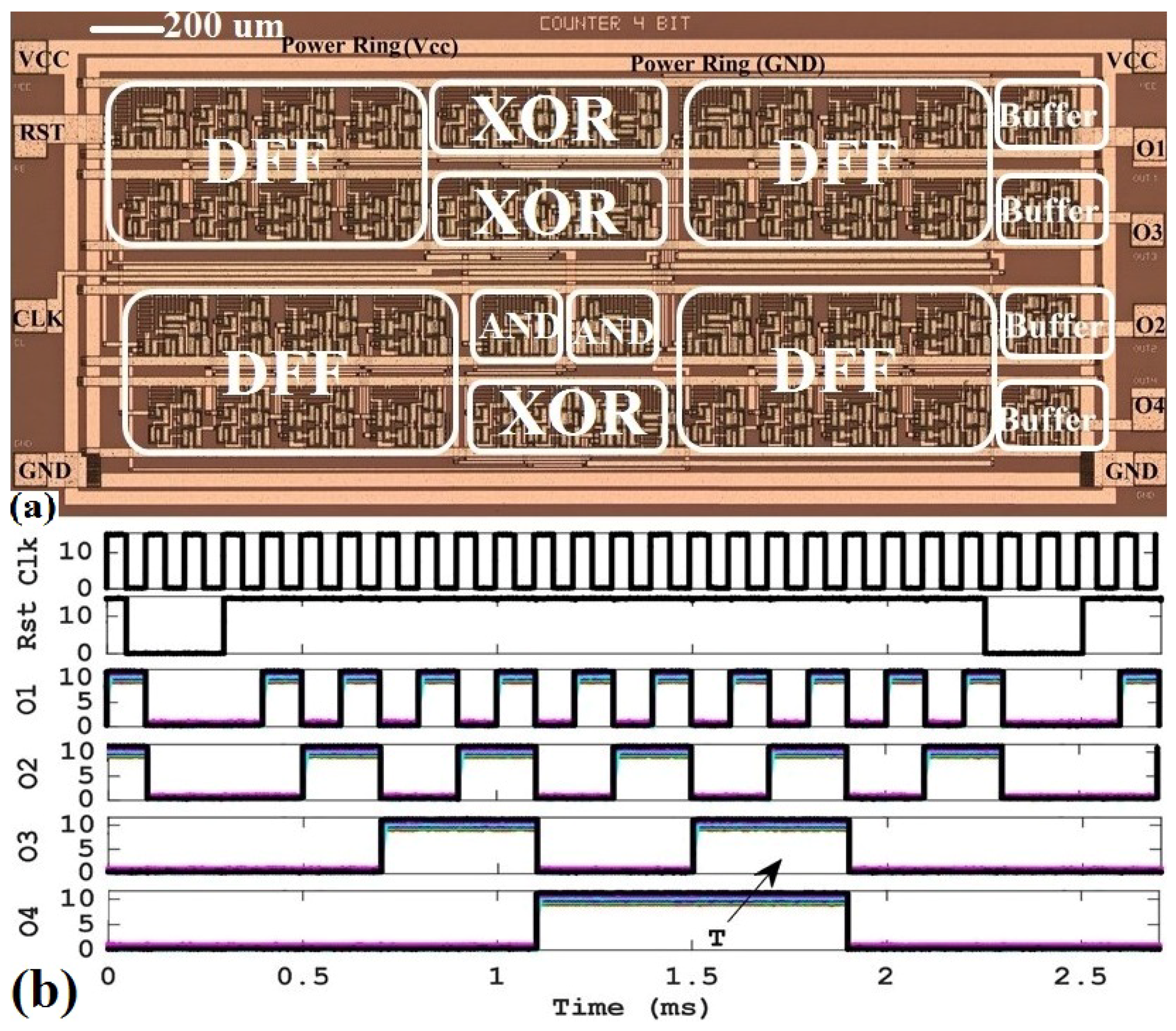

3.4.2. 4-bit Counter

3.5. Analog and Mixed Signal Circuits

3.6. Reliability

4. Discussion

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Cressler, J.D.; Mantooth, H.A. Extreme Environment Electronics; CRC Press: Boca Raton, FL, USA, 2012. [Google Scholar]

- National Research Council. Vision and Voyages for Planetary Science in the Decade 2013–2022; The National Academic Press: Washington, DC, USA, 2011. [Google Scholar]

- Neudeck, P.G.; Okojie, R.S.; Chen, L.Y. High-temperature electronics—A role for wide bandgap semiconductors? Proc. IEEE 2002, 90, 1065–1076. [Google Scholar] [CrossRef]

- Zetterling, C.-M. Integrated Circuits in Silicon Carbide for High-Temperature Applications. MRS Bull. 2015, 40, 431–438. [Google Scholar] [CrossRef]

- Young, R.A.R.; Clark, D.T.; Cormack, J.D.; Murphy, A.E.; Smith, D.A.; Thompson, R.F.; Ramsay, E.P.; Finney, S. High Temperature Digital and Analogue Integrated Circuits in Silicon Carbide. Mater. Sci. Forum 2013, 740–472, 1065–1068. [Google Scholar] [CrossRef]

- Yu, L.C.; Dunne, G.T.; Matocha, K.S.; Cheung, K.P.; Suehle, J.S.; Sheng, K. Reliability Issues of SiC MOSFETs: A Technology for High-Temperature Environments. IEEE Trans. Device Mater. Reliab. 2010, 10, 418–426. [Google Scholar] [CrossRef]

- Ahmad, Shamim. Modeling and Validation of 4H-SiC Low Voltage MOSFETs for Integrated Circuit Design. Ph.D. Thesis, Department of Electrical Engineering, University of Arkansas, Fayetteville, AR, USA, 2015. [Google Scholar]

- Francis, A.M.; Rahman, A.; Holmes, J.; Shepherd, P.; Ahmed, S.; Barlow, M.; Bhuyan, S.; Caley, L.; Moudy, T.; Mantooth, H.A.; et al. Design of analog and mixed-signal integrated SiC CMOS circuits with a high fidelity process design kit. In Proceedings of the 39th Annual GOMACTech Conference, Charleston, SC, USA, 31 March–3 April 2014; pp. 555–598. [Google Scholar]

- Francis, M.A.; Moudy, T.; Holmes, J.A.; Rahman, A.; Barlow, M.; Ahmed, S.; Mantooth, H.A. Towards standard component parts in silicon carbide CMOS. In Proceedings of the IEEE Aerospace Conference, Big Sky, MT, USA, 7–14 March 2015; pp. 1–9. [Google Scholar] [CrossRef]

- Neudeck, P.G.; Spry, D.J.; Chen, L.; Prokop, N.F.; Krasowski, M.J. Demonstration of 4H-SiC Digital Integrated Circuits Above 800 °C. IEEE Electron Device Lett. 2017, 38, 1082–1085. [Google Scholar] [CrossRef]

- Hedayati, R.; Lanni, L.; Rodriguez, S.; Malm, B.G.; Rusu, A.; Zetterling, C.M. A Monolithic, 500 °C Operational Amplifier in 4H-SiC Bipolar Technology. IEEE Electron Device Lett. 2014, 35, 693–695. [Google Scholar] [CrossRef]

- Lanni, L.; Malm, B.G.; Östling, M.; Zetterling, C.M. 500 °C Bipolar Integrated OR/NOR Gate in 4H-SiC. IEEE Electron Device Lett. 2013, 34, 1091–1093. [Google Scholar] [CrossRef]

- Lanni, L.; Ghandi, R.; Malm, B.G.; Zetterling, C.M.; Östling, M. Design and Characterization of High-Temperature ECL-Based Bipolar Integrated Circuits in 4H-SiC. IEEE Trans. Electron Devices 2012, 59, 1076–1083. [Google Scholar] [CrossRef]

- Hedayati, R.; Lanni, L.; Shakir, M.; Salemi, A.; Zetterling, C.M. High temperature bipolar master-slave comparator and frequency divider in 4H-SiC technology. In Proceedings of the European Conference on Silicon Carbide Related Materials (ECSCRM), Halkidiki, Greece, 25–29 September 2016; p. 1. [Google Scholar] [CrossRef]

- Hussain, M.W.; Elahipanah, H.; Zumbro, J.E.; Schröder, S.; Rodriguez, S.; Malm, B.G.; Mantooth, H.A.; Rusu, A. A 500 °C Active Down-Conversion Mixer in Silicon Carbide Bipolar Technology. IEEE Electron Device Lett. 2018, 39, 855–858. [Google Scholar] [CrossRef]

- Ayers, J.E. Digital Integrated Circuits Analysis and Design; CRC Press LLC: Boca Raton, FL, USA, 2004. [Google Scholar]

- Shakir, M.; Hou, S.; Malm, B.G.; Östling, M.; Zetterling, C.M. A 600 °C TTL-Based 11-Stage Ring Oscillator in Bipolar Silicon Carbide Technology. IEEE Electron Device Lett. 2018, 39, 1540–1543. [Google Scholar] [CrossRef]

- Shakir, M.; Elahipanah, H.; Hedayati, R.; Zetterling, C.M. Electrical Characterization of Integrated 2-Input TTL NAND Gate at Elevated Temperature, Fabricated in Bipolar SiC-Technology. Mater. Sci. Forum 2018, 924, 958–961. [Google Scholar] [CrossRef]

- Gummel, H.K.; Poon, H.C. An integral charge control model of bipolar transistors. Bell Syst. Tech. J. 1970, 49, 827–852. [Google Scholar] [CrossRef]

- McAndrew, C.; Seitchik, J.; Bowers, D.; Dunn, M.; Foisy, M.; Getreu, I.; McSwain, M.; Moinian, S.; Park, J.; van Wijnen, P.; et al. VBIC95: An improved vertical, IC bipolar transistor model. In Proceedings of the Bipolar/BiCMOS Circuits and Technology Meeting, Minneapolis, MN, USA, 2–3 October 1995; pp. 170–177. [Google Scholar]

- Hedayati, R. High-Temperature Analog and Mixed-Signal Integrated Circuits in Bipolar Silicon Carbide Technology. Ph.D. Thesis, KTH Royal Institute of Technology, Stockholm, Sweden, 2017. Available online: http://urn.kb.se/resolve?urn=urn:nbn:se:kth:diva-213697 (accessed on 14 March 2019).

- Tian, Y.; Hedayati, R.; Zetterling, C.M. SiC BJT Compact DC Model With Continuous- Temperature Scalability From 300 to 773 K. IEEE Trans. Electron Devices 2017, 64. [Google Scholar] [CrossRef]

- Hou, S.; Shakir, M.; Hellström, P.-E.; Zetterling, C.-M.; Östling, M. Process Control and Optimization of 4H-SiC Semiconductor Devices and Circuits. In Proceedings of the Electron Devices Technology and Manufacturing Conference, Singapore, 13–15 March 2019. in press. [Google Scholar]

- Shakir, M.; Hou, S.; Zetterling, C.M. A Monolithic 500 °C D-flip flop Realized in Bipolar 4H-SiC TTL Technology. In Proceedings of the European Conference on Silicon Carbide Related Materials (ECSCRM), Birmingham, UK, 2–6 September 2018. in press. [Google Scholar]

- Zetterling, C.-M.; Hallen, A.; Hedayati, R.; Kargarrazi, S.; Lanni, L.; Malm, B.G.; Mardani, S.; Norstrom, H.; Rusu, A.; Suvanam, S.S.; et al. Bipolar integrated circuits in SiC for extreme environment operation. Semicond. Sci. Technol. 2017, 32, 034002. [Google Scholar] [CrossRef]

- Lanni, L.; Malm, B.G.; Zetterling, C.M.; Östling, M. A 4H-SiC Bipolar Technology for High-Temperature Integrated Circuits. J. Microelectron. Electron. Packag. 2013, 10. [Google Scholar] [CrossRef]

- Spry, D.J.; Neudeck, P.G.; Chen, L.; Lukco, D.; Chang, C.W.; Beheim, G.M. Prolonged 500 °C Demonstration of 4H-SiC JFET ICs with Two-Level Interconnect. IEEE Electron Device Lett. 2016, 37, 625–628. [Google Scholar] [CrossRef]

| Gate/Module | No of Input | Comb. (C)/Seq. (S) | Devices (Transistors + Resistors) |

|---|---|---|---|

| Inverter | − | C | 9 |

| NAND | 3 | C | 9 |

| AND | 4 | C | 11 |

| OR | 4 | C | 20 |

| XOR | 2 | C | 32 |

| Buffer/Repeater | − | C | 14 |

| AND-OR-Invert (AOI) | − | C | 12 |

| 2 to 1 Multiplexer | − | C | 20 |

| 2 to 4 Decoder | − | C | 62 |

| Full-Adder | − | C | 76 |

| ALU | − | C | 720 |

| DFF with Set and Reset | − | S | 120 |

| 4-bit Counter | − | S | 520 |

| Temperature °C | [V] | / [ns] | [ns] | [nJ] |

|---|---|---|---|---|

| 25 | 9.4/0.3 | 990/130 | 450/125 | 7 |

| 100 | 9.8/0.3 | 445/90 | 255/60 | 4.7 |

| 200 | 10.2/0.3 | 380/85 | 235/45 | 4.6 |

| 300 | 10.8/0.3 | 420/90 | 220/40 | 4.5 |

| 400 | 11/0.3 | 440/95 | 210/45 | 4 |

| 500 | 11.4/0.3 | 515/110 | 255/65 | 4.7 |

| T [°C] | / [V] | / [ns] | [ns] | [ns] | [nJ] |

|---|---|---|---|---|---|

| 25 | 9.4/0.2 | 680/120 | 360 | 720 | 216 |

| 100 | 9.8/0.2 | 560/100 | 230 | 520 | 187 |

| 200 | 10.2/0.2 | 480/105 | 230 | 400 | 150 |

| 300 | 10.6/0.2 | 440/120 | 230 | 400 | 162 |

| 400 | 11/0.2 | 520/125 | 240 | 440 | 145 |

| 500 | 11.4/0.2 | 540/130 | 250 | 480 | 144 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shakir, M.; Hou, S.; Hedayati, R.; Malm, B.G.; Östling, M.; Zetterling, C.-M. Towards Silicon Carbide VLSI Circuits for Extreme Environment Applications. Electronics 2019, 8, 496. https://doi.org/10.3390/electronics8050496

Shakir M, Hou S, Hedayati R, Malm BG, Östling M, Zetterling C-M. Towards Silicon Carbide VLSI Circuits for Extreme Environment Applications. Electronics. 2019; 8(5):496. https://doi.org/10.3390/electronics8050496

Chicago/Turabian StyleShakir, Muhammad, Shuoben Hou, Raheleh Hedayati, Bengt Gunnar Malm, Mikael Östling, and Carl-Mikael Zetterling. 2019. "Towards Silicon Carbide VLSI Circuits for Extreme Environment Applications" Electronics 8, no. 5: 496. https://doi.org/10.3390/electronics8050496

APA StyleShakir, M., Hou, S., Hedayati, R., Malm, B. G., Östling, M., & Zetterling, C.-M. (2019). Towards Silicon Carbide VLSI Circuits for Extreme Environment Applications. Electronics, 8(5), 496. https://doi.org/10.3390/electronics8050496