Implementation of ARINC 659 Bus Controller for Space-Borne Computers

Abstract

:1. Introduction

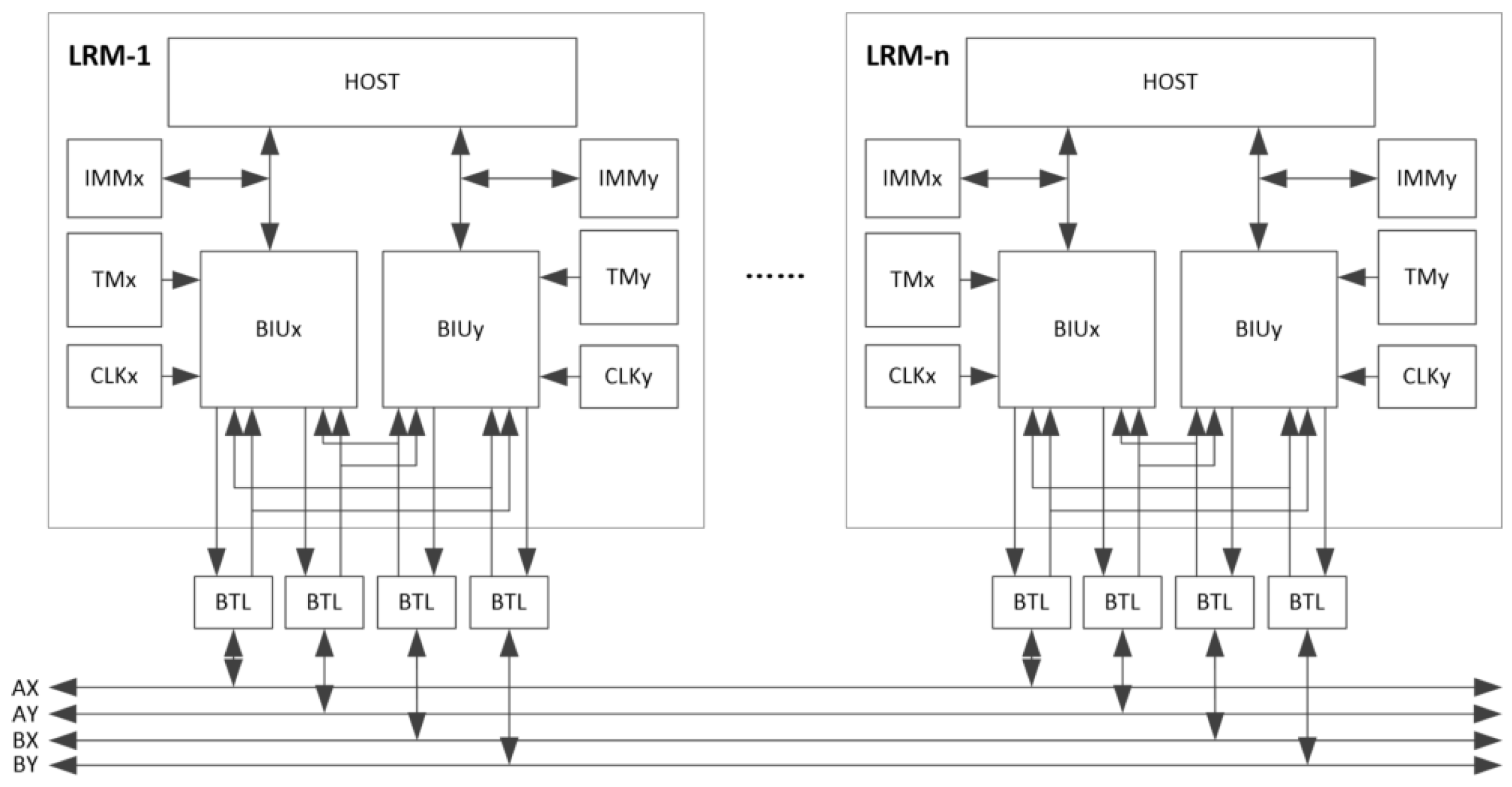

2. Architecture of ARINC 659 Bus Controller

3. Key Technologies

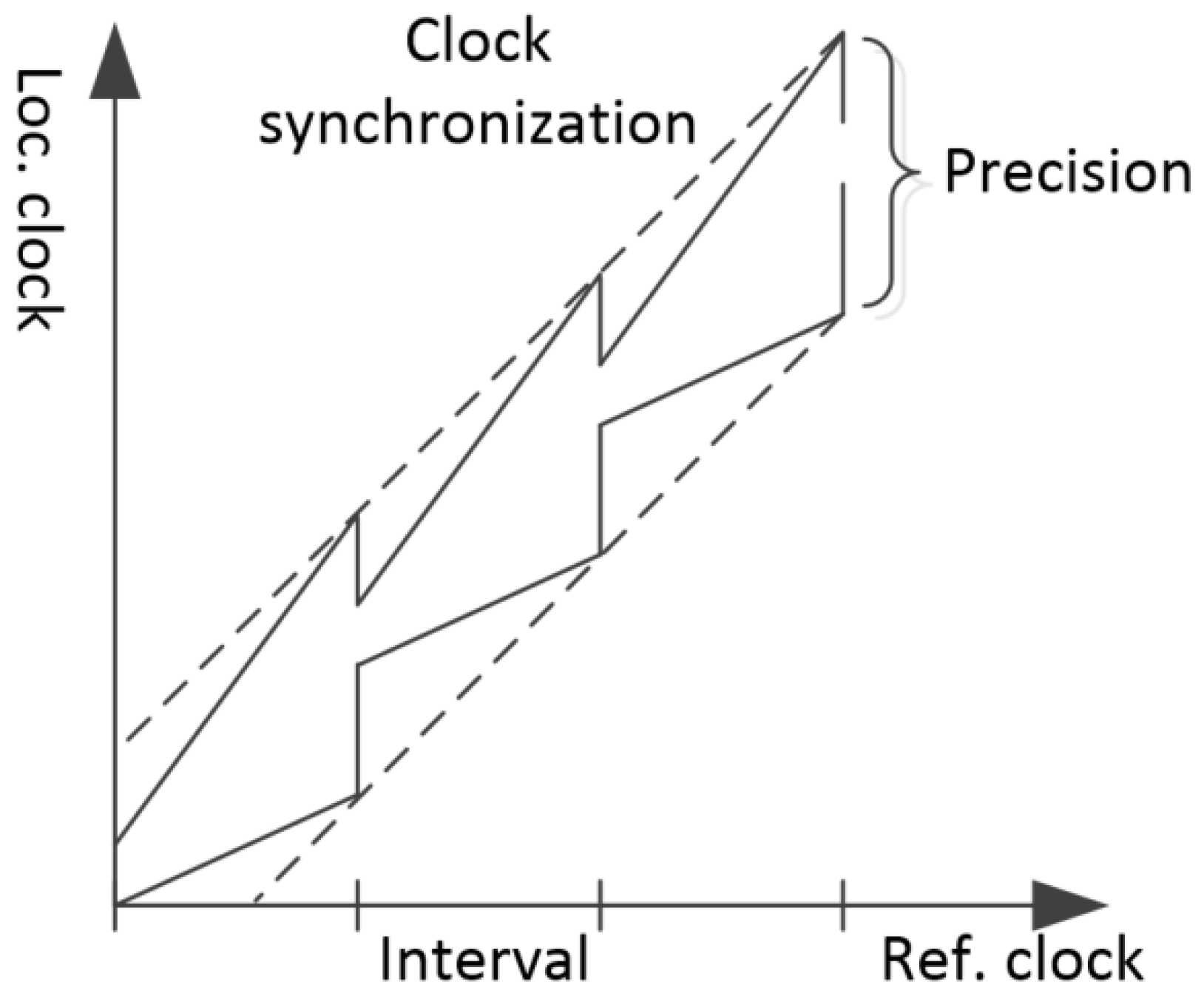

3.1. Internal Clock Synchronization

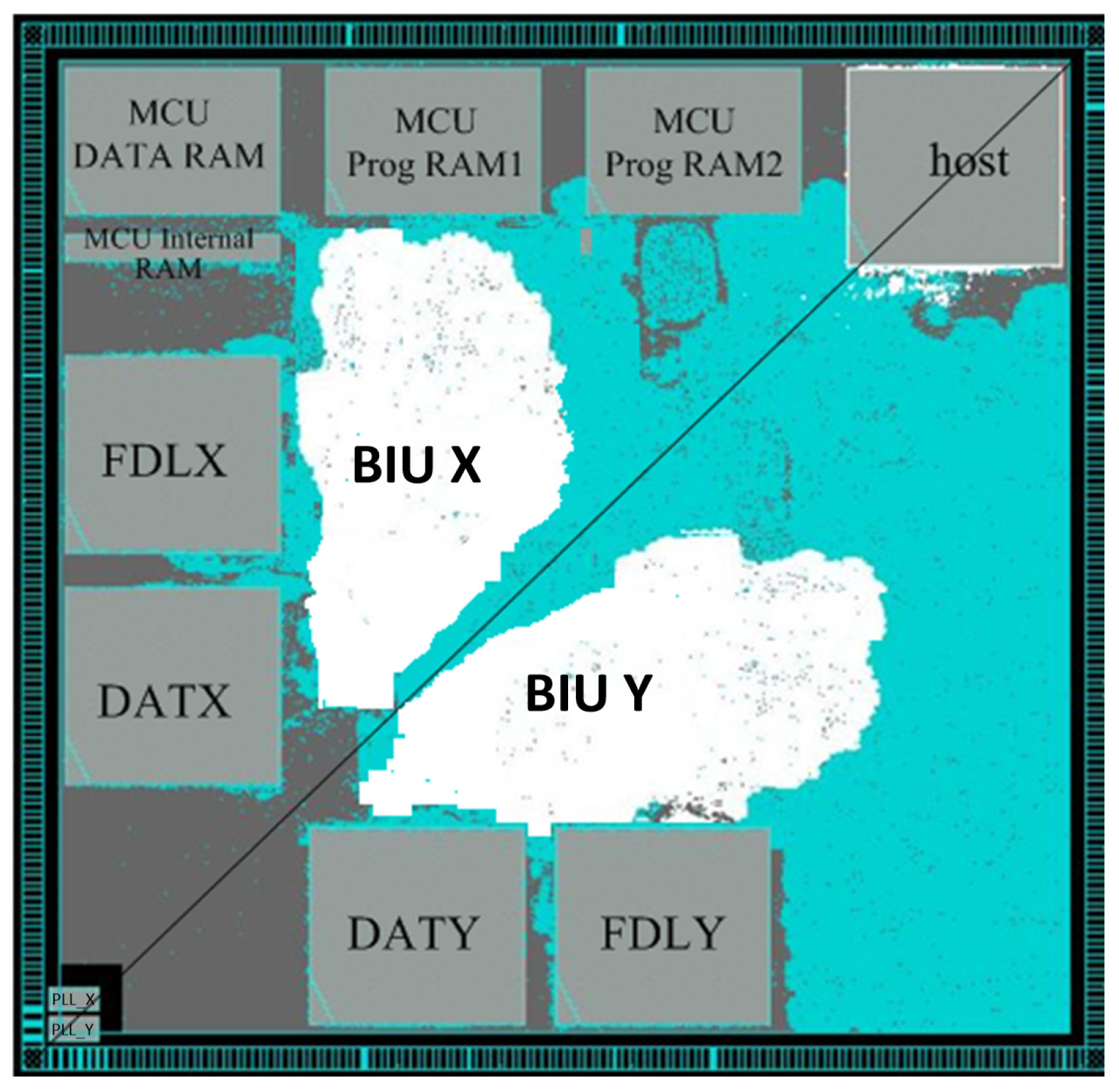

3.2. Symmetric Structure

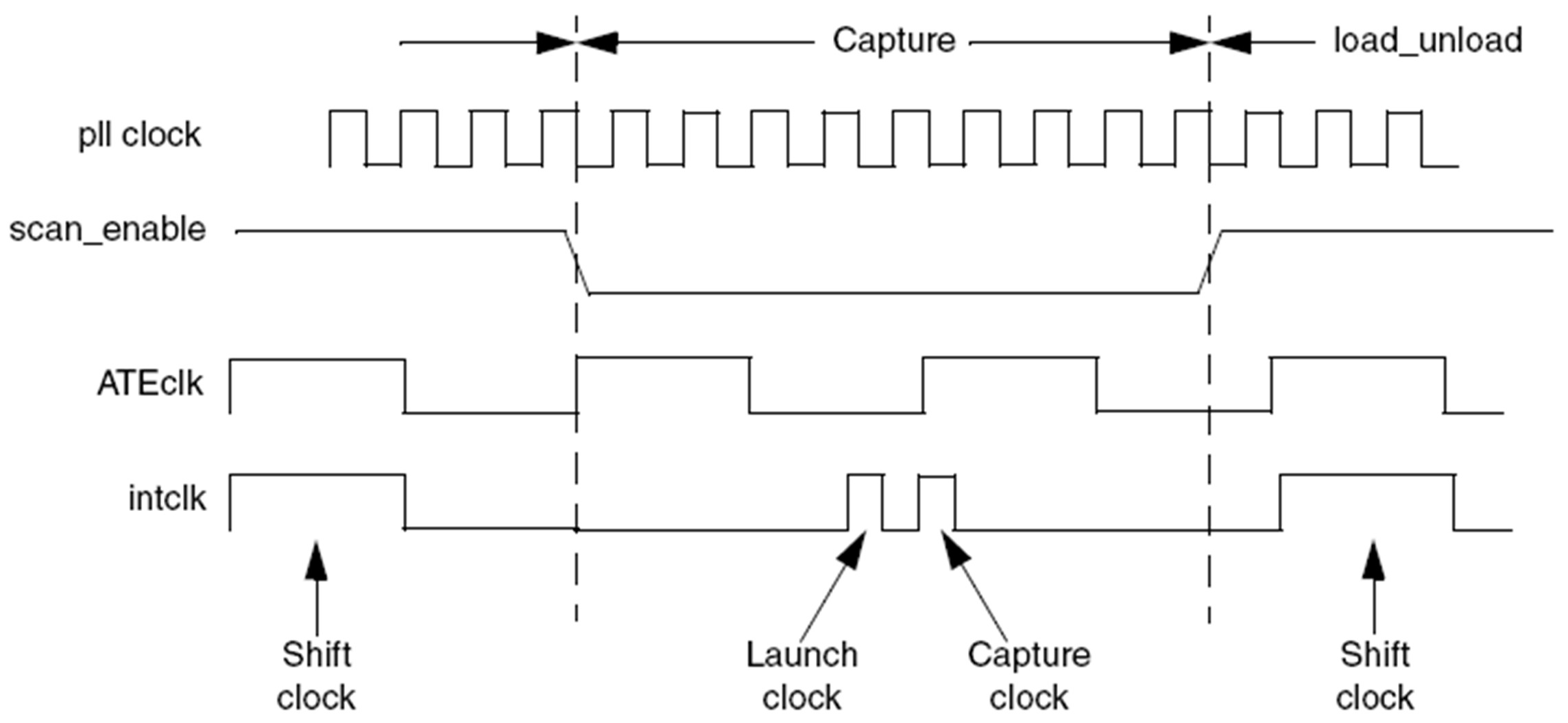

3.3. On-Chip Clock (OCC) for at-Speed Test

3.4. Scanning Compression Test

4. Simulation Results

4.1. Time Convergence Analysis

- (1)

- The symmetry from the reference clock to the two PLLs;

- (2)

- Clock tree symmetry;

- (3)

- Symmetry from the bus input signals to the first stage registers;

- (4)

- Symmetry between the output bus signals of the two BIUs.

4.2. DFT Analysis

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Bohm, P. Incremental and Verified Modeling of the PCI Express Protocol. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2010, 29, 1495–1508. [Google Scholar] [CrossRef]

- Li, Z.; Hu, X. An extension HA design for the hot-swap application of Compact PCI device. In Proceedings of the 2013 IEEE 8th Conference on Industrial Electronics and Applications (ICIEA), Melbourne, Australia, 19–21 June 2013; pp. 646–650. [Google Scholar] [CrossRef]

- Yin, H.; Fu, P.; Wang, B. Design of the VME Bus Controller Module Based on ARM. In Proceedings of the 2016 Sixth International Conference on Instrumentation & Measurement, Computer, Communication and Control (IMCCC), Harbin, China, 21–23 July 2016; pp. 193–196. [Google Scholar] [CrossRef]

- Lu, C.L.; Zhang, G.; Du, C.T.; Cheng, J.H.; Chen, X.F. Design of closed-loop feedback control system based on PXI bus. In Proceedings of the 2017 IEEE 2nd Information Technology, Networking, Electronic and Automation Control Conference (ITNEC), Chengdu, China, 15–17 December 2017; pp. 1655–1658. [Google Scholar] [CrossRef]

- Li, M.; Liang, G.; Gao, Q. Design and implementation of VXI bus Arbitrary Waveform Generator. In Proceedings of the 2012 International Conference on Systems and Informatics (ICSAI2012), Yantai, China, 19–21 May 2012; pp. 1295–1297. [Google Scholar] [CrossRef]

- Kornek-Percin, B.; Petersen, B.; Reichle, M.; Bader, J. New IMA architecture approach based on IMA resources. In Proceedings of the 2015 IEEE/AIAA 34th Digital Avionics Systems Conference (DASC), Prague, Czech Republic, 13–17 September 2015; pp. 6A2-1–6A2-8. [Google Scholar] [CrossRef]

- Carpenter, D.; Hoyme, C. ARINC 659 scheduling: Problem definition. In Proceedings of the 1994 Real-Time Systems Symposium, San Juan, PR, USA, 7–9 December 1994; pp. 165–169. [Google Scholar] [CrossRef]

- ARINC Backplane Data Bus. Available online: https://standards.globalspec.com/std/514584/arinc-659 (accessed on 24 February 2019).

- Michael, J.M. Boeing B-777. In The Avionics Handbook; Spitzer, C.R., Ed.; Boca Ratonby by CRC Press LLC: Boca Raton, FL, USA, 2001; p. 29. [Google Scholar]

- Sutterfield, B.; Hoschette, J.A.; Anton, P. Future integrated modular avionics for jet fighter mission computers. In Proceedings of the 2008 IEEE/AIAA 27th Digital Avionics Systems Conference, St. Paul, MN, USA, 26–30 October 2008; pp. 1.A.4-1–1.A.4-11. [Google Scholar] [CrossRef]

- Black, R.; Fletcher, M. Next generation space avionics: A highly reliable layered system implementation. In Proceedings of the 23rd Digital Avionics Systems Conference (IEEE Cat. No. 04CH37576), Salt Lake City, UT, USA, 28 October 2004; pp. 13.E.4-1–13.E.4-15. [Google Scholar] [CrossRef]

- Shenzhou (Spacecraft). Available online: https://en.wikipedia.org/wiki/Shenzhou_(spacecraft) (accessed on 7 April 2019).

- Abbas, G.G.; Zhu, Y.; Muhammad, A.H.; Waqar, A.; An, J. Backplane bus controller implementation in Fpga for hard real time control systems. In Proceedings of the 2011 IEEE 3rd International Conference on Communication Software and Networks, Xi’an, China, 27–29 May 2011; pp. 451–456. [Google Scholar] [CrossRef]

- Muhammad, A.H.; Fan, X.; Abbas, G.G.; Waqar, A.; An, J. Implementation of data transfer and synchronous pulse operation for ARINC 659. In Proceedings of the 2011 IEEE 3rd International Conference on Communication Software and Networks, Xi’an, China, 27–29 May 2011; pp. 485–489. [Google Scholar] [CrossRef]

- Ahmad, W.; Shengbing, Z.; Amjad, H.M.; Gillani, G.A.; Jianfeng, A. FPGA based real time implementation scheme for ARINC 659 backplane data bus. In Proceedings of the 2011 3rd International Conference on Computer Research and Development, Shanghai, China, 11–13 March 2011; pp. 478–482. [Google Scholar] [CrossRef]

- Wedde, H.F.; Freund, W. Harmonious internal clock synchronization. In Proceedings of the 12th Euromicro Conference on Real-Time Systems, Stockholm, Sweden, 19–21 June 2000; pp. 175–182. [Google Scholar] [CrossRef]

- Chaudhuri, S.; Nandy, S. A modified physical clock synchronization algorithm. In Proceedings of the 2013 3rd IEEE International Advance Computing Conference (IACC), Ghaziabad, India, 22–23 Febuary 2013; pp. 34–39. [Google Scholar] [CrossRef]

- Matsumoto, F.; Matsuo, S.; Nishioka, S.; Abe, H.; Ohbuchi, T. Study on offset reduction method for a fully differential filter employing symmetrical floating impedance scaling circuits. In Proceedings of the 2016 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), Phuket, Thailand, 24–27 October 2016; pp. 1–5. [Google Scholar] [CrossRef]

- Ai, Z.; Wang, L.; Liu, G.; Xu, C. A method of multi-channel pulse acquisition synchronization. In Proceedings of the 2017 International Conference on Circuits, System and Simulation (ICCSS), London, UK, 14–17 July 2017; pp. 176–179. [Google Scholar] [CrossRef]

- DFTMAX Ultra. Available online: https://www.synopsys.com (accessed on 24 February 2019).

| Path | BIU X | BIU Y | Deviation |

|---|---|---|---|

| Ref. clock to First stage Reg. | 4.05 ns | 4.07 ns | 0.02 ns |

| axck/ayck to First stage Reg. | 5.94 ns | 5.83 ns | 0.11 ns |

| axd0/ayd0 to First stage Reg. | 5.88 ns | 5.88 ns | 0 ns |

| axd1/ayd1 to First stage Reg. | 5.66 ns | 5.96 ns | 0.30 ns |

| bxck/byck to First stage Reg. | 5.72 ns | 5.96 ns | 0.24 ns |

| bxd0/byd0 to First stage Reg. | 5.72 ns | 5.64 ns | 0.08 ns |

| bxd1/byd1 to First stage Reg. | 5.62 ns | 5.76 ns | 0.14 ns |

| Path | Deviation |

|---|---|

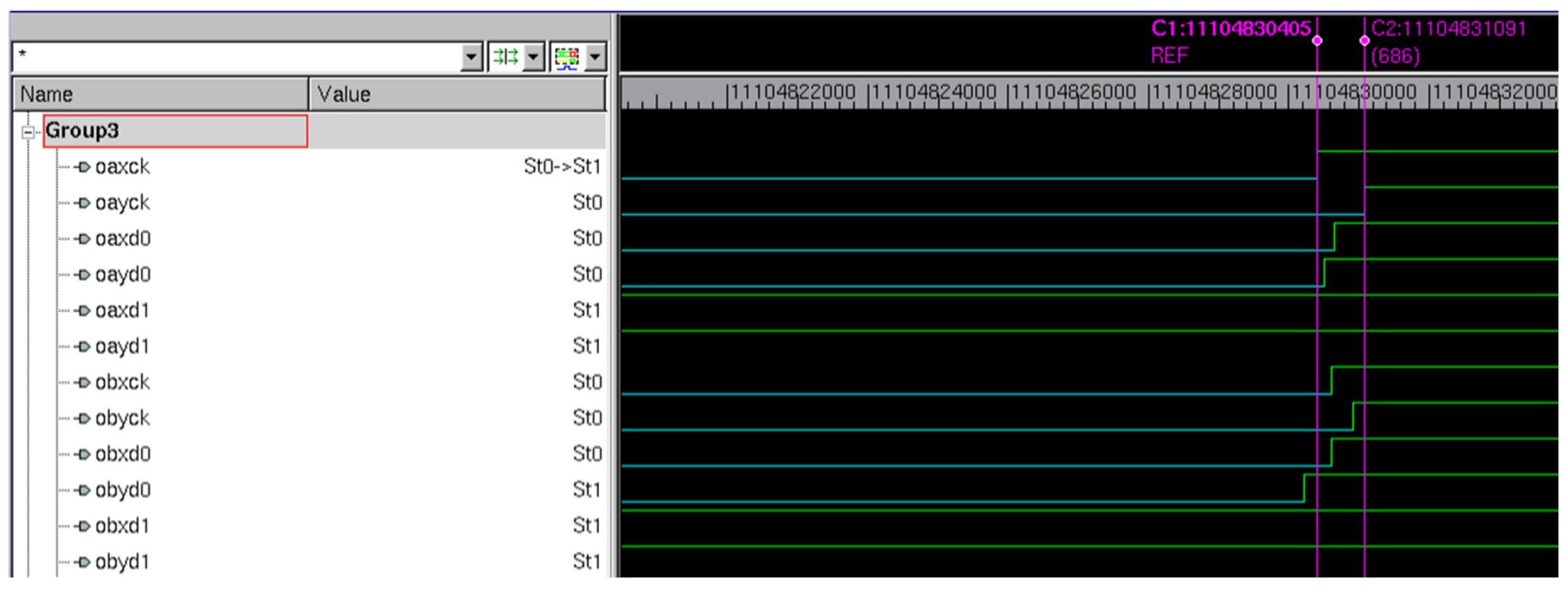

| Path Deviation oaxck-oayck | 0.686 ns |

| oaxd0-oayd0 | 0.144 ns |

| oaxd1-oayd1 | 0.376 ns |

| obxck-obyck | 0.322 ns |

| obxd0-obyd0 | 0.390 ns |

| obxd1-obyd1 | 0.335 ns |

| Test Type | DT | PT | UD | AU | ND | Total Faults | Test Coverage |

|---|---|---|---|---|---|---|---|

| Stuck-at fault test | 1,736,637 | 828 | 23,550 | 26,551 | 32 | 1,787,598 | 98.47% |

| At-speed test | 1,373,130 | 42 | 3153 | 0 | 192,849 | 1,569,174 | 87.68% |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, S.; Liu, S.; Guo, C.; Fan, X.; Ma, T.; Tiwari, P. Implementation of ARINC 659 Bus Controller for Space-Borne Computers. Electronics 2019, 8, 435. https://doi.org/10.3390/electronics8040435

Jiang S, Liu S, Guo C, Fan X, Ma T, Tiwari P. Implementation of ARINC 659 Bus Controller for Space-Borne Computers. Electronics. 2019; 8(4):435. https://doi.org/10.3390/electronics8040435

Chicago/Turabian StyleJiang, Shuang, Shibin Liu, Chenguang Guo, Xu Fan, Teng Ma, and Prayag Tiwari. 2019. "Implementation of ARINC 659 Bus Controller for Space-Borne Computers" Electronics 8, no. 4: 435. https://doi.org/10.3390/electronics8040435

APA StyleJiang, S., Liu, S., Guo, C., Fan, X., Ma, T., & Tiwari, P. (2019). Implementation of ARINC 659 Bus Controller for Space-Borne Computers. Electronics, 8(4), 435. https://doi.org/10.3390/electronics8040435