An Effective FPGA Solver on Probability Distribution and Preprocessing

Abstract

1. Introduction

2. Preliminaries

3. Outline of probSAT+

| Algorithm 1. probSAT+. |

| Require: a CNF Formula F; Maxtries; Maxflips; |

| Ensure: Satisfying assignments (if found) |

| probSAT+(F, Maxtries, Maxflips) |

| { |

| for (tries = 1 to Maxtries) { |

| determine the values of variables that conform to pure literal rules; |

| calculate the initial probability of the remaining variables as positive ; |

| V ← generate a set of random assignments according to ; |

| C ← search for unsatisfied clauses at the current initial assignments; |

| for (flips = 1 to Maxflips) { |

| if (C = ) then |

| return V; |

| ← an unsatisfied clause selected at random; |

| for (x in ) { |

| calculate the break-value; |

| sort the break-value; |

| search for the flipping probability of variables; |

| } |

| if ( < ) |

| p ← flip a variable according to ; |

| else |

| p ← select the variable with ; |

| V ← V with p flipped; |

| C ← update the set of unsatisfied clauses at the current value; |

| } |

| } |

| return “no satisfying assignment found”; |

| } |

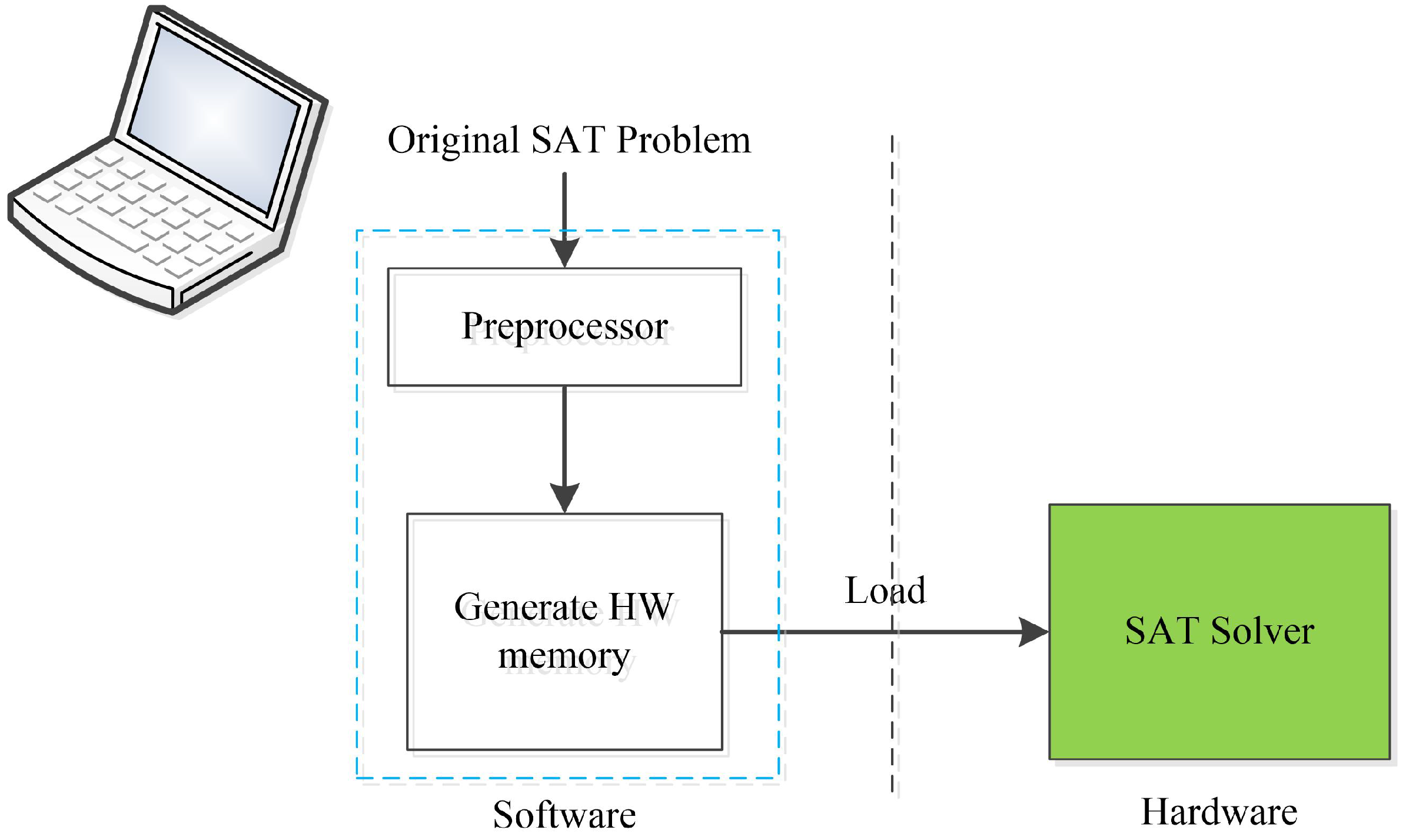

3.1. Software Preprocessing

3.2. Hardware Architecture

4. Results and Discussion

4.1. Preprocessing Performance

4.2. Solver Performance

5. Conclusions and Future Work

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Skliarova, I.; de Brito Ferrari, A. Reconfigurable hardware SAT solvers: A survey of systems. IEEE Trans. Comput. 2004, 53, 1449–1461. [Google Scholar] [CrossRef]

- Safar, M.; El-Kharashi, M.W.; Shalan, M.; Salem, A. A reconfigurable, pipelined, conflict directed jumping search sat solver. In Proceedings of the 2011 Design, Automation & Test in Europe, Grenoble, France, 14–18 March 2011; pp. 1–6. [Google Scholar]

- Kanazawa, K.; Maruyama, T. An approach for solving large sat problems on fpga. ACM Trans. Reconfigurable Technol. Syst. 2010, 4, 10. [Google Scholar] [CrossRef]

- Kanazawa, K.; Maruyama, T. An FPGA solver for large SAT problems. In Proceedings of the 2006 International Conference on Field Programmable Logic and Applications (FPL’06), Madrid, Spain, 28–30 August 2006; pp. 1–6. [Google Scholar]

- Kanazawa, K.; Maruyama, T. Solving SAT-encoded formal verification problems on SoC based on a WSAT algorithm with a new heuristic for hardware acceleration. In Proceedings of the 2013 IEEE 7th International Symposium on Embedded Multicore Socs (MCSoC), Tokyo, Japan, 26–28 September 2013; pp. 101–106. [Google Scholar]

- Kanazawa, K.; Maruyama, T. FPGA acceleration of SAT/Max-SAT solving using variable-way cache. In Proceedings of the 2014 24th International Conference on Field Programmable Logic and Applications (FPL), Munich, Germany, 2–4 September 2014; pp. 1–4. [Google Scholar]

- Ivan, T.; Aboulhamid, E.M. An efficient hardware implementation of a sat problem solver on FPGA. In Proceedings of the 2013 Euromicro Conference on Digital System Design (DSD), Los Alamitos, CA, USA, 4–6 September 2013; pp. 209–216. [Google Scholar]

- Haller, L.; Singh, S. Relieving capacity limits on FPGA-based SAT-solvers. In Proceedings of the Formal Methods in Computer-Aided Design (FMCAD), Lugano, Switzerland, 20–23 October 2010; pp. 217–220. [Google Scholar]

- Thong, J.; Nicolici, N. FPGA acceleration of enhanced boolean constraint propagation for SAT solvers. In Proceedings of the International Conference on Computer-Aided Design, San Jose, CA, USA, 18–21 November 2013; pp. 234–241. [Google Scholar]

- Sohanghpurwala, A.A.; Athanas, P. An effective probability distribution SAT solver on reconfigurable hardware. In Proceedings of the 2016 International Conference on ReConFigurable Computing and FPGAs (ReConFig), Cancun, Mexico, 30 November–2 December 2016; pp. 1–6. [Google Scholar]

- Kefan, M.; Liquan, X.; Jianmin, Z.; Tiejun, L. An FPGA SAT solver based on enhanced constraint. In Proceedings of the 2017 International Conference on FPGA Reconfiguration for General-Purpose Computing (FPGA4GPC), Hamburg, Germany, 9–10 May 2017; pp. 25–30. [Google Scholar]

- Zhang, J.; Shen, S.; Li, S. An Unsatisfiable Subformulae Extraction Algorithm Base on Refutation Proof and Local Search. Chin. J. Comput. 2013, 37, 2262–2267. [Google Scholar]

- Mohammed, S.M.Z.; Khader, A.T.; Al-Betar, M.A. 3-SAT Using Island-based Genetic Algorithm. IEEJ Trans. Electron. Inf. Syst. 2016, 136, 1694–1698. [Google Scholar]

- Marques-Silva, J. Algebraic simplification techniques for propositional satisfiability. In Proceedings of the International Conference on Principles and Practice of Constraint Programming, Singapore, 18–21 September 2000; pp. 537–542. [Google Scholar]

- Balint, A.; Schöning, U. Choosing probability distributions for stochastic local search and the role of make versus break. In Proceedings of the International Conference on Theory and Applications of Satisfiability Testing, Trento, Italy, 17–20 June 2012; pp. 16–29. [Google Scholar]

- Guo, Y.; Zhang, C.; Zhang, B. Research Advance of SAT Solving Algorithm. Comput. Sci. 2016, 43, 8–17. [Google Scholar]

- Achlioptas, D. Lower bounds for random 3-SAT via differential equations. Theor. Comput. Sci. 2001, 265, 159–185. [Google Scholar] [CrossRef]

- Dubois, O.; Boufkhad, Y.; Mandler, J. Typical random 3-SAT formulae and the satisfiability threshold. arXiv, 2002; arXiv:cs/0211036. [Google Scholar]

- Mitchell, D.; Selman, B.; Levesque, H. Hard and easy distributions of SAT problems. AAAI 1992, 92, 459–465. [Google Scholar]

- Mertens, S.; Mézard, M.; Zecchina, R. Threshold values of random K-SAT from the cavity method. Random Struct. Algorithms 2006, 28, 340–373. [Google Scholar] [CrossRef]

- Kilani, Y.; Bsoul, M.; Alsarhan, A.; Al-Khasawneh, A. A survey of the satisfiability-problems solving algorithms. Int. J. Adv. Intell. Paradig. 2013, 5, 233–256. [Google Scholar] [CrossRef]

- Le Berre, D.; Roussel, O. Random Benchmark Problems. Available online: https://www.satcompetition.org/2011/ (accessed on 21 January 2019).

- Kautz, H. WalkSAT Version 51. Available online: https://github.com/tonyling/research-sat-solvers/ (accessed on 18 March 2019).

- Tompkins, D. Sparrow. Available online: http://www.cril.univ-artois.fr/SAT11/ (accessed on 18 March 2019).

- Balint, A.; Schöning, U. Engineering a Lightweight and Efficient Local Search SAT Solver. In Algorithm Engineering; Springer: Berlin, Germany, 2016; pp. 1–18. [Google Scholar]

| k | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|

| 4.267 | 9.931 | 21.117 | 43.37 | 87.79 |

| Problems | Name | ||

|---|---|---|---|

| MQ1 | 350 | 1491 | uf350-004, uf350-011, uf350-022, uf350-054, uf350-050, uf350-075, uf350-064, uf350-077, uf350-063, uf350-098 |

| MQ2 | 400 | 1704 | uf400-084, uf400-002, uf400-037, uf400-064, uf400-053, uf400-021, uf400-001, uf400-025, uf400042-, uf400-089 |

| MQ3 | 450 | 1917 | uf450-014, uf450-001, uf450-027, uf450-011, uf450-033, uf450-059, uf450-085, uf450-034, uf450-078, uf450-097 |

| MQ4 | 500 | 2130 | uf500-003, uf500-027, uf500-036, uf500-047, uf500-054, uf500-075, uf500-083, uf500-055, uf500-067, uf500-097 |

| MQ5 | 550 | 2343 | uf550-005, uf550-011, uf550-30, uf550-045, uf550-069, uf550-052, uf550-088, uf550-090, uf550-080, uf550-094 |

| MQ6 | 600 | 2556 | uf600-002, uf600-033, uf600-054, uf600-052, uf600-039, uf600-075, uf600-086, uf600-077, uf600-030, uf600-099 |

| MQ7 | 650 | 2769 | uf650-002, uf650-009, uf650-015, uf650-034, uf650-050, uf650-068, uf650-079, uf650-083, uf650-085, uf650-064 |

| MQ8 | 700 | 2982 | uf700-003, uf700-026, uf700-021, uf700-036, uf700-043, uf700-074, uf700-051, uf700-015, uf700-009, uf700-096 |

| MQ9 | 750 | 3195 | uf750-027, uf750-014, uf750-023, uf750-049, uf750-061, uf750-070, uf750-080, uf750-083, uf750-078, uf750-088 |

| MQ10 | 800 | 3408 | uf800-019, uf800-017, uf800-021, uf800-024, uf800-035, uf800-029, uf800-054, uf800-069, uf800-090, uf800-088 |

| LQ1 | 2500 | 10,500 | uf2500-004, uf2500-024, uf2500-038, uf2500-066, uf2500-088 |

| LQ2 | 5000 | 21,000 | uf5000-009, uf5000-025, uf5000-051, uf5000-077, uf5000-090 |

| LQ3 | 10,000 | 42,000 | uf10000-011, uf10000-031, uf10000-047, uf10000-068, uf10000-085 |

| LQ4 | 15,000 | 63,000 | uf15000-003, uf15000-026, uf15000-051, uf15000-059, uf15000-091 |

| LQ5 | 20,000 | 84,000 | uf20000-017, uf20000-029, uf20000-048, uf20000-076, uf20000-097 |

| LQ6 | 25,000 | 105,000 | uf25000-006, uf25000-018, uf25000-030, uf25000-066, uf25000-092 |

| LQ7 | 30,000 | 126,000 | uf30000-001, uf30000-028, uf30000-064, uf30000-076, uf30000-100 |

| LQ8 | 35,000 | 147,000 | uf35000-016, uf35000-022, uf35000-060, uf35000-078, uf35000-093 |

| LQ9 | 40,000 | 168,000 | uf40000-069, uf40000-003, uf40000-078, uf40000-085, uf40000-098 |

| LQ10 | 50,000 | 210,000 | uf50000-065, uf50000-015, uf50000-041,uf50000-003, uf50000-094 |

| Problems | Flips Number | Flips/Sec | Solving Time(s) | Speed Up | |||||

|---|---|---|---|---|---|---|---|---|---|

| Sparrow | probSAT+ | Sparrow | probSAT+ | Sparrow | probSAT+ | ||||

| uf350-042 | 350 | 1491 | 64,921 | 36,441 | 3,895,275 | 1,994,933 | 0.017 | 0.018 | 0.91 |

| uf400-084 | 400 | 1704 | 123,446 | 270,823 | 3,429,065 | 6,728,517 | 0.036 | 0.040 | 0.89 |

| uf450-014 | 450 | 1917 | 273,291 | 110,341 | 3,693,125 | 2,691,237 | 0.074 | 0.041 | 1.80 |

| uf500-047 | 500 | 2130 | 42,860 | 27,513 | 3,061,425 | 2,751,300 | 0.014 | 0.010 | 1.40 |

| uf550-038 | 550 | 2343 | 159,125 | 57,381 | 3,978,128 | 1,593,905 | 0.040 | 0.036 | 1.11 |

| uf600-002 | 600 | 2556 | 358,903 | 169,469 | 3,450,992 | 2,689,989 | 0.104 | 0.063 | 1.65 |

| uf650-079 | 650 | 2769 | 949,363 | 441,472 | 3,859,197 | 2,348,253 | 0.246 | 0.188 | 1.31 |

| uf700-009 | 700 | 2982 | 7,673,077 | 2,393,852 | 4,379,610 | 2,358,475 | 1.752 | 1.015 | 1.73 |

| uf750-027 | 750 | 3195 | 19,304,434 | 9,442,474 | 3,978,655 | 2,720,390 | 4.852 | 3.471 | 1.40 |

| uf800-029 | 800 | 3408 | 246,110 | 54,290 | 3,238,287 | 1,872,070 | 0.076 | 0.029 | 2.62 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ma, K.; Xiao, L.; Zhang, J. An Effective FPGA Solver on Probability Distribution and Preprocessing. Electronics 2019, 8, 333. https://doi.org/10.3390/electronics8030333

Ma K, Xiao L, Zhang J. An Effective FPGA Solver on Probability Distribution and Preprocessing. Electronics. 2019; 8(3):333. https://doi.org/10.3390/electronics8030333

Chicago/Turabian StyleMa, Kefan, Liquan Xiao, and Jianmin Zhang. 2019. "An Effective FPGA Solver on Probability Distribution and Preprocessing" Electronics 8, no. 3: 333. https://doi.org/10.3390/electronics8030333

APA StyleMa, K., Xiao, L., & Zhang, J. (2019). An Effective FPGA Solver on Probability Distribution and Preprocessing. Electronics, 8(3), 333. https://doi.org/10.3390/electronics8030333