Review of Multilevel Voltage Source Inverter Topologies and Analysis of Harmonics Distortions in FC-MLI

Abstract

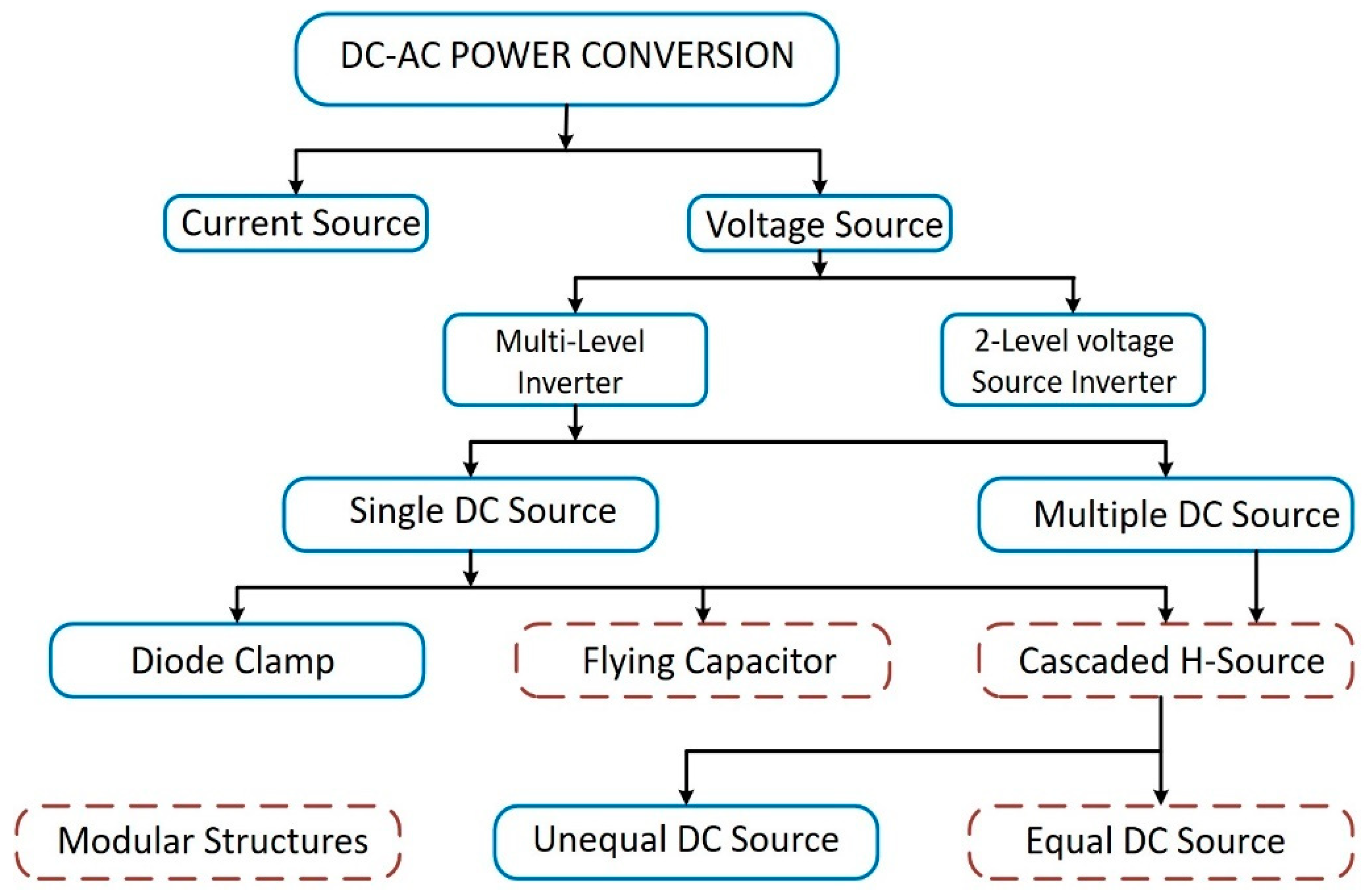

1. Introduction

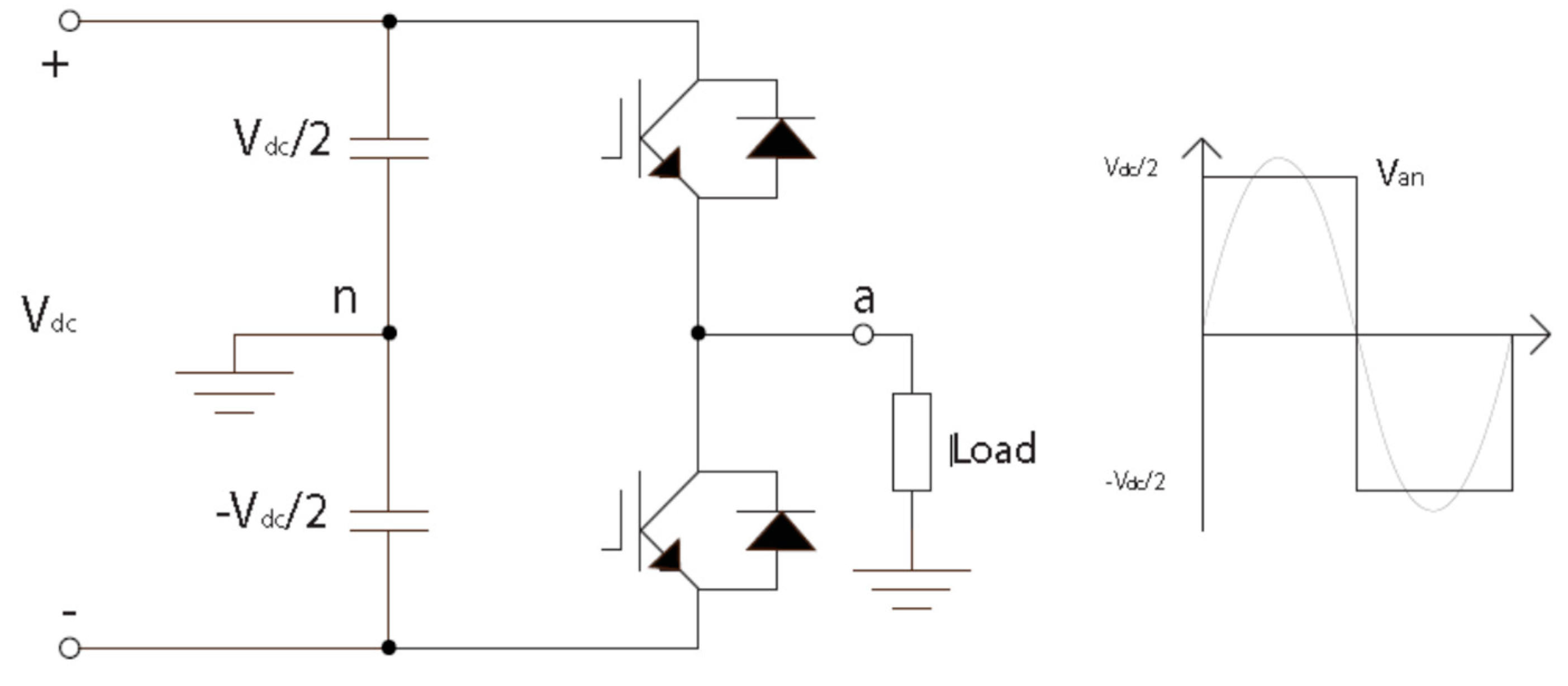

The Concept of Multilevel Inverters

2. Topologies of Multilevel Inverter

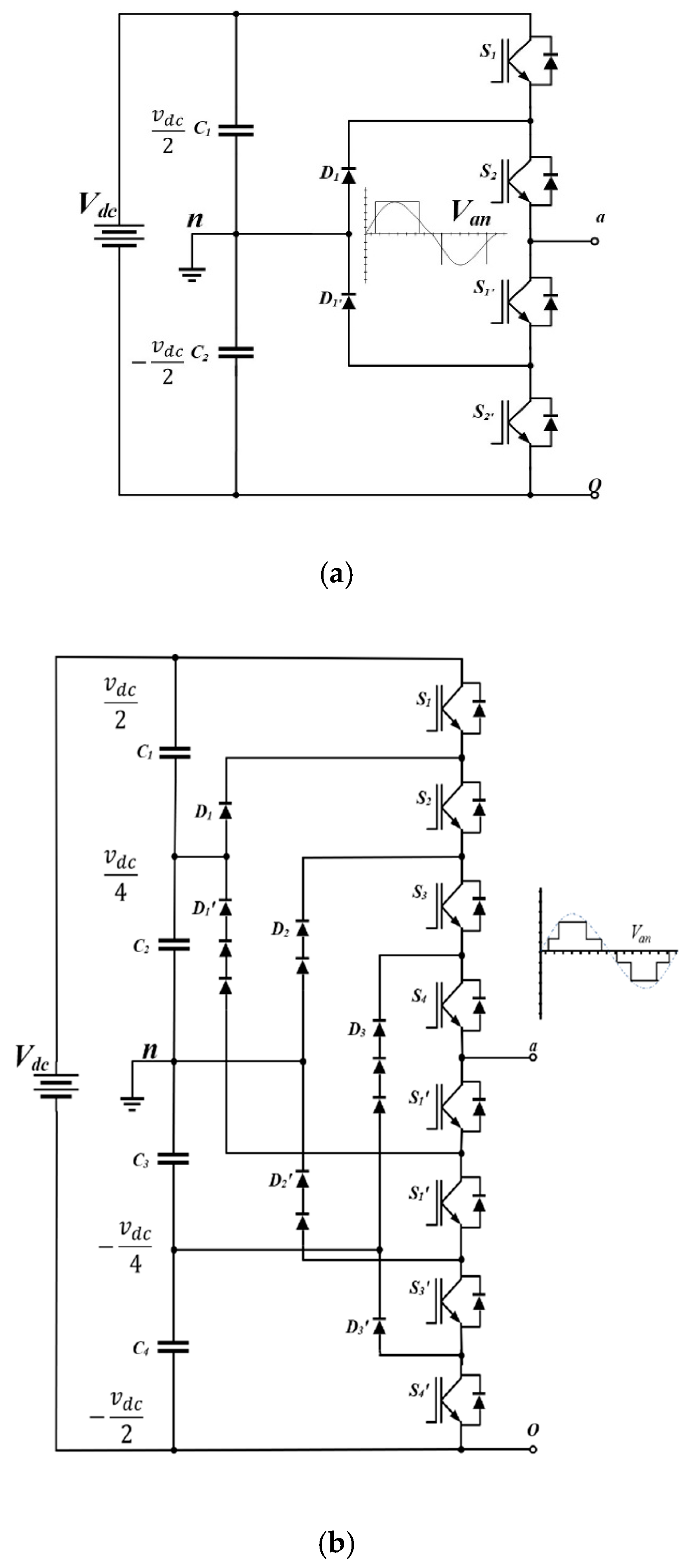

2.1. Diode-Clamped Multilevel Inverter (DC-MLI)

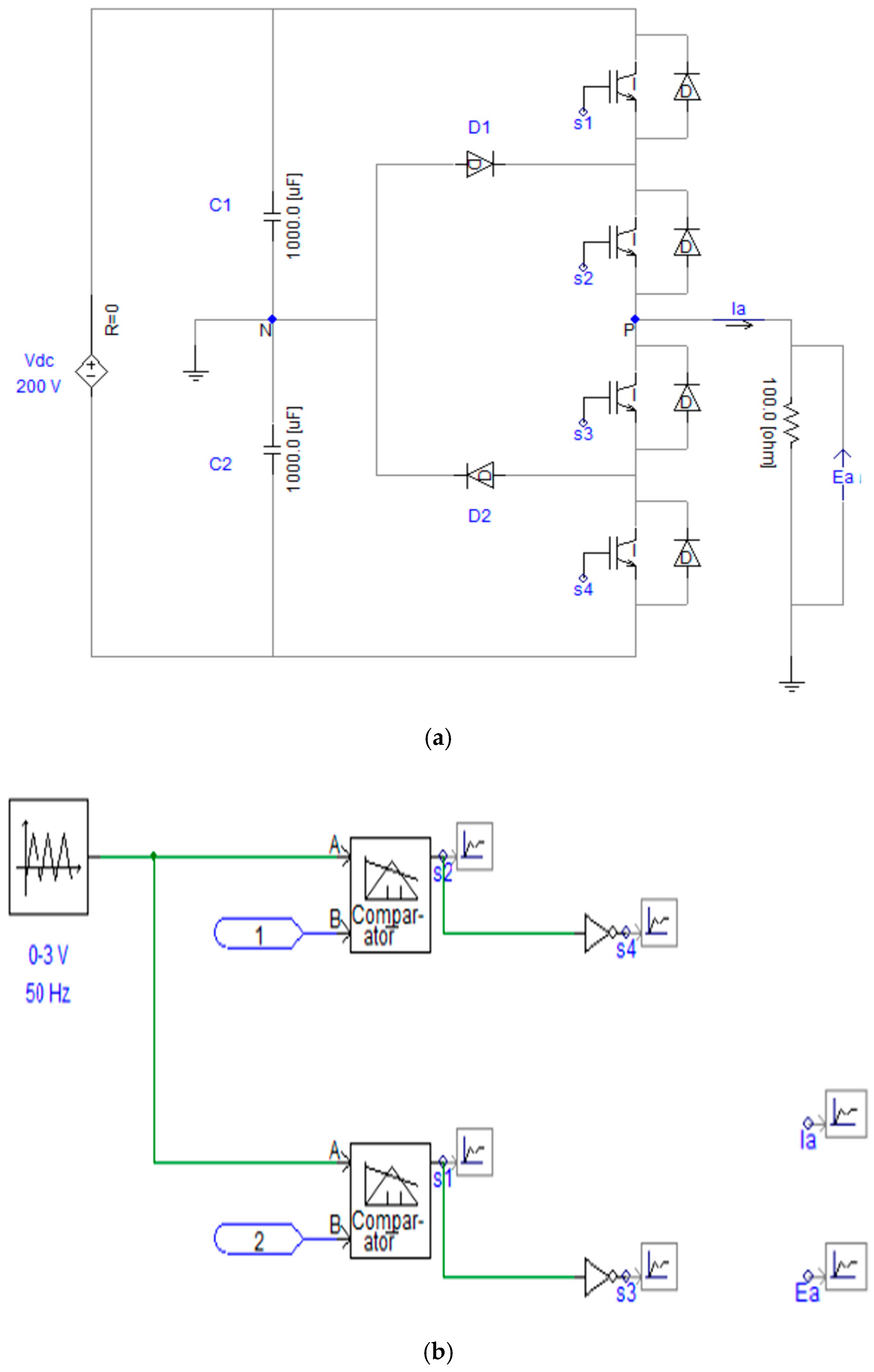

2.1.1. 3-Level DC-MLI PSCAD Simulations

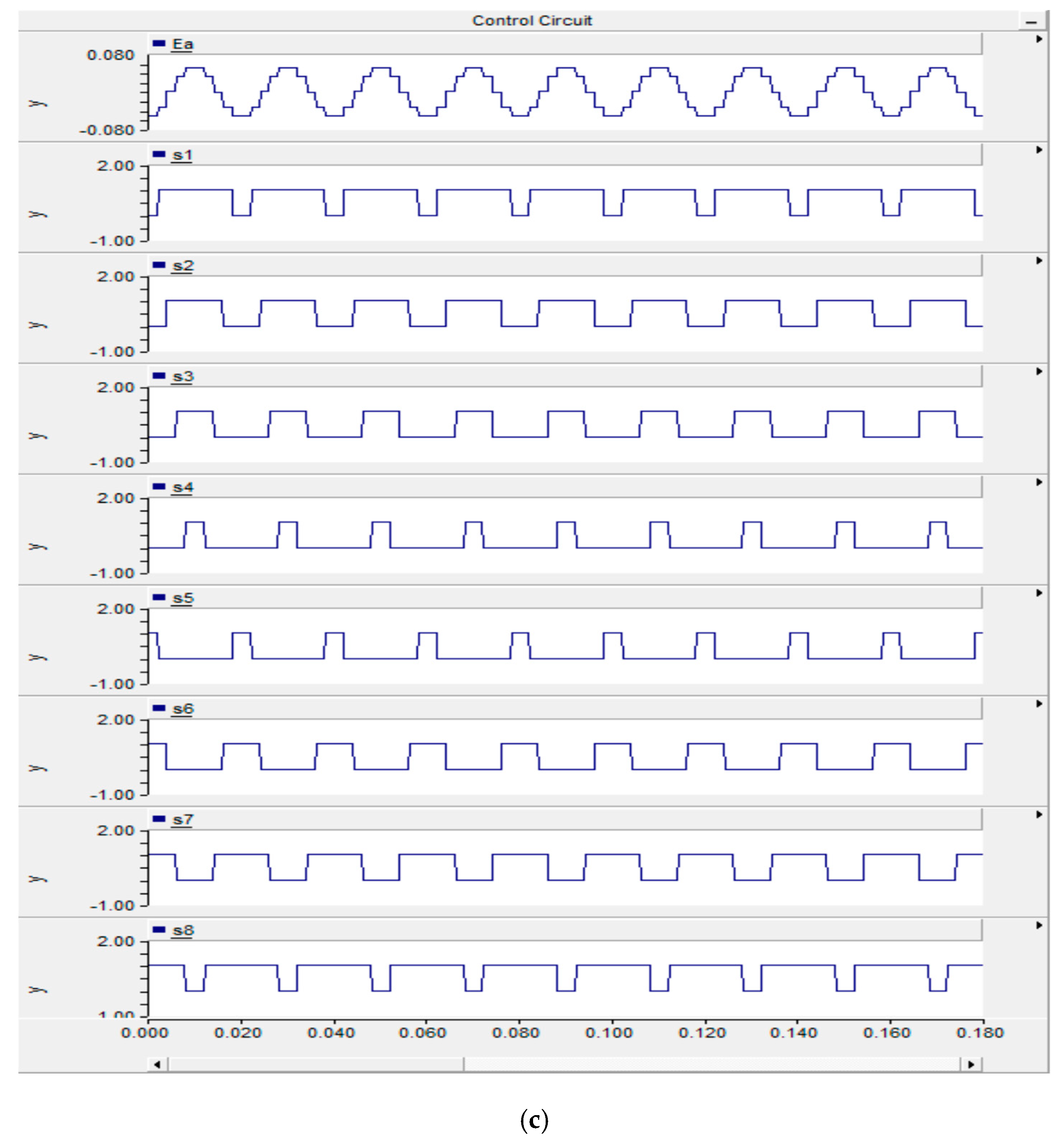

2.1.2. 5-Level DC-MLI PSCAD Simulations

2.2. Cascaded H-Bridge Multilevel Inverter (CHB-MLI)

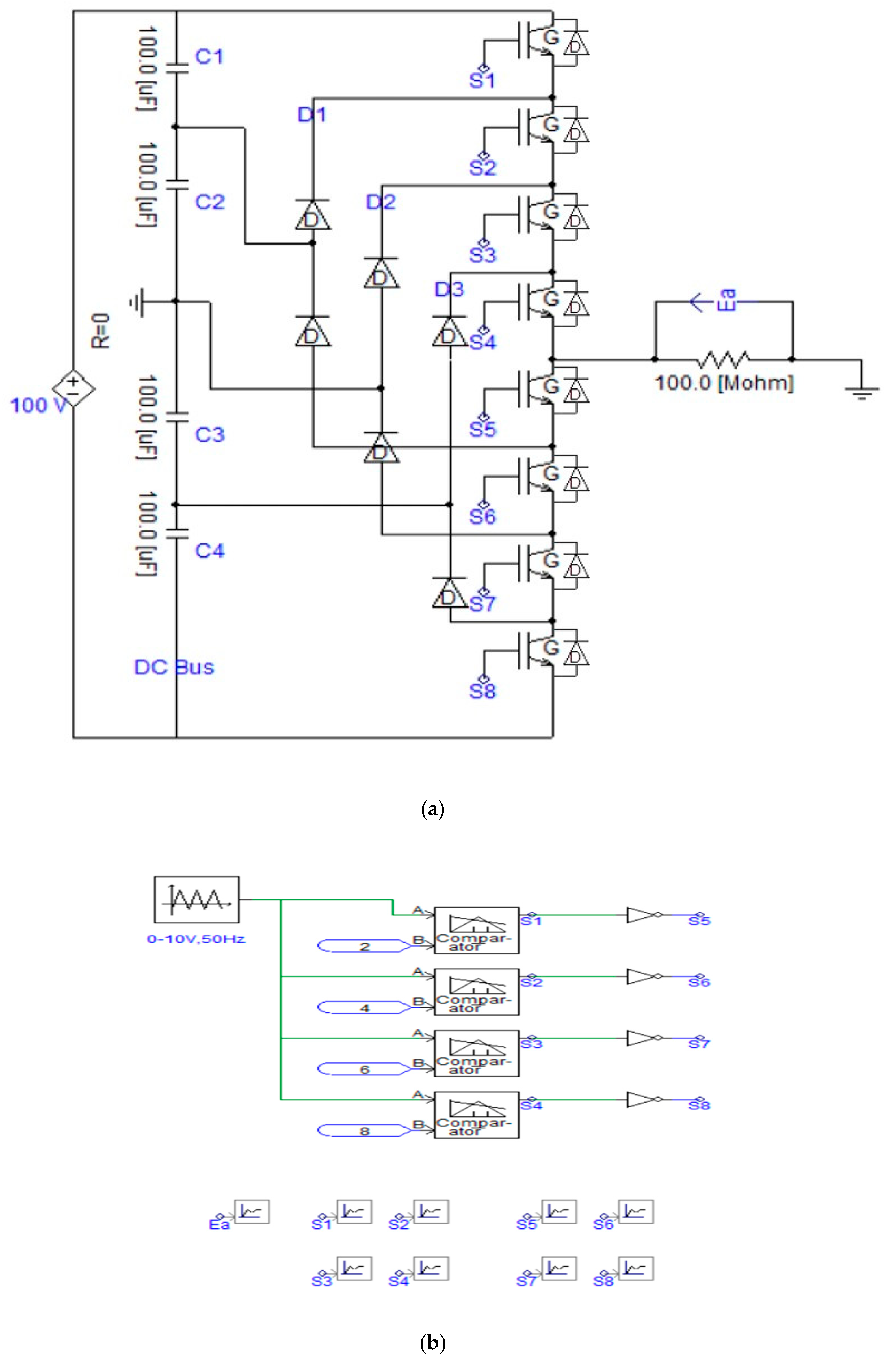

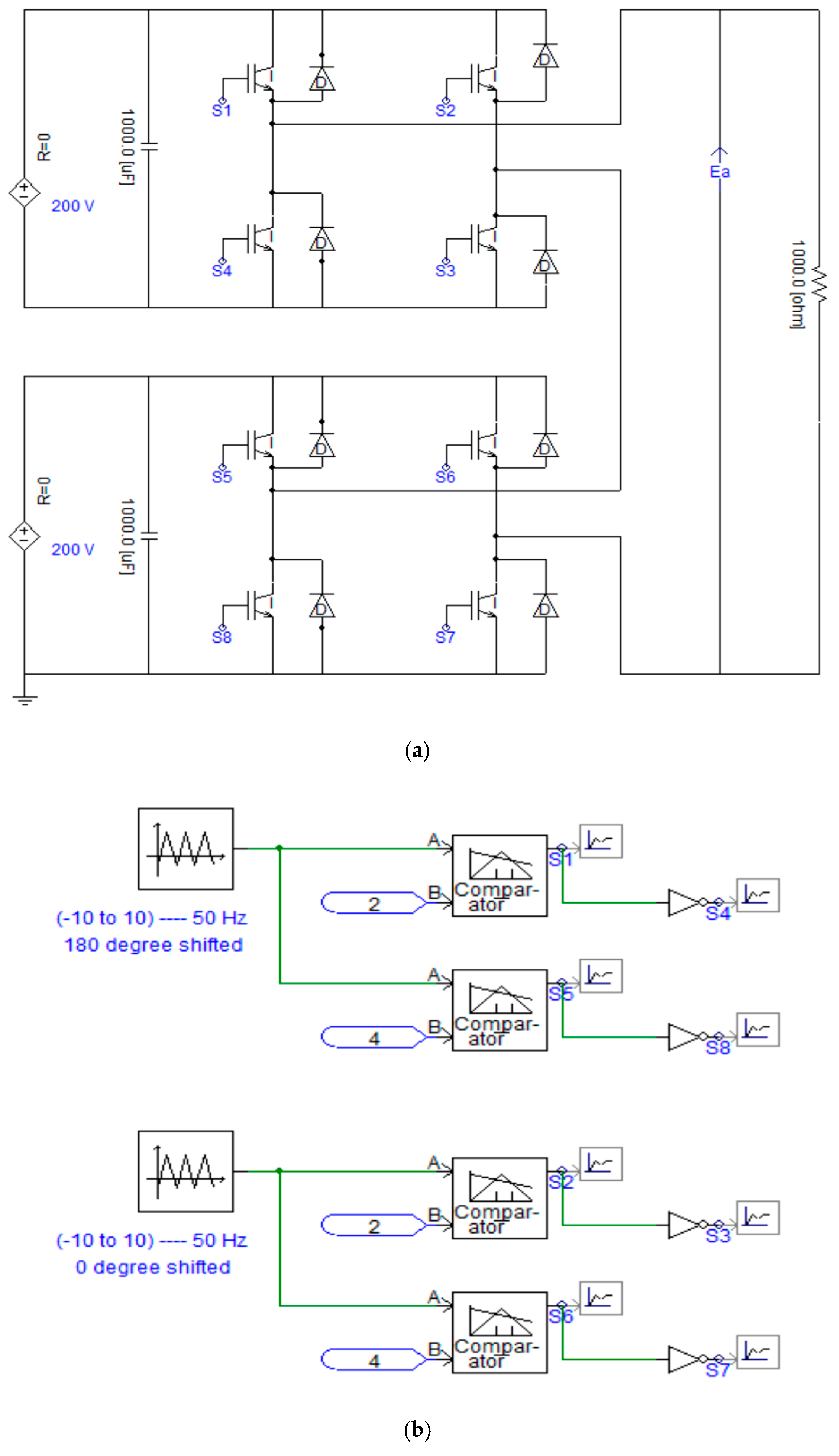

2.2.1. Three-Level CHB-MLI PSCAD Simulations

2.2.2. Five-Level CHB-MLI PSCAD Simulation

2.3. Flying-Capacitor Multilevel Inverter (FC-MLI)

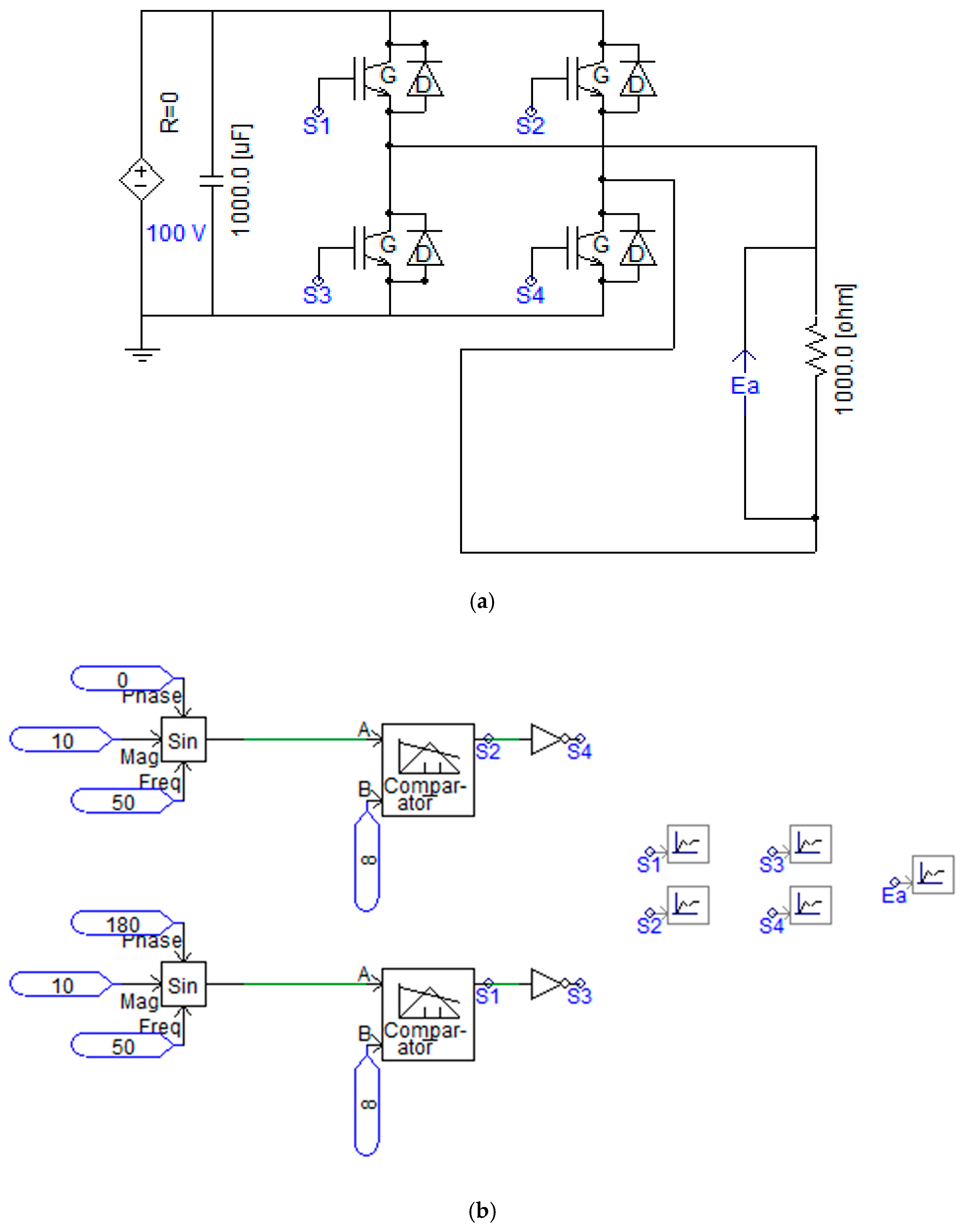

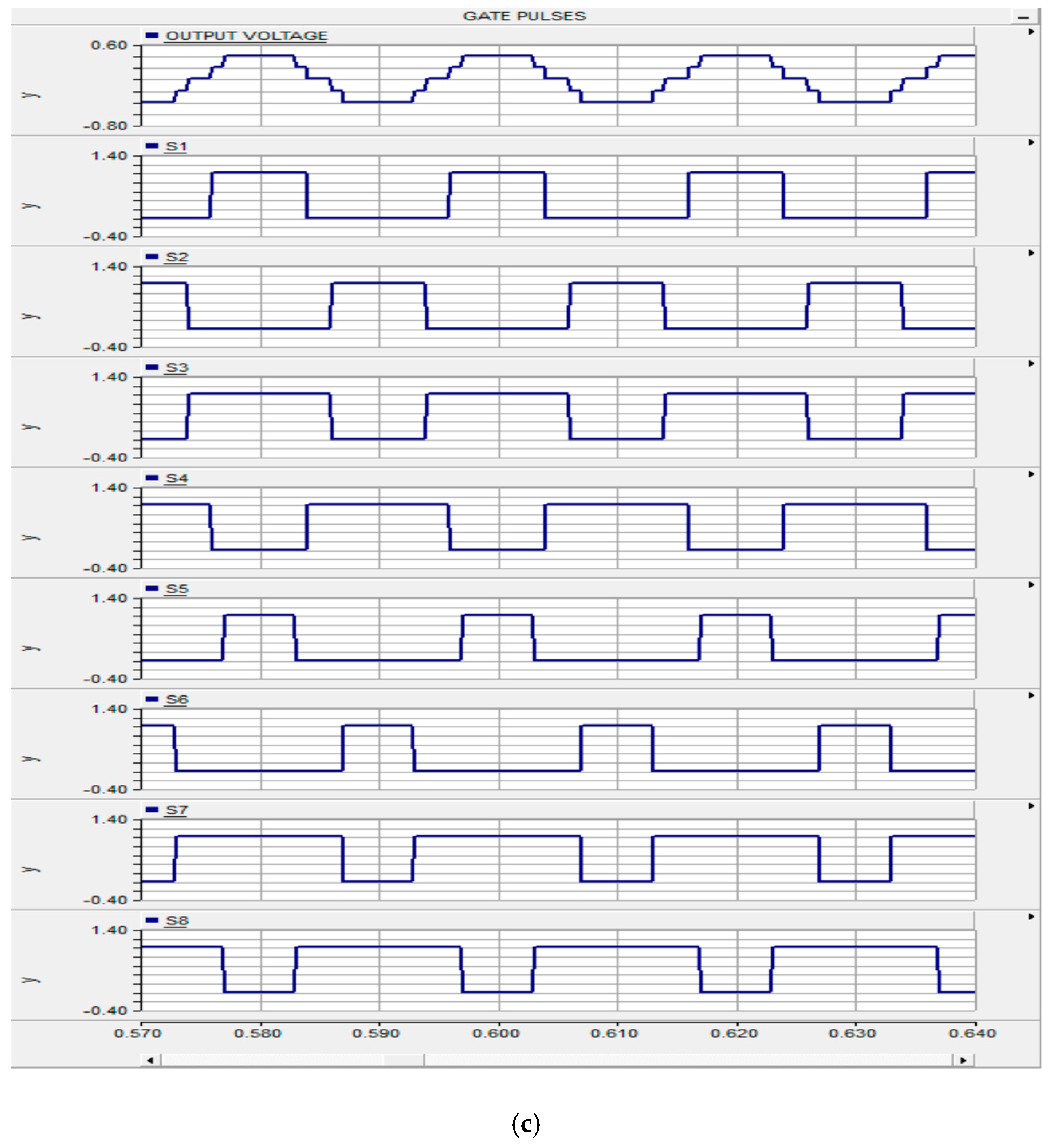

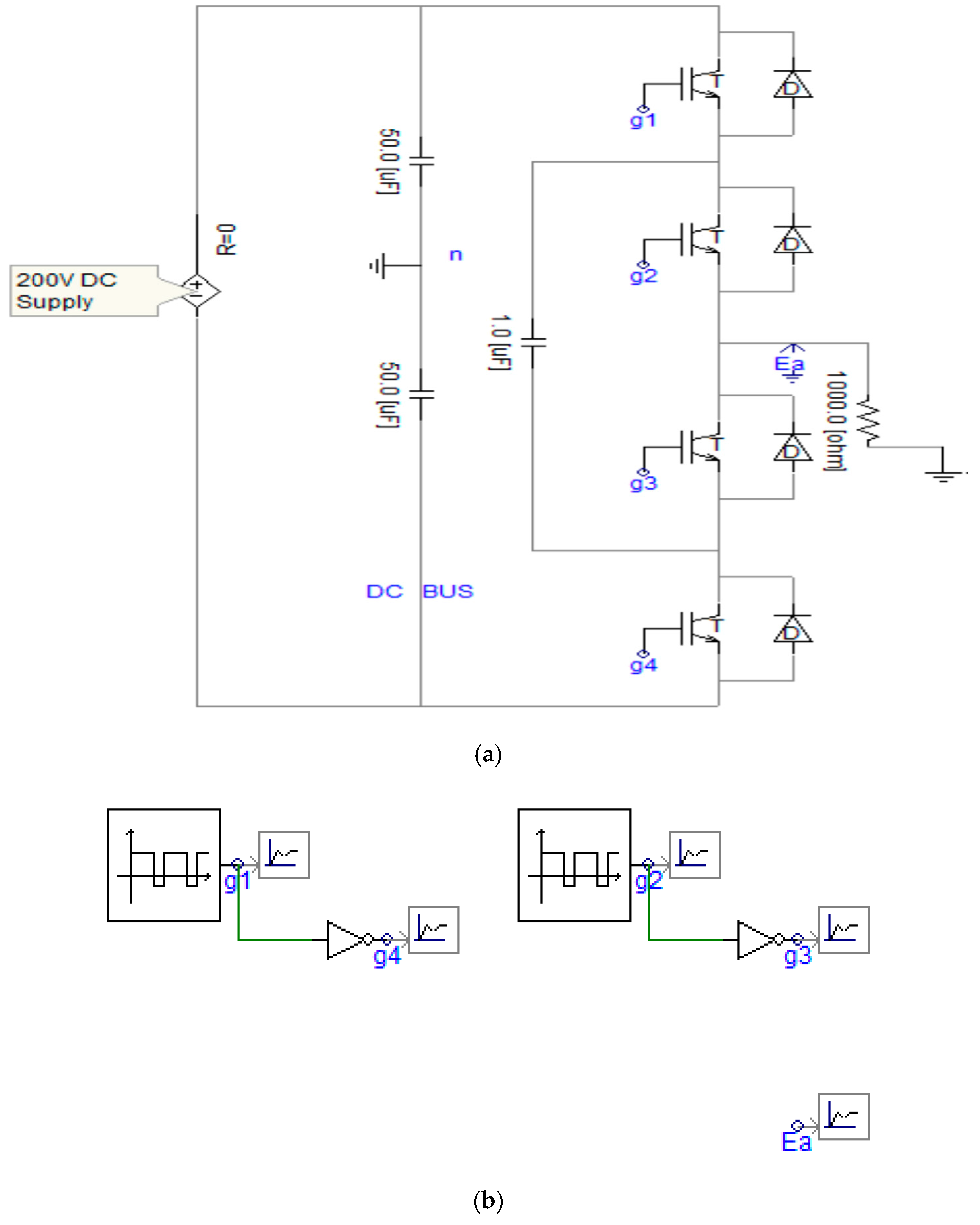

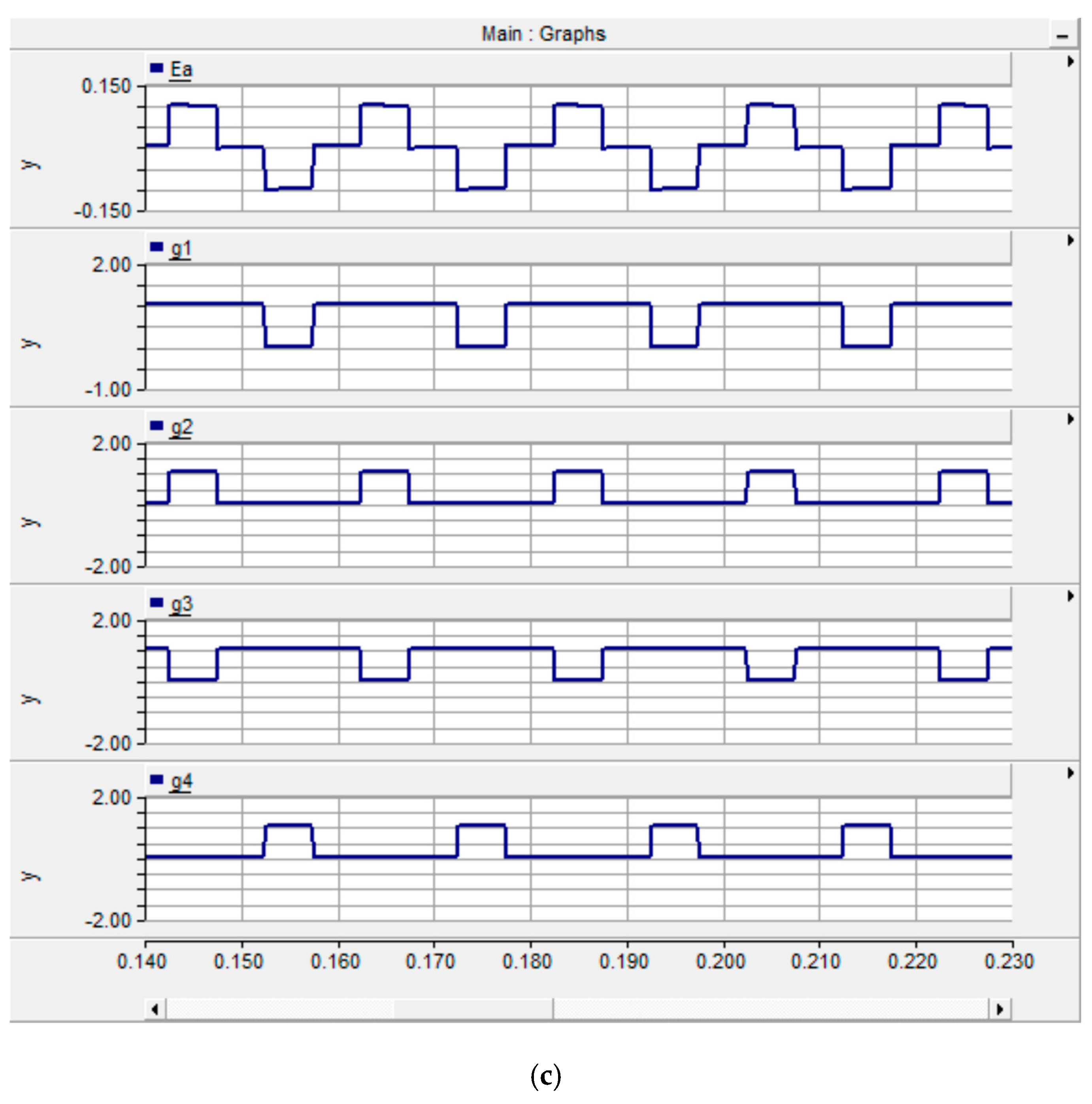

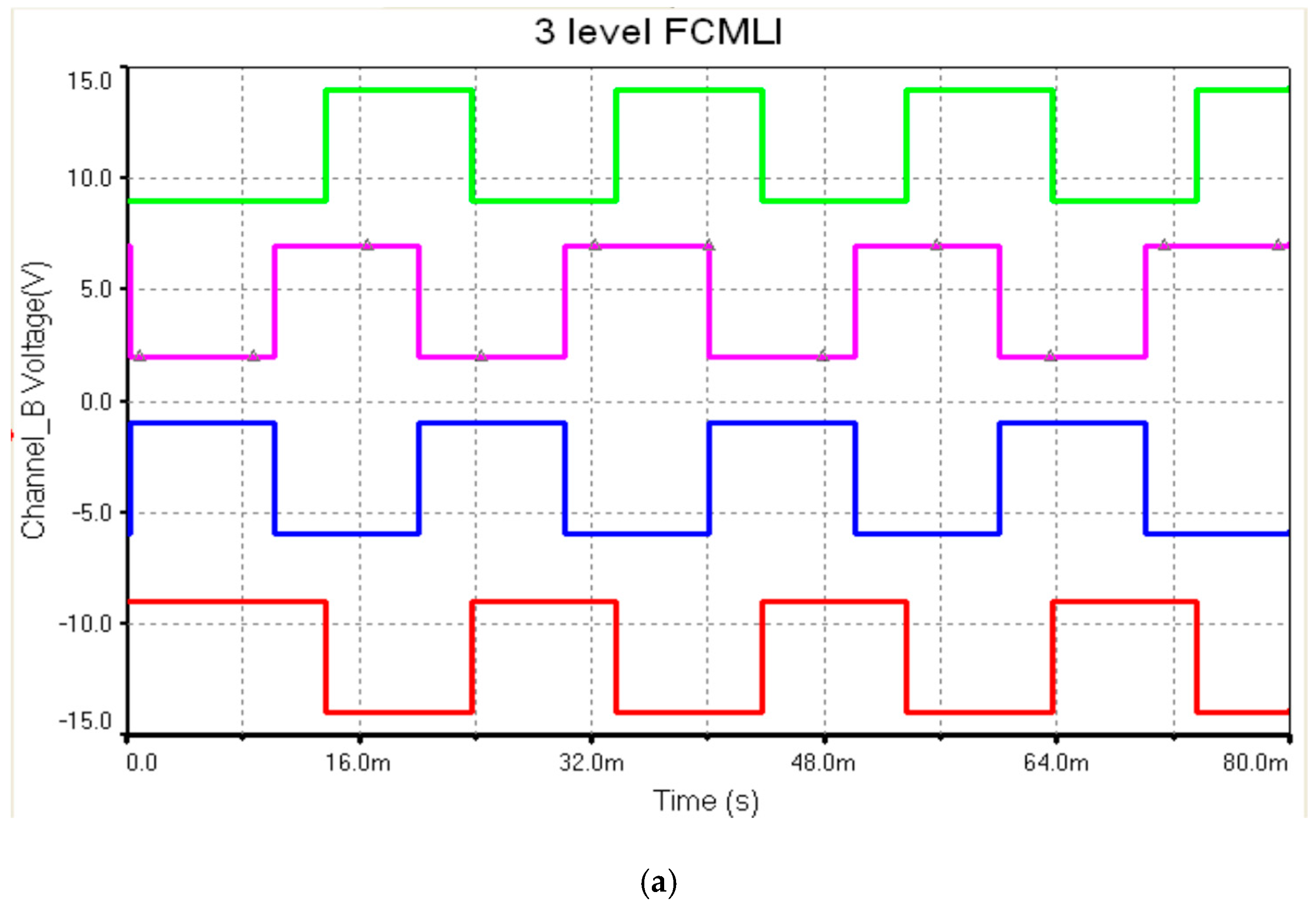

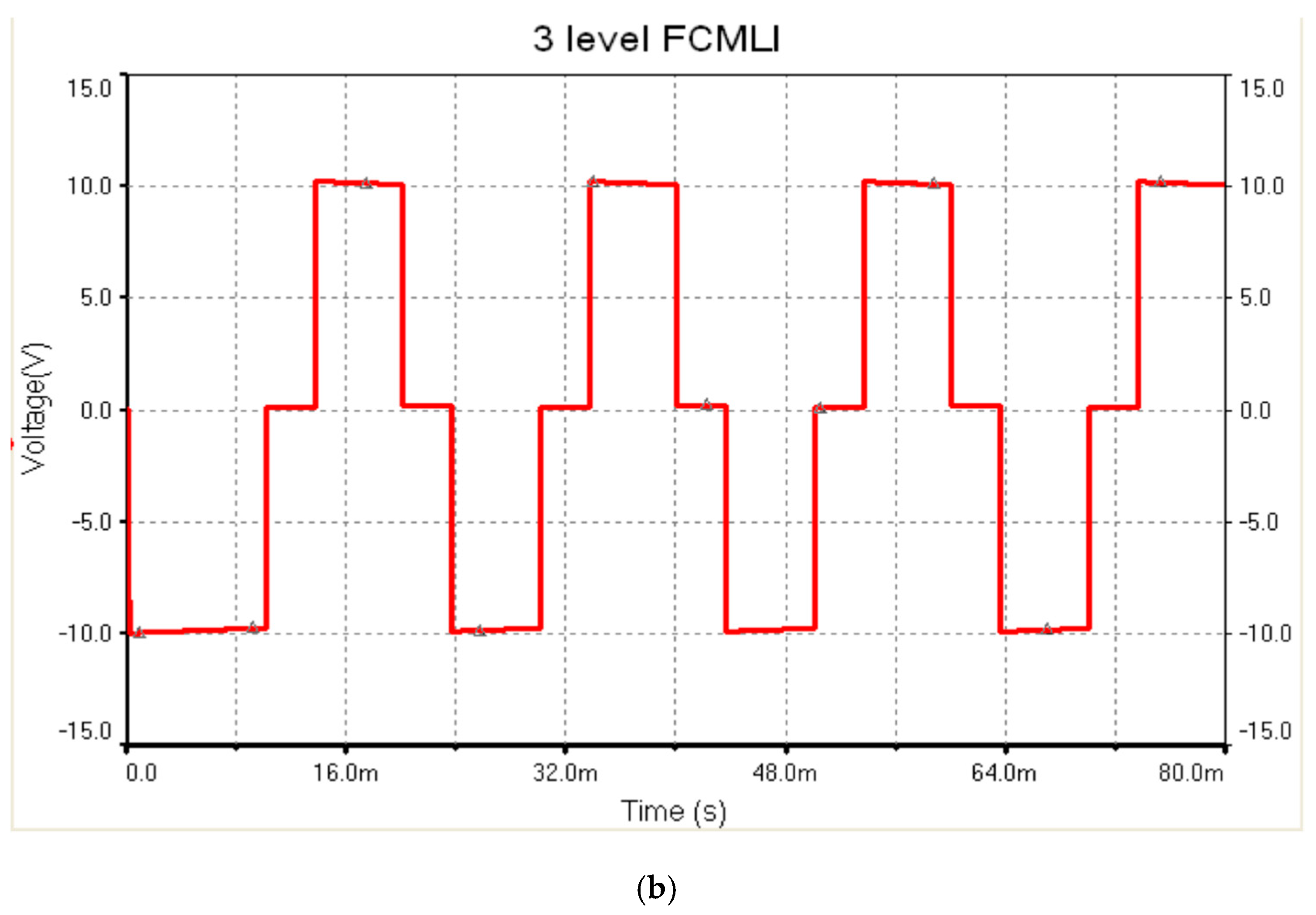

2.3.1. Three-Level FC-MLI PSCAD Simulations

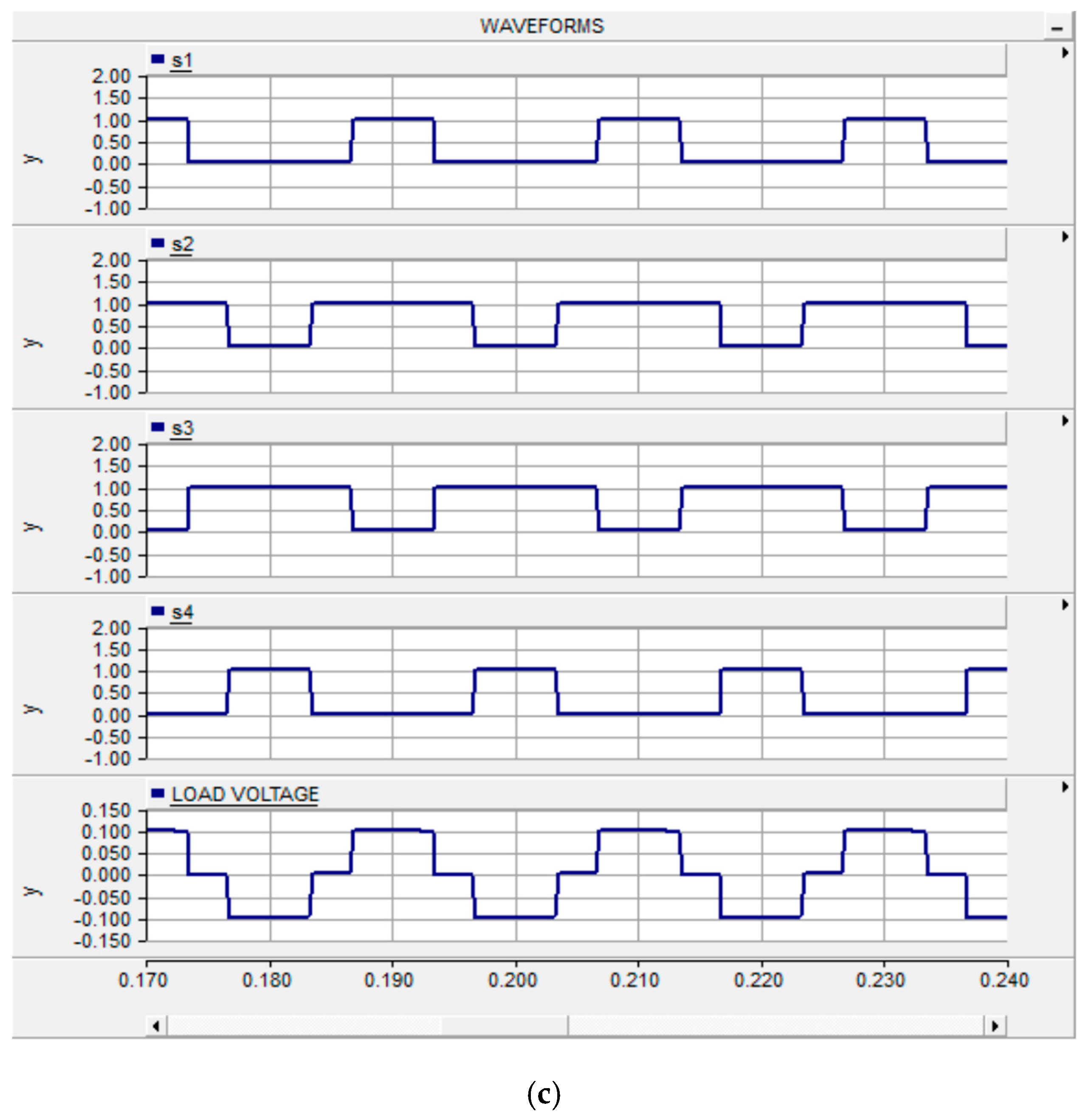

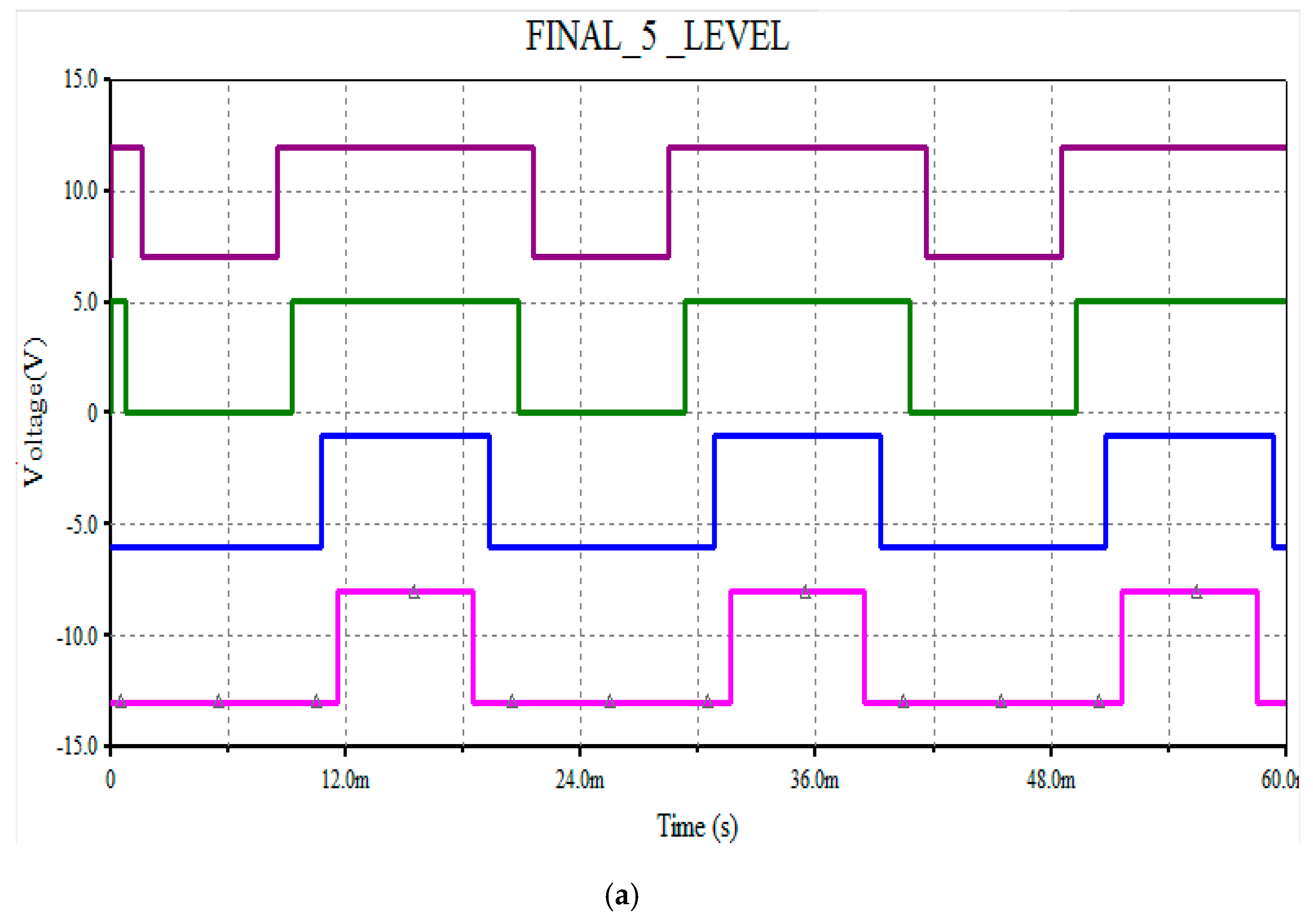

2.3.2. Five-Level FC-MLI PSCAD Simulations

3. Performance Evaluations of Different Multilevel Inverters and Characteristics Overview

3.1. Choosing Topology

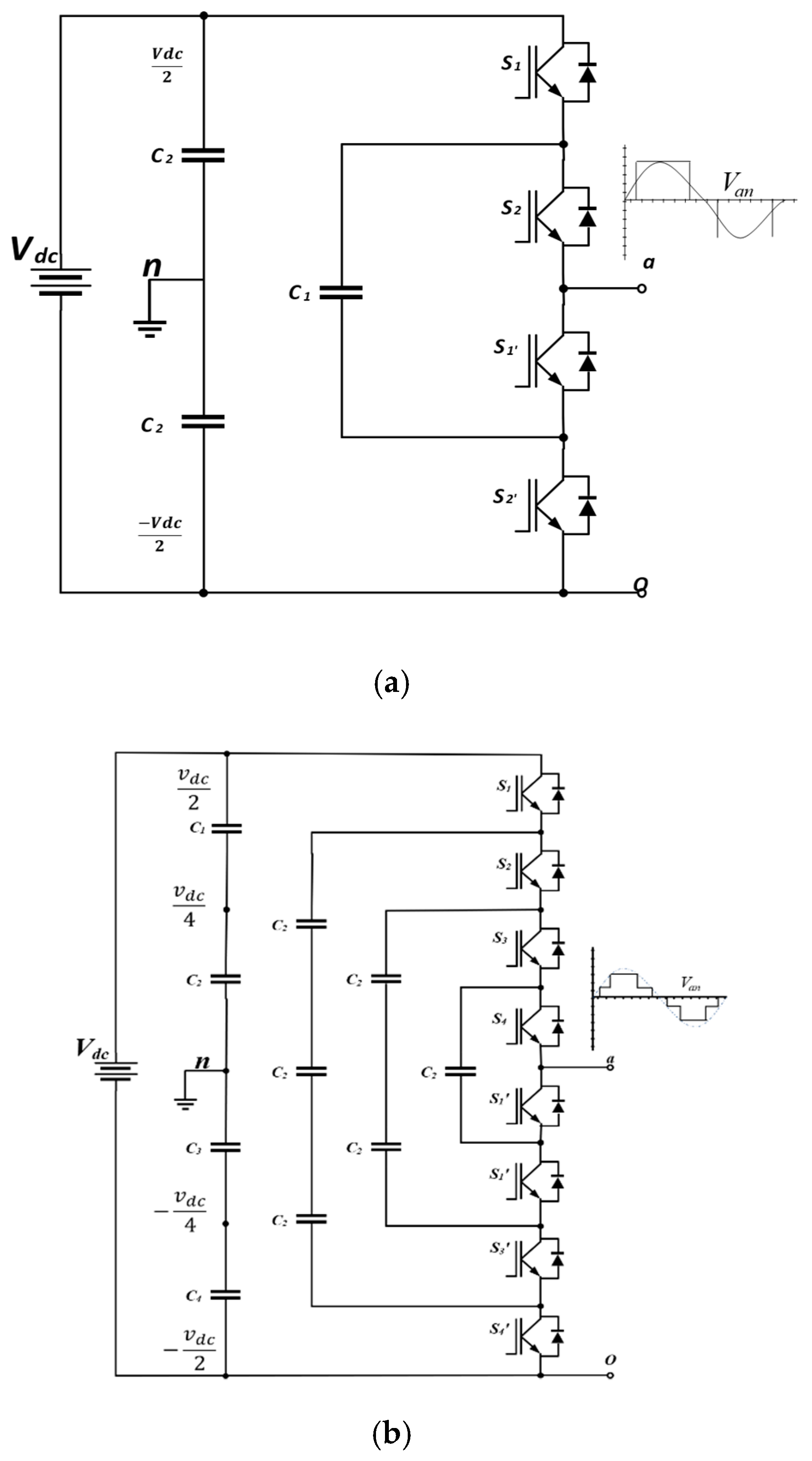

3.2. MULTISIM Simulations of FC-MLI

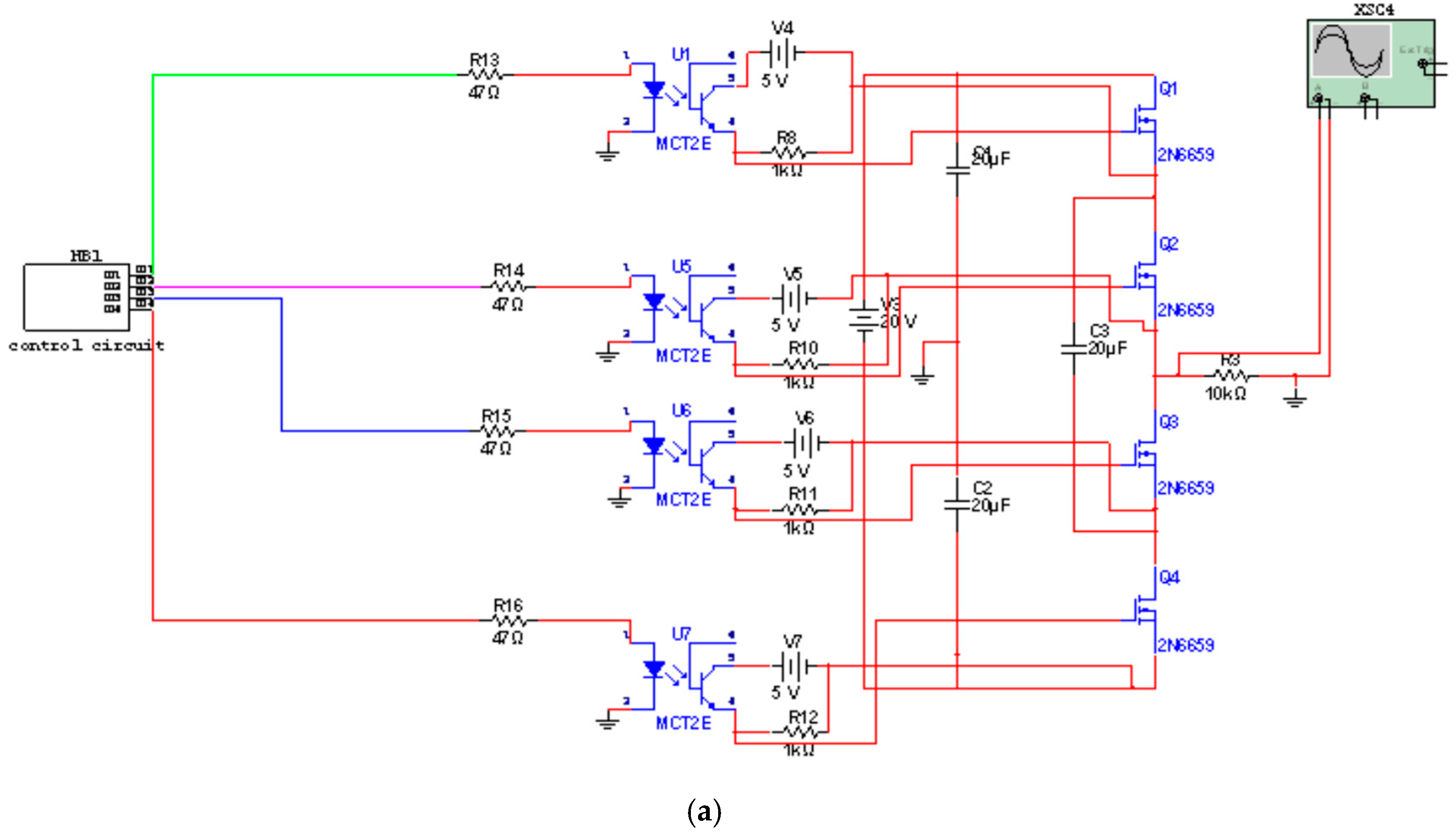

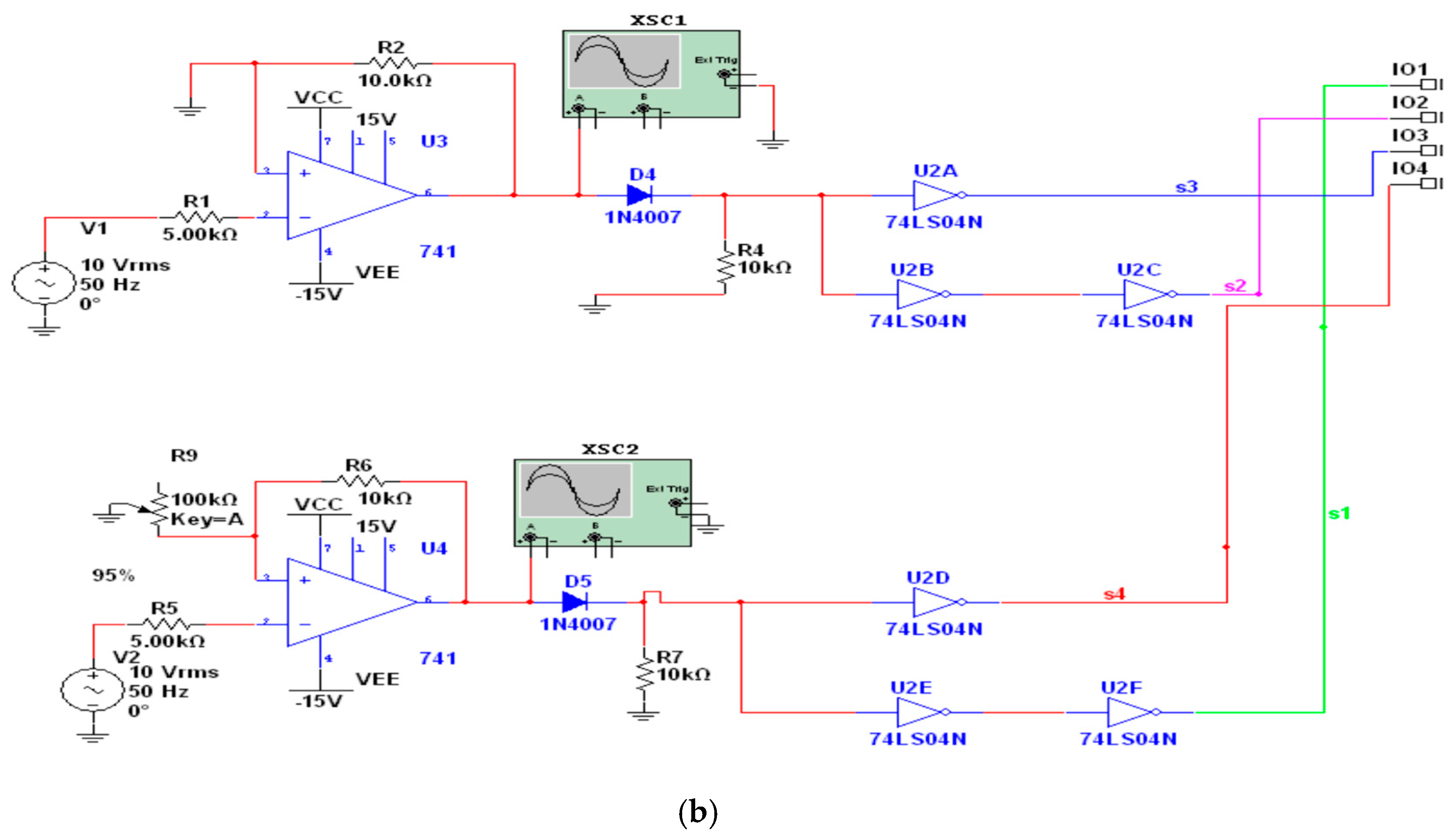

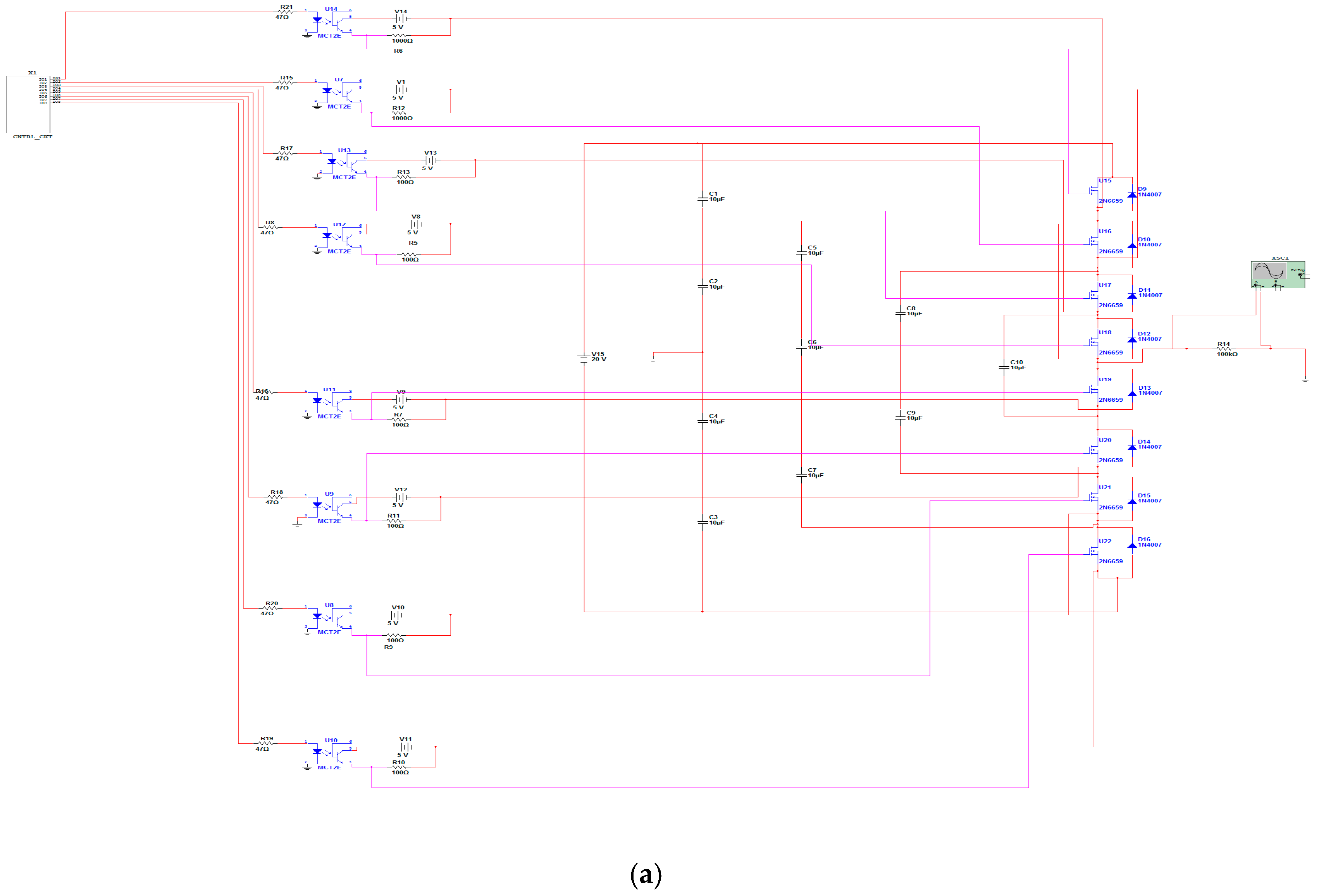

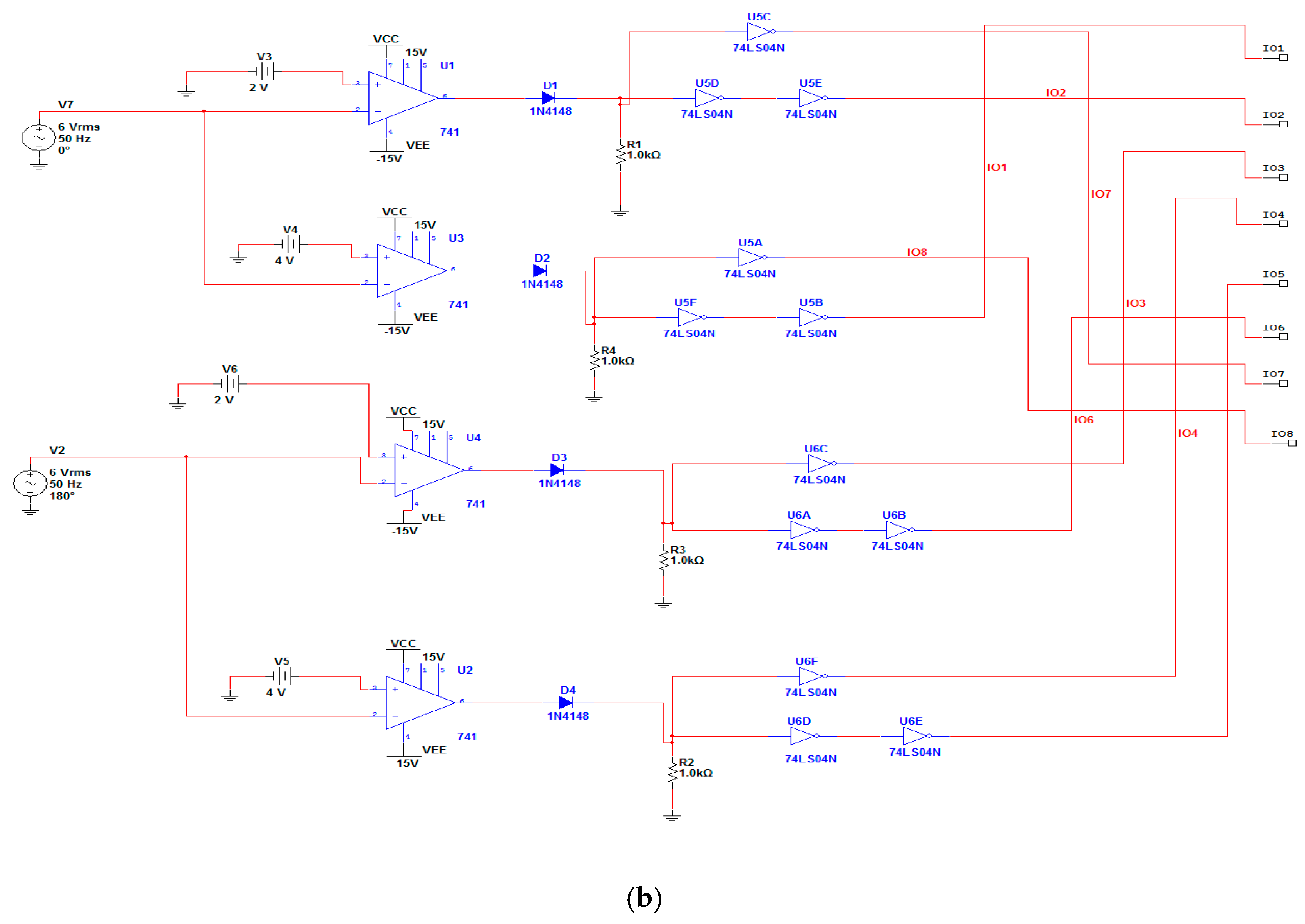

3.2.1. Three-Level FC-MLI MULTISIM Simulations

3.2.2. 5-Level FC-MLI MULTISIM Simulations

4. Harmonics Analysis of FC-MLI

4.1. Total Harmonic Distortion (THD)

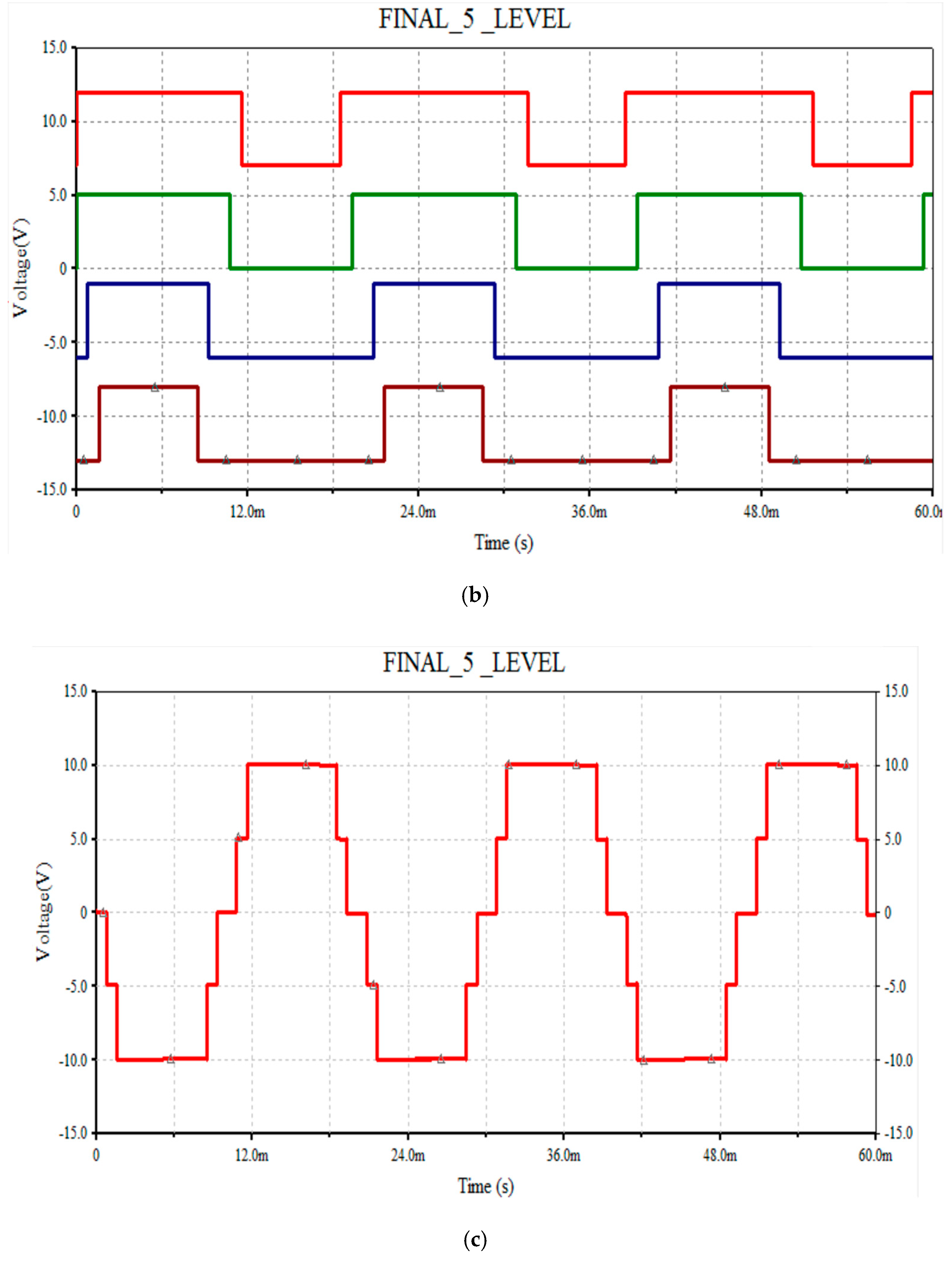

4.1.1. Harmonics Analysis of 3-Level FC-MLI

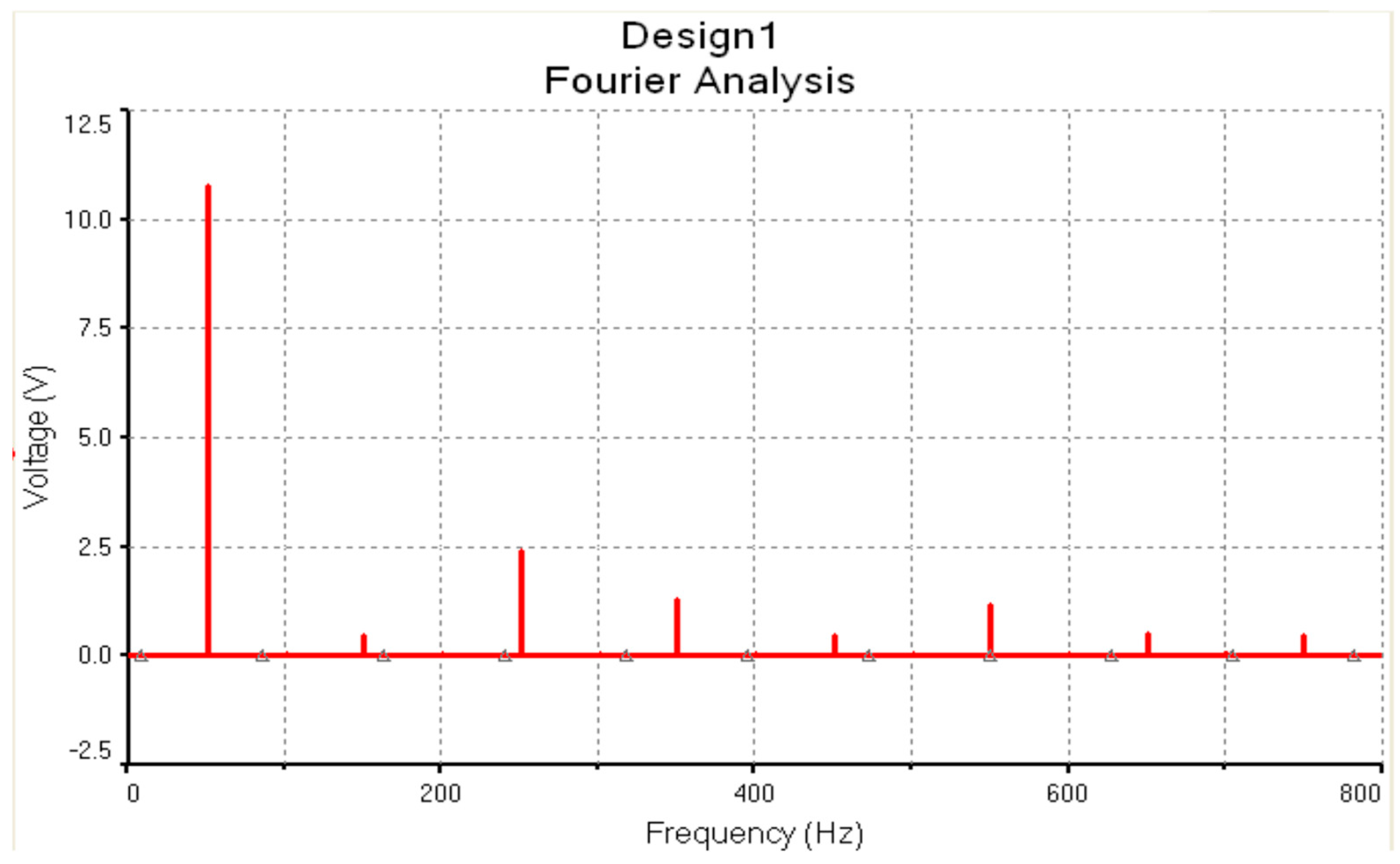

4.1.2. Harmonics Analysis of 5-Level FC-MLI

5. Pulse width modulation (PWM) control techniques

5.1. Open-Loop PWM Control Techniques

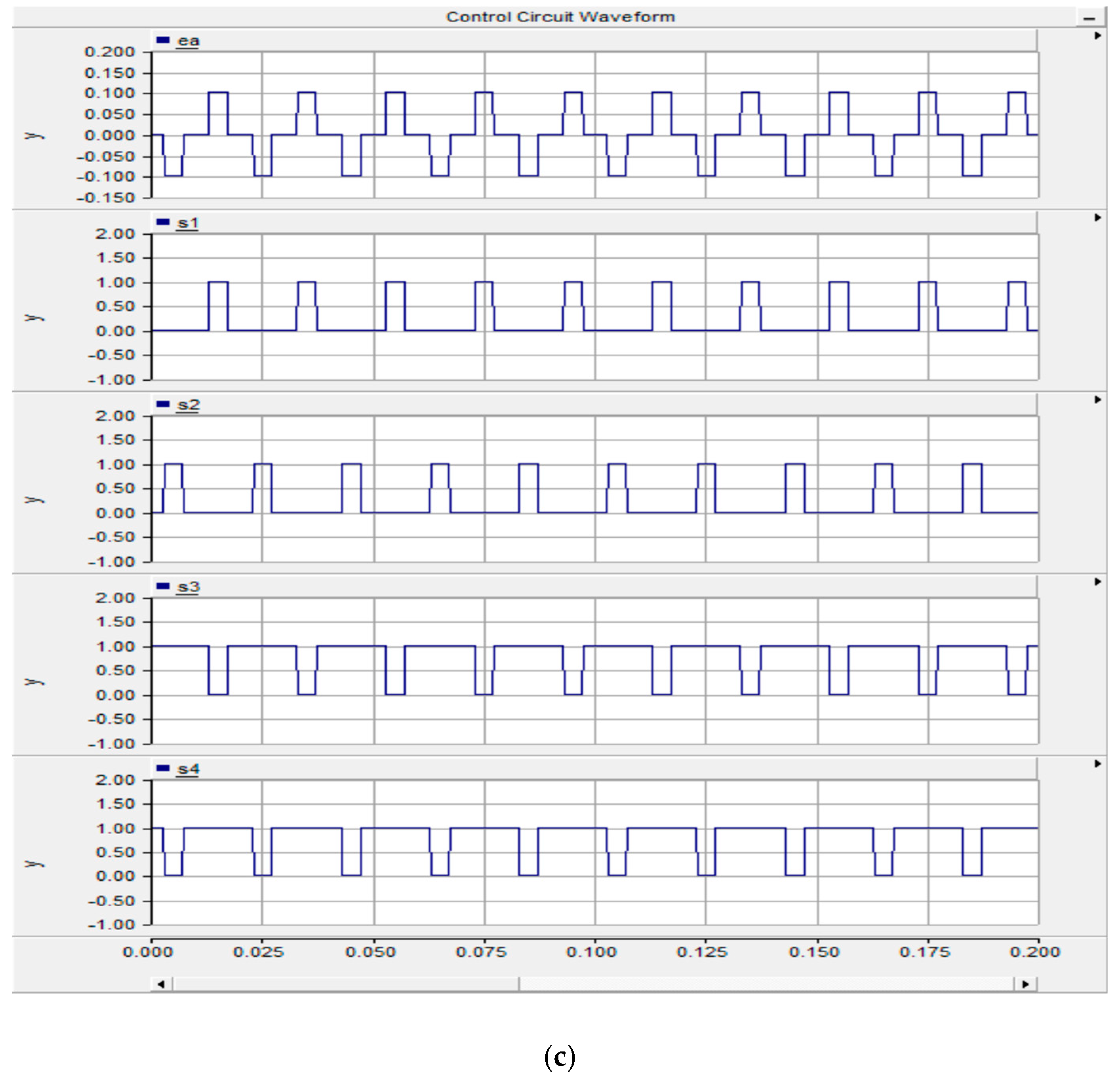

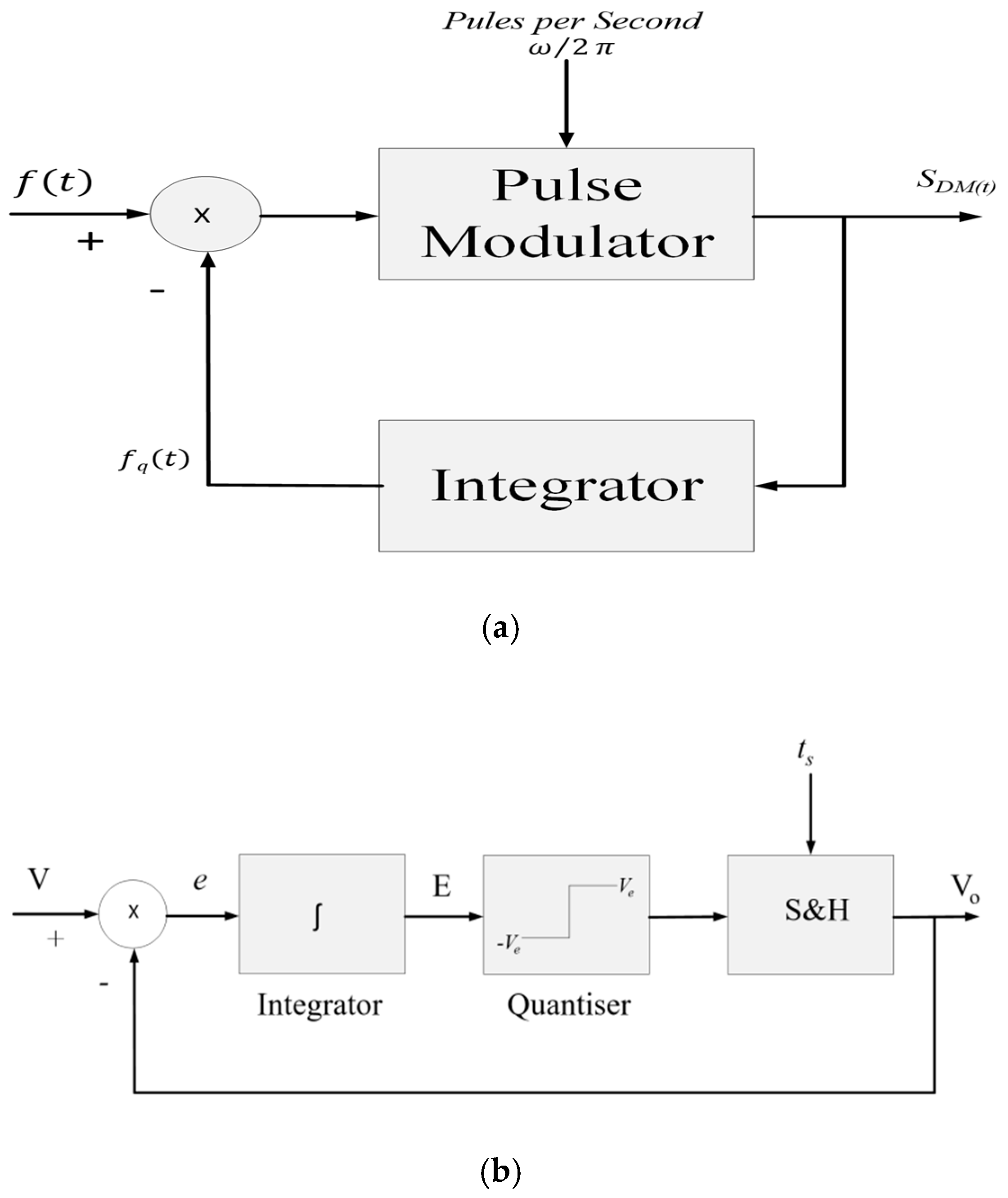

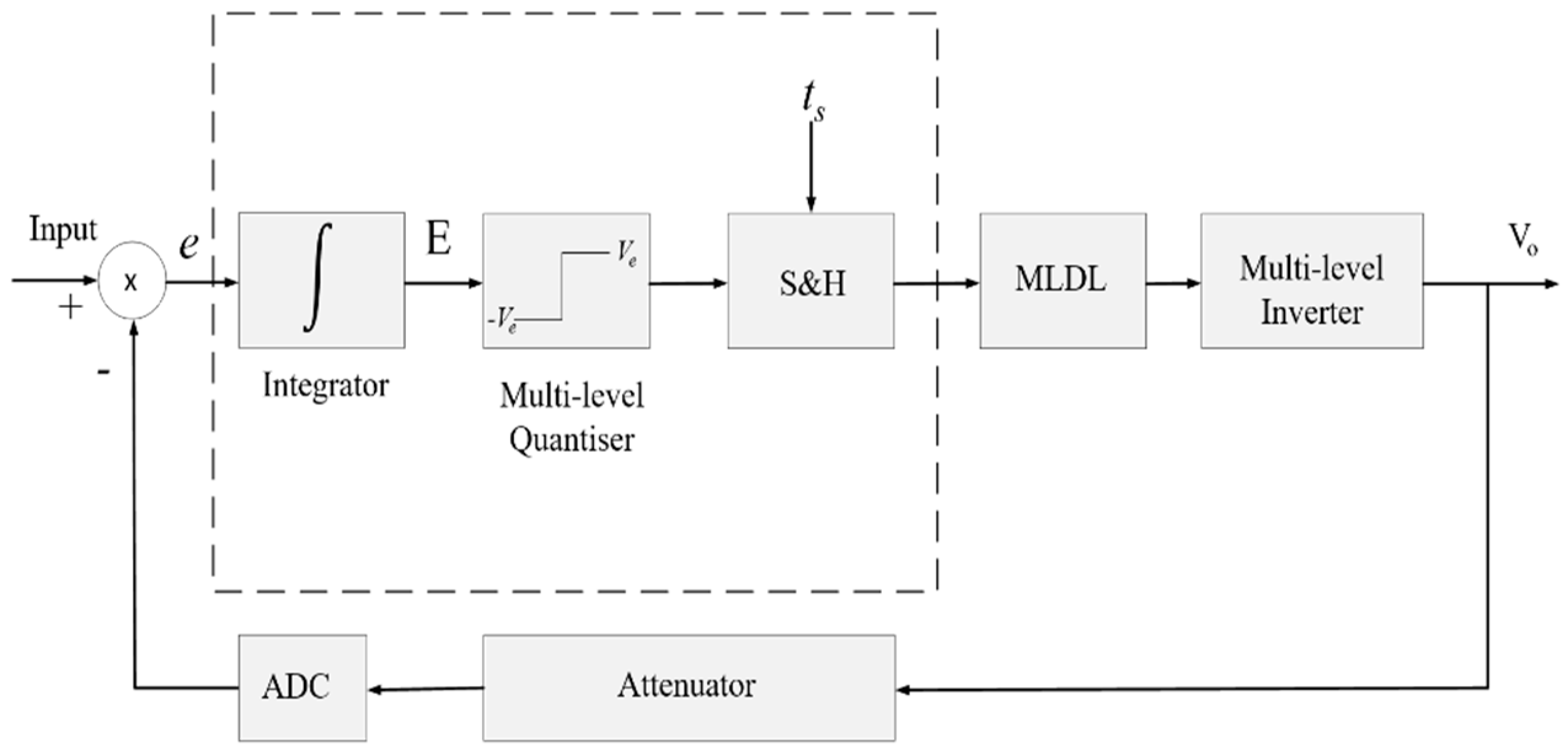

5.1.1. Sigma Delta PWM (SDM)

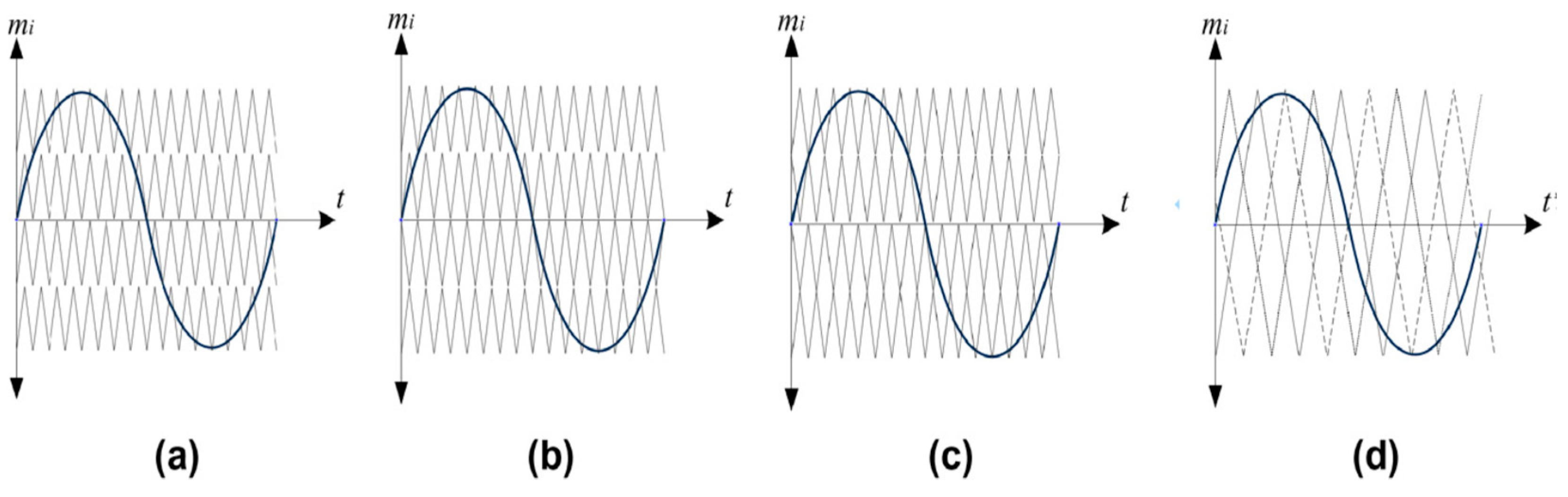

5.1.2. Sinusoidal PWM (SPWM)

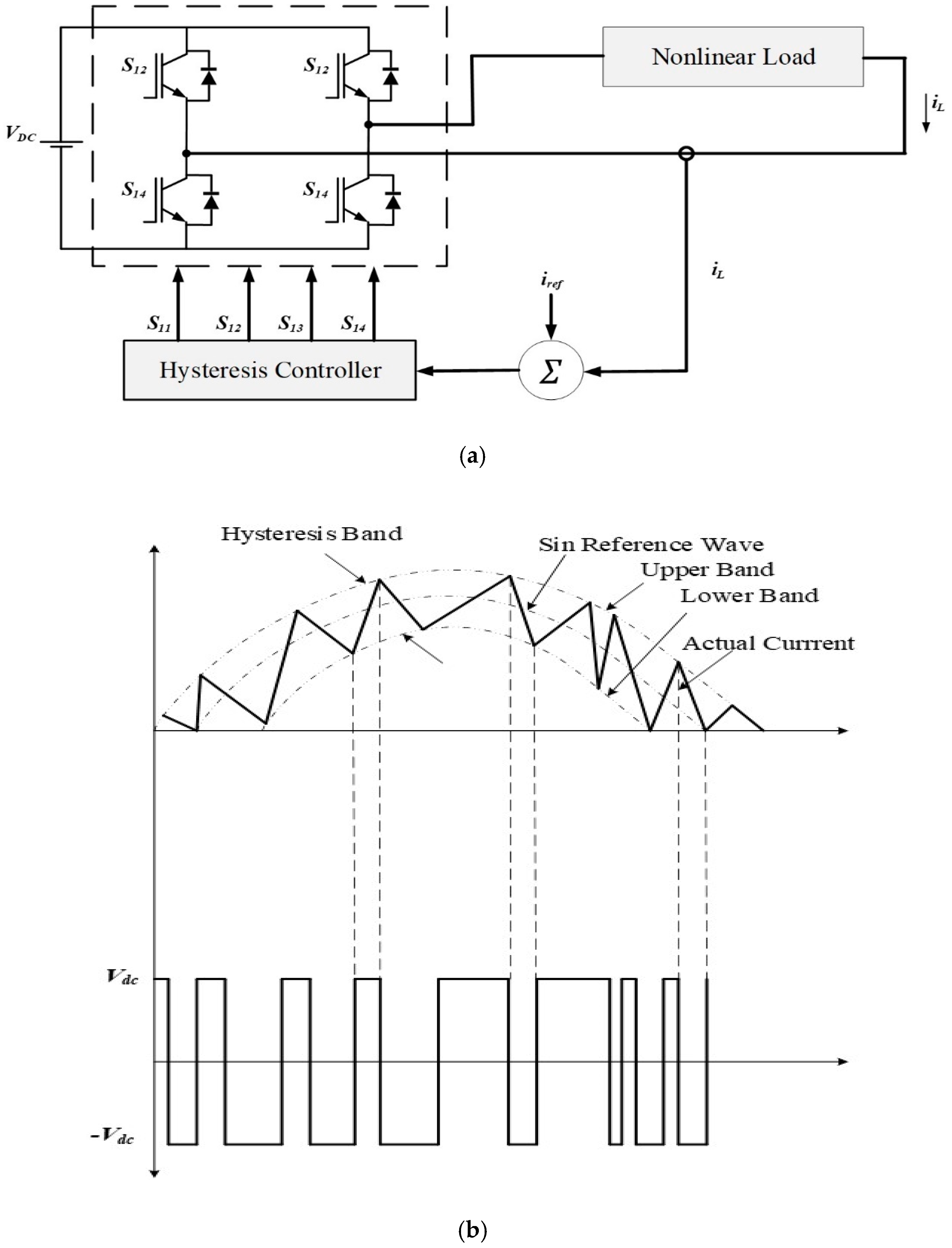

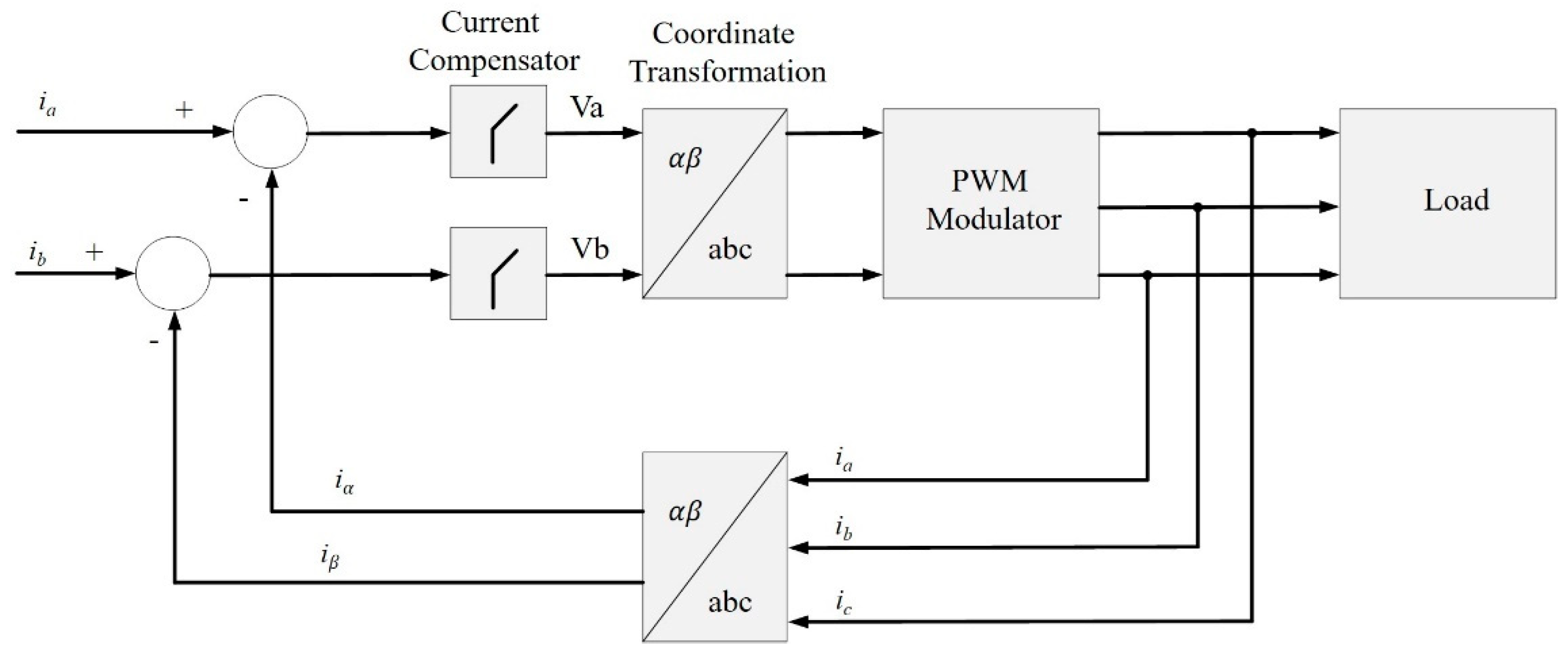

5.2. Closed-Loop PWM Control Techniques

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Rashid, M.H. Power Electronics Circuits, Devices and Application Handbook, 3rd ed.; Pearson Education: Upper Saddle River, NJ, USA, 2003. [Google Scholar]

- Rodriguez, J.; Jih-Sheng, L.; Fang, P. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Raghavendra, R.K.; Vijay, B.B.; Hiralal, M.S. A three-phase hybrid cascaded modular multilevel inverter for renewable energy environment. IEEE Trans. Power Electron. 2016, 32, 1070–1078. [Google Scholar]

- Youssef, O.; Kamal, A.H.; Luc-Andre, G. Packed u cells multilevel converter topology: Theoretical study and experimental validation. IEEE Trans. Ind. Electron. 2011, 58, 1294–1306. [Google Scholar]

- Sumit, K.C.; Chandan, C. A new asymmetric multilevel inverter topology suitable for solar PV applications with varying irradiance. IEEE Trans. Sustain. Energy 2017, 8, 1496–1506. [Google Scholar]

- Vahid, D.; Arash, K.S.; Mostafa, A.; Soheila, E.; Keith, A.C. A new family of modular multilevel converter based on modified flying-capacitor multicell converters. IEEE Trans. Power Electron. 2015, 30, 138–147. [Google Scholar]

- Vahid, D.; Saeedeh, D. Analytical modelling of single-phase stacked multicell multilevel converters exploiting kapteyn (fourier–bessel) series. IET Power Electron. 2013, 6, 1220–1238. [Google Scholar]

- Arash, K.; Vahid, D.; Mostafa, A.; Saeedeh, D. Reduced dc voltage source flying capacitor multicell multilevel inverter: Analysis and implementation. IET Power Electron. 2014, 7, 439–450. [Google Scholar]

- Arash, K.; Mostafa, A.; Keith, A.C.; Vahid, D. A new breed of optimized symmetrical and asymmetrical cascaded multilevel power converters. IEEE J. Emerg Sel. Top. Power Electron. 2015, 3, 1160–1170. [Google Scholar]

- Saeedeh, D.; Ebrahim, B.; Soheila, E.; Vahid, D.; Mehran, S. Flying-capacitor stacked multicell multilevel voltage source inverters: Analysis and modelling. IET Power Electron. 2014, 7, 2969–2987. [Google Scholar]

- Arash, K.; Vahid, D.; Keith, A.C. New flying-capacitor-based multilevel converter with optimized number of switches and capacitors for renewable energy integration. IEEE Trans. Energy Convers 2016, 31, 846–859. [Google Scholar]

- Margarita, N.; Samir, K.; Sibylle, D.; Jose, R. Reduced multilevel converter: A novel multilevel converter with a reduced number of active switches. IEEE Trans. Ind. Electron. 2018, 65, 3636–3645. [Google Scholar]

- Amir, T.; Jafar, A.; Mohammad, R. A multilevel inverter structure based on a combination of switched capacitors and dc sources. IEEE Trans. Ind. Inform. 2017, 13, 2162–2171. [Google Scholar]

- Meysam, S.; Jafar, A.; Seyyed, M.H. Cascaded multilevel inverter based on symmetric asymmetric dc sources with reduced number of components. IET Power Electron. 2017, 10, 1468–1478. [Google Scholar]

- Reza, B.; Majid, M.; Elyas, Z.; Hossein, M.K.; Frede, B. A new boost switched-capacitor multilevel converter with reduced circuit devices. IEEE Trans. Power Electron. 2017, 33, 6738–6754. [Google Scholar]

- Krishna, K.G.; Alekh, R.; Pallavee, B.; Lalit, K.S.; Shailendra, J. Multilevel inverter topologies with reduced device count: A review. IEEE Trans. Power Electron. 2016, 31, 135–151. [Google Scholar]

- Kavitha, M.; Arunkumar, A.; Gokulnath, N.; Arun, S. New Cascaded H-Bridge Multilevel Inverter Topology with Reduced Number of Switches and Sources. IOSR-JEEE 2012, 2, 26–36. [Google Scholar] [CrossRef]

- Ke, Ma.; Frede, B. Modulation Methods for Neutral-Point-Clamped Wind Power Converter Achieving Loss and Thermal Redistribution under Low-Voltage-Ride-Through. IEEE Trans. on Ind. Electron. 2013, 61, 835–845. [Google Scholar]

- Hochgra, C.; Lasseter, R.; Divan, D.; Lipo, T.A. Comparison of multilevel inverters for static VAR compensation. In Proceedings of the IEEE Industry Applications Society Annual Meeting, Denver, CO, USA, 2–6 October 1994. [Google Scholar]

- Kuhn, H.; Rüger, N.E.; Mertens, A. Control strategy for multilevel inverter with non-ideal dc sources. In Proceedings of the IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007. [Google Scholar]

- Panagis, P.; Stergiopoulos, F.; Marabeas, P.; Manias, S. Comparison of state-of-the-art multilevel inverters. In Proceedings of the IEEE Annual Power Electronics Specialist Conference PESC, Rhodes Greece, 15–19 June 2008. [Google Scholar]

- Sumithira, T.R.; Nirmal, A. Elimination of harmonics in multilevel inverters connected to solar photovoltaic systems using ANFIS: An experimental case study. Appl. Res. Technol. 2013, 11, 124–132. [Google Scholar] [CrossRef]

- Jih-Sheng, L.; Fang, P. Multilevel converters-a new breed of power converters. IEEE Trans. Ind. Appl. 1996, 32, 509–517. [Google Scholar] [CrossRef]

- Mohammadreza, D. Analysis of Different Topologies of Multilevel Inverter Thesis; Chalmers University of Technology: Gothenburg, Sweden, 2010. [Google Scholar]

- Khairnar, D.D.; Deshmukh, V.M. Performance Analysis of Diode Clamped 3 Level MOSFET Based Inverter. Int. Electr. Eng. J. 2014, 5, 1484–1489. [Google Scholar]

- Mehdi, N.; Bin, W.; Navid, R. A Novel Five level voltage source inverter with sinusoidal pulse width modulator for medium voltage applications. IEEE Trans. Power Electron. 2016, 31, 1959–1967. [Google Scholar]

- Kai, T.; Bin, W.; Mehdi, N.; Xu, D.D.; Cheng, Z.; Navid, R. A Capacitor voltage balancing method for Nested neutral point clamped (NNPC) inverter. IEEE Trans. Power Electron. 2015, 31, 2575–2583. [Google Scholar]

- Song, B.M.; Kim, J.; Lai, J.S.; Seong, K.C.; Kim, H.J.; Park, S.S. A multilevel soft-switching inverter with inductor coupling. IEEE Trans. Ind. Appl. 2001, 37, 628–636. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H. Multi-level conversion: High voltage choppers and voltage-source inverters. In Proceedings of the IEEE Power Electronics Specialists Conference, Toledo, Spain, 29 June–3 July 1992. [Google Scholar]

- Xu, L.; Agelidis, V.G. Active capacitor voltage control of flying capacitor multilevel converters. IEEE Electr. Power Appl. 2004, 151, 313–320. [Google Scholar] [CrossRef]

- Feng, C.; Liang, J.; Agelidis, V.G.; Green, T.C. A multi-modular system based on parallel-connected multilevel flying capacitor converters controlled with fundamental frequency SPWM. In Proceedings of the 32nd IEEE Conference on Industrial Electronics, Paris, France, 7–10 November 2006. [Google Scholar]

- Nami, A.; Liang, J.; Dijkhuizen, F.; Demetriades, G.D. Modular multilevel converters for HVDC applications: Review on converter cells and functionalities. IEEE Trans. Power Electron. 2015, 30, 18–36. [Google Scholar] [CrossRef]

- Hiller, M. Method for Controlling a Polyphase Converter with Distributed Energy Stores. U.S. Patent 12/067, 555, 20 March 2008. [Google Scholar]

- Ilves, K.; Taffner, F.; Norrga, S.; Antonopoulos, A.; Harnefors, L.; Nee, H.-P. A submodule implementation for parallel connection of capacitors in modular multilevel converters. IEEE Trans. Power Electron. 2015, 30, 3518–3527. [Google Scholar] [CrossRef]

- Farhadi, M.; Babaei, E. Cross-switched multilevel inverter: An innovative topology. IET Trans. Power Electron. 2013, 6, 642–651. [Google Scholar] [CrossRef]

- Mathew, E.C.; Ghat, M.B.; Shukla, A. A generalized cross-connected submodule structure for hybrid multilevel converters. IEEE Trans. Ind. Appl. 2016, 52, 3159–3170. [Google Scholar] [CrossRef]

- Wang, Y.; Marquardt, R. Future HVDC-grids employing modular multilevel converters and hybrid DC-breakers. In Proceedings of the 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 3–5 September 2013. [Google Scholar]

- Marquardt, R. Modular multilevel converter topologies with DC-short circuit current limitation. In Proceedings of the 8th International Conference on Power Electronics—ECCE Asia, Jeju, Korea, 30 May–3 June 2011. [Google Scholar]

- Li, X.; Song, Q.; Liu, W.; Zhu, Z.; Xu, S. Experiment on DC-fault ride through of MMC using a half-voltage clamp submodule. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 1273–1279. [Google Scholar] [CrossRef]

- Elserougi, A.A.; Massoud, A.M.; Ahmed, S. A switched-capacitor submodule for modular multilevel HVDC converters with DC-fault blocking capability and a reduced number of sensors. IEEE Trans. Power Del. 2016, 31, 313–322. [Google Scholar] [CrossRef]

- Qin, J.; Saeedifard, M.; Rockhill, A.; Zhou, R. Hybrid design of modular multilevel converters for HVDC systems based on various submodule circuits. IEEE Trans. Power Del. 2015, 30, 385–394. [Google Scholar] [CrossRef]

- Nami, A.; Wang, L.; Dijkhuizen, F.; Shukla, A. Five level cross connected cell for cascaded converters. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 3–5 September 2013. [Google Scholar]

- Li, R.; Fletcher, J.E.; Xu, L.; Holliday, D.; Williams, B.W. A hybrid modular multilevel converter with novel three-level cells for DC fault blocking capability. IEEE Trans. Power Del. 2015, 30, 1853–1862. [Google Scholar] [CrossRef]

- Hu, X.; Zhang, J.; Xu, S.; Jiang, Y. Investigation of a new modular multilevel converter with DC fault blocking capability. IEEE Trans. Ind. Appl. 2018, 55, 552–562. [Google Scholar] [CrossRef]

- Chattopadhyay, S.K.; Chakraborty, C. Multilevel inverters with level doubling network: A new topological variation. In Proceedings of the Industrial Electronics Society Conference, Vienna, Austria, 10–14 November 2013. [Google Scholar]

- Chattopadhyay, S.K.; Chakraborty, C. A new multilevel inverter topology with self-balancing level doubling network. IEEE Trans. Ind. Electron. 2014, 61, 4622–4631. [Google Scholar] [CrossRef]

- Ji, Y.; Chen, G. A novel three-phase seven-level active clamped converter using H-bridge as a level doubling network. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference, IPEMC-ECCE Asia, Hefei, China, 22–26 May 2016. [Google Scholar]

- Rajesh, V.; Chattopadhyay, S.K.; Chakraborty, C. Full bridge level doubling network assisted multilevel DC link inverter. In Proceedings of the IEEE 7th Power India International Conference, PIICON 2016, Bikaner, India, 25–27 November 2017. [Google Scholar]

- Agelidis, V.G.; Demetriades, G.D.; Flourentzou, N. Recent advances in high-voltage direct-current power transmission systems. In Proceedings of the 2006 IEEE International Conference on Industrial Technology, Mumbai, India, 15–17 December 2006. [Google Scholar]

- Akagi, H. Classification, terminology, and application of the modular multilevel cascade converter (MMCC). IEEE Trans. Power Electron. 2011, 26, 3119–3130. [Google Scholar] [CrossRef]

- Hu, X.; Zhang, J.; Xu, S.; Jiang, Y. Extended state observer-based fault detection and location method for modular multilevel converters. In Proceedings of the IECON 42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016. [Google Scholar]

- Pérez, M.; Rodríguez, J.; Pontt, J.; Kouro, S. Power distribution in hybrid multi-cell converter with nearest level modulation. In Proceedings of the IEEE International Symposium on Industrial Electronics, 4–7 June 2007. [Google Scholar]

- Ebrahimi, J.; Babaei, E.; Gharehpetian, G.B. A new topology of cascaded multilevel converters with reduced number of components for high-voltage applications. IEEE Trans. Power Electron. 2011, 26, 3109–3118. [Google Scholar] [CrossRef]

- Barbosa, P.; Steimer, P.; Steinke, J.; Winkelnkemper, M.; Celanovic, N. Active-neutral-point-clamped (ANPC) multilevel converter technology. In Proceedings of the European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005. [Google Scholar]

- Bruckner, T.; Bernet, S.; Guldner, H. The active NPC converter and its loss-balancing control. IEEE Trans. Ind. Electron. 2005, 54, 855–868. [Google Scholar] [CrossRef]

- Pulikanti, S.R.; Agelidis, V.G. Hybrid flying-capacitor-based active-neutral-point-clamped five-level converter operated with SHE-PWM. IEEE Trans. Ind. Electron. 2011, 58, 4643–4653. [Google Scholar] [CrossRef]

- Wang, H.; Kou, L.; Liu, Y.-F.; Sen, P.C. A new six-switch five-level active neutral point clamped inverter for PV applications. IEEE Trans. Power Electron. 2017, 32, 6700–6715. [Google Scholar] [CrossRef]

- Naderi, R.; Smedley, K. A new hybrid active neutral point clamped flying capacitor multilevel inverter. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015. [Google Scholar]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Teichmann, R.; Bernet, S. A comparison of three-level converters versus two-level converters for low-voltage drives, traction, and utility applications. IEEE Trans. Ind. Appl. 2005, 41, 855–865. [Google Scholar] [CrossRef]

- Yuan, X. Derivation of voltage source multilevel converter topologies. IEEE Trans. Ind. Electron. 2017, 64, 966–976. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A survey on neutral-point-clamped inverters. IEEE Trans. Ind Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Wu, B.; Point, J.O.; Kouro, S. Multilevel voltage-source-converter topologies for industrial medium-voltage drives. IEEE Trans. Ind. Electron. 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H. Multi-level choppers for high voltage applications. EPE J. 1992, 2, 45–50. [Google Scholar] [CrossRef]

- Leon, J.I.; Vazquez, S.; Franquelo, L.G. Multilevel converters: Control and modulation techniques for their operation and industrial applications. Proc. IEEE 2017, 105, 2066–2081. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Holtz, J.; Rodriguez, J.; Baoming, G. Medium-voltage multilevel converters-State of the art, challenges, and requirements in industrial applications. IEEE Trans. Ind. Electron. 2010, 57, 2581–2596. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H.; Forest, F.; Turpin, C. Multicell converters: Derived topologies. IEEE Trans. Ind. Electron. 2002, 49, 978–987. [Google Scholar] [CrossRef]

- Hammond, P.W. A new approach to enhance power quality for medium voltage ac drives. IEEE Trans. Ind. Appl. 1997, 33, 202–208. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Peng, F.Z.; Wang, J. A universal STATCOM with delta-connected cascade multilevel inverter. In Proceedings of the PESC Record-IEEE Annual Power Electronics Specialists Conference, Aachen, Germany, 20–25 June 2004. [Google Scholar]

- Hammami, M.; Grandi, G. Input current and voltage ripple analysis in level doubling network (LDN) cells for H-bridge multilevel inverters. IEEE Trans. Ind. Electron. 2019, 66, 8414–8423. [Google Scholar] [CrossRef]

- Dewangan, N.K.; Gurjar, V.S.; Ullah, U.; Zafar, S. A level-doubling network (LDN) for cross-connected sources based multilevel inverter (CCS-MLI). In Proceedings of the IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Mumbai, India, 16–19 December 2014. [Google Scholar]

- Srndovic, M.; Viatkin, A.; Grandi, G. Grid-connected three-phase H-bridge inverter with level doubling network controlled by staircase modulation techniques. In Proceedings of the 10th International Conference on Integrated Power Electronics Systems, Stuttgart, Germany, 20–22 March 2018. [Google Scholar]

- Allebrod, S.; Hamerski, R.; Marquardt, R. New transformerless, scalable modular multilevel converters for HVDC-transmission. In Proceedings of the PESC Record-IEEE Annual Power Electronics Specialists Conference PESC, Rhodes Greece, 15–19 June 2008. [Google Scholar]

- Mohammadi, H.P.; Bina, M.T. A transformerless medium-voltage STATCOM topology based on extended modular multilevel converters. IEEE Trans. Power Electron. 2011, 26, 1534–1545. [Google Scholar]

- Leon, J.I.; Kouro, S.; Franquelo, L.G.; Rodriguez, J.; Wu, B. The essential role and the continuous evolution of modulation techniques for voltage-source inverters in the past, present, and future power electronics. IEEE Trans. Ind. Electron. 2016, 63, 2688–2701. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H.; Thomas, P.; Courault, J.; Jakob, R.; Nahrstaedt, M. Multicell converters: Basic concepts and industry applications. IEEE Trans. Ind. Electron. 2002, 49, 955–964. [Google Scholar] [CrossRef]

- Xiaomin, K.; Corzine, K.A.; Familiant, Y.L. Full binary combination schema for floating voltage source multi-level inverters. IEEE Trans. Power Electron. 2002, 17, 891–897. [Google Scholar] [CrossRef]

- Meynard, T.A.; Fadel, M.; Aouda, N. Modeling of multilevel converters. IEEE Trans. Ind. Electron. 1997, 44, 356–364. [Google Scholar] [CrossRef]

- Xiaoming, Y.; Stemmler, H.; Barbi, I. Self-balancing of the clamping capacitor-voltages in the multilevel capacitor-clamping-inverter under sub-harmonic PWM modulation. IEEE Trans. Power Electron. 2001, 16, 256–263. [Google Scholar] [CrossRef]

- Richardeau, F.; Baudesson, P.; Meynard, T. Failures-tolerance and remedial strategies of a PWM multicell inverter. In Proceedings of the IEEE Power Electronics Specialists Conference, Galway, Ireland, 18–23 June 2000. [Google Scholar]

- Peebles, P.Z. Digital Communication Systems; Prentice Hall: Upper Saddle River, NJ, USA, 1987. [Google Scholar]

- Zierhofer, C.M. Adaptive sigma-delta modulation with one-bit quantization. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process 2000, 47, 408–415. [Google Scholar] [CrossRef][Green Version]

- Brukner, T.; Bernet, S. Investigation of a high-power three-level quasi-resonant dc-link voltage source inverter. IEEE Trans. Ind. Appl. 2001, 37, 619–627. [Google Scholar] [CrossRef]

- Diaz, C.S.; Escobar, F.I.; Diotaiuti, G.C.; Arguis, V.M.G. Adaptive sigma-delta modulator applied to control five level multilevel inverter. In Proceedings of the IEEE International Caracas Conference on Devices, Circuits and Systems, ICCDCS, Punta Cana, Dominican Republic, 3–5 November 2004. [Google Scholar]

- Zhang, L.; Watkins, S.J.; Shepherd, W. Analysis and control of a multi-level flying capacitor inverter. In Proceedings of the IEEE International Power Electronics Congress-CIEP, Guadalajara, Mexico, 24–24 October 2002. [Google Scholar]

- Ismail, B.; Taib, S.; Saad, A.R.M.; Isa, M.; Hadzer, C.M. Development of a single phase SPWM microcontroller-based inverter. In Proceedings of the 1st International Power and Energy Conference, Putra Jaya, Malaysia, 28–29 November 2006. [Google Scholar]

- Bojoi, R.; Griva, G.; Guerriero, M.; Farina, F.; Profumo, F.; Bostan, V. Improved current control strategy for power conditioners using sinusoidal signal integrators in synchronous reference frame. In Proceedings of the PESC Record-IEEE Annual Power Electronics Specialists Conference, Aachen, Germany, 20–25 June 2004. [Google Scholar]

- Kang, B.J.; Liaw, C.M. Random hysteresis PWM inverter with robust spectrum shaping. IEEE Trans. Aerosp. Electron. Syst. 2001, 37, 619–628. [Google Scholar] [CrossRef]

- Escobar, G.; Martínez, P.R.; Leyva-Ramos, J. Analog circuits to implement repetitive controllers with feedforward for harmonic compensation. IEEE Trans. Ind. Electron. 2007, 54, 567–573. [Google Scholar] [CrossRef]

- Loh, P.C.; Bode, G.H.; Holmes, D.G.; Lipo, T.A. A time-based double-band hysteresis current regulation strategy for single-phase multilevel inverters. IEEE Trans. Ind. Appl. 2003, 39, 883–892. [Google Scholar]

- Loh, P.C.; Bode, G.H.; Tan, P.C. Modular hysteresis current control of hybrid multilevel inverters. IEE Proc. Electr. Power Appl. 2005, 152, 1–8. [Google Scholar] [CrossRef]

- Blanco, E.; Bueno, E.; Espinosa, F.; Cobreces, S.; Rodríguez, F.J.; Ruiz, M.A. Fast harmonics compensation in VSCs connected to the grid by synchronous frame generalized integrators. In Proceedings of the IEEE International Symposium on Industrial Electronics, Dubrovnik, Croatia, 20–23 June 2005. [Google Scholar]

- Castilla, M.; Miret, J.; Matas, J.; García de Vicuña, L.; Guerrero, J.M. Linear current control scheme with series resonant harmonic compensator for single-phase grid-connected photovoltaic inverters. IEEE Trans. Ind. Electron. 2008, 55, 2727–2733. [Google Scholar] [CrossRef]

- Zare, F.; Nami, A. A new random current control technique for a single-phase inverter with bipolar and unipolar modulations. In Proceedings of the 4th Power Conversion Conference-NAGOYA, PCC-NAGOYA, Nagoya, Japan, 2–5 April 2007. [Google Scholar]

- Ahmad, Z.; Singh, S.N. Comparative analysis of single-phase transformer less inverter topologies for grid connected PV system. Sol. Energy 2017, 149, 245–271. [Google Scholar] [CrossRef]

| Voltage | ||||

|---|---|---|---|---|

| Voltage | ||||||||

|---|---|---|---|---|---|---|---|---|

| Voltage | ||||

|---|---|---|---|---|

| Voltage | ||||||||

|---|---|---|---|---|---|---|---|---|

| Voltage | g1 | g2 | g3 | g4 |

|---|---|---|---|---|

| Voltage | g1 | g2 | g3 | g4 | g5 | g6 | g7 | g8 |

|---|---|---|---|---|---|---|---|---|

| IT | DC-MLI | FC-MLI | CHB-MLI | A-NPC | MMC |

|---|---|---|---|---|---|

| MS | |||||

| MD | |||||

| CD | (m 1) (m 2) | - | - | - | - |

| DBC | - | - | |||

| BC | - | - | - | - | |

| RD | Not Redundant | Redundant | Redundant | Redundant | Redundant |

| F | Not Flexible | Not Flexible | Flexible | Flexible | Not Flexible |

| MDV | |||||

| CVR | |||||

| ACC | |||||

| C | M | M | M | H | H |

| R | T | A | D | MT | AP |

|---|---|---|---|---|---|

| [2,59,60,61,62,63,64] | DC-MLI | Low cost and fewer components due to a smaller number of capacitors therefore simple structure; equalized blocking voltage of power. | Unequal distribution of power losses; DC-link voltage balance limits the converter to three-level topology. | Pulse width modulation (PWM) carrier modulation (based zero-sequence injection); Space vector pulse width modulation (SVPWM) method (based space vector selection). | Renewable energy; variable speed motor drive; static var compensation; HVDC/AC transmission lines. |

| [64,65,66,67,68] | FC-MLI | Modular structure; possessing a large number of redundant states; each branch can be analyzed independently. | The poor dynamic response of dc voltage balancing; large amounts of flying capacitors reduce the system reliability; pre-charging capacitors is difficult. | Phase-shifted carrier PWM (achieves neutral balancing of flying capacitors). | Renewable energy; motor drive; induction motor control using direct torque control circuit; sinusoidal current rectifiers; static var generation. |

| [69,70,71] | CHB-MLI | Modular structure is easier to analyses; possessing fault tolerant capability; same switching frequencies for all the switches. | Separate DC sources are required; isolated transformers increase the system volume. | Phase-shifted carrier PWM (achieves equalization of power losses). | Renewable energy; DC power source utilization; Power factor compensators; flexible alternating current transmission system (FACTS); electric vehicle drives. |

| [32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51,72,73,74,75,76] | MMC | Modular structure; easy to achieve fault tolerant operation. | Low-frequency voltage oscillation of floating capacitors; complex data acquisition and communication for each power cell. | Nearest-level modulation (achieves equalization of power losses and dc voltage balance). | High-voltage DC (HVDC) transmission, A static synchronous compensator (STATCOM) |

| [54,55,56,57,58] | A-NPC | Simple structure; easily extendable to a higher level by stacking flying. | Unequal usage of switches and flying capacitors; requires series switches to handle high voltage. | Hybrid phase-shifted PWM (low frequency for high voltage switches and high frequency for flying capacitor cells). | Renewable energy |

| Fourier Analysis for V (25) | |||||

|---|---|---|---|---|---|

| DC Components No. Harmonics THD Grid Size Interpolation Degree | 0.142395 15 28.8803% 512 1 | ||||

| Harmonics | Frequency | Magnitude | Phase | Norm. Mag | Norm. Phase |

| 1 | 50 | 10.7723 | 147.086 | 1 | 0 |

| 2 | 100 | 0.0359127 | −87.093 | 0.00333381 | −234.18 |

| 3 | 150 | 0.482066 | −91.605 | 0.0447506 | −238.69 |

| 4 | 200 | 0.0370429 | −90.48 | 0.00343872 | −237.57 |

| 5 | 250 | 2.40309 | −164.03 | 0.223081 | −311.11 |

| 6 | 300 | 0.0368095 | −93.112 | 0.00341705 | −240.2 |

| 7 | 350 | 1.2825 | 129.104 | 0.119056 | −17.982 |

| 8 | 400 | 0.0367623 | −94.406 | 0.00341267 | −241.49 |

| 9 | 450 | 0.470903 | −113.53 | 0.0437143 | −260.61 |

| 10 | 500 | 0.0369758 | −96.153 | 0.0034325 | −243.24 |

| 11 | 550 | 1.14951 | 178.466 | 0.106709 | 31.3803 |

| 12 | 600 | 0.0368479 | −97.806 | 0.00342062 | −244.89 |

| 13 | 650 | 0.517375 | 111.212 | 0.0480284 | −35.874 |

| 14 | 700 | 0.0369105 | −99.11 | 0.00342644 | −246.21 |

| 15 | 750 | 0.454395 | −131.73 | 0.042818 | −278.82 |

| Fourier Analysis for V (47) | |||||

|---|---|---|---|---|---|

| DC components No. Harmonics THD Grid Size Interpolation Degree | −0.037107 15 18.5624% 512 1 | ||||

| Harmonics | Frequency | Magnitude | Phase | Norm. Mag | Norm. Phase |

| 1 | 50 | 11.8044 | −0.86678 | 1 | 0 |

| 2 | 100 | 0.00272927 | −87.038 | 0.0002231207 | −86.172 |

| 3 | 150 | 1.82486 | −3.0824 | 0.154591 | −2.2156 |

| 4 | 200 | 0.000617738 | −38.435 | 0.000052331 | −37.568 |

| 5 | 250 | 0.489755 | 174.772 | 0.0414891 | 175.638 |

| 6 | 300 | 0.00209954 | 69.2359 | 0.00017786 | 70.1027 |

| 7 | 350 | 0.930224 | 172.689 | 0.0788029 | 173.556 |

| 8 | 400 | 0.00315766 | 75.7679 | 0.000267498 | 76.6347 |

| 9 | 450 | 0.561122 | 170.638 | 0.0475349 | 171.505 |

| 10 | 500 | 0.00256501 | 79.3973 | 0.000217292 | 80.264 |

| 11 | 550 | 0.114071 | 168.906 | 0.00966337 | 169.773 |

| 12 | 600 | 0.000955366 | 95.2264 | 8.09328 × 10−05 | 96.0932 |

| 13 | 650 | 0.00525038 | −19.574 | 0.000444781 | −18.707 |

| 14 | 700 | 0.000845858 | −137.32 | 7.16559 × 10−05 | −136.45 |

| 15 | 750 | 0.195151 | 164.189 | 0.016532 | 165.055 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rana, R.A.; Patel, S.A.; Muthusamy, A.; Lee, C.w.; Kim, H.-J. Review of Multilevel Voltage Source Inverter Topologies and Analysis of Harmonics Distortions in FC-MLI. Electronics 2019, 8, 1329. https://doi.org/10.3390/electronics8111329

Rana RA, Patel SA, Muthusamy A, Lee Cw, Kim H-J. Review of Multilevel Voltage Source Inverter Topologies and Analysis of Harmonics Distortions in FC-MLI. Electronics. 2019; 8(11):1329. https://doi.org/10.3390/electronics8111329

Chicago/Turabian StyleRana, Ronak A., Sujal A. Patel, Anand Muthusamy, Chee woo Lee, and Hee-Je Kim. 2019. "Review of Multilevel Voltage Source Inverter Topologies and Analysis of Harmonics Distortions in FC-MLI" Electronics 8, no. 11: 1329. https://doi.org/10.3390/electronics8111329

APA StyleRana, R. A., Patel, S. A., Muthusamy, A., Lee, C. w., & Kim, H.-J. (2019). Review of Multilevel Voltage Source Inverter Topologies and Analysis of Harmonics Distortions in FC-MLI. Electronics, 8(11), 1329. https://doi.org/10.3390/electronics8111329