Design and Emulation of All-Digital Phase-Locked Loop on FPGA

Abstract

1. Introduction

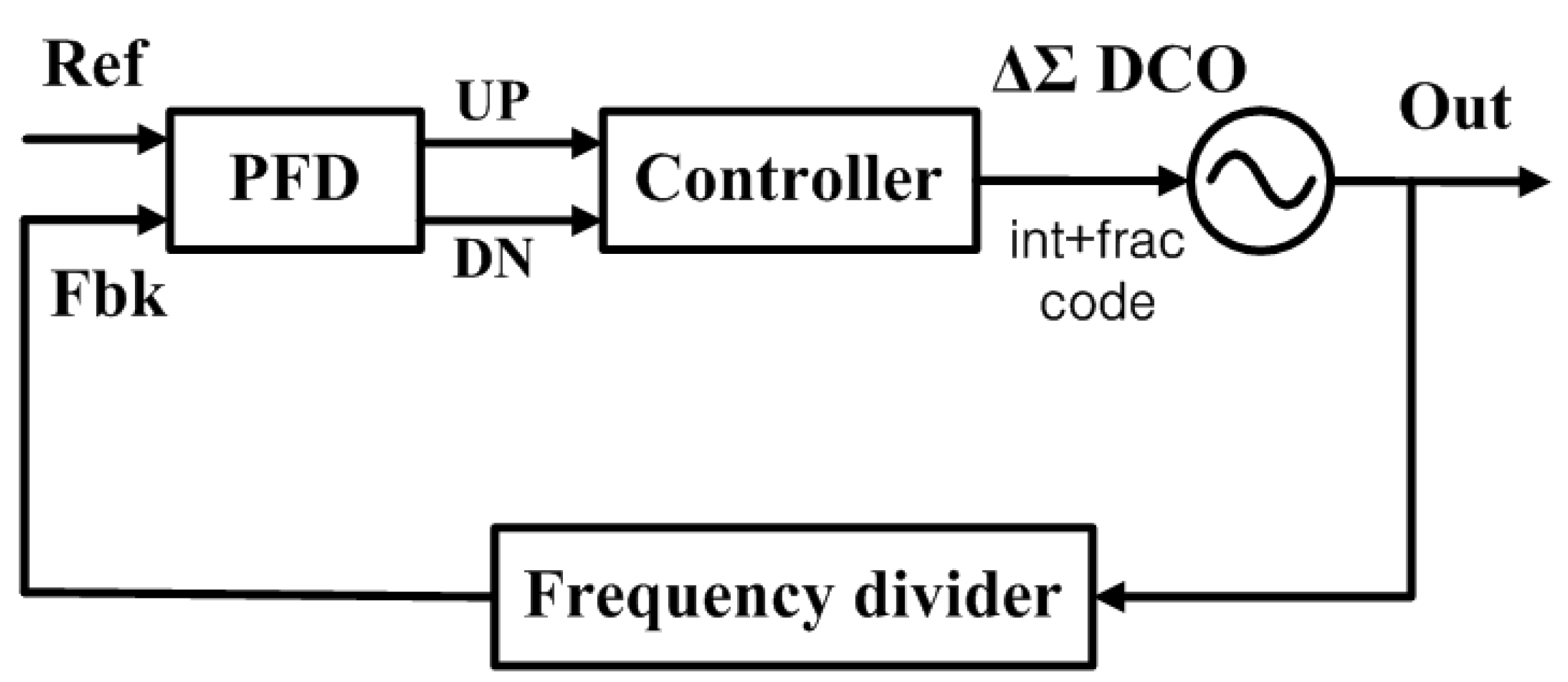

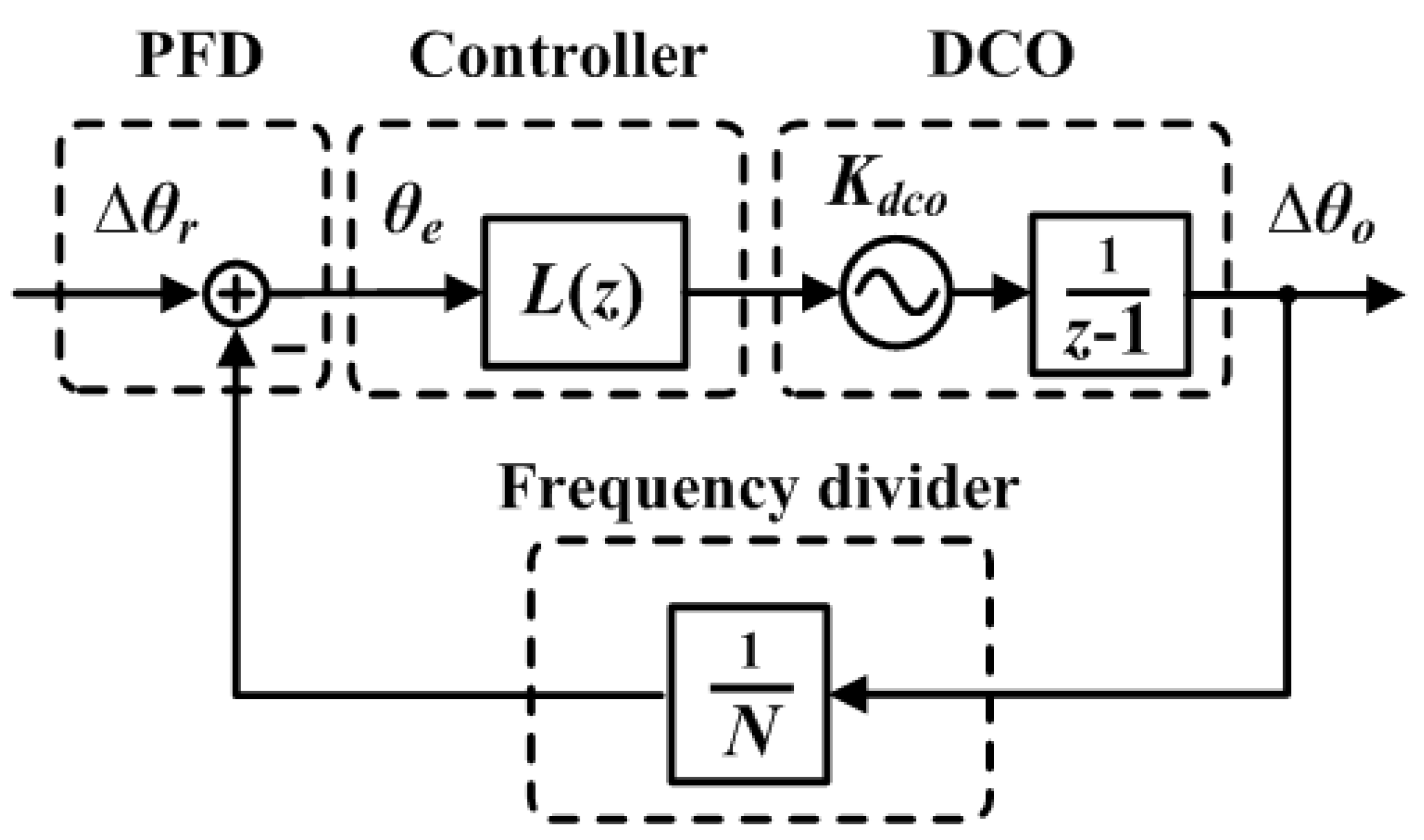

2. Controller-Based ADPLL and Its Functional Building Blocks

2.1. System Configuration

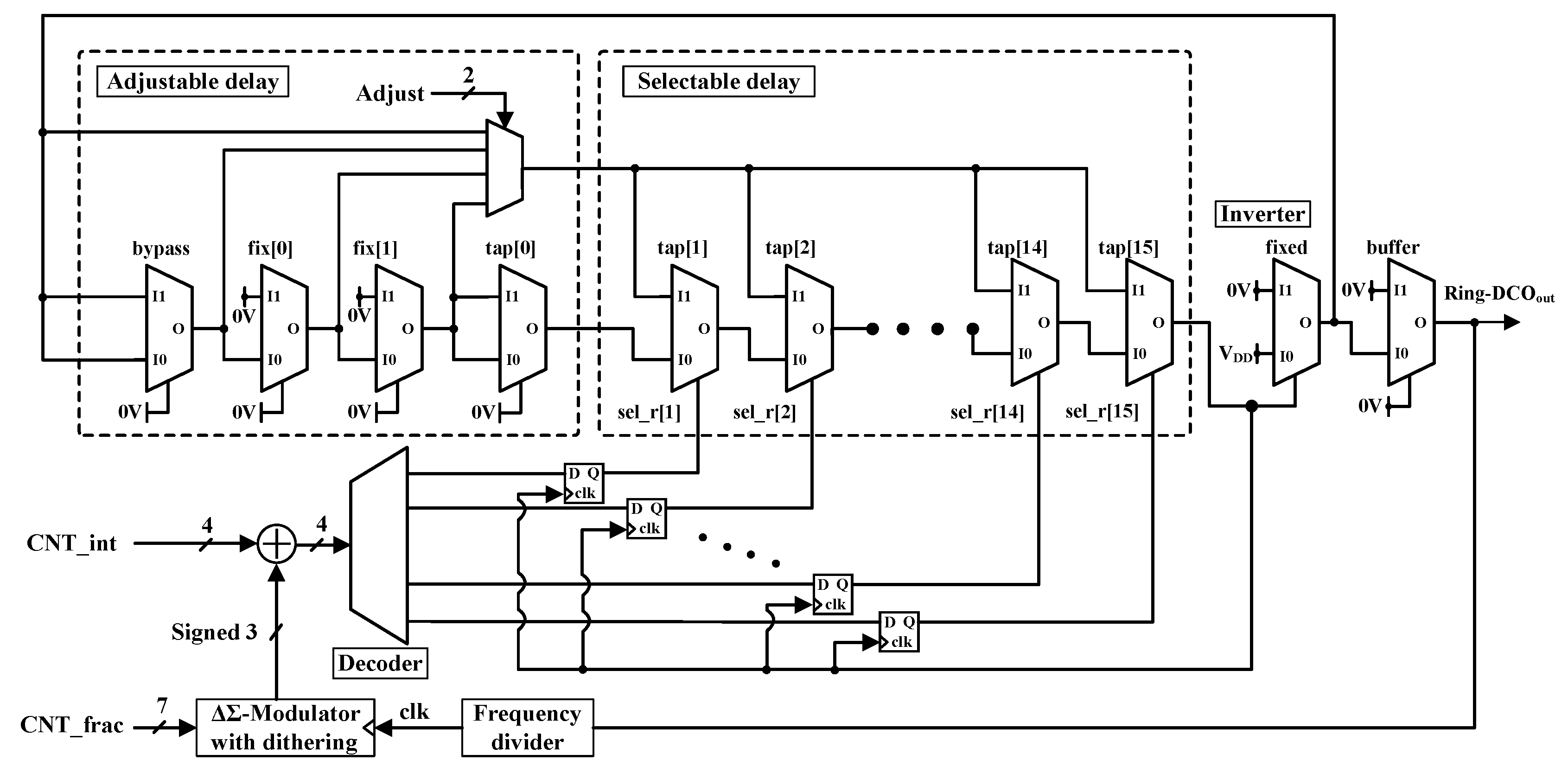

2.2. Ring-DCO

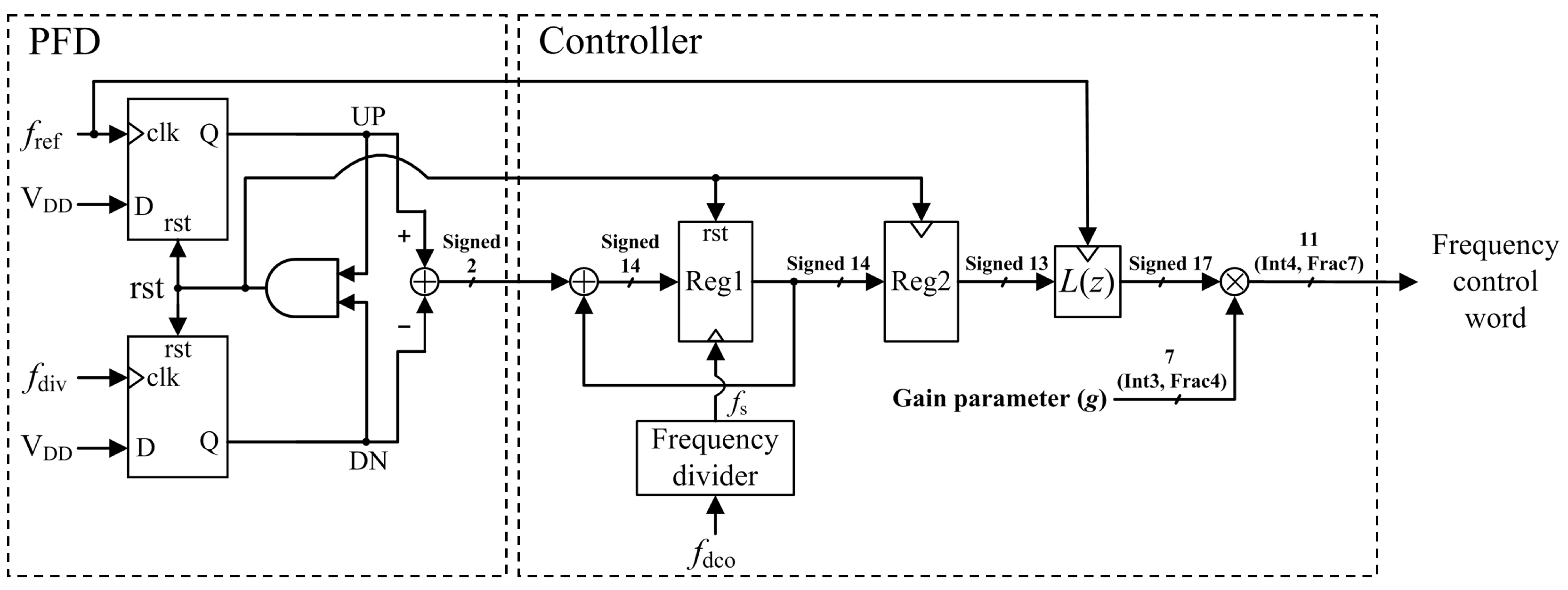

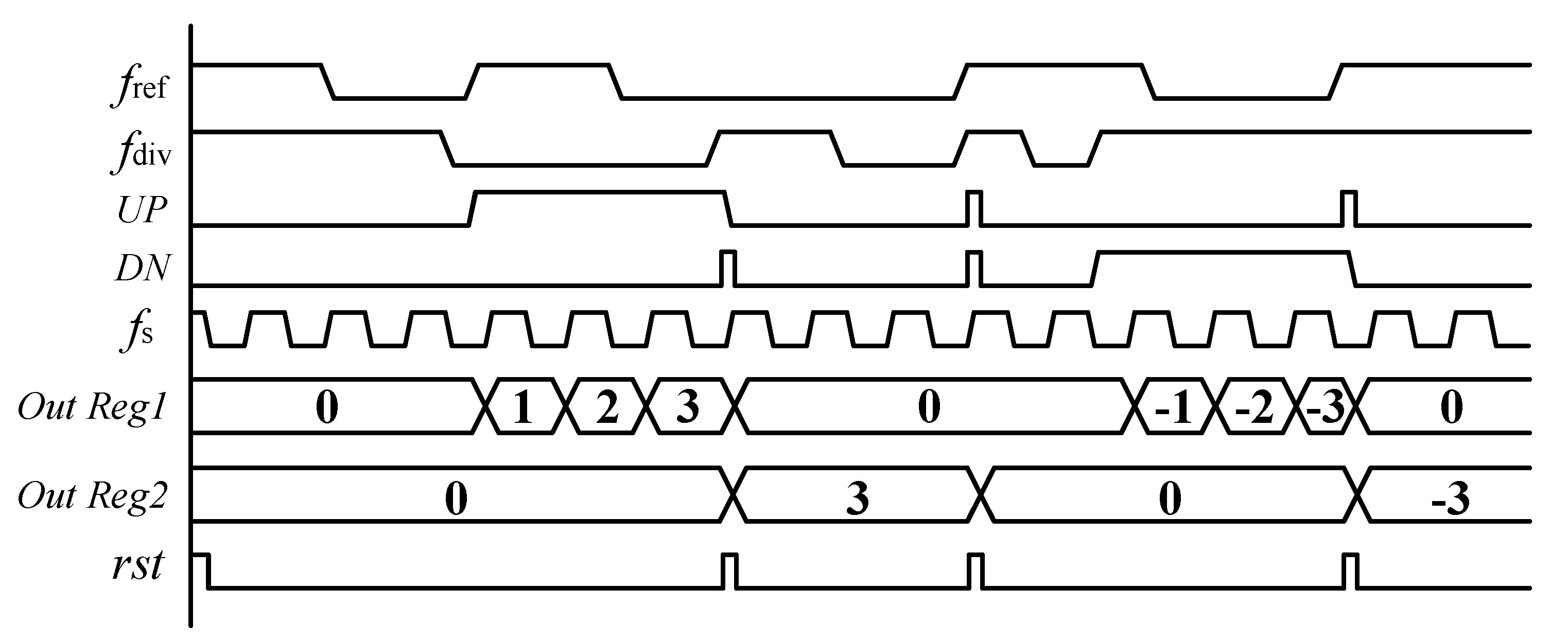

2.3. PFD and Loop Filter

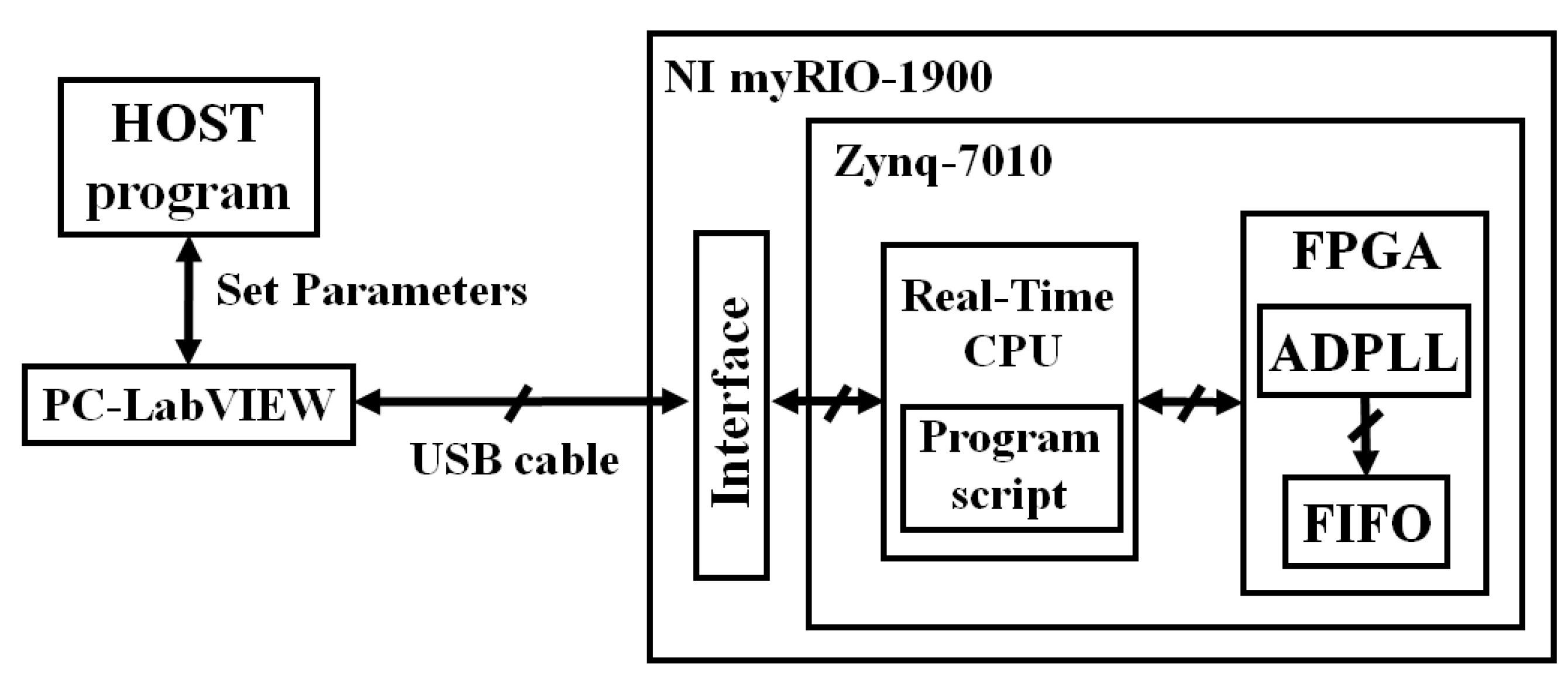

3. Experimental Setup

4. Experimental Results

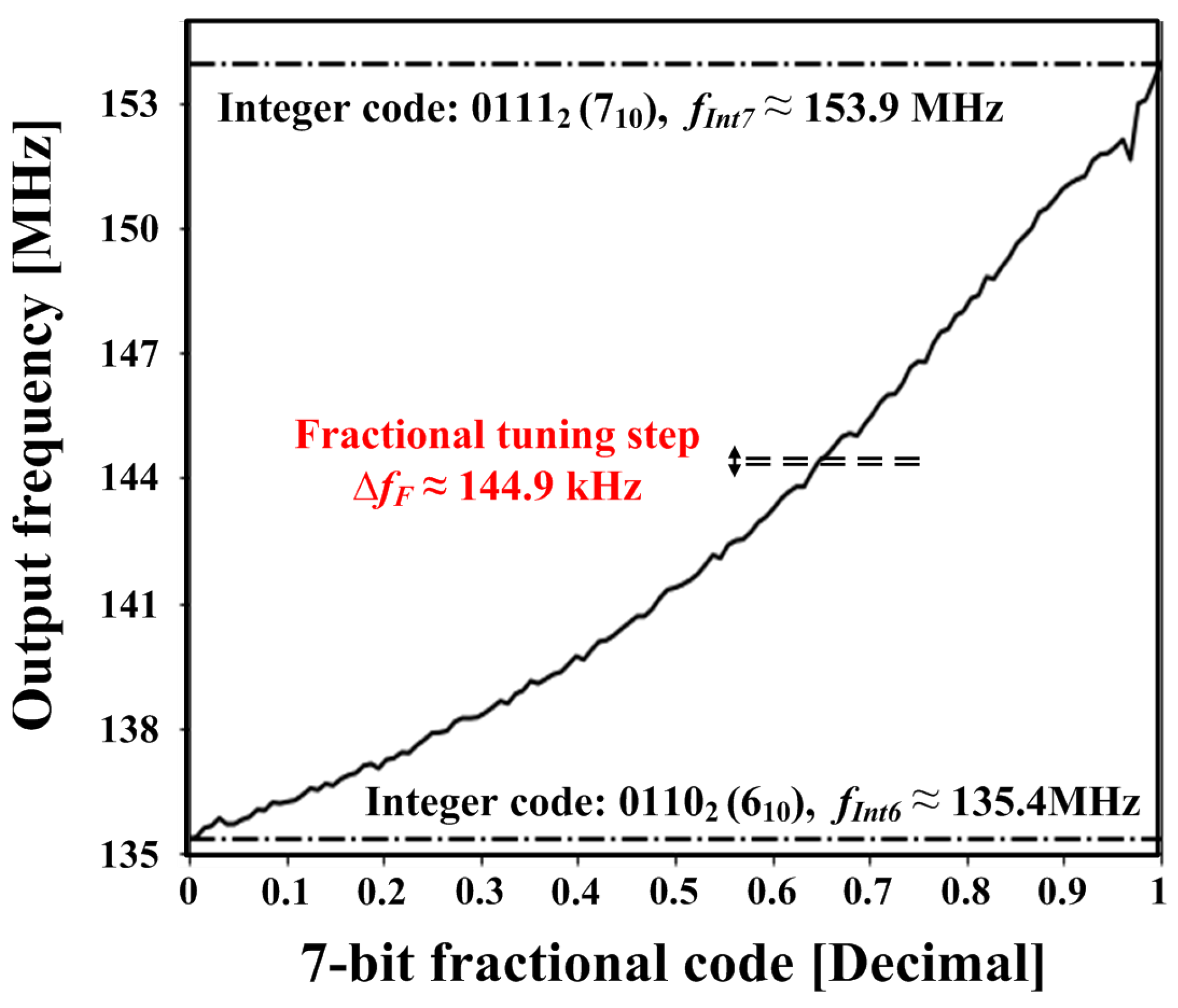

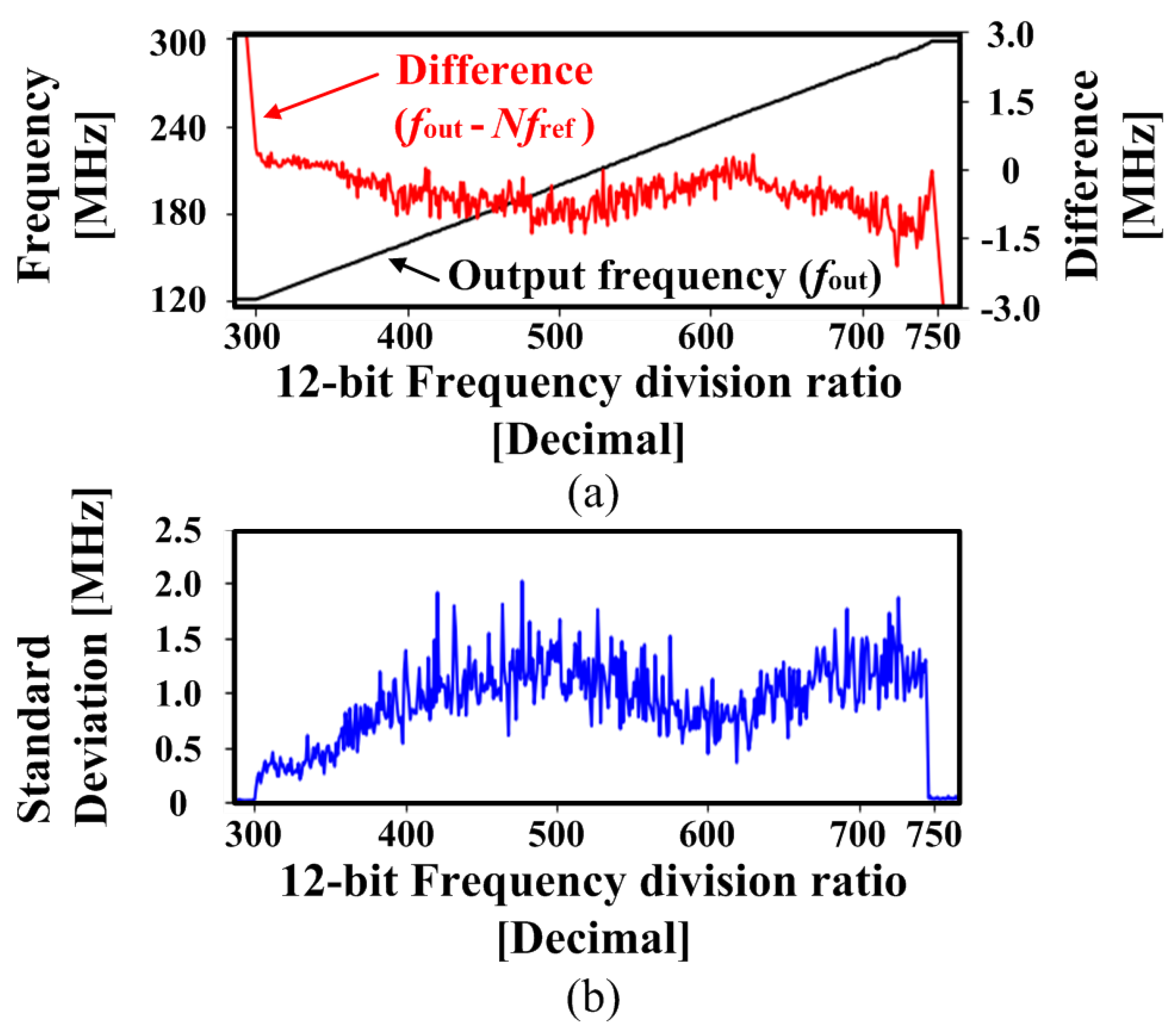

4.1. DCO Frequency Range

4.2. ADPLL Steady-State Operation

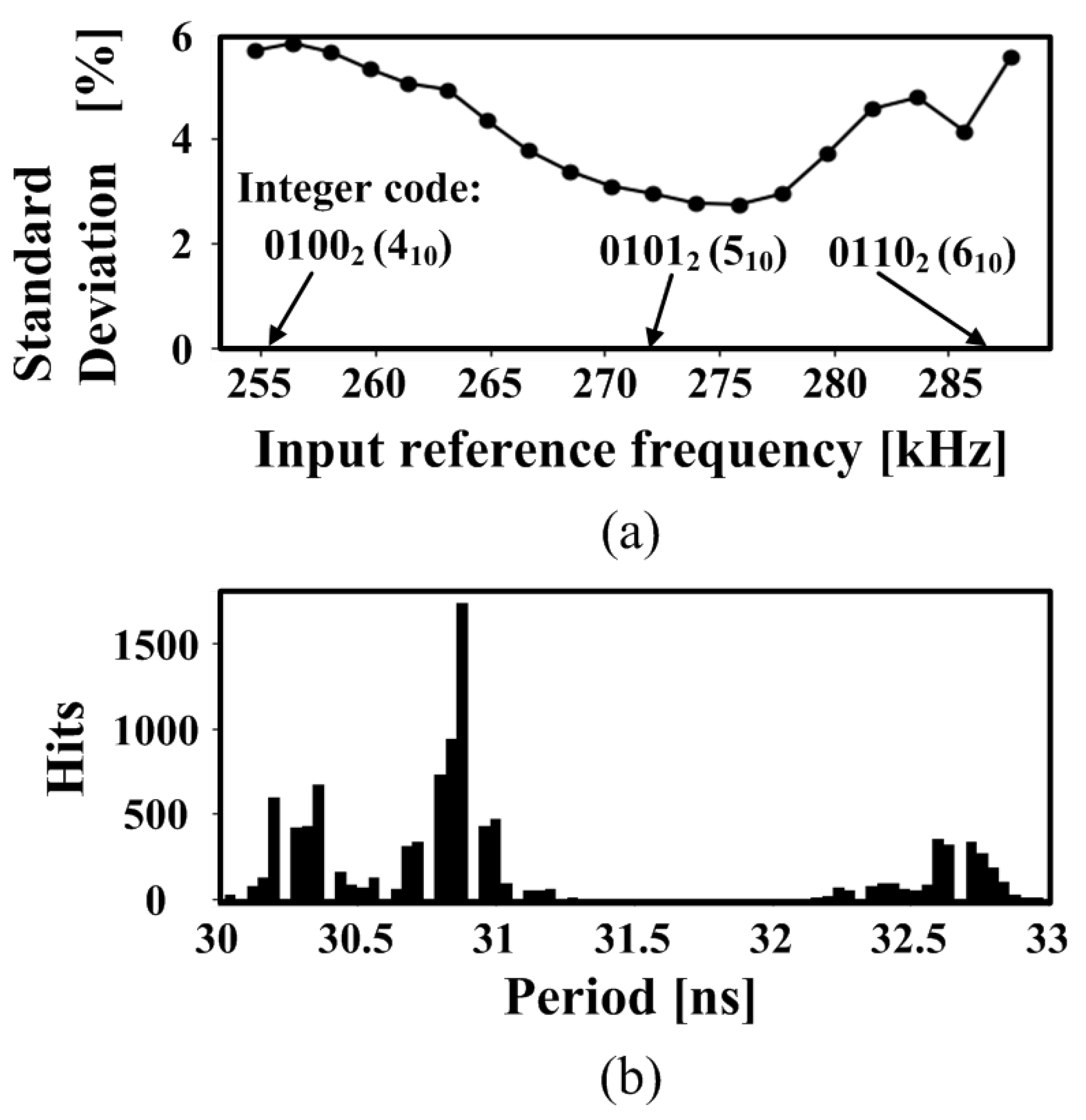

4.3. Jitter Measurement

4.4. Input Frequency Step Response

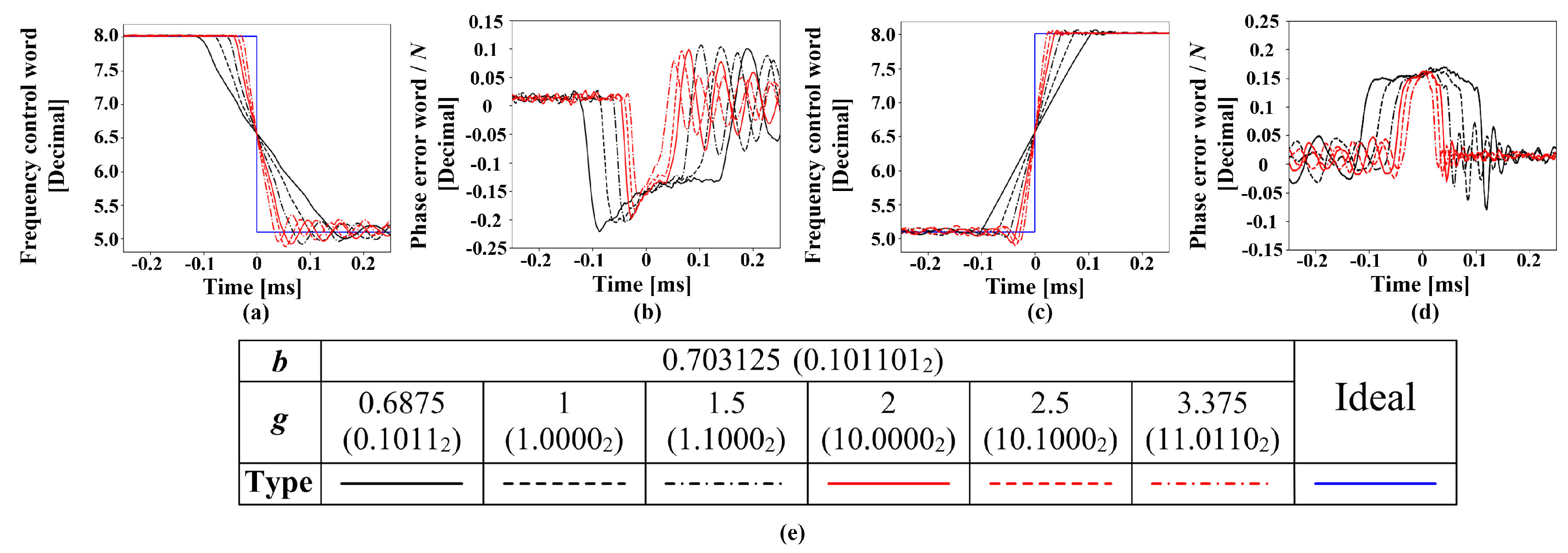

4.4.1. Influence of g Parameter with Fixed b Value

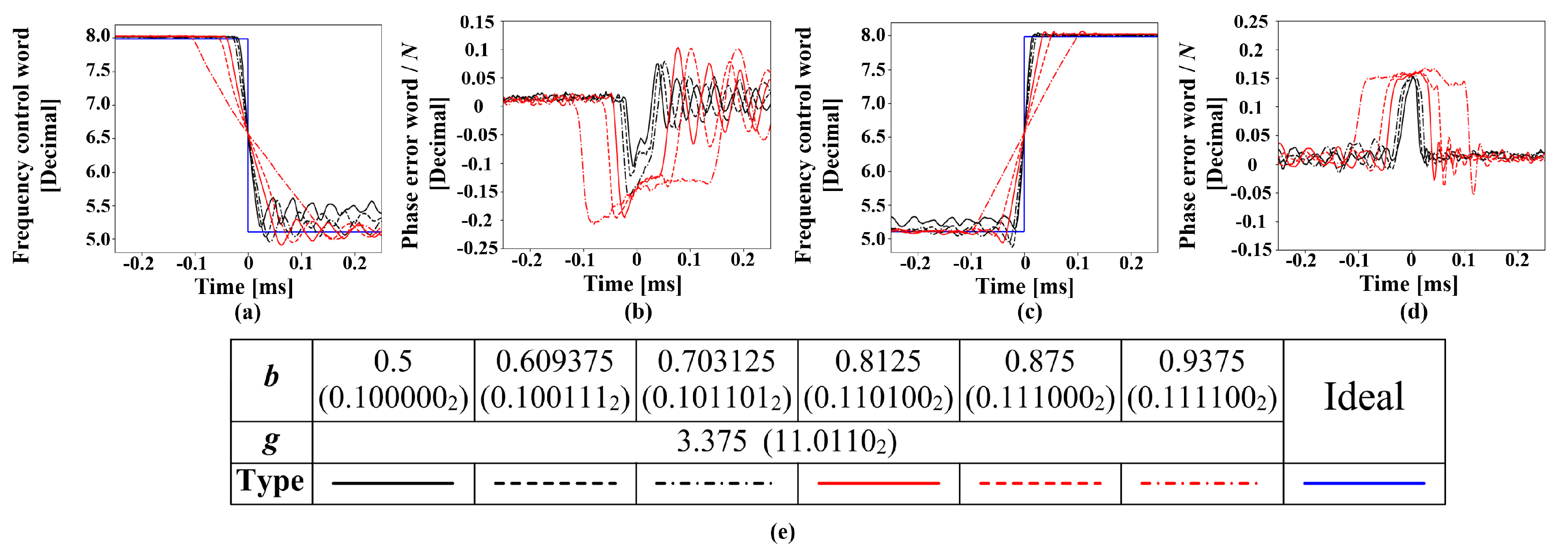

4.4.2. Influence of b Parameter with Fixed g Value

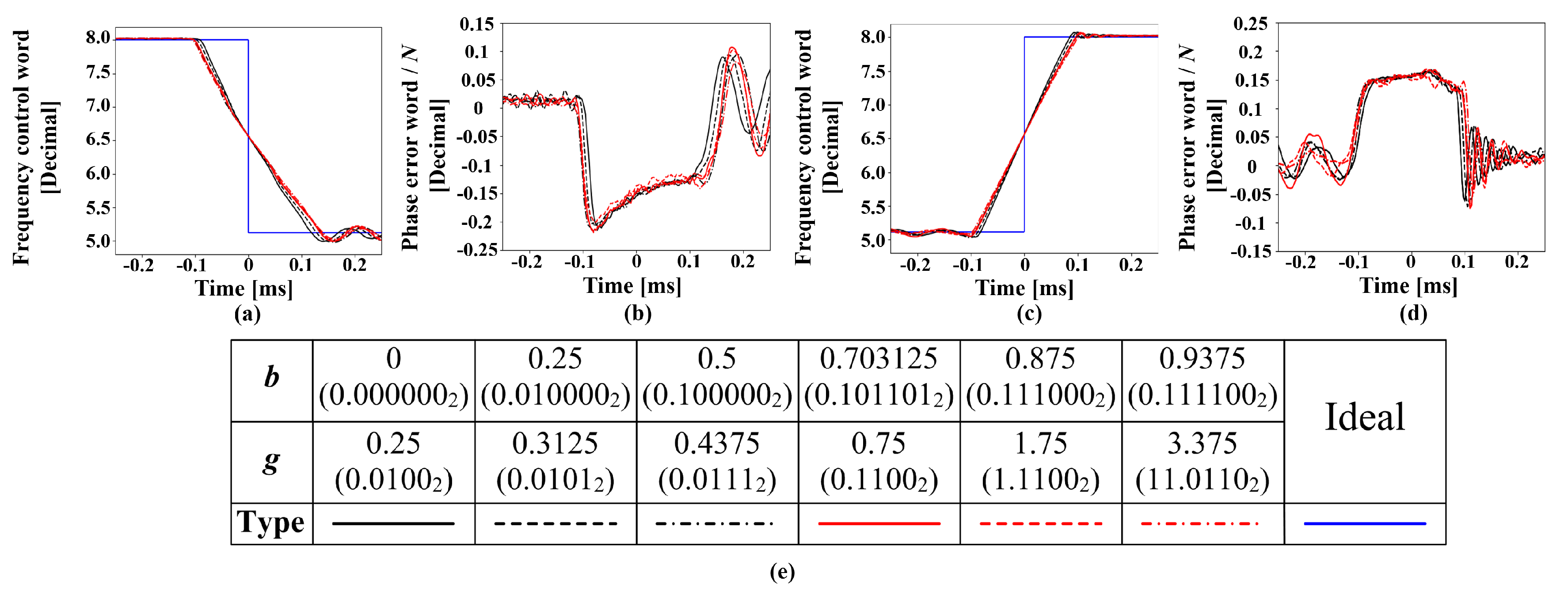

4.4.3. Case of Constant Low-Frequency Open-Loop Gain

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Chen, H.-C.; Wang, T.; Chiu, H.-W.; Kao, T.-H.; Lu, S.-S. 0.5-V 5.6-GHz CMOS Receiver Subsystem. IEEE Trans. Microw. Theory Tech. 2009, 57, 329–335. [Google Scholar] [CrossRef]

- Matsuoka, T.; Wang, J.; Kihara, T.; Ham, H.; Taniguchi, K. Low-Voltage Wireless Analog CMOS Circuits toward 0.5 V Operation. IEICE Trans. Fundam. 2010, E93-A, 356–366. [Google Scholar] [CrossRef]

- Yamashita, F.; Matsuoka, T.; Kihara, T.; Takobe, I.; Park, H.-J.; Taniguchi, K. Analytical design of a 0.5V 5GHz CMOS LC-VCO. IEICE Electron. Express 2009, 6, 1025–1031. [Google Scholar] [CrossRef]

- Hegazi, E.; Sjöland, H.; Abidi, A.A. A Filtering Technique to Low LC Oscillator Phase Noise. IEEE J. Solid-State Circuits 2001, 36, 1921–1930. [Google Scholar] [CrossRef]

- Kamata, T.; Matsuoka, T.; Taniguchi, T. Design of Wideband Tuning VCO for TV Receiver System. IEICE Trans. Electron. Jpn. Ed. 2007, J90-C, 634–641. [Google Scholar]

- Staszewski, R.B.; Muhammad, K.; Leipold, D.; Hung, C.-M.; Ho, Y.-C.; Wallberg, J.L.; Fernando, C.; Maggio, K.; Staszewski, R.; Jung, T.; et al. All-Digital TX Frequency Synthesizer and Discrete-Time Receiver for Bluetooth Radio in 130-nm CMOS. IEEE J. Solid-State Circuits 2004, 39, 2278–2291. [Google Scholar] [CrossRef]

- Miyashita, D.; Kobayashi, H.; Deguchi, J.; Kousai, S.; Hamada, M.; Fujimoto, R. A −104 dBc/Hz In-Band Phase Noise 3 GHz All Digital PLL with Phase Interpolation Based Hierarchical Time to Digital Converter. IEICE Trans. Electron. 2012, E95-C, 1008–1016. [Google Scholar] [CrossRef]

- Bae, J.; Radhapuram, S.; Jo, I.; Kihara, T.; Matsuoka, T. A Design of 0.7-V 400-MHz Digitally Controlled Oscillator. IEICE Trans. Electron. 2015, E98-C, 1179–1186. [Google Scholar] [CrossRef]

- Bae, J.; Radhapuram, S.; Jo, I.; Wang, W.; Kihara, T.; Matsuoka, T. A Design of 0.7-V 400-MHz All-Digital Phase-Locked Loop for Implantable Biomedical Devices. IEICE Trans. Electron. 2016, E99-C, 431–439. [Google Scholar] [CrossRef]

- Gardner, F. Charge-Pump Phase-Lock Loops. IEEE Trans. Commun. 1980, 28, 1849–1858. [Google Scholar] [CrossRef]

- van Paemel, M. Analysis of a charge-pump PLL: A new model. IEEE Trans. Commun. 1994, 42, 2490–2498. [Google Scholar] [CrossRef]

- Kratyuk, V.; Hanumolu, P.K.; Moon, U.-K.; Mayaram, K. A Design Procedure for All-Digital Phase-Locked Loops Based on a Charge-Pump Phase-Locked-Loop Analogy. IEEE Trans. Circuits Syst. II 2007, 54, 247–251. [Google Scholar] [CrossRef][Green Version]

- Riley, T.A.; Copeland, M.A.; Kwasniewski, T.A. Delta-sigma modulation in fractional-N frequency synthesis. IEEE J. Solid-State Circuits 1993, 28, 553–559. [Google Scholar] [CrossRef]

- Rhee, W.; Song, B.S.; Ali, A. A 1.1-GHz CMOS Fractional-N Frequency Synthesizer with a 3-b Third-Order ΔΣ Modulator. IEEE J. Solid-State Circuits 2000, 35, 1453–1460. [Google Scholar] [CrossRef]

- Perrott, M.H.; Trott, M.D.; Sodini, C.G. A Modeling Approach for Σ-Δ Fractional-N Frequency Synthesizers Allowing Straightforward Noise Analysis. IEEE J. Solid-State Circuits 2002, 37, 1028–1038. [Google Scholar] [CrossRef]

- Staszewski, R.B.; Fernando, C.; Balsara, P.T. Event-Driven Simulation and Modeling of Phase Noise of an RF Oscillator. IEEE Trans. Circuits Syst. I 2005, 32, 723–733. [Google Scholar] [CrossRef]

- Fishburn, M.; Menninga, L.H.; Favi, C.; Charbon, E. A 19.6 ps, FPGA-Based TDC With Multiple Channels for Open Source Applications. IEEE Trans. Nucl. Sci. 2013, 60, 2203–2208. [Google Scholar] [CrossRef]

- Radhapuram, S.; Bae, J.; Jo, I.; Wang, W.; Matsuoka, T. Analysis of A Controller-Based All-Digital Phase-Locked Loop. Far East J. Electron. Commun. 2015, 15, 57–73, Erratum in 2016, 16, 199–201. [Google Scholar] [CrossRef]

- Kumm, M.; Klingbeil, H.; Zipf, P. An FPGA-Based Linear All-Digital Phase-Locked Loop. IEEE Trans. Circuits Syst. I 2010, 57, 2487–2497. [Google Scholar] [CrossRef]

- Shan, C.; Zianbetov, E.; Yu, W.; Anceau, F.; Billoint, O.; Galayko, D. FPGA prototyping of large reconfigurable ADPLL network for distributed clock generation. In Proceedings of the 2013 International Conference on Reconfigurable Computing and FPGAs, Cancun, Mexico, 9–11 December 2013. [Google Scholar]

- Shan, C.; Zianbetov, E.; Anceau, F.; Billoint, O.; Galayko, D. A distributed synchronization of all-digital PLLs network for clock generation in synchronous SOCs. In Proceedings of the IEEE 13th International New Circuits and Systems Conference, Grenoble, France, 7–10 June 2015. [Google Scholar]

- Makihara, Y.; Ikebe, M.; Sano, E. Evaluation of Digitally Controlled PLL by Clocked-Period Comparison. IEICE Trans. Electron. 2007, E90-C, 1307–1310. [Google Scholar] [CrossRef]

- Xilinx. LogiCORE IP Accumulator v11.0 Product Specification; DS213 March 1; Xilinx: San Jose, CA, USA, 2011. [Google Scholar]

- National Instruments. NI myRIO-1900 User Guide and Specifications; National Instruments: Austin, TX, USA, 2016. [Google Scholar]

- Xilinx. LogiCORE IP Binary Counter v11.0 Product Specification; DS215 March 1; Xilinx: San Jose, CA, USA, 2011. [Google Scholar]

- Miyamura, M.; Sakamoto, T.; Bai, X.; Tsuji, Y.; Morioka, A.; Nebashi, R.; Tada, M.; Banno, N.; Okamoto, K.; Iguchi, N.; et al. NanoBridge-Based FPGA in High-Temperature Environments. IEEE Micro 2017, 37, 32–42. [Google Scholar] [CrossRef]

- Ochi, H.; Yamaguchi, K.; Fujimoto, T.; Hotate, J.; Kishimoto, T.; Higashi, T.; Imagawa, T.; Doi, R.; Tada, M.; Sugibayashi, T.; et al. Via-Switch FPGA: Highly Dense Mixed-Grained Reconfigurable Architecture with Overlay Via-Switch Crossbars. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 2723–2736. [Google Scholar] [CrossRef]

| Element | Number (Utilization Rate) |

|---|---|

| Total Slices | 4310 (98.0%) |

| Slice LUTs | 13772 (78.2%) |

| Slice Registers | 13970 (39.7%) |

| Block RAMs | 10 (16.7%) |

| DSP48s | 4 (5.0%) |

| Power Consumption | 28 mW |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Radhapuram, S.; Yoshihara, T.; Matsuoka, T. Design and Emulation of All-Digital Phase-Locked Loop on FPGA. Electronics 2019, 8, 1307. https://doi.org/10.3390/electronics8111307

Radhapuram S, Yoshihara T, Matsuoka T. Design and Emulation of All-Digital Phase-Locked Loop on FPGA. Electronics. 2019; 8(11):1307. https://doi.org/10.3390/electronics8111307

Chicago/Turabian StyleRadhapuram, Saichandrateja, Takuya Yoshihara, and Toshimasa Matsuoka. 2019. "Design and Emulation of All-Digital Phase-Locked Loop on FPGA" Electronics 8, no. 11: 1307. https://doi.org/10.3390/electronics8111307

APA StyleRadhapuram, S., Yoshihara, T., & Matsuoka, T. (2019). Design and Emulation of All-Digital Phase-Locked Loop on FPGA. Electronics, 8(11), 1307. https://doi.org/10.3390/electronics8111307