Data-Adaptive Coherent Demodulator for High Dynamics Pulse-Wave Ultrasound Applications

Abstract

1. Introduction

2. Background and Motivation

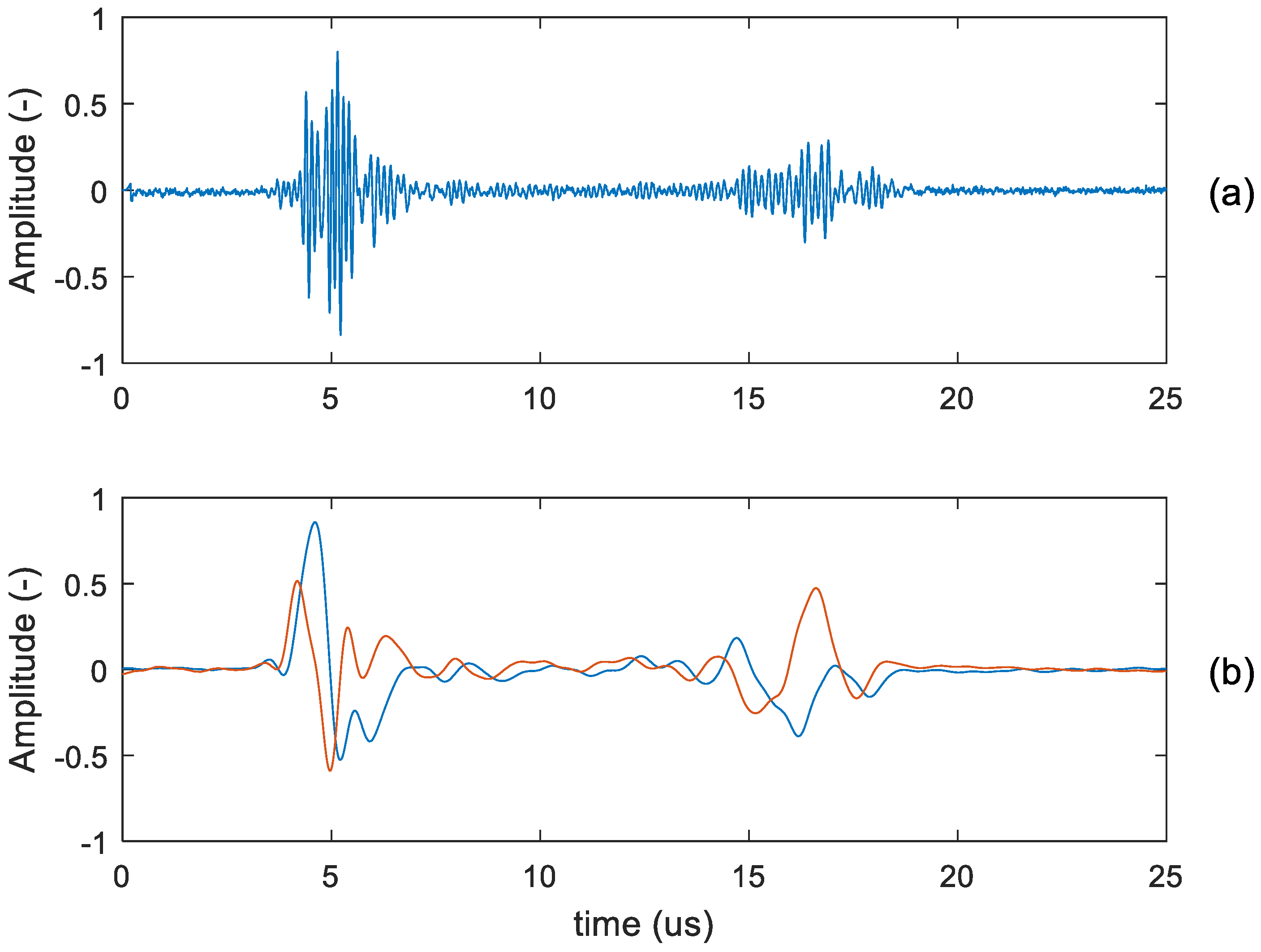

2.1. Pulse Wave Signals in Industrial Echo-Doppler Applications and Their Processing

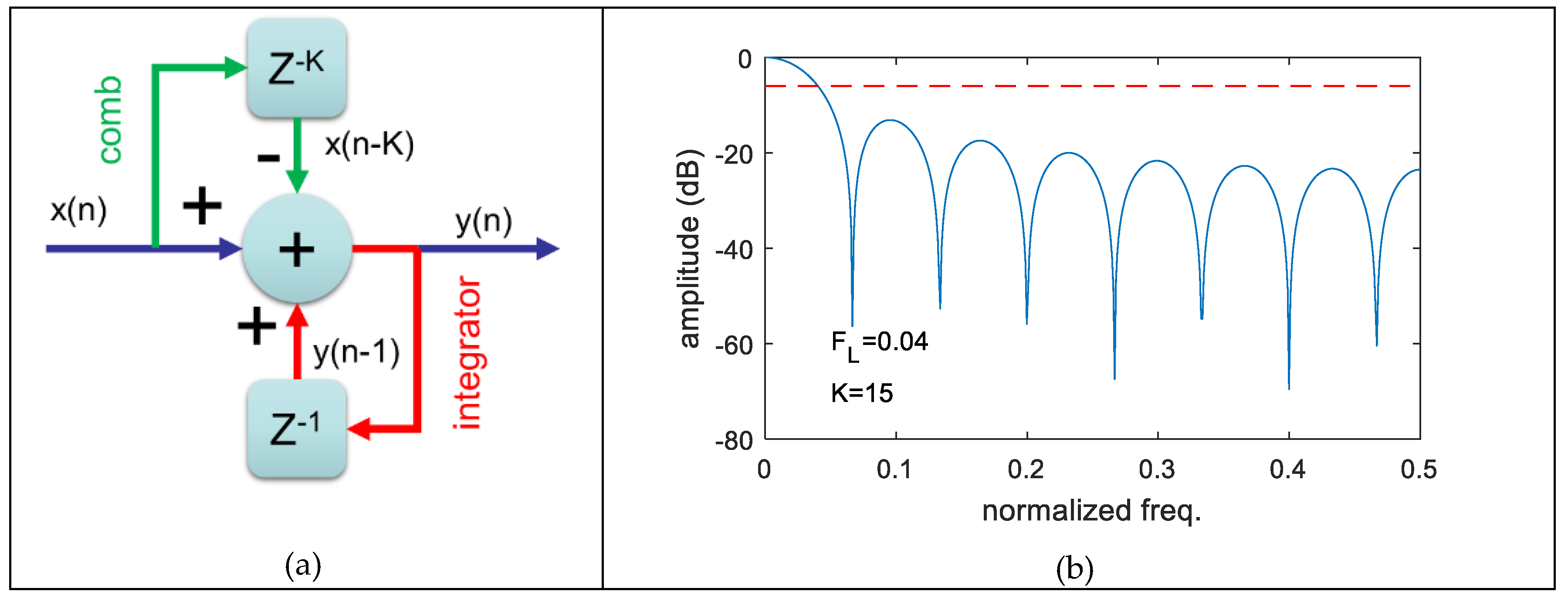

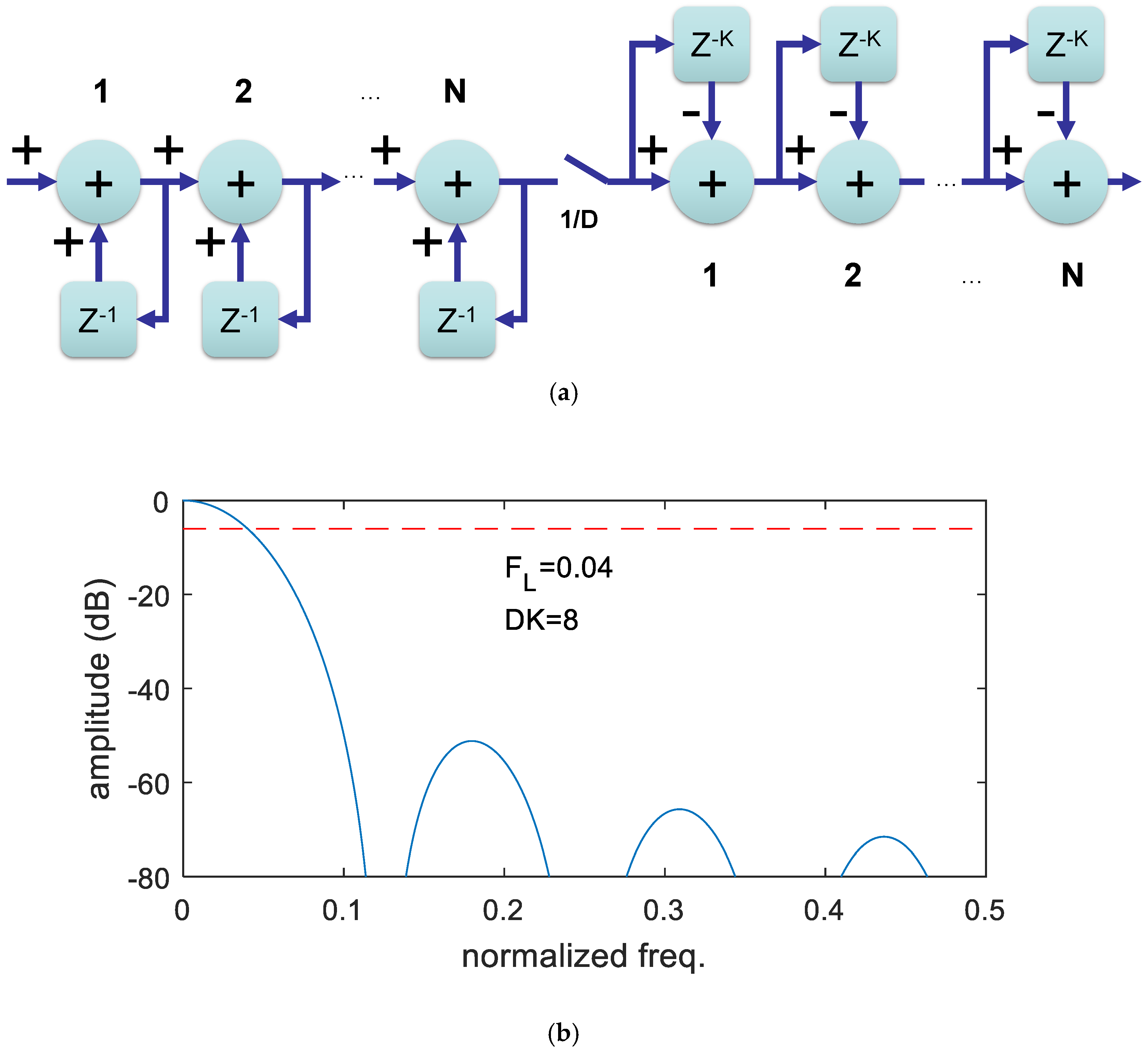

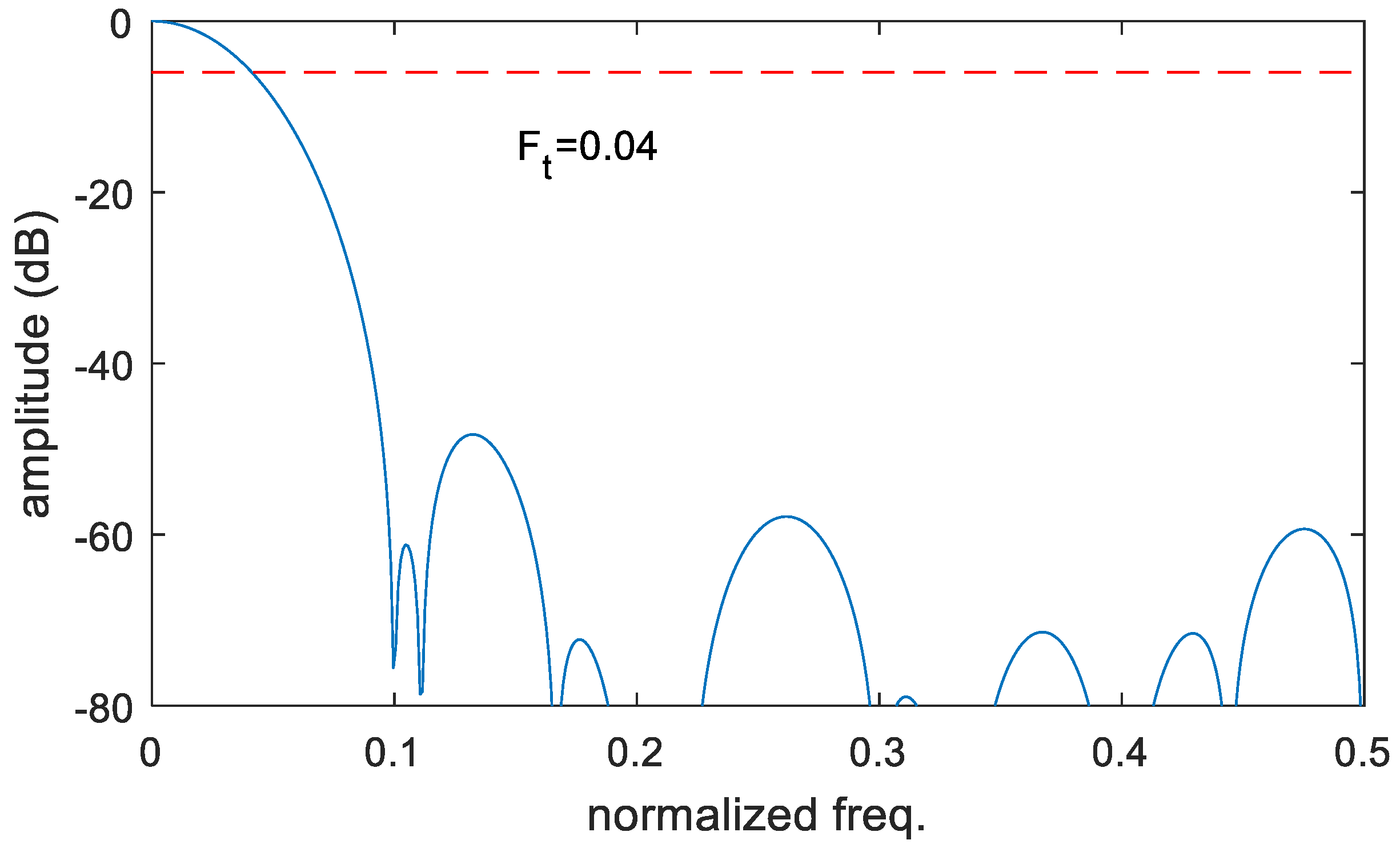

2.2. Coherent Demodulator and CIC Filter Basics

2.3. Demodulator Desired Features

- Cut-off frequency programmable in a wide range of frequencies;

- Input dynamic range sufficient for accommodating both the strong pipe echoes and weak fluid signal;

- Low mathematical noise;

- Reasonable FPGA resource utilization;

- Up to 100 MHz working frequency.

3. Methods

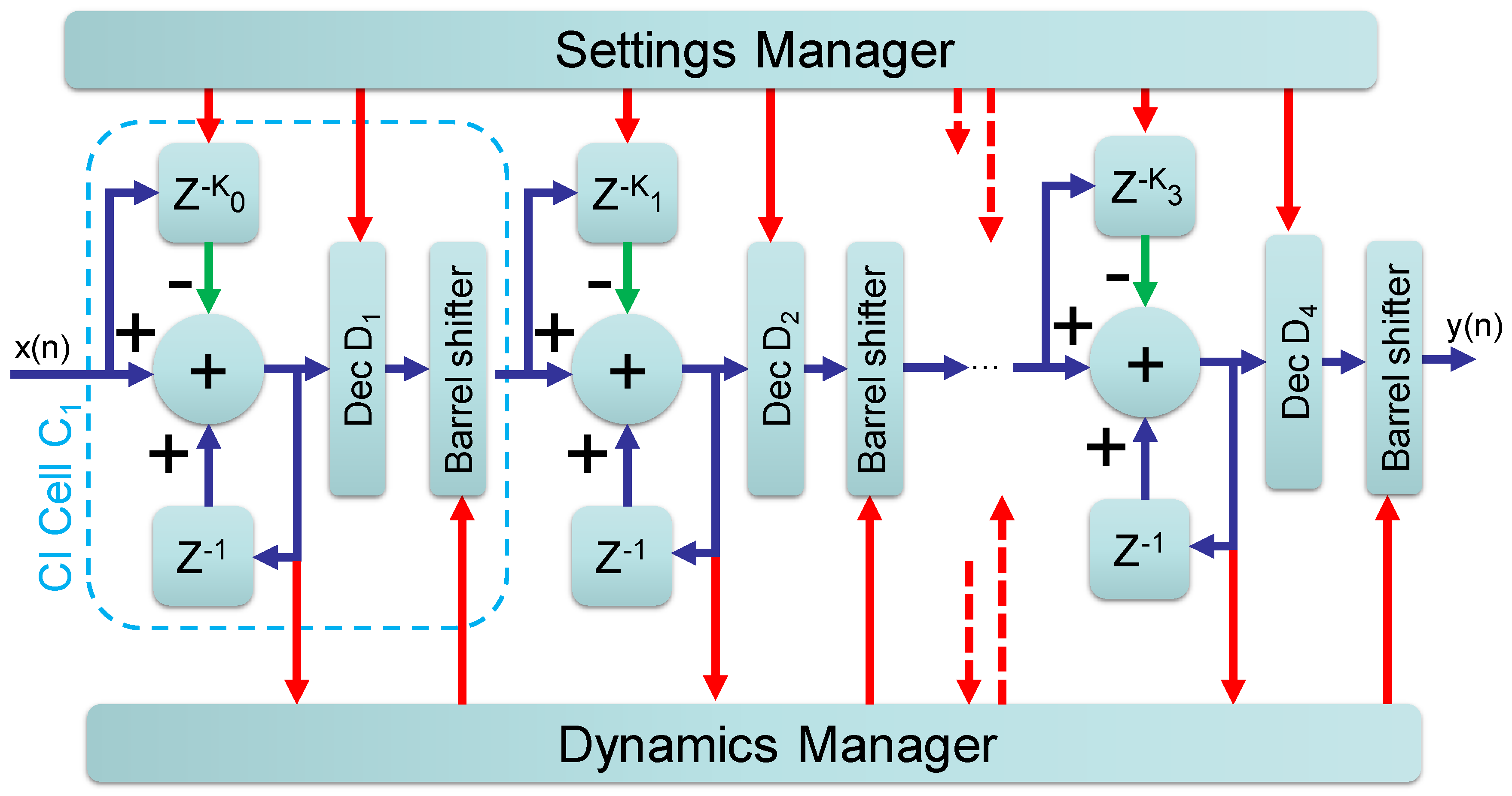

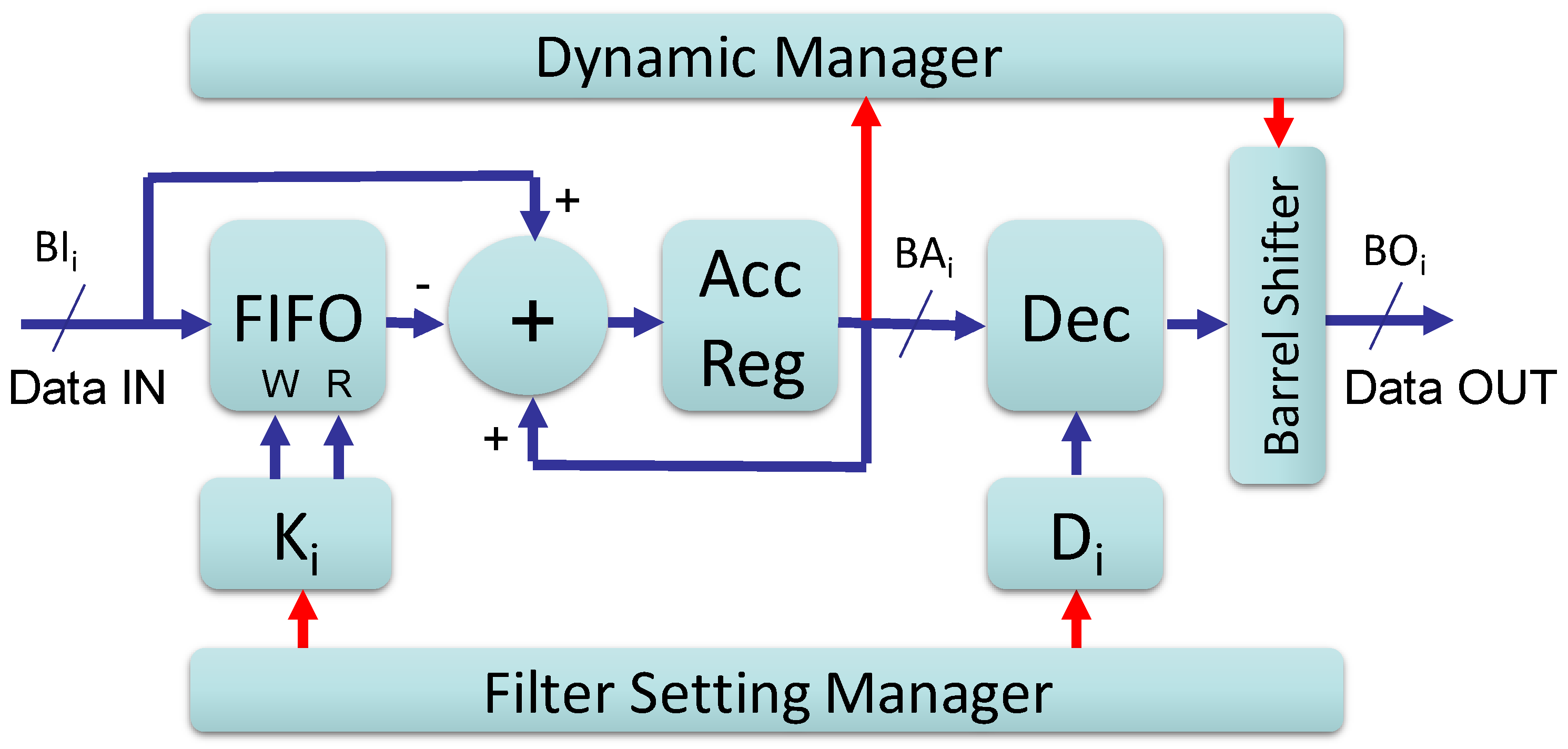

3.1. Modified-CIC FilterAarchitecture

3.2. Dynamics Management

- 1)

- “Setting Manager” block program K0, K1, K2, K3, and D1, D2, D3, D4

- 2)

- Repeat for ICi cells I = 1 to 4:

- Detect the maximum data amplitude on 10 PRIs, M=max(abs(Data))

- Calculate the bits necessary to represent data: J=ceil(log2(M))+1

- Set the shifter so that J is the most significant bit

- Discard the PRIs used for training

- 3)

- Start normal data acquisition and processing

3.3. FPGA Implementation

4. Experiments and Results

4.1. Resources Utilization

4.2. Demodulator Noise Performance

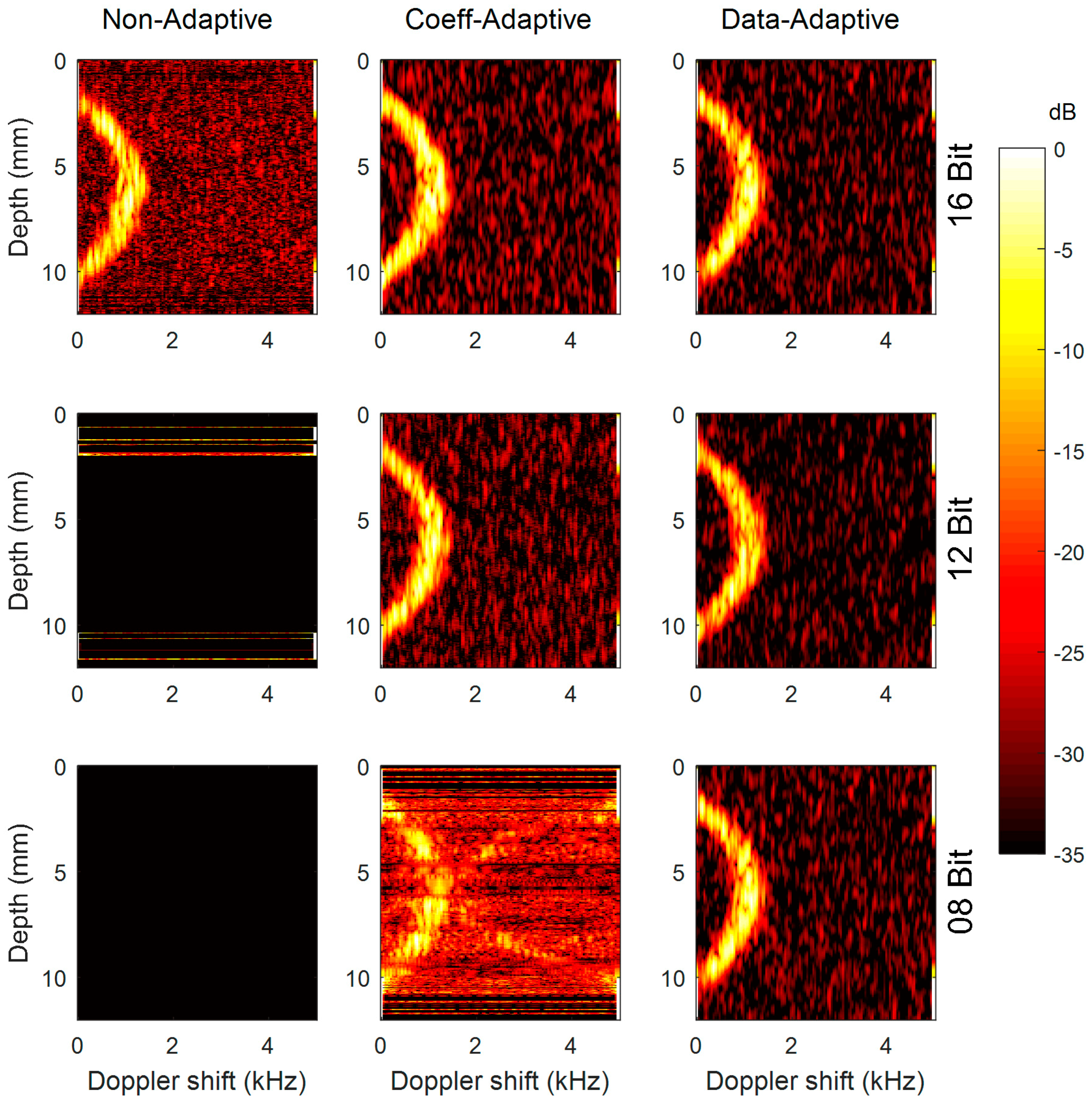

4.3. Flow Simulation

4.4. Example of Application

5. Discussion and Conclusion

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Evans, D.H.; McDicken, W.N. Doppler Ultrasound Physics, Instrumentation and Signal Processing; Wiley: Chichester, UK, 2000; ISBN 978-0471970019. [Google Scholar]

- Vogt, M. Direct sampling and baseband conversion in Doppler systems for high-frequency ultrasound blood flow measurements. Electron. Lett. 2005, 41, 189–790. [Google Scholar] [CrossRef]

- Weibao, Q.; Zongying, Y.; Yanyan, Y.; Yan, C.; Liyang, C.; Peitian, M.; Guofeng, L.; Congzhi, W.; Yang, X.; Jiyan, D.; et al. A Digital Multigate Doppler Method for High Frequency Ultrasound. Sensors 2014, 14, 13348–13360. [Google Scholar] [CrossRef]

- Boni, E.; Bassi, L.; Dallai, A.; Meacci, V.; Ramalli, A.; Scaringella, M.; Guidi, F.; Ricci, S.; Tortoli, P. Architecture of an Ultrasound System for Continuous Real-Time High Frame Rate Imaging. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2017, 64, 1276–1284. [Google Scholar] [CrossRef] [PubMed]

- Jensen, J.A.; Nikolov, S.I.; Yu, A.C.H.; Garcia, D. Ultrasound Vector Flow Imaging-Part II: Parallel Systems. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2016, 63, 722–1732. [Google Scholar] [CrossRef] [PubMed]

- Hervás, M.; Alsina-Pagès, R.M.; Salvador, M. An FPGA Scalable Software Defined Radio Platform Design for Educational and Research Purposes. Electronics 2016, 5, 27. [Google Scholar] [CrossRef]

- Koulamas, C.; Lazarescu, M.T. Real-Time Embedded Systems: Present and Future. Electronics 2018, 7, 205. [Google Scholar] [CrossRef]

- Rodriguez-Andina, J.J.; Moure, M.J.; Valdes, M.D. Features, design tools, and application domains of FPGAs. IEEE Trans. Ind. Electron. 2007, 54, 1810–1823. [Google Scholar] [CrossRef]

- Richard, L. Understanding Digital Signal Processing, 2nd ed.; Prentice Hall: Upper Saddle River, NJ, USA, 2004; ISBN 978-0-13-702741-5. [Google Scholar]

- Mohsin, A.; Fadhel, M.G.; Mohamed, H. Blind Compensation of I/Q Impairments in Wireless Transceivers. Sensors 2017, 17, 2948. [Google Scholar] [CrossRef]

- Ricci, S.; Matera, R.; Tortoli, P. An improved Doppler model for obtaining accurate maximum blood velocities. Ultrasonics 2014, 7, 2006–2014. [Google Scholar] [CrossRef]

- Wiklund, J.; Stading, M. Application of in-line ultrasound Doppler-based UVP–PD rheometry method to concentrated model and industrial suspensions. Flow Meas. Instrum. 2008, 19, 171–179. [Google Scholar] [CrossRef]

- Birkhofer, B.; Debacker, A.; Russo, S.; Ricci, S.; Lootens, D. In-line rheometry based on ultrasonic velocity profiles: Comparison of data processing methods. Appl. Rheol. 2012, 22, 44701. [Google Scholar] [CrossRef]

- Morganti, T.; Ricci, S.; Vittone, F.; Palombo, C.; Tortoli, P. Clinical validation of common carotid artery wall distension assessment based on multigate Doppler processing. Ultras. Med. Biol. 2005, 31, 937–945. [Google Scholar] [CrossRef] [PubMed]

- Shamu, T.J.; Kotzé, R.; Wiklund, J. Characterization of acoustic beam propagation through high-grade stainless steel pipes for improved pulsed ultrasound velocimetry measurements in complex industrial fluids. IEEE Sens. J. 2016, 16, 5636–5647. [Google Scholar] [CrossRef]

- Kotzé, R.; Ricci, S.; Birkhofer, B.; Wiklund, J. Performance tests of a new non-invasive sensor unit and ultrasound electronics. Flow Meas. Instrum. 2016, 48, 104–111. [Google Scholar] [CrossRef]

- Qwist, P.K.; Sander, C.; Okkels, F.; Jessen, V.; Baldursdottir, S.; Rantanen, J. On-line rheological characterization of semi-solid formulations. Eur. J. Pharm. Sci. 2019, 128, 36–42. [Google Scholar] [CrossRef] [PubMed]

- Ricci, S.; Swillens, A.; Ramalli, A.; Segers, P.; Tortoli, P. Wall Shear Rate Measurement: Validation of a new Method through Multi-physics Simulations. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2017, 64, 66–77. [Google Scholar] [CrossRef] [PubMed]

- Meacci, V.; Matera, R.; Ricci, S. High dynamics adaptive demodulator for ultrasound applications: FPGA implementation. In Proceedings of the 1st New Generation of CAS, NGCAS, Genoa, Italy, 6–8 September 2017. [Google Scholar]

- Hogenauer, E. An economical class of digital filters for decimation and interpolation. IEEE Trans. Acoust. Speech Signal Process. 1981, 29, 155–162. [Google Scholar] [CrossRef]

- Peilu, L.; Xinghua, L.; Haopeng, L.; Zhikun, S.; Hongxu, Z. Implementation of High Time Delay Accuracy of Ultrasonic Phased Array Based on Interpolation CIC Filter. Sensors 2017, 17, 2322. [Google Scholar] [CrossRef]

- Pilato, L.; Fanucci, L.; Saponara, S. Real-Time and High-Accuracy Arctangent Computation Using CORDIC and Fast Magnitude Estimation. Electronics 2017, 6, 22. [Google Scholar] [CrossRef]

- Ricci, S.; Meacci, V.; Birkhofer, B.; Wiklund, J. FPGA-based System for In-Line Measurement of Velocity Profiles of Fluids in Industrial Pipe Flow. IEEE Trans. Ind. Electron. 2017, 64, 3997–4005. [Google Scholar] [CrossRef]

- Ricci, S.; Liard, M.; Birkhofer, B.; Lootens, D.; Brühwiler, A.; Tortoli, P. Embedded Doppler System for Industrial in-Line Rheometry. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2012, 59, 1395–1401. [Google Scholar] [CrossRef]

- Cooley, J.W.; Tukey, J.W. An algorithm for the machine calculation of complex Fourier series. Math. Comput. 1965, 19, 297–301. [Google Scholar] [CrossRef]

- Minotta, F.; Jimenez, M.; Rodriguez, D. Automated Scalable Address Generation Patterns for 2-Dimensional Folding Schemes in Radix-2 FFT Implementations. Electronics 2018, 7, 33. [Google Scholar] [CrossRef]

- Nguyen, H.N.; Khan, S.A.; Kim, C.H.; Kim, J.M. A Pipelined FFT Processor Using an Optimal Hybrid Rotation Scheme for Complex Multiplication: Design, FPGA Implementation and Analysis. Electronics 2018, 7, 137. [Google Scholar] [CrossRef]

- Ricci, S. Adaptive Spectral Estimators for Fast Flow Profile Detection. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2013, 60, 421–427. [Google Scholar] [CrossRef] [PubMed]

- Elif, D.Ü.; Hakan, I.; İnan, G. Application of FFT and Arma Spectral Analysis to Arterial Doppler Signals. Math. Comput. Appl. 2003, 8, 311–318. [Google Scholar] [CrossRef]

- Larsson, E.; Stoica, P. Fast implementation of two-dimensional APES and Capon spectral estimators. Multidimens. Syst. Signal Process. 2002, 13, 35–54. [Google Scholar] [CrossRef]

- Jensen, J.A.; Svendsen, N.B. Calculation of pressure fields from arbitrarily shaped, apodized, and excited ultrasound transducers. IEEE Trans. Ultrason. Ferroelect. Freq. Control 1992, 39, 262–267. [Google Scholar] [CrossRef] [PubMed]

- Jensen, J.A. Field: A Program for Simulating Ultrasound Systems. Med. Biol. Eng. Comp. 1996, 34, 351–353. [Google Scholar]

- Granger, R.A. Fluid Mechanics; Dover: Mineola, NY, USA, 1995; ISBN 978-0486683560. [Google Scholar]

- Meacci, V.; Ricci, S.; Wiklund, J.; Birkhofer, B.; Kotze, R. Flow-Viz—An integrated digital in-line fluid characterization system for industrial applications. In Proceedings of the 11th IEEE Sensors Applications Symposium (SAS), Catania, Italy, 13–15 April 2016; pp. 128–133. [Google Scholar]

- 754-2008—IEEE Standard for Floating-Point Arithmetic. 2008. Available online: https://doi.org/10.1109/IEEESTD.2008.4610935 (accessed on 12 December 2018).

- Al Kadi, M.; Janssen, B.; Huebner, M. Floating-Point Arithmetic Using GPGPU on FPGAs. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, ISVLSI, Bochum, Germany, 3–5 July 2017; pp. 134–139. [Google Scholar]

- Sanchez, A.; Todorovich, E.; De Castro, A. Exploring the Limits of Floating-Point Resolution for Hardware-In-the-Loop Implemented with FPGAs. Electronics 2018, 7, 219. [Google Scholar] [CrossRef]

| Device | Cyclone V | ||||

|---|---|---|---|---|---|

| ALM | ALUT | Reg | Memory Bits | DSP | |

| data-adaptive demodulator | 831 | 1271 | 871 | 17700 | 2 |

| coeff-adaptive demodulator | 818 | 1056 | 869 | 17700 | 2 |

| non-adaptive demodulator | 523 | 758 | 803 | 17700 | 2 |

| Parameters Ki | Parameters Di | Cut-off Frequency (Normalized) | Cut-off Frequency |

|---|---|---|---|

| K0 = 32, K1 = 17, K2 = 9, K3 = 14 | D1 = 1, D2 = 3, D3 = 1, D4 = 1 | FL = 0.01 | 1 MHz |

| SNR (dB) | Non-Adaptive | Coeff-Adaptive | Data-Adaptive | Reference |

|---|---|---|---|---|

| S16 | 24.7 | 60.2 | 83.4 | 85.0 |

| S12 | 5.7 | 36.3 | 83.4 | 85.0 |

| S08 | 0.0 | 14.2 | 83.4 | 85.0 |

| Non-Adaptive | Coeff-Adaptive | Data-Adaptive | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| BS1 | BS2 | BS3 | BS4 | BS1 | BS2 | BS3 | BS4 | BS1 | BS2 | BS3 | BS4 | |

| S16 | 9 | 9 | 9 | 9 | 8 | 8 | 7 | 7 | 7 | 7 | 6 | 6 |

| S12 | 9 | 9 | 9 | 9 | 8 | 8 | 7 | 7 | 3 | 7 | 6 | 6 |

| S08 | 9 | 9 | 9 | 9 | 8 | 8 | 7 | 7 | 0 | 6 | 6 | 6 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ricci, S.; Meacci, V. Data-Adaptive Coherent Demodulator for High Dynamics Pulse-Wave Ultrasound Applications. Electronics 2018, 7, 434. https://doi.org/10.3390/electronics7120434

Ricci S, Meacci V. Data-Adaptive Coherent Demodulator for High Dynamics Pulse-Wave Ultrasound Applications. Electronics. 2018; 7(12):434. https://doi.org/10.3390/electronics7120434

Chicago/Turabian StyleRicci, Stefano, and Valentino Meacci. 2018. "Data-Adaptive Coherent Demodulator for High Dynamics Pulse-Wave Ultrasound Applications" Electronics 7, no. 12: 434. https://doi.org/10.3390/electronics7120434

APA StyleRicci, S., & Meacci, V. (2018). Data-Adaptive Coherent Demodulator for High Dynamics Pulse-Wave Ultrasound Applications. Electronics, 7(12), 434. https://doi.org/10.3390/electronics7120434