1. Introduction

Modern-day digital devices such as cellular phones, camcorders, calculators, digital cameras, portable electronic devices, microprocessors, DSP core, handheld computers and PDAs, MP3 personal players, and so on utilize switch-mode power supplies (SMPSs). The devices need to have regulated output voltages irrespective of the perturbation in the input voltage or load current. For this purpose, traditionally, analog controllers have been applied to SMPSs to ensure regulated voltages for the digital devices. Analog controllers, however, show limitations in the form of poor design portability, large size, low reliability, and low flexibility. Digital controllers, on the other hand, offer advantages in the form of high flexibility and programmability, competency to implement complex control strategies, no need to alter hardware upon changing algorithms, high performance/cost ratio, and excellent dynamic performance, among others [

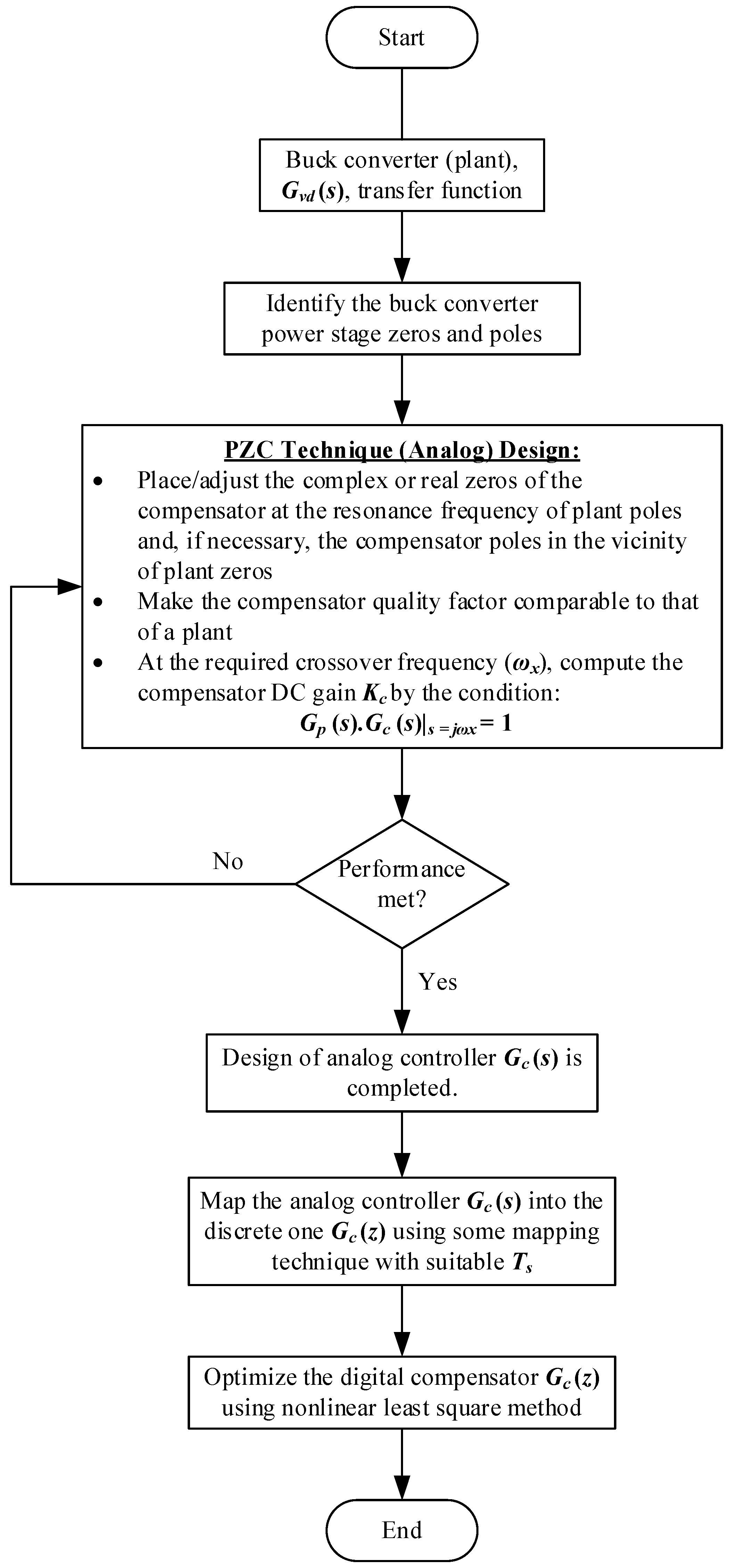

1]. Consequently, SMPS designers are more interested in developing efficient and optimized digital controllers as compared to the predominately used analog controllers. In this paper, well-recognized PZC techniques-based optimized digital controllers are designed for buck converters to display much-improved performance. One of the optimization techniques, named the nonlinear least squares technique, is employed to optimize the performance of PZC-based digital controllers.

As far as the literature review is concerned, in [

2], a pole-zero-cancellation technique-based digital controller for a buck converter was suggested by Abe et al. to improve the performance characteristics. The effect of the resonance peak and ESR-zero is nullified by completely cancelling the poles and the zero of the buck converter with the help of the complex zeros and the pole of the compensator, respectively. An additional pole representing a simple low-pass filter is introduced to gain control of the characteristics of the composite buck converter system. A two-pole two-zero analog controller is mapped into the digital controller using bilinear transformation. In [

3], the same authors (Abe et al.) applied successfully the two-pole two-zero analog compensator to the buck and boost converters to ensure superior performance, yet without cancelling the RHP-zero in the case of the boost converter. The effect of change in the capacitance of the output capacitor in a PZC-based digitally controlled buck converter on the stability margin, and thus the performance, was investigated in [

4]. Reference [

5] also suggested the application of a three-pole two-zero (analog) compensator with complex as well as real zeros to a switching converter exhibiting nonminimum phase characteristics. Such a converter possesses RHP-zero in its transfer function, which limits the bandwidth, thus causing the response to be slow and sluggish. Reference [

6] suggested a slightly different approach for designing a PZC-based digital controller for the step-down converter. Rather than using the real or complex zeros by the compensator close to the resonant frequency of the converter’s power stage, the compensator zeros are selected on the basis of the quality factor and output impedance of the plant. The effect of the quality factor on compensator design is also investigated efficiently. In [

7], the task of providing feedback compensation to the relatively complicated switching converters (as they involve RHP-zero), namely boost and flyback working in continuous conduction mode, was efficiently performed through various combinations of PZC-based controllers. The PZC-based digital controllers mentioned in the aforementioned references show somewhat satisfactory performance. Their performance may even be improved by retuning their coefficients through some optimization techniques.

Many researchers successfully applied advanced numerically based or metaheuristic optimization techniques to tune the compensator parameters to ameliorate performance. Reference [

8] suggested the tuning of the parameters of the digital controller designed on the basis of a Chebyshev polynomial approach for the fifth-order boost converter through a genetic algorithm (GA). The problem with the GA is that it has to employ its three operators, namely selection, crossover, and mutation, at each iteration, thus resulting in slower responses. In addition, it shows enhanced sensitivity to the initial population and does not use gradients. In [

9], although metaheuristic techniques such as particle swarm optimization (PSO) and the gravitational search algorithm (GSA) were successfully employed for the fine-tuning of parameters of Type II and Type III compensators applied to a step-up converter, but they may converge prematurely. Mercader et al. in [

10] tried to overcome the problem of convergence to the local minimum of convex optimization and proposed a convex-concave procedure (CCP) for the fine-tuning of PID controller coefficients that controlled the loop shape efficiently to ensure better dynamic performance. On the other hand, the NLS method capitalizes on the structure of the Hessian, which can be attained through the computation of Jacobian (first-order derivatives only) and minimizes the errors (residuals) quickly, and thus ensures better set-point tracking.

In addition, many instances in the literature have been reported where the nonlinear least squares (NLS) method has been successfully employed to optimize the performance of various types of compensators used for various applications. In [

11], optimization of the discrete root locus-based discrete-time controller applied to a buck converter was accomplished through the NLS method. In [

12], tuning of the PID-based track-keeping controllers of a remotely controlled autonomous in-scale fast-ferry model was carried out through the NLS method and a genetic algorithm (GA), where the former showed superiority over the latter one while doing sea trials. Reference [

13] suggested the use of the NLS method for the optimization of offline pulse patterns for arbitrary modulation indices and arbitrary numbers of modules per branch, while minimizing the harmonic content of the load current (specifically measured in the total demand distortion (TDD)), instead of using selective harmonic elimination, in the case of the indirect modular multilevel converter (MMC). In [

14], a Levenberg-Marquardt (LM) and quasi-Newton (QN)-based NLS hybrid method was used efficiently to improve the performance of the designed linear-phase quadrature mirror filter (QFM) bank in the form of mean squares error in passband and stopband regions, as well as peak reconstruction error (PRE) and error in the transition band at quadrature frequency. This was accomplished by optimizing the quadratic measure of the ideal characteristics of the prototype filter and filter bank at quadrature frequency. In [

15], a predictive current controller with an extended-state observer (ESO), suggested for the grid integration of wind energy systems, utilized the NLS method to minimize a cost function, defined as a sum of the squared values of d-axis and q-axis current errors, while computing the optimal converter switching time. In [

16], calibration of the roadside camera employed in traffic surveillance systems was accomplished on the basis of the least squares optimization method, which involved camera-intrinsic parameters and rotation angles. In [

17], for anticipating the epileptic seizure via EEG signals in epileptic individuals suffering from unexpected and momentary electrical deterioration in the brain, fitting of the EEG signals filtered through singular spectrum analysis into the exponential curve was carried out using the NLS method. Statistical examination of the features extracted from exponential curves assists in diagnosis. In [

18], nonlinear rational systems were identified using an NLS-based, globally consistent two-step estimator. In [

19], a high face recognition rate was achieved by performing NLS computations, while taking into account the ‘holistic’ and ‘detailed’ features of the face.

Although enormous numbers of examples of the application of the NLS method to control plants of various types are found in the literature, to the best knowledge of the authors, very limited instances are found in the literature where pole-zero-cancellation-based digital controllers have been optimized through the NLS method. In this paper, PZC-based optimized digital controllers are, thus, suggested for the buck converter to achieve much-improved performance.

The paper is formulated in the following way.

Section 2 describes the dynamics of the buck converter, which is considered to be the plant in the paper. Three types of pole-zero-cancellation (with complex and real zeros)-based digital controllers are designed in

Section 3. The digital controller design techniques are essentially of the types digital redesign or emulation. The NLS method involving the LM algorithm to optimize the digital controllers is detailed in

Section 4. Nonlinearities involved in the digital control loop are modelled in

Section 5.

Section 6 involves the redesigning and reoptimizing of the digital controllers when the nonlinear effects in the digital control loop are considered.

Section 7 is dedicated to additional simulation results. HiL implementation is described in

Section 8. Concluding remarks are given in

Section 9.

2. Buck Converter Modelling

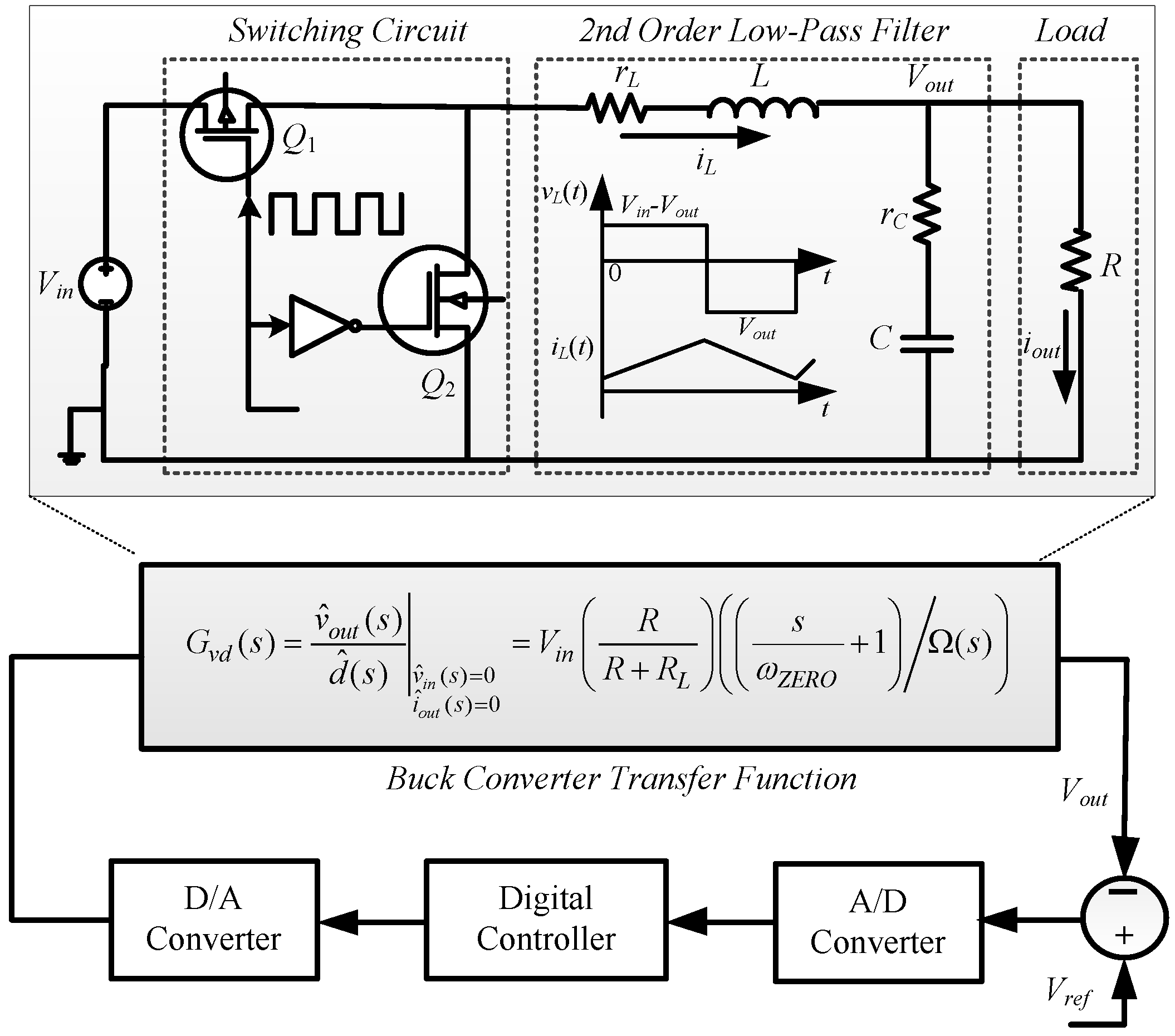

For the sake of reducing higher unregulated DC input voltage,

Vin, to lower regulated DC output voltage,

Vout, a realistic buck converter circuit (see

Figure 1) is used, as it takes into consideration the parasitic resistances, i.e., capacitor equivalent series resistance (ESR) and inductor direct current resistance (DCR), denoted explicitly by

rC and

rL, respectively. Owing to capacitor ESR, a zero is introduced into the buck converter transfer function [

20]. The component values to be considered for the converter throughout the paper are the following:

Vin = 3.6 V,

Vout = 2.0 V,

L = 4.7 µH,

C = 4.7 µF,

rL = 505 mΩ,

rC = 5 mΩ,

fs = 1000 kHz, and

Ts = 1/

fs = 1 µs. The block diagram of the closed-loop (digital) control system containing the buck converter power stage, ADC and DAC converters, and the digital controller is shown in

Figure 1.

The buck converter’s dynamics (transfer function) imperative for the controller design can be derived through its small-signal AC-equivalent circuit model (see

Figure 2), where the nonlinear power switches

Q1 and

Q2 are replaced by their equivalent linear small-signal models [

21]. By applying the averaging and linearization technique adopted in [

22] to the small-signal model, the small-signal transfer functions, such as duty cycle-to-output voltage

, input voltage-to-output voltage

, and load current-to-output voltage (loaded power converter output impedance

), can be computed and are described by Equations (1)–(3), respectively [

22,

23].

where

and

Here , , and represent the filter resonance frequency, capacitor zero frequency, and the quality factor of the filter, respectively.

Among the transfer functions, the one described in Equation (1), i.e., duty cycle-to-output voltage, is controlled through the controller for output voltage regulation. To achieve the closed-loop characteristics, and thus required performance, a controller is applied to it as it behaves as a plant. The contains a complex conjugate pair whose effect can be nullified by the complex or real zeros of the compensator.

In order to design the digital controller, the continuous-time converter transfer function

is discretized using zero-order-hold (ZOH) with a sampling period

, as follows:

For the component values mentioned above, the transfer function in the analog and digital form of the buck converter with a short description is presented in

Table 1.

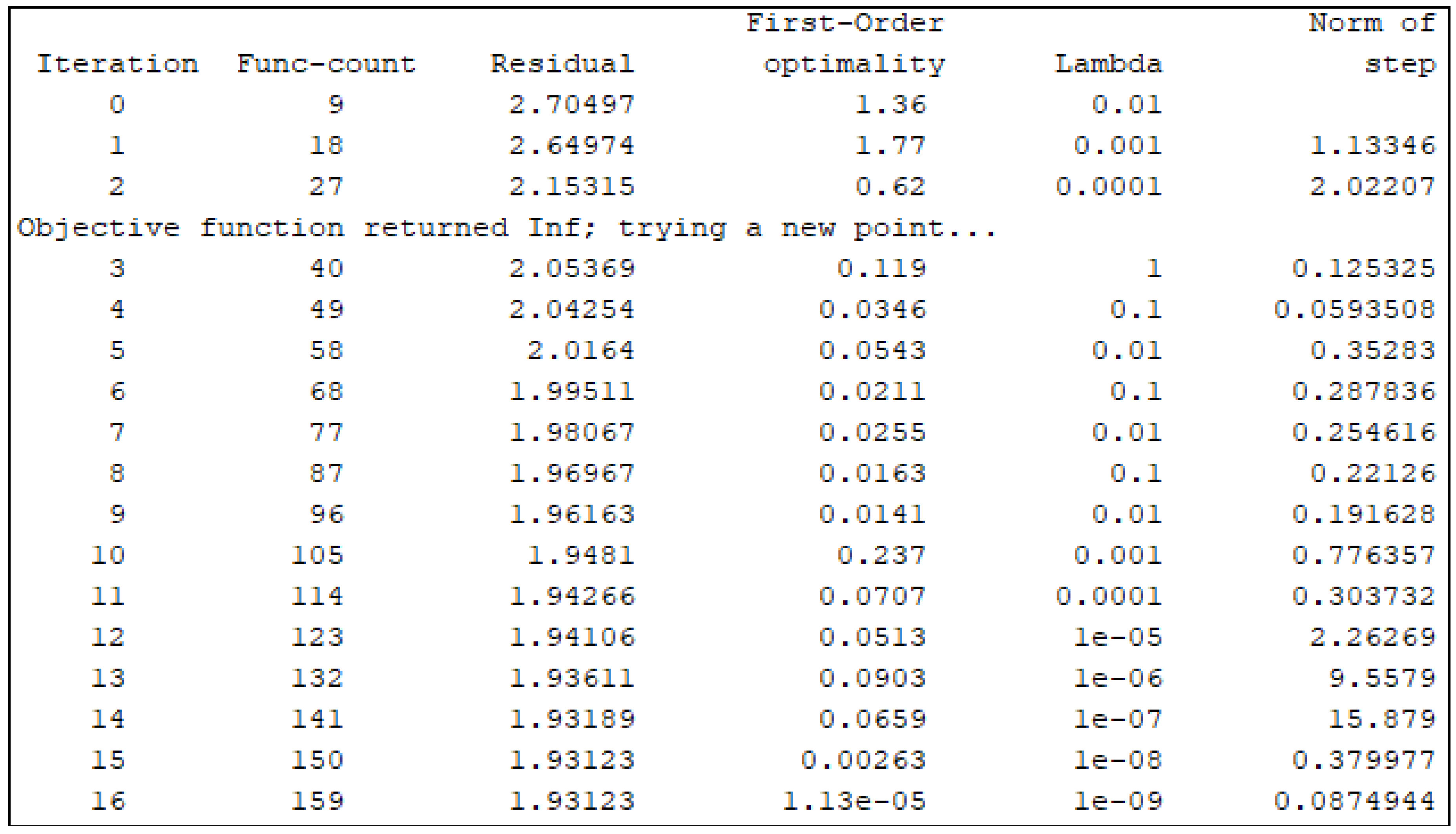

4. NLS Method-Based Optimized Digital Controllers

In the context of optimization, the nonlinear least squares (NLS) method bears a tempting structure that can be exploited with great effectiveness in algorithm design. Regarding the compensated buck converter system, minimization of the voltage error signal essentially constitutes the NLS problem. Specifically, the NLS technique can be employed to retune the discrete-time controller coefficients for fast setpoint tracking. This is accomplished by adjusting the controller coefficients to speedily reduce the error e(t) = Vout − Vref at all steps of the simulation time. As the minimization of the sum of squares of the error functions is carried out by the algorithm at each step, this constitutes the multiobjective optimization problem.

In the paper, for calculating the sum of error squares, among the different large-scale algorithms [

25], such as the trust-region-reflective (TRR), variable projection (VP), and Levenberg–Marquardt (LM) algorithms, LM is employed. Linear algebra is exploited in large-scale algorithms which do not require or store full matrices for its operation. It is a well-established fact that the LM algorithm performs better when bound constraints are not considered in the problem.

The algorithm starts with the initial design vector, x0, indicating the initial design variables in the form of coefficients of the digital controller computed through the pole-zero-cancellation techniques. For the considered cases, no restriction has been imposed on the lower and upper bounds of the design variables.

Mathematically speaking, the NLS method using the LM algorithm involves minimizing the sum of squares of the error signal, i.e.,

subject to the constraints:

where

,

, and

. Here,

and

, and

and

are the matrices of doubles for linear inequalities and equalities, and nonlinear inequalities and equalities, respectively. Similarly,

and

are the vectors of doubles for linear inequalities and equalities, respectively, and

and

represent the lower and upper bounds, respectively, on each

component. In our case, since no restriction is imposed on the bounds of design variables for the unconstrained multiobjective optimization problem, all matrices and vectors are empty sets. Here, the function to be minimized,

, representing the

l2-norm of error, is assumed to be continuously differentiable at point

. It is assumed that

. As remarked, the vector

represents the number of design/decision variables, which are specifically the coefficients of the digital controllers.

In the compensated control systems, in order to achieve the targeted trajectories realistically, the residual

, being a function from

to

, described in Equation (31)

is made small optimally and converged speedily. Rapidly converged minimum residuals result in better set-point tracking. A unique solution is guaranteed due to the convex nature of the minimizer.

In order to get deep mathematical insight, the algorithm forces the output

to track the continuous required trajectory

for the decision vector

x and scaler

t. That is to say,

Discretization of the integral through an appropriate quadrature formula reduces Equation (32) to the least squares problem:

A

m-by-

n-sized Jacobian matrix

of the residual

of

n variables is computed by

On the basis of

, the specially structured gradient vector

and Hessian matrix

of the NLS method are calculated by Equations (35) and (36), respectively.

where

The matrix comes with the property that it tends to approach zero as the residual approaches zero on the occasion the decision variables , finally settling to optimal values. In other words, the matrix gives an indication of how fast the minimization of the error is accomplished.

By amalgamating the salient characteristics of the Gauss–Newton (GN) and steepest descent (SD) algorithms, the LM method computes the search direction on the basis of a solution of the linear set of equations [

26], i.e.,

More precisely, the LM method modifies the GN search direction by altering

with

. By replacing the identity matrix with the diagonal of the Hessian, Equation (38) can be expressed alternatively as

Or, equivalently, in terms of the least squares problem, Equation (39) takes the form

The magnitude and direction of

is controlled through the scalar

, whose initial value

is set empirically, perhaps, as 100. The LM method therefore uses a search direction that falls within the directions calculated by the GN and SD methods. The LM algorithm, thus, essentially is an aggregation of the SD and GN algorithms. For example, when

is zero, the direction

refers to the direction of the GN method, whereas when

tends to infinity,

assumes the direction of SD, with its magnitude tending to zero. This comes with the observation that the term

holds true for some adequately large values of

. Through the control of the term

, descent can be ensured even when second-order terms, which limit the GN method’s efficiency, are experienced. The algorithm adjusts the value of

during each of the step as follows:

In a nutshell, the LM algorithm works in the following way:

It starts with an initial guess and iterates for .

The Lagrange multiplier is then selected for each step .

Equation (39) or (40) is solved for determining .

For the next iteration, , is calculated.

At the end, the solution is checked for convergence.

Although several stopping criteria, such as absolute function criterion, sequence convergence criterion, maximum iteration count criterion, and so on, can be adopted, here, the algorithm stops when the final change in the sum of squares relative to its initial value is less than the default value of the function tolerance. One must remember that although the algorithm ensures optimal performance, convergence to the global minimum of the objective function cannot be guaranteed. To realize the LM algorithm based on the NLS method, a MATLAB/Simulink environment is used. Termination tolerance for both the objective function and the parameter estimation is appropriately selected.

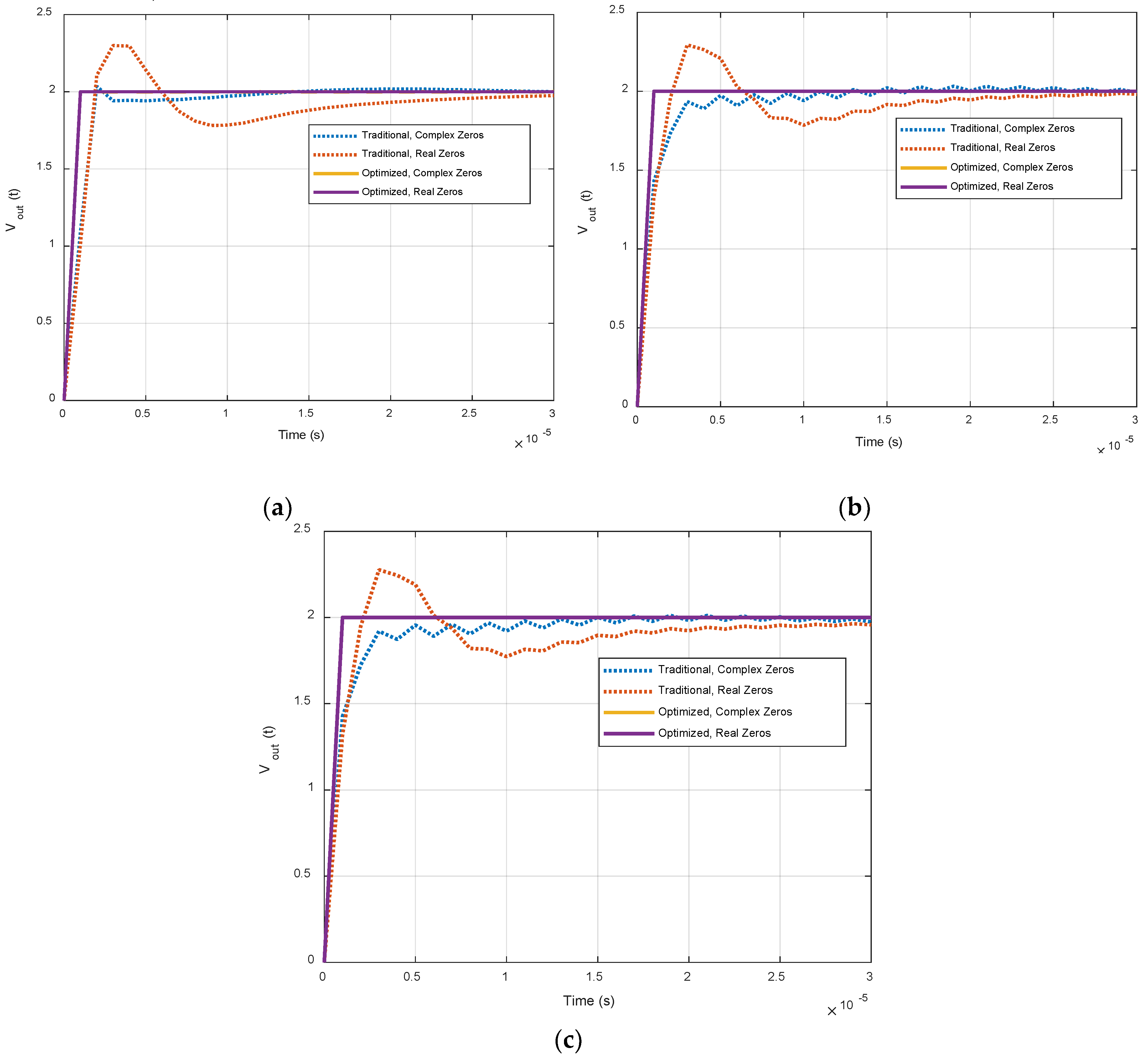

When the NLS method is applied to retune the coefficients of the digital controllers, tremendous improvement in performance is observed. All the controllers, traditional and optimized, in transfer function form, are summarized in

Table 2. Correspondingly, step response characteristics displayed by all the controllers, traditional and optimized, are shown in

Figure 8. The performance parameters in the form of maximum overshoot, settling time, and rise time, computed from the step response characteristics, are summarized and compared in

Table 3. From

Table 3, it is inferred that the optimized digital controllers offer much-improved performance as compared to their traditional counterparts. This validates the applicability and workability of the NLS method.

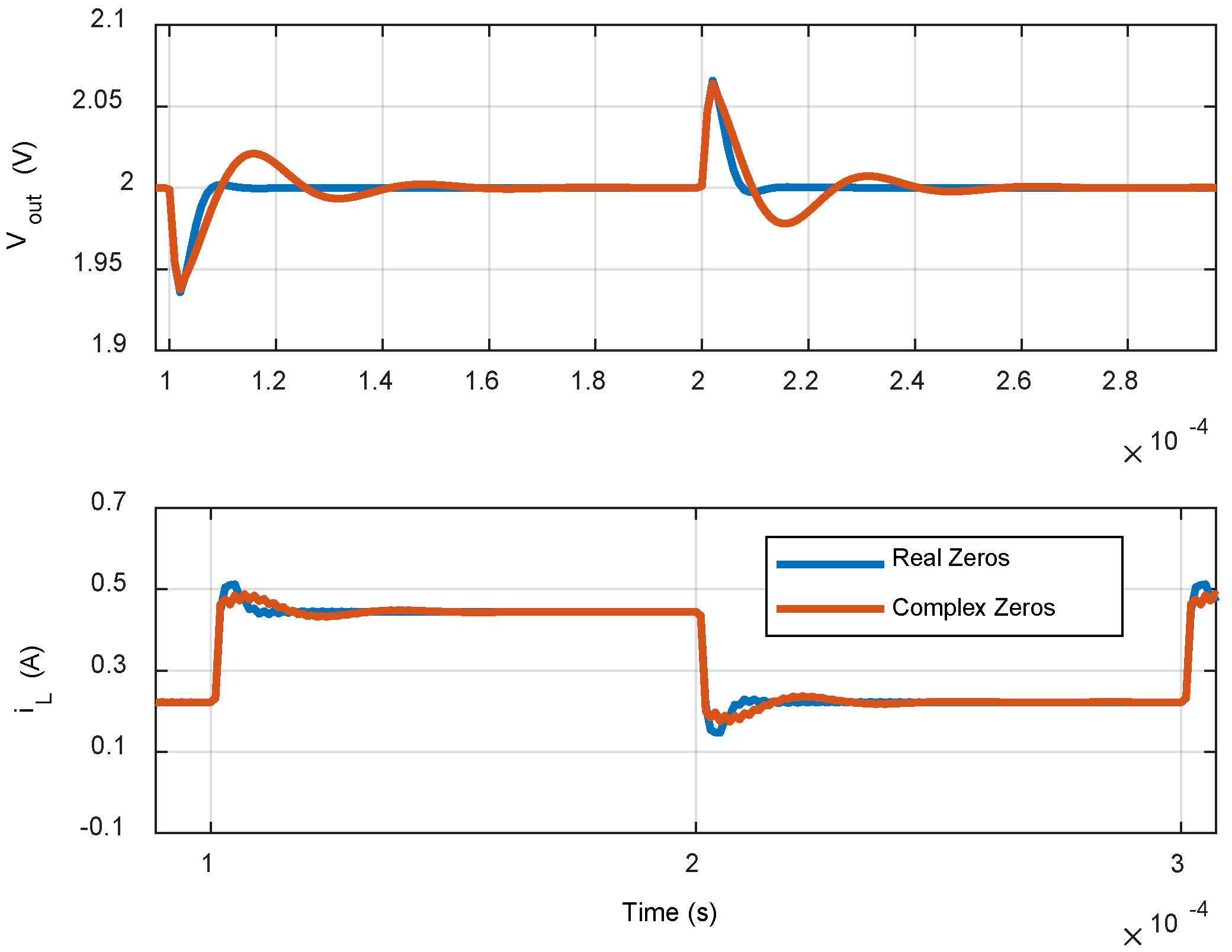

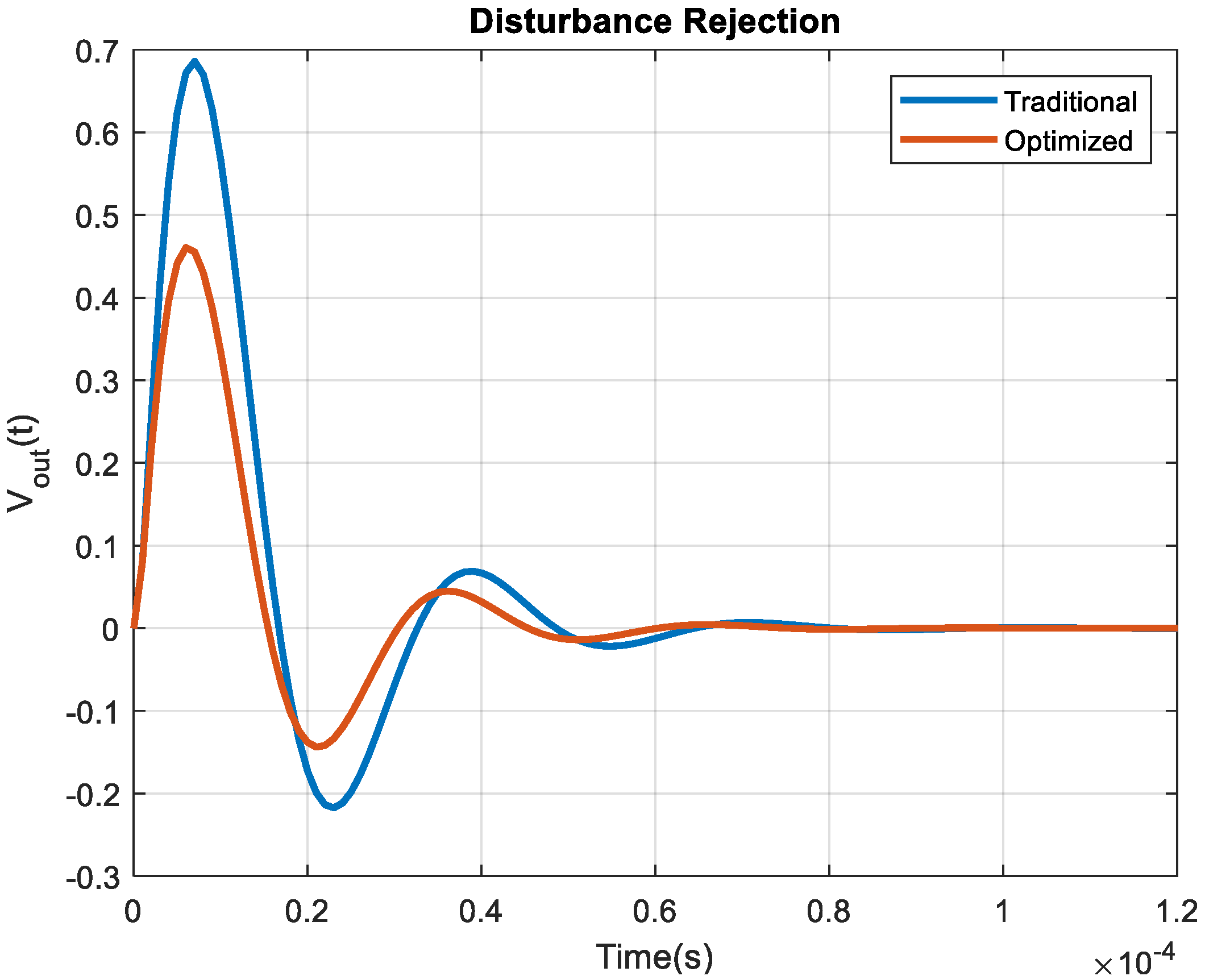

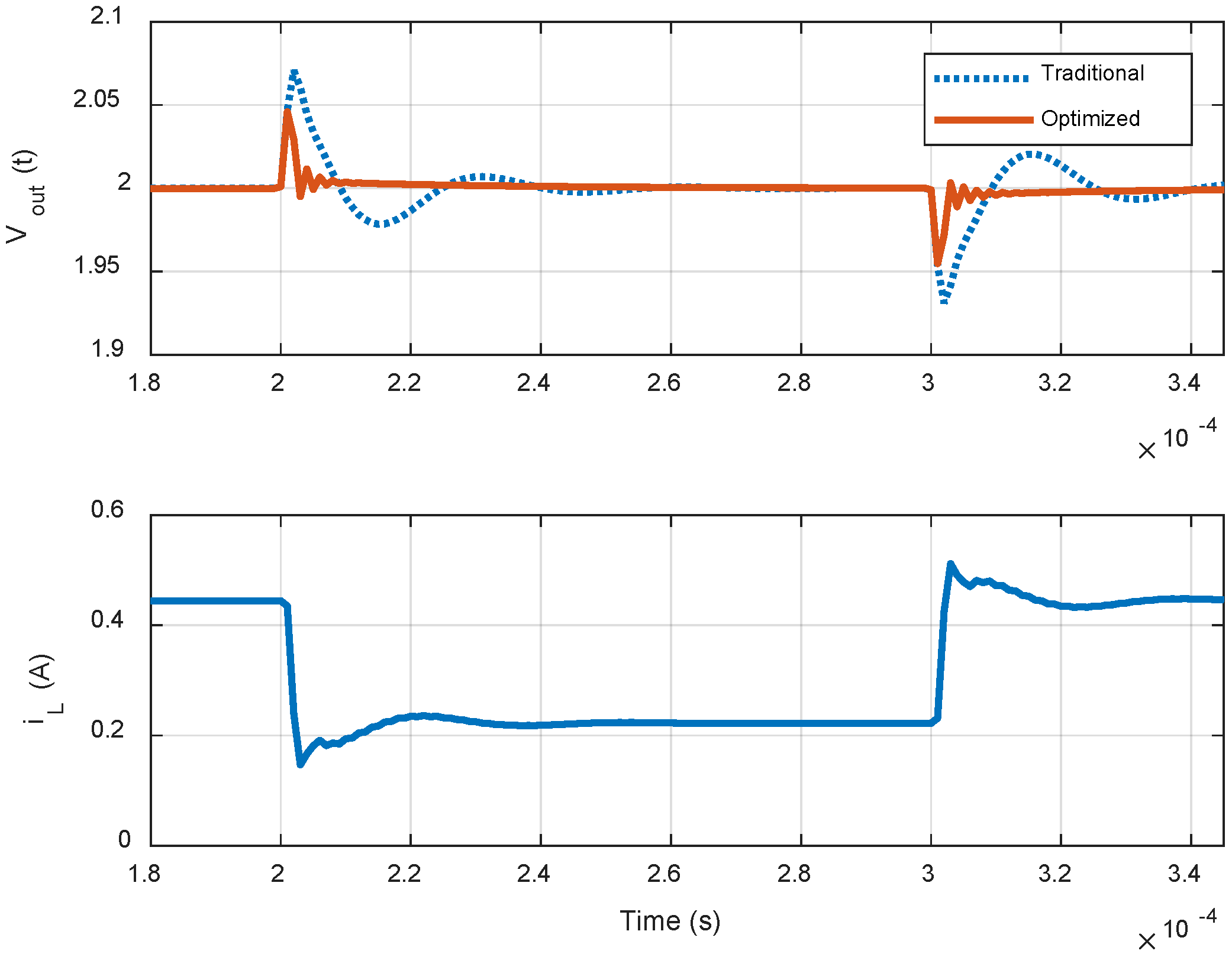

Like the step response characteristics, the optimized controllers also offer superior transient behavior. A three-pole two-zero (complex)-based optimized digital controller offers reduced recovery time and peak-to-peak spike voltage at the time of load transient as compared to its traditional form (see

Figure 9). In the same way, other optimized controllers also show fast transient response with regard to their unoptimized counterparts.

The optimized controller not only offers excellent set-point tracking and load regulation characteristics, but also exhibits improved disturbance rejection abilities against the disturbance (due to variations in the converter power-stage parameters because of aging or model uncertainties) injected at the converter input (see

Figure 10).

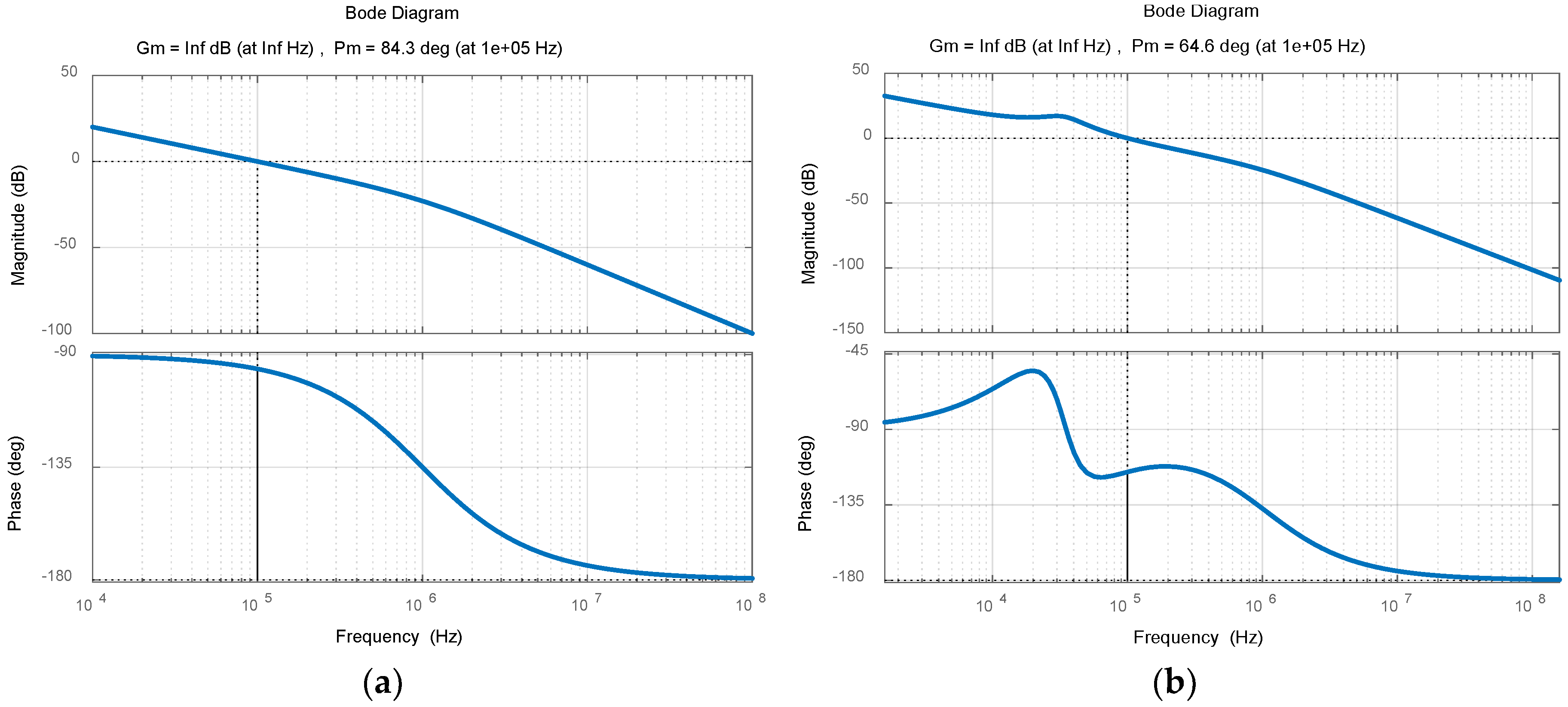

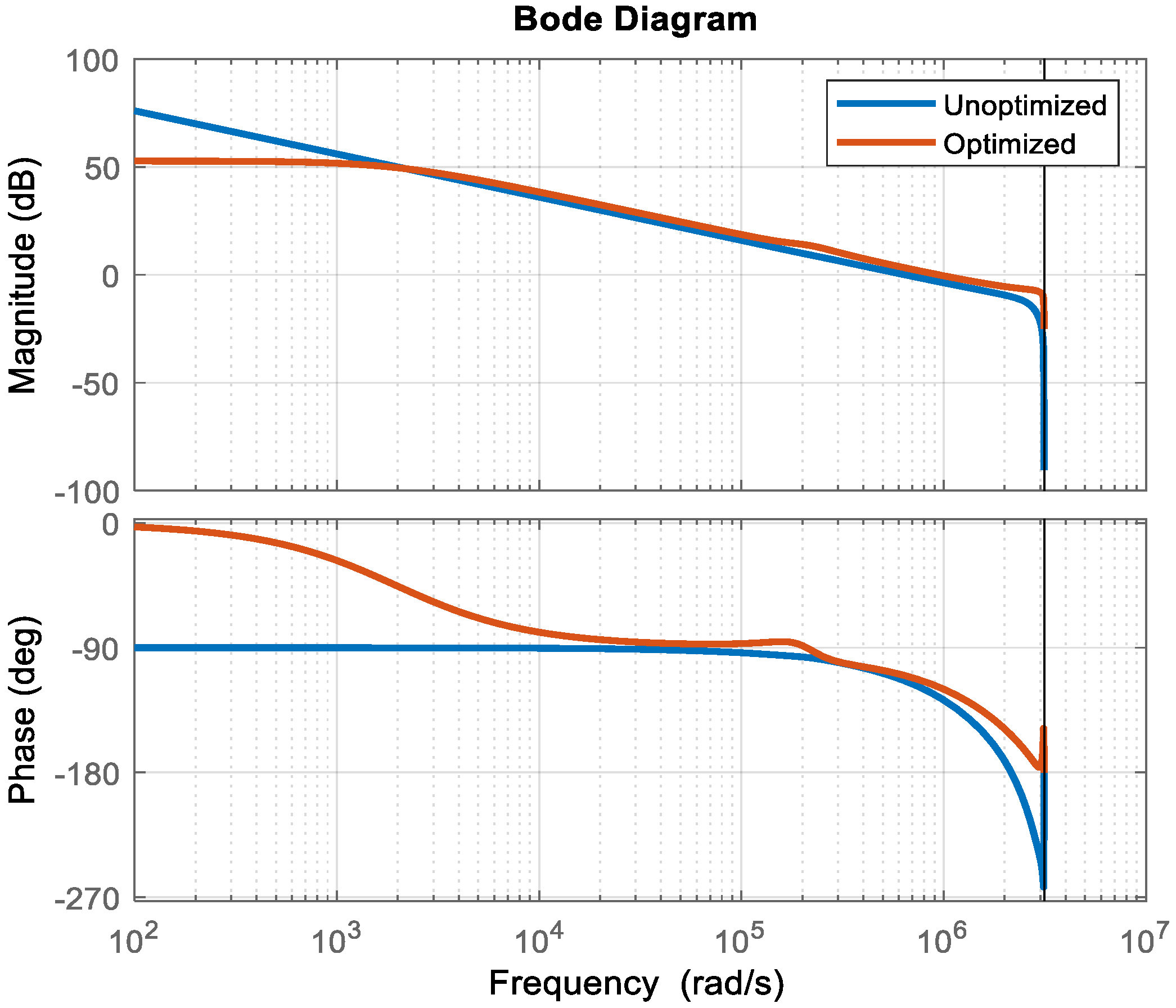

To gain more insight into the performance in terms of frequency-domain characteristics, the Bode plot of the unoptimized and optimized

of case 1 shown in

Figure 11 clearly depicts that the optimized digital controller assists in ensuring more phase margin (and thus system stability) for all the frequencies, as compared to the unoptimized digital controller.

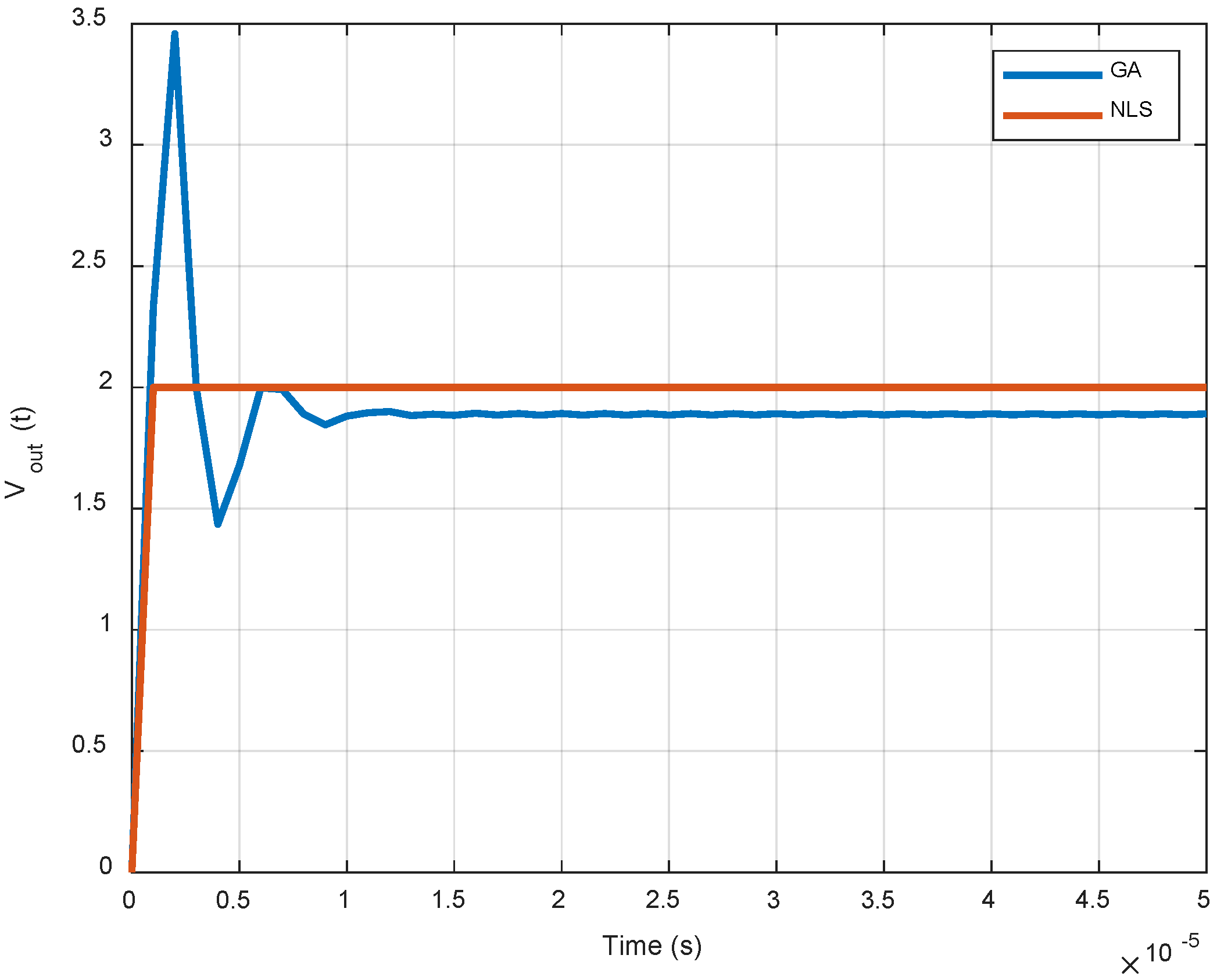

In order to validate the superiority of the proposed NLS method over the other optimization techniques, such as a genetic algorithm (GA), a comparison of the voltage response of the two-pole two-zero (complex)-based optimized digital controllers obtained through NLS and GA is presented in

Figure 12. For the typical design example, the NLS method completely outshines GA performance-wise (overshoots, steady-state error, etc.). The GA parameters considered are the following: objective function = Integral Time Absolute Error (ITAE), population size = 200, generations = 25, crossover fraction = 0.65, and function tolerance = 1 × 10

−6.

8. Rapid Hardware-in-the-Loop (HiL) Implementation

The Simulink plugged-in architecture-level design tool named Xilinx System Generator (XSG), for DSP from Xilinx, is employed for the implementation of a digital control algorithm on a high-speed, high-end, and high-density Basys 3 Artix-7 FPGA board after automatically generating portable, synthesizable, and vendor-neutral VHDL code. XSG automatically invokes both the Core Generator and ChipScope generator to construct the netlist and cores, and thus the configuration bitstream, once the target device/FPGA XC7A35T-1CPG236C from Xilinx, Inc. (an American technology company) and the compilation target (Hardware Co-Simulation JTAG) are set in its settings. High-level abstractions produced by a control design engineer in the Simulink model are translated into the low-level and executable VHDL code through the bitstream. FPGAs can be easily interfaced with Simulink through the XSG environment. This enables control design engineers to build sophisticated digital control algorithms quickly, with respect to the traditional Resistor-Transistor Logic (RTL) development times without having the knowledge of VHDL language, and then implement it on an FPGA, thus shortening the design and testing time.

The optimized digital controller described in Equation (47) can be expressed equivalently in the standard form as follows:

Equation (48) can be translated into the difference equation through the inverse Z-transform as follows:

The above controller difference equation realized using hardware-realizable blocks from the XSG library is shown in

Figure 16. The controller coefficients are realized using a single precision floating-point data type characterized by the word lengths of 32 bits. A new hardware cosimulation library and thus a synthesizable block (which is to be downloaded into the Artix-7 board) are automatically generated (see

Figure 16) on the successful generation of VHDL code. The JTAG cosimulation block is the equivalent representation of the previously used XSG simulation blocks, including the gateway-in and gateway-out blocks used for the realization of digital control algorithms. JTAG communication between a hardware platform (Artix-7 FPGA board) and Simulink (on PC) for a supported board is carried out for downloading the bitstream. In this way, a JTAG-based hardware cosimulation is performed by downloading the Vivado program-based generated bit file into the FPGA, thereby closing the loop.

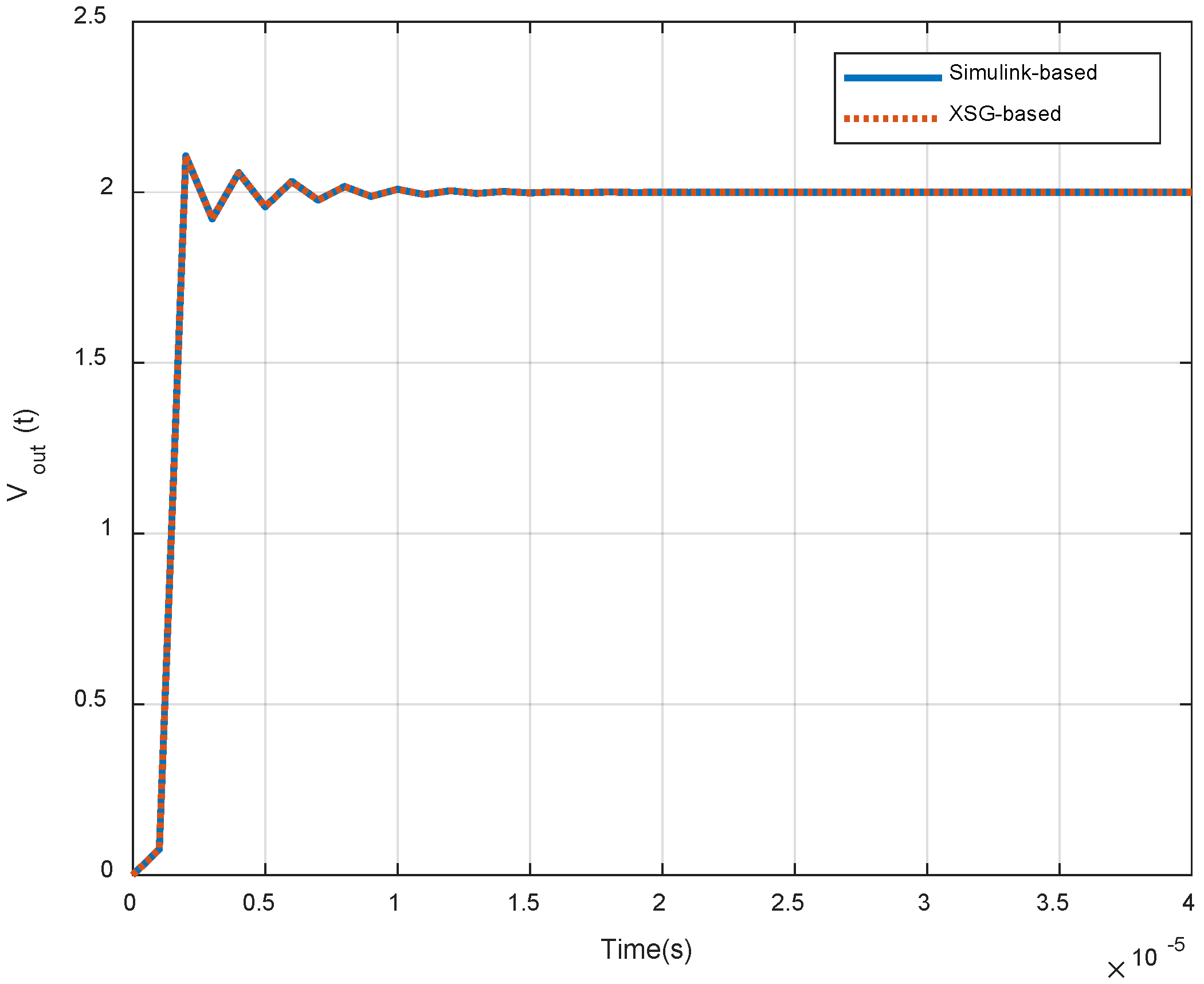

Careful analysis of the step response shown in

Figure 17 depicts that the XSG-based compensated system displays almost the same performance as the Simulink-based compensated system. This is due to the fact that XSG uses the floating-point data format for the realization of controller coefficients, just like Simulink, which utilizes ‘double’ type data. Set time-steps for the hardware implementation, rounding and truncation errors, and the sampling issues associated with the digital systems may cause slight performance deterioration in the XSG-based system. The bit-true and cycle-true characteristic of the XSG makes the numerical simulations such as if they were attained through the real hardware implementation.