Temperature-Dependent Degradation in SiC MOS Structures Under Laser-Assisted AC BTI

Abstract

1. Introduction

2. Experiments

3. Results and Discussion

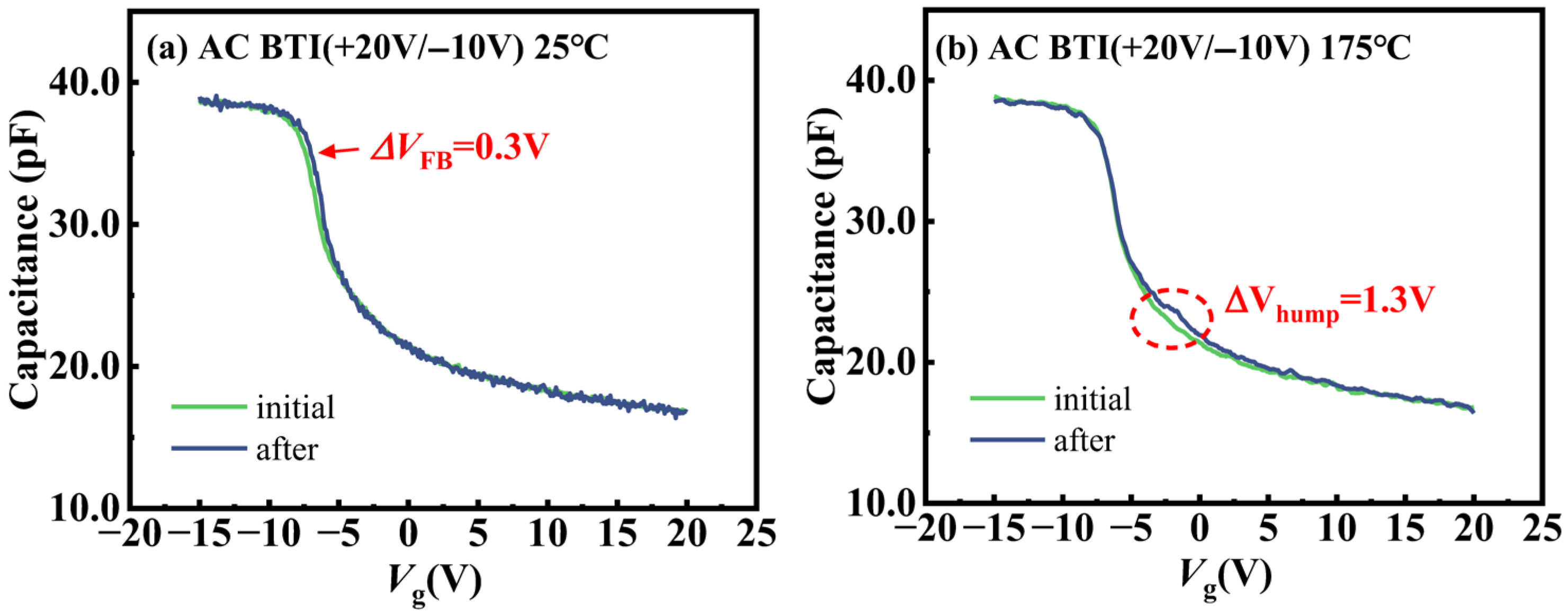

3.1. Effects of AC BTI on P-MOS Characteristics at Different Temperatures

3.2. Effects of AC BTI on N-MOS Characteristics at Different Temperatures

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kimoto, T. Material science and device physics in SiC technology for high-voltage power devices. Jpn. J. Appl. Phys. 2015, 54, 040103. [Google Scholar] [CrossRef]

- She, X.; Huang, A.Q.; Lucia, O.; Ozpineci, B. Review of Silicon Carbide Power Devices and Their Applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Di Giovanni, F. Silicon Carbide: Physics, Manufacturing, and Its Role in Large-Scale Vehicle Electrification. Chips 2023, 2, 209–222. [Google Scholar] [CrossRef]

- Kimoto, T.; Watanabe, H. Defect engineering in SiC technology for high-voltage power devices. Appl. Phys. Express 2020, 13, 120101. [Google Scholar] [CrossRef]

- Fiorenza, P.; Giannazzo, F.; Roccaforte, F. Characterization of SiO2/4H-SiC Interfaces in 4H-SiC MOSFETs: A Review. Energies 2019, 12, 2310. [Google Scholar] [CrossRef]

- Puschkarsky, K.; Grasser, T.; Aichinger, T.; Gustin, W.; Reisinger, H. Review on SiC MOSFETs High-Voltage Device Reliability Focusing on Threshold Voltage Instability. IEEE Trans. Electron Devices 2019, 66, 4604–4616. [Google Scholar] [CrossRef]

- Zhong, X.; Xu, C.; Jiang, H.; Liao, R.; Tang, L.; Huang, Y.; Zhao, K.; Xiao, N.; Qi, X.; Liu, L.; et al. Recovery Performance of the Dynamic Threshold Voltage Drift of Silicon Carbide MOSFETs. IEEE Trans. Power Electron. 2024, 39, 7620–7631. [Google Scholar] [CrossRef]

- Grasser, T.; Feil, M.W.; Waschneck, K.; Reisinger, H.; Berens, J.; Waldhoer, D.; Vasilev, A.; Waltl, M.; Aichinger, T.; Bockstedte, M.; et al. Gate Switching Instability in Silicon Carbide MOSFETs—Part II: Modeling. IEEE Trans. Electron Devices 2024, 71, 4218–4226. [Google Scholar] [CrossRef]

- Feil, M.W.; Waschneck, K.; Reisinger, H.; Berens, J.; Aichinger, T.; Prigann, S.; Pobegen, G.; Salmen, P.; Rescher, G.; Waldhoer, D.; et al. Gate Switching Instability in Silicon Carbide MOSFETs—Part I: Experimental. IEEE Trans. Electron Devices 2024, 71, 4210–4217. [Google Scholar] [CrossRef]

- Grasser, T.; Feil, M.; Waschneck, K.; Reisinger, H.; Berens, J.; Waldhoer, D.; Vasilev, A.; Waltl, M.; Aichinger, T.; Bockstedte, M.; et al. A Recombination-Enhanced-Defect-Reaction-Based Model for the Gate Switching Instability in SiC MOSFETs. In Proceedings of the 2024 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 14–18 April 2024; pp. 3B.1-1–3B.1-7. [Google Scholar]

- Gómez, A.A.; García-Meré, J.R.; Rodríguez, A.; Rodríguez, J.; Jimenez, C.; Roig-Guitart, J. Deep Investigation on SiC MOSFET Degradation under Gate Switching Stress and Application Switching Stress. In Proceedings of the 2024 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 25–29 February 2024; pp. 1067–1072. [Google Scholar]

- Cai, Y.; Sun, P.; Chen, C.; Zhang, Y.; Zhao, Z.; Li, X.; Qi, L.; Chen, Z.; Nee, H.-P. Investigation on Gate Oxide Degradation of SiC MOSFET in Switching Operation. IEEE Trans. Power Electron. 2024, 39, 9565–9578. [Google Scholar] [CrossRef]

- Yang, L.; Bai, Y.; Li, C.; Yang, C.; Chen, H.; Tang, Y.; Hao, J.; Tian, X.; Liu, X. Gate Oxide Instability of 4H-SiC p-Channel MOSFET Induced by AC Stress at 200 °C. IEEE Trans. Electron Devices 2023, 70, 379–382. [Google Scholar] [CrossRef]

- Cai, Y.; Chen, C.; Zhao, Z.; Sun, P.; Li, X.; Zhang, M.; Wang, H.; Chen, Z.; Nee, H.-P. Characterization of Gate-Oxide Degradation Location for SiC MOSFETs Based on the Split C–V Method Under Bias Temperature Instability Conditions. IEEE Trans. Power Electron. 2023, 38, 6081–6093. [Google Scholar] [CrossRef]

- Jiang, H.; Zhong, X.; Qiu, G.; Tang, L.; Qi, X.; Ran, L. Dynamic Gate Stress Induced Threshold Voltage Drift of Silicon Carbide MOSFET. IEEE Electron Device Lett. 2020, 41, 1284–1287. [Google Scholar] [CrossRef]

- Zhong, X.; Jiang, H.; Qiu, G.; Tang, L.; Mao, H.; Chao, X.; Jiang, X.; Hu, J.; Qi, X.; Ran, L. Bias Temperature Instability of Silicon Carbide Power MOSFET under AC Gate Stresses. IEEE Trans. Power Electron. 2021, 37, 1998–2008. [Google Scholar] [CrossRef]

- Habersat, D.B.; Lelis, A.J. AC-Stress Degradation and Its Anneal in SiC MOSFETs. IEEE Trans. Electron Devices 2022, 69, 5068–5073. [Google Scholar] [CrossRef]

- Xu, C.; Zhong, X.; Jiang, H.; Qiu, G.; Tang, L.; Ran, L. Impact of Duty Cycle and Junction Temperature on Dynamic Threshold Drift of SiC MOSFET. In Proceedings of the 2021 4th International Conference on Energy, Electrical and Power Engineering (CEEPE), Chongqing, China, 23–25 April 2021; pp. 347–350. [Google Scholar]

- Feil, M.W.; Waschneck, K.; Reisinger, H.; Berens, J.; Aichinger, T.; Salmen, P.; Rescher, G.; Gustin, W.; Grasser, T. Towards Understanding the Physics of Gate Switching Instability in Silicon Carbide MOSFETs. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–10. [Google Scholar]

- Jiang, H.; Qi, X.; Qiu, G.; Zhong, X.; Tang, L.; Mao, H.; Wu, Z.; Chen, H.; Ran, L. A Physical Explanation of Threshold Voltage Drift of SiC MOSFET Induced by Gate Switching. IEEE Trans. Power Electron. 2022, 37, 8830–8834. [Google Scholar] [CrossRef]

- Yano, H.; Inoue, N.; Kimoto, T.; Matsunami, H. Deep States in SiO2/p-Type 4H-SiC Interface. Mater. Sci. Forum 1998, 264–268, 841–844. [Google Scholar] [CrossRef]

- Yu, K.; Liu, Y.; Zhang, W.; Chen, H.; Li, C.; Ding, J.; Wang, J.; Zhai, D.; Wang, Y. Characterization of the slow-state traps in 4H–SiC P-type MOS capacitor by a preconditioning technique with high positive voltage stress. Micro Nanostruct. 2023, 175, 207506. [Google Scholar] [CrossRef]

- Fiorenza, P.; Frazzetto, A.; Guarnera, A.; Saggio, M.; Roccaforte, F. Fowler-Nordheim tunneling at SiO2/4H-SiC interfaces in metal-oxide-semiconductor field effect transistors. Appl. Phys. Lett. 2014, 105, 142108. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.

Share and Cite

Yu, K.; Wang, J. Temperature-Dependent Degradation in SiC MOS Structures Under Laser-Assisted AC BTI. Electronics 2026, 15, 337. https://doi.org/10.3390/electronics15020337

Yu K, Wang J. Temperature-Dependent Degradation in SiC MOS Structures Under Laser-Assisted AC BTI. Electronics. 2026; 15(2):337. https://doi.org/10.3390/electronics15020337

Chicago/Turabian StyleYu, Kanghua, and Jun Wang. 2026. "Temperature-Dependent Degradation in SiC MOS Structures Under Laser-Assisted AC BTI" Electronics 15, no. 2: 337. https://doi.org/10.3390/electronics15020337

APA StyleYu, K., & Wang, J. (2026). Temperature-Dependent Degradation in SiC MOS Structures Under Laser-Assisted AC BTI. Electronics, 15(2), 337. https://doi.org/10.3390/electronics15020337