A 1.06 ppm/°C Compact CMOS Voltage Reference

Abstract

1. Introduction

2. Proposed Design

2.1. and Current Generators

2.2. Compensation Circuit

2.3. Trimming Circuit

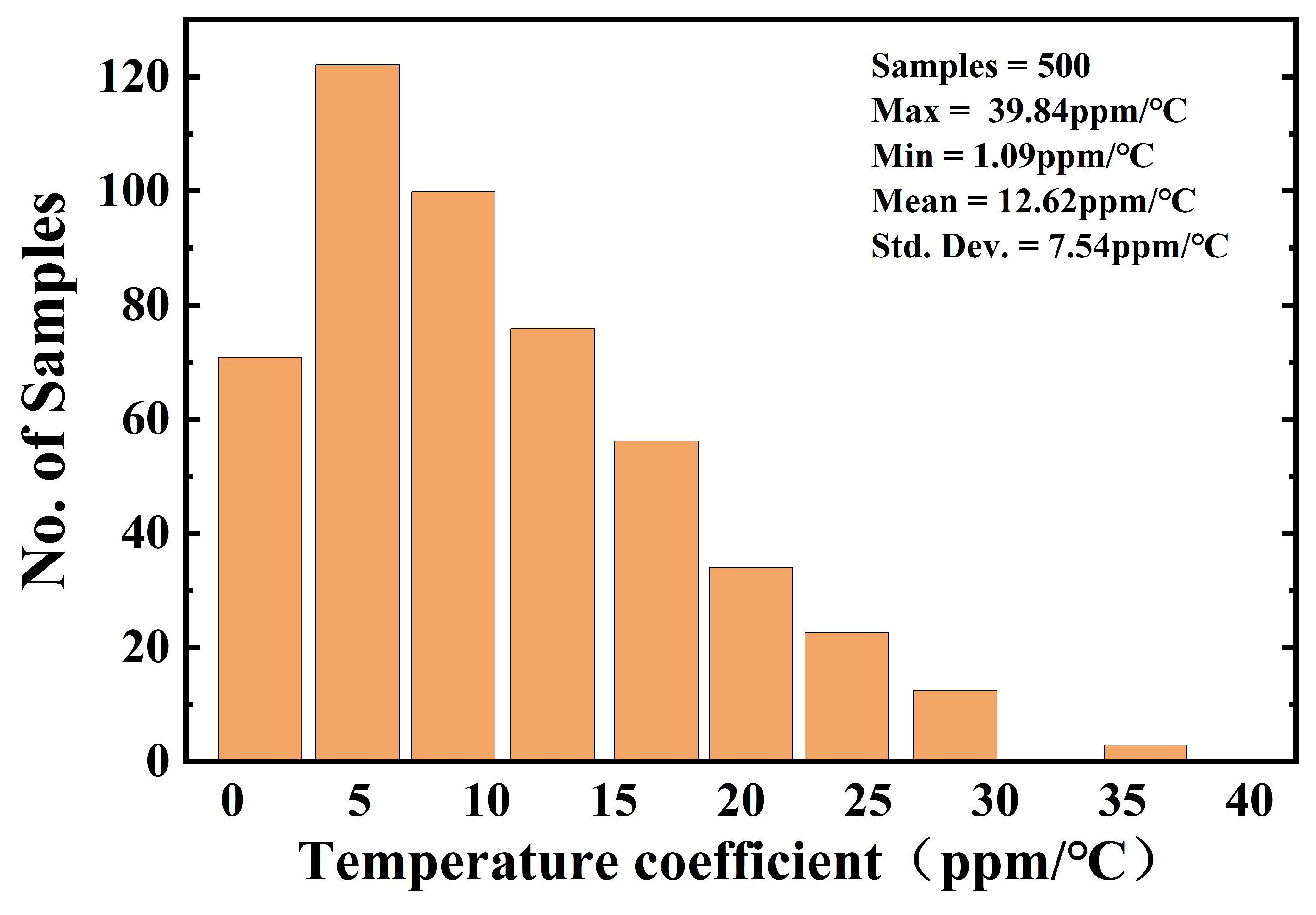

3. Post-Layout Simulation Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, C.-C.; Chao, K.-Y.; Sampath, S.; Suresh, P. Anti-PVT-variation low-power time-to-digital converter design using 90-nm CMOS process. IEEE Trans. Very Large Scale Integr. (Vlsi) Syst. 2020, 28, 2069. [Google Scholar] [CrossRef]

- Wen, K.; Shen, Y.; Li, Y.; Liu, S. A 0.018%/V Line Sensitivity Voltage Reference with −82.46 dB PSRR at 100 Hz for Bio-Potential Signals Readout Systems. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 2031. [Google Scholar] [CrossRef]

- He, L.; Zhong, C.; Qiu, H.; Zheng, B.; Li, J.; Luo, Z. A novel curvature-compensated adjustable output CMOS voltage reference. IEICE Electron. Express 2025, 22, 20250366. [Google Scholar] [CrossRef]

- Gagliardi, F.; Ria, A.; Piotto, M.; Bruschi, P. A CMOS Current Reference with Novel Temperature Compensation Based on Geometry-Dependent Threshold Voltage Effects. Electronics 2025, 14, 2698. [Google Scholar] [CrossRef]

- Jia, S.; Ye, T.; Xiao, S. A 2.25 ppm/°C High-Order Temperature-Segmented Compensation Bandgap Reference. Electronics 2024, 13, 1499. [Google Scholar] [CrossRef]

- Chen, H.-M.; Lee, C.-C.; Jheng, S.-H.; Chen, W.-C.; Lee, B.-Y. A sub-1 ppm/°C precision bandgap reference with adjusted-temperature-curvature compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1308. [Google Scholar] [CrossRef]

- Nagulapalli, R.; Palani, R.K.; Bhagavatula, S. A 24.4 ppm/°C Voltage Mode Bandgap Reference With a 1.05V Supply. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 1088. [Google Scholar] [CrossRef]

- Jize, J.; Jeong, S.; Myers, P.D.; Bang, S.; Shen, J.; Kim, C. A 5.6 ppm/°C temperature coefficient, 87-dB PSRR, sub-1-V voltage reference in 65-nm CMOS exploiting the zero-temperature-coefficient point. IEEE J. Solid-State Circuits 2016, 52, 623–633. [Google Scholar] [CrossRef]

- Quanzhen, D.; Jeongjin, R. A 1.2-V 4.2-ppm°C high-order curvature-compensated CMOS bandgap reference. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 62, 662–670. [Google Scholar] [CrossRef]

- Chen, K.; Petruzzi, L.; Hulfachor, R.; Onabajo, M. A 1.16-V 5.8-to-13.5-ppm/°C Curvature-Compensated CMOS Bandgap Reference Circuit with a Shared Offset-Cancellation Method for Internal Amplifiers. IEEE J. Solid-State Circuits 2021, 56, 267. [Google Scholar] [CrossRef]

- Lee, C.-F.; Chi-Wa, U.; Martins, R.P.; Lam, C.-S. 0.4-V Supply, 12-nW Reverse Bandgap Voltage Reference With Single BJT and Indirect Curvature Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 5040. [Google Scholar] [CrossRef]

- Kim, M.; Cho, S. A Single BJT Bandgap Reference With Frequency Compensation Exploiting Mirror Pole. IEEE J. Solid-State Circuits 2021, 56, 2902. [Google Scholar] [CrossRef]

- Xie, J.; Wu, C.; Wu, J.; Li, J.; Luo, Z.; Sun, Q. A −184 dB PSRR and 2.47 μVrms noise self-biased bandgap reference based on FVF structure. Microelectron. J. 2024, 152, 106388. [Google Scholar] [CrossRef]

- Zheng, Y.; Yan, Z.; Yang, R.; Zhang, B.; Luo, Z.; Li, J. A −122 dB PSRR curvature-compensated bandgap reference with cross-connected NPN. AEU—Int. J. Electron. Commun. 2025, 202, 156005. [Google Scholar] [CrossRef]

- Qiu, H.; Chen, Q.; He, L.; Zheng, B.; Li, J.; Luo, Z. A CMOS voltage reference with low temperature coefficient. AEU—Int. J. Electron. Commun. 2025, 190, 155649. [Google Scholar] [CrossRef]

- Zheng, B.; Chen, Q.; Qiu, H.; He, L.; Li, J.; Luo, Z. A 10.42 ppm/°C CMOS voltage reference with high PSRR. AEU—Int. J. Electron. Commun. 2025, 198, 155837. [Google Scholar] [CrossRef]

- Jung, M.; Min, K.; Son, H.; Ji, Y. A 5-Transistor CMOS Voltage Reference with Double Supply-Regulation. Electronics 2025, 14, 588. [Google Scholar] [CrossRef]

- Chen, Y.; Guo, J. A 42 nA IQ, 1.5–6 V VIN, Self-Regulated CMOS Voltage Reference With −93 dB PSR at 10 Hz for Energy Harvesting Systems. IEEE Trans. Circuits Syst. II Regul. Pap. 2021, 68, 2357. [Google Scholar] [CrossRef]

- Wang, L.; Zhan, C. A 0.7-V 28-nW CMOS Subthreshold Voltage and Current Reference in One Simple Circuit. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 3457. [Google Scholar] [CrossRef]

- Wang, Y.; Zhu, Z.; Yao, J.; Yang, Y. A 0.45-V, 14.6-nW CMOS Subthreshold Voltage Reference With No Resistors and No BJTs. IEEE Trans. Circuits Syst. II 2015, 62, 621. [Google Scholar] [CrossRef]

- Zhang, H.; Liu, X.; Zhang, J.; Zhang, H.; Li, J.; Zhang, R. A Nano-Watt MOS-Only Voltage Reference With High-Slope PTAT Voltage Generators. IEEE Trans. Circuits Syst. II Regul. Pap. 2018, 65, 1. [Google Scholar] [CrossRef]

- Liao, X.; Zhang, Y.; Zhang, S.; Liu, L. A 3.0 μVrms, 2.4 ppm/°C BGR With Feedback Coefficient Enhancement and Bowl-Shaped Curvature Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 2424–2433. [Google Scholar] [CrossRef]

- Chen, Q.; Gong, Y.; Tu, R.; Xie, J.; Dai, H.; Chen, Y.; Wei, R.; Li, J.; Luo, Z. A 1.2-V 0.959-ppm/°C multi-section curvature-compensated bandgap voltage reference with trimming. Microelectron. J. 2023, 136, 105769. [Google Scholar] [CrossRef]

- Zhu, Z.; Hu, J.; Wang, Y. A 0.45 V, Nano-Watt 0.033% Line Sensitivity MOSFET-Only Sub-Threshold Voltage Reference with no Amplifiers. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1370–1380. [Google Scholar] [CrossRef]

- Yan, Z.; Zhang, B.; Yang, R.; Zheng, Y.; Li, J.; Luo, Z.; Sun, Q. A 1.2-V compact bandgap reference with curvature compensation technology. IEICE Electron. Express 2025, 22, 20250028. [Google Scholar] [CrossRef]

- Lee, I.; Sylvester, D.; Blaauw, D. A Subthreshold Voltage Reference With Scalable Output Voltage for Low-Power IoT Systems. IEEE J. Solid-State Circuits 2017, 52, 1443–1449. [Google Scholar] [CrossRef]

- Alhassan, N.; Zhou, Z.; Sánchez-Sinencio, E. An All-MOSFET Voltage Reference With −50-dB PSR at 80 MHz for Low-Power SoC Design. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 892–896. [Google Scholar] [CrossRef]

- Cheng, T.; Rao, H.; Wei, J. A 8.83 ppm/°C temperature coefficient, 75 dB PSRR subthreshold CMOS voltage reference with piecewise curvature compensation. Integration 2024, 97, 102209. [Google Scholar] [CrossRef]

- Duan, J.; Zhu, Z.; Deng, J.; Xu, W.; Wei, B. A Novel 0.8-V 79-nW CMOS-Only Voltage Reference with −55-dB PSRR @ 100 Hz. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 849. [Google Scholar] [CrossRef]

| Process Corner | TC Before Trimming (ppm/°C) | TC After Trimming (ppm/°C) |

|---|---|---|

| TT | 1.06 | 1.06 |

| FF | 17.67 | 7.46 |

| SS | 19.11 | 7.41 |

| FS | 13.51 | 3.42 |

| SF | 13.34 | 4.94 |

| Specification | [10] JSSC’21 | [2] TCAS-II’22 | [7] TCAS-II’21 | [14] AEU’25 | [25] IEICE’25 | This Work |

|---|---|---|---|---|---|---|

| Technology (nm) | 130 | 350 | 45 | 180 | 180 | 180 |

| Supply Voltage (V) | 3.3 | 2 | 1 | 3.3 | 3.3 | 1.8 |

| Temp. Range (°C) | –150 | –125 | –125 | –125 | –125 | –125 |

| (V) | 1.16 | 1.22 | 0.500 | 1.13 | 1.22 | 1.20 |

| Line Regulation (%) | 0.03 | 0.018 | 0.15 | 0.027 | 0.048 | 0.36 |

| Avg. TC (ppm/°C) | 8.75 | 12.3 | 22.4 | 7.7 | 7.86 | 4.86 |

| Power (μW) | 396 | 46 | 7.56 | 183.1 | 151.8 | 50.4 |

| Active Area (mm2) | 0.08 | 0.16 | 0.079 | 0.019 | 0.01 | 0.008 |

| PSRR (dB) | −82 @10 Hz | −82.46 @100 Hz | −60 @10 kHz | −85 @100 kHz | −65 @1 kHz | −52.3 @1 kHz |

| Trimming | NO | YES | NO | YES | NO | YES |

| Sim or Meas | Meas | Meas | Meas | Sim | Sim | Sim |

| FoM °C3/(W·mm2) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.

Share and Cite

Yang, R.; Zhang, B.; Yan, Z.; Zheng, Y.; Li, J.; Luo, Z. A 1.06 ppm/°C Compact CMOS Voltage Reference. Electronics 2026, 15, 268. https://doi.org/10.3390/electronics15020268

Yang R, Zhang B, Yan Z, Zheng Y, Li J, Luo Z. A 1.06 ppm/°C Compact CMOS Voltage Reference. Electronics. 2026; 15(2):268. https://doi.org/10.3390/electronics15020268

Chicago/Turabian StyleYang, Rui, Binhan Zhang, Zhenjie Yan, Yi Zheng, Jinghu Li, and Zhicong Luo. 2026. "A 1.06 ppm/°C Compact CMOS Voltage Reference" Electronics 15, no. 2: 268. https://doi.org/10.3390/electronics15020268

APA StyleYang, R., Zhang, B., Yan, Z., Zheng, Y., Li, J., & Luo, Z. (2026). A 1.06 ppm/°C Compact CMOS Voltage Reference. Electronics, 15(2), 268. https://doi.org/10.3390/electronics15020268