Author Contributions

Conceptualization, S.D., A.M. and T.N.; methodology, S.D. and A.M.; validation, S.D. and A.M.; formal analysis, S.D.; investigation, S.D.; writing—original draft preparation, S.D.; writing—review and editing, A.M., D.T., V.F.P. and T.N.; visualization, S.D.; supervision, A.M., D.T., V.F.P. and T.N. All authors have read and agreed to the published version of the manuscript.

Figure 1.

Block diagram of a typical receiver (RX) chain architecture.

Figure 1.

Block diagram of a typical receiver (RX) chain architecture.

Figure 2.

Schematic of the single-ended cascode LNA.

Figure 2.

Schematic of the single-ended cascode LNA.

Figure 3.

Equivalent output load network including , its parallel resistance, and matching capacitor.

Figure 3.

Equivalent output load network including , its parallel resistance, and matching capacitor.

Figure 4.

Schematic of the proposed differential single-stage LNA.

Figure 4.

Schematic of the proposed differential single-stage LNA.

Figure 5.

Smith Chart Visualization for impedance tuning of the proposed differential LNA.

Figure 5.

Smith Chart Visualization for impedance tuning of the proposed differential LNA.

Figure 6.

Small-signal equivalent circuit of the differential LNA input stage.

Figure 6.

Small-signal equivalent circuit of the differential LNA input stage.

Figure 7.

, and as functions of the neutralization capacitance .

Figure 7.

, and as functions of the neutralization capacitance .

Figure 8.

Layout of the inductor showing the PCELL-based model and surrounding interconnects.

Figure 8.

Layout of the inductor showing the PCELL-based model and surrounding interconnects.

Figure 9.

Inductance and Quality Factor comparison for standard RC vs. EM extracted netlists.

Figure 9.

Inductance and Quality Factor comparison for standard RC vs. EM extracted netlists.

Figure 10.

On-chip balun layout and its coupling coefficient vs. frequency.

Figure 10.

On-chip balun layout and its coupling coefficient vs. frequency.

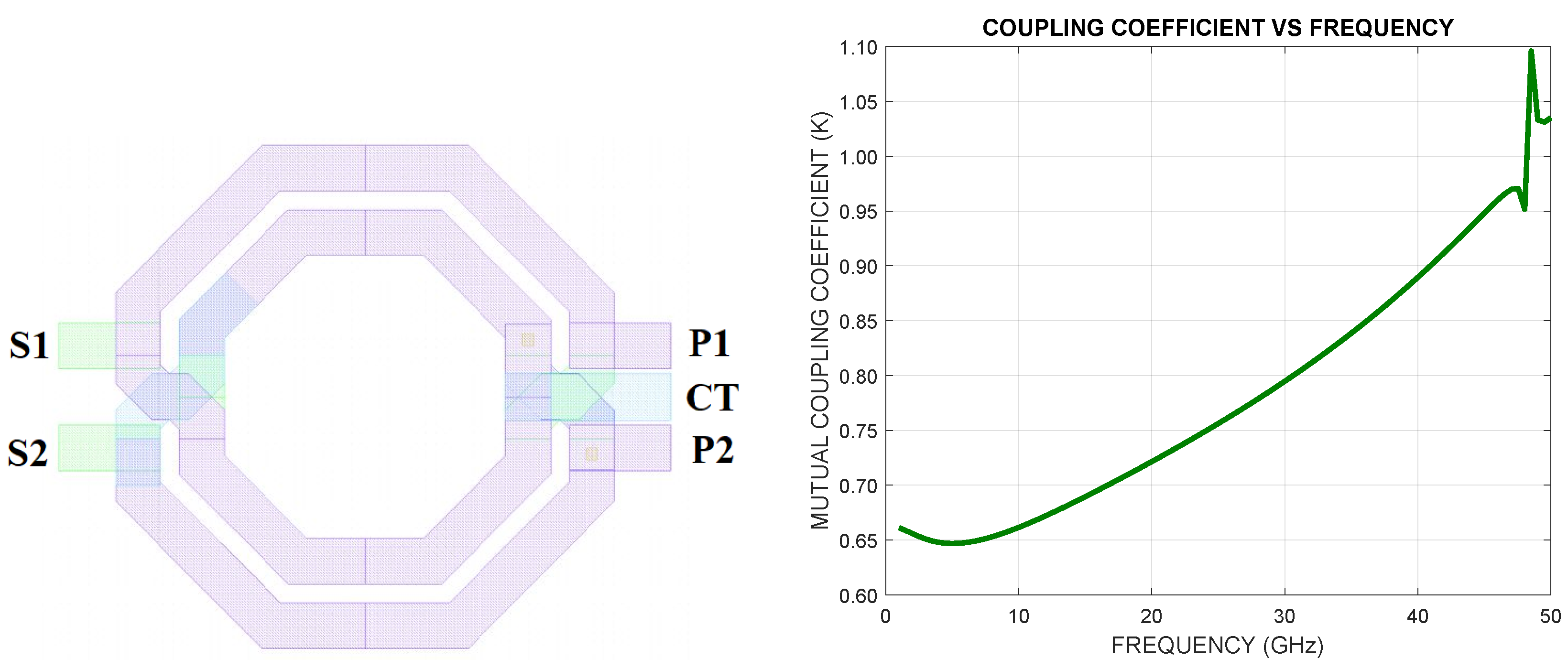

Figure 11.

On-chip nested inductor structure and its coupling coefficient vs. frequency.

Figure 11.

On-chip nested inductor structure and its coupling coefficient vs. frequency.

Figure 12.

Proposed RF/mmWave LNA Design methodology.

Figure 12.

Proposed RF/mmWave LNA Design methodology.

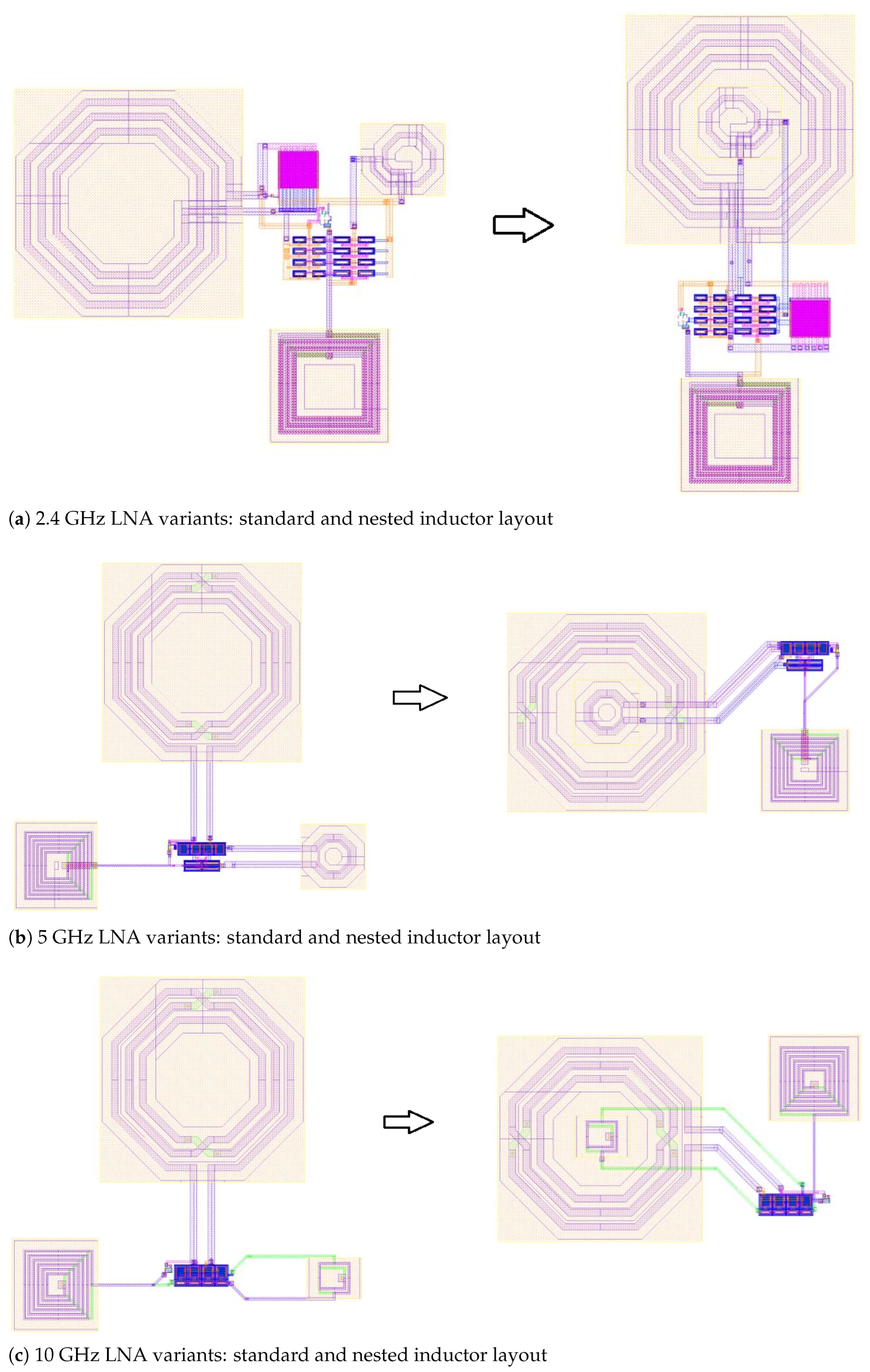

Figure 13.

Layout transition from standard to nested inductor designs for LNAs targeting (a) 2.4 GHz, (b) 5 GHz, (c) 10 GHZ.

Figure 13.

Layout transition from standard to nested inductor designs for LNAs targeting (a) 2.4 GHz, (b) 5 GHz, (c) 10 GHZ.

Figure 14.

Comparison of inductance and quality factor before and after nesting, for and across different nested inductor implementations: (a) vs. frequency, (b) Q of vs. frequency, (c) vs. frequency, (d) Q of vs. frequency.

Figure 14.

Comparison of inductance and quality factor before and after nesting, for and across different nested inductor implementations: (a) vs. frequency, (b) Q of vs. frequency, (c) vs. frequency, (d) Q of vs. frequency.

Figure 15.

Optimized layouts of the nested single-ended LNAs for three target frequencies: (a) 2.4 GHz, (b) 5 GHz and (c) 10 GHz.

Figure 15.

Optimized layouts of the nested single-ended LNAs for three target frequencies: (a) 2.4 GHz, (b) 5 GHz and (c) 10 GHz.

Figure 16.

Smith Chart representations of input/output impedance for the three LNA designs at frequencies: (a) 2.4 GHz, (b) 5 GHz, and (c) 10 GHz.

Figure 16.

Smith Chart representations of input/output impedance for the three LNA designs at frequencies: (a) 2.4 GHz, (b) 5 GHz, and (c) 10 GHz.

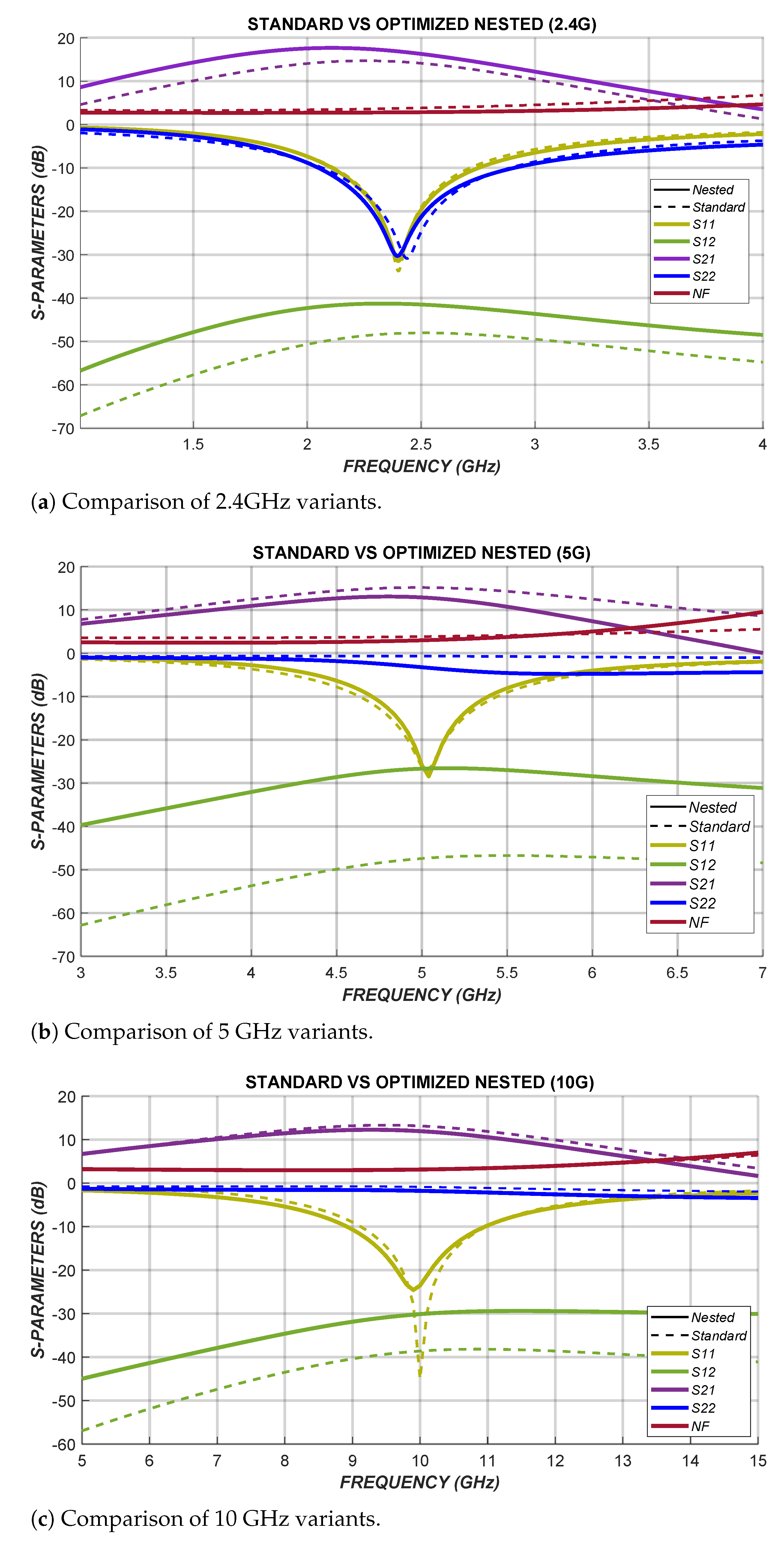

Figure 17.

Simulated performance evaluation of the standard and optimized nested LNAs at (a) 2.4 GHz, (b) 5 GHz, (c) 10 GHz.

Figure 17.

Simulated performance evaluation of the standard and optimized nested LNAs at (a) 2.4 GHz, (b) 5 GHz, (c) 10 GHz.

Figure 18.

Simulated evaluation of stability factor () of the optimized nested LNA designs.

Figure 18.

Simulated evaluation of stability factor () of the optimized nested LNA designs.

Figure 19.

Frequency scalability of nested inductor structure: (a) layout area comparison and (b) mutual coupling coefficient.

Figure 19.

Frequency scalability of nested inductor structure: (a) layout area comparison and (b) mutual coupling coefficient.

Figure 20.

Layout of stacked and interleaved balun topologies.

Figure 20.

Layout of stacked and interleaved balun topologies.

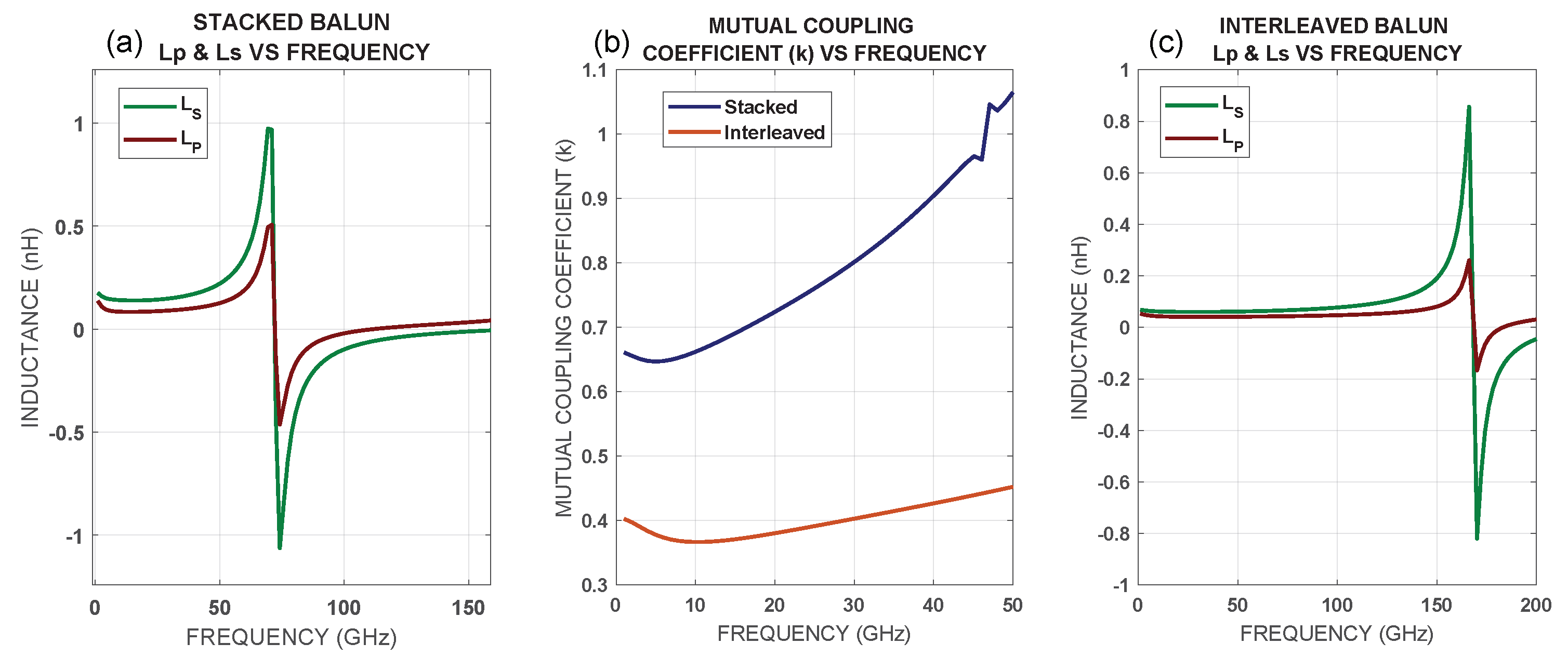

Figure 21.

Extracted parameters of stacked and interleaved baluns: (a) stacked inductances , (b) coupling coefficient k, (c) interleaved inductances .

Figure 21.

Extracted parameters of stacked and interleaved baluns: (a) stacked inductances , (b) coupling coefficient k, (c) interleaved inductances .

Figure 22.

Layout Implementation of the 33 GHz differential LNA.

Figure 22.

Layout Implementation of the 33 GHz differential LNA.

Figure 23.

Smith chart of input impedance and output admittance for the 33 GHz LNA.

Figure 23.

Smith chart of input impedance and output admittance for the 33 GHz LNA.

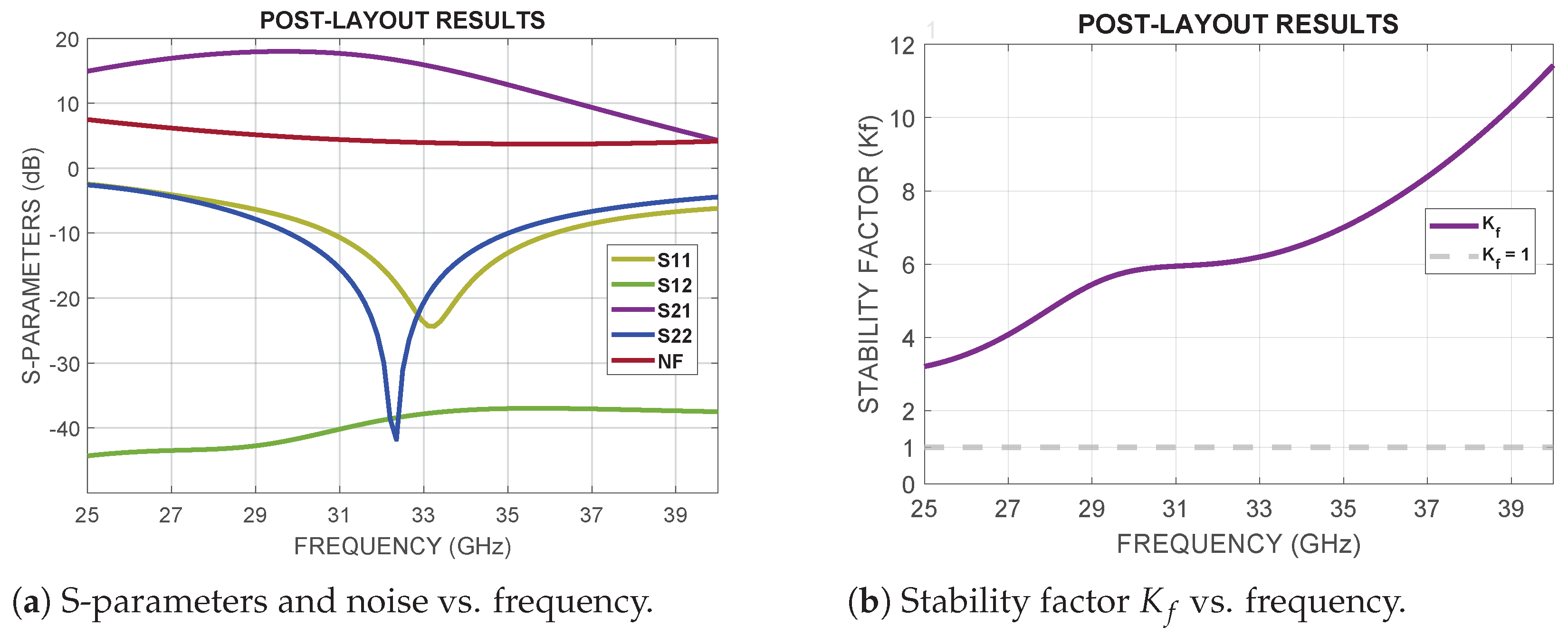

Figure 24.

Post-layout simulation results of the 33 GHz LNA: (a) S-parameters, (b) stability factor.

Figure 24.

Post-layout simulation results of the 33 GHz LNA: (a) S-parameters, (b) stability factor.

Table 1.

Design parameters for the single-ended LNAs across different operating frequencies.

Table 1.

Design parameters for the single-ended LNAs across different operating frequencies.

| Design Parameter | 2.4 GHz | 5 GHz | 10 GHz |

|---|

| 0.8 V | 0.8 V | 0.8 V |

| 400/0.07 μm | 80/0.07 μm | 60/0.07 μm |

| 400/0.04 μm | 400/0.07 μm | 400/0.07 μm |

| 16/0.07 μm | 20/0.07 μm | 5/0.02 μm |

| 1.4 nH | 1.1 nH | 0.9 nH |

| 78 pH | 33 pH | 89 pH |

| 9.6 nH | 7.5 nH | 2.9 nH |

| 210 | 65 | 60 |

| 5.1 k | 1.3 k | 3.6 k |

| 70 | — | — |

| 2.4 pF | — | — |

Table 2.

Simulated performance metrics of the single-ended LNAs before and after nesting.

Table 2.

Simulated performance metrics of the single-ended LNAs before and after nesting.

| Performance Metric | 2.4 GHz | 5 GHz | 10 GHz |

|---|

| Standard | Nested | Standard | Nested | Standard | Nested |

|---|

| Silicon Footprint (mm2) | 0.063 | 0.045 | 0.045 | 0.024 | 0.035 | 0.022 |

| (dB) | −33.8 | −19.5 | −24.7 | −9.0 | −45.0 | −11.5 |

| (dB) | 14.5 | 13.5 | 15.2 | 13.4 | 13.1 | 10.9 |

| (dB) | −48.1 | −38.2 | −47.4 | −25.4 | −38.6 | −26.6 |

| (dB) | −27.4 | −17.0 | −0.7 | −0.5 | −0.9 | −2.3 |

| Noise Figure (dB) | 3.7 | 3.0 | 3.8 | 3.3 | 3.1 | 2.9 |

| IP1 (dBm) | −15.2 | −13.0 | −16.0 | −16.9 | −15.4 | −11.6 |

| IP3 (dBm) | −6.2 | −3.6 | −9.0 | −10.3 | −7.5 | −3.7 |

| Power Dissipation (mW) | 9.8 | 10.0 | 7.3 | 5.1 | 5.8 | 6.2 |

Table 3.

Initial and re-tuned EM simulated values of design parameters for each operating frequency.

Table 3.

Initial and re-tuned EM simulated values of design parameters for each operating frequency.

| Design Parameter | 2.4 GHz | 5 GHz | 10 GHz |

|---|

| Initial | Re-Tuned | Initial | Re-Tuned | Initial | Re-Tuned |

|---|

| (pH) | 78 | 49 | 33 | 64 | 89 | 21 |

| (nH) | 9.6 | 8.5 | 7.5 | 17.0 | 2.9 | 2.8 |

| (k) | 5.1 | — | 1.3 | — | 3.6 | 740 |

Table 4.

Final simulated performance metrics of the proposed nested single-ended LNAs.

Table 4.

Final simulated performance metrics of the proposed nested single-ended LNAs.

| Performance Metric | 2.4 GHz | 5 GHz | 10 GHz |

|---|

| Silicon Footprint (mm2) | 0.047 | 0.025 | 0.021 |

| (dB) | −31.5 | −23.8 | −23.4 |

| (dB) | 16.9 | 12.9 | 11.9 |

| (dB) | −41.3 | −26.5 | −29.9 |

| (dB) | −30.2 | −3.2 | −1.2 |

| Noise Figure (dB) | 2.8 | 2.9 | 3.1 |

| IP1 (dBm) | −14.5 | −16.6 | −13.6 |

| IP3 (dBm) | −6.5 | −9.7 | −5.9 |

| Power Dissipation (mW) | 13.2 | 6.3 | 5.4 |

Table 5.

Percentage of total layout area occupied by inductors in the standard LNA designs and the corresponding area reduction due to nesting.

Table 5.

Percentage of total layout area occupied by inductors in the standard LNA designs and the corresponding area reduction due to nesting.

| Frequency | Inductor Area (%) | Area Reduction (%) |

|---|

| 2.4 GHz | 48.1 | 25.4 |

| 5 GHz | 43.0 | 44.4 |

| 10 GHz | 41.5 | 40.0 |

Table 6.

Final design parameters for the 33 GHz differential LNA.

Table 6.

Final design parameters for the 33 GHz differential LNA.

| Design Parameter | Value (Unit) |

|---|

| 0.8 V |

| 0.45 V |

| 180/0.02 μm |

| 180/0.02 μm |

| 360/0.02 μm |

| 360/0.02 μm |

| 70 fF |

| 90 fF |

| 45 fF |

| 160 fF |

| R | 125 |

| Inner Diameter of Input Balun | 26 μm |

| Inner Diameter of Output Balun | 60 μm |

Table 7.

Post-layout simulated performance metrics of the proposed 33 GHz differential LNA.

Table 7.

Post-layout simulated performance metrics of the proposed 33 GHz differential LNA.

| Performance Metric | 33 GHz Differential LNA |

|---|

| (dB) | −23.7 |

| (dB) | 16.0 |

| (dB) | −37.8 |

| (dB) | −20.7 |

| Noise Figure (dB) | 3.9 |

| IP1 (dBm) | −26.9 |

| IP3 (dBm) | −13.2 |

| Power Dissipation (mW) | 64.4 |

| Silicon Footprint (mm2) | 0.047 |

Table 8.

Comparison with State of the Art for the Proposed LNAs.

Table 8.

Comparison with State of the Art for the Proposed LNAs.

| Metric | [45] | This Work | [9] | This Work | [46] | This Work | [47] | This Work |

|---|

| Results | Meas | Sim | Sim | Sim | Meas | Sim | Meas | Sim |

| Tech. Node | 22 nm | 22 nm | 65 nm | 22 nm | 65 nm | 22 nm | 22 nm | 22 nm |

| Vdd (V) | 1 | 0.8 | 1.2 | 0.8 | 1 | 0.8 | 1.6 | 0.8 |

| Freq. (GHz) | 2.1–5.2 | 2.4 | 4.0–6.5 | 5.0 | 8–12.2 | 10.0 | 28/38 | 33.0 |

| (dB) | 12.7–15.7 | 16.9 | 15.6 | 12.9 | 28.5 | 11.9 | 22.4 | 16.0 |

| NF (dB) | 1.5–2 | 2.8 | 2.7 | 2.9 | 1.61–2.17 | 3.1 | 3.6–4.9 | 3.9 |

| Power (mW) | 16 | 13.2 | 22 | 6.3 | 22 | 5.4 | 13.6 | 64.4 |

| IP3 (dBm) | −6 | −6.5 | 2.5 | −9.7 | −19 | −5.9 | −10.3 | −13.2 |

| Area (mm2) | 0.380 | 0.047 | 0.21 | 0.025 | 0.187 | 0.021 | 0.310 | 0.047 |

| 8.44 | 16.2 | 34.7 | 46.2 | 1.26 | 259.5 | 11.93 | 5.72 |