Design and Implementation of an L-Band 400 W Continuous-Wave GaN Power Amplifier

Abstract

1. Introduction

2. Circuit Design

2.1. GaN HEMT Selection

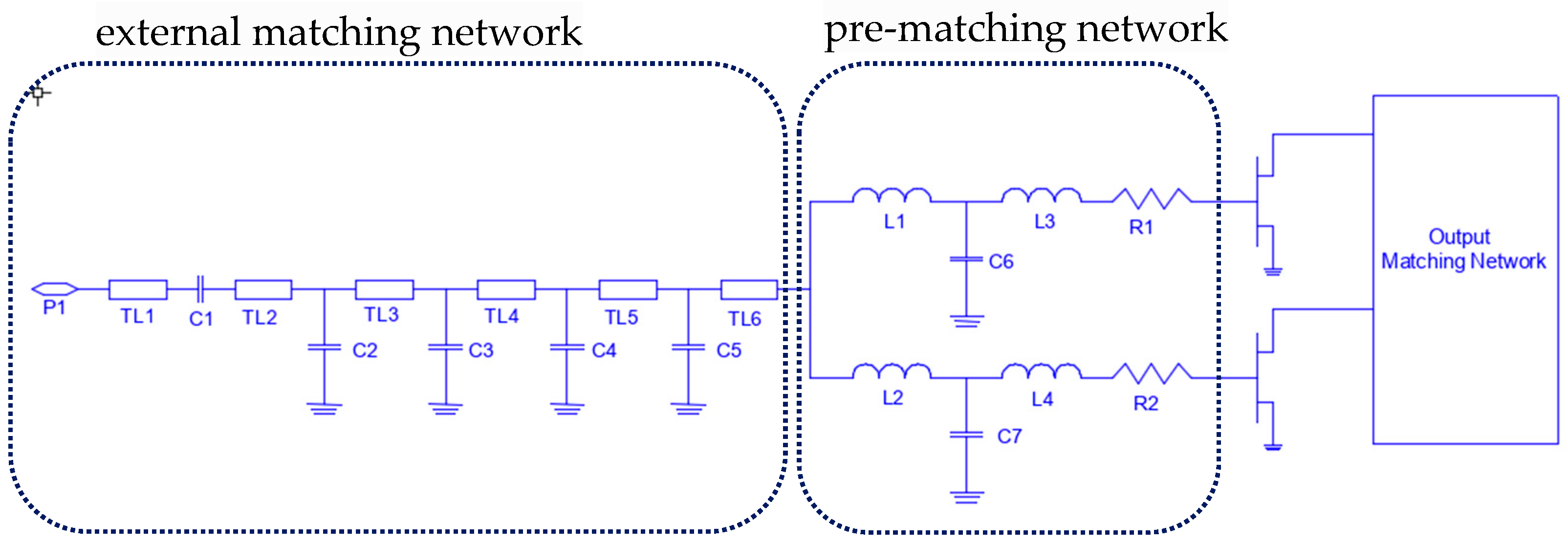

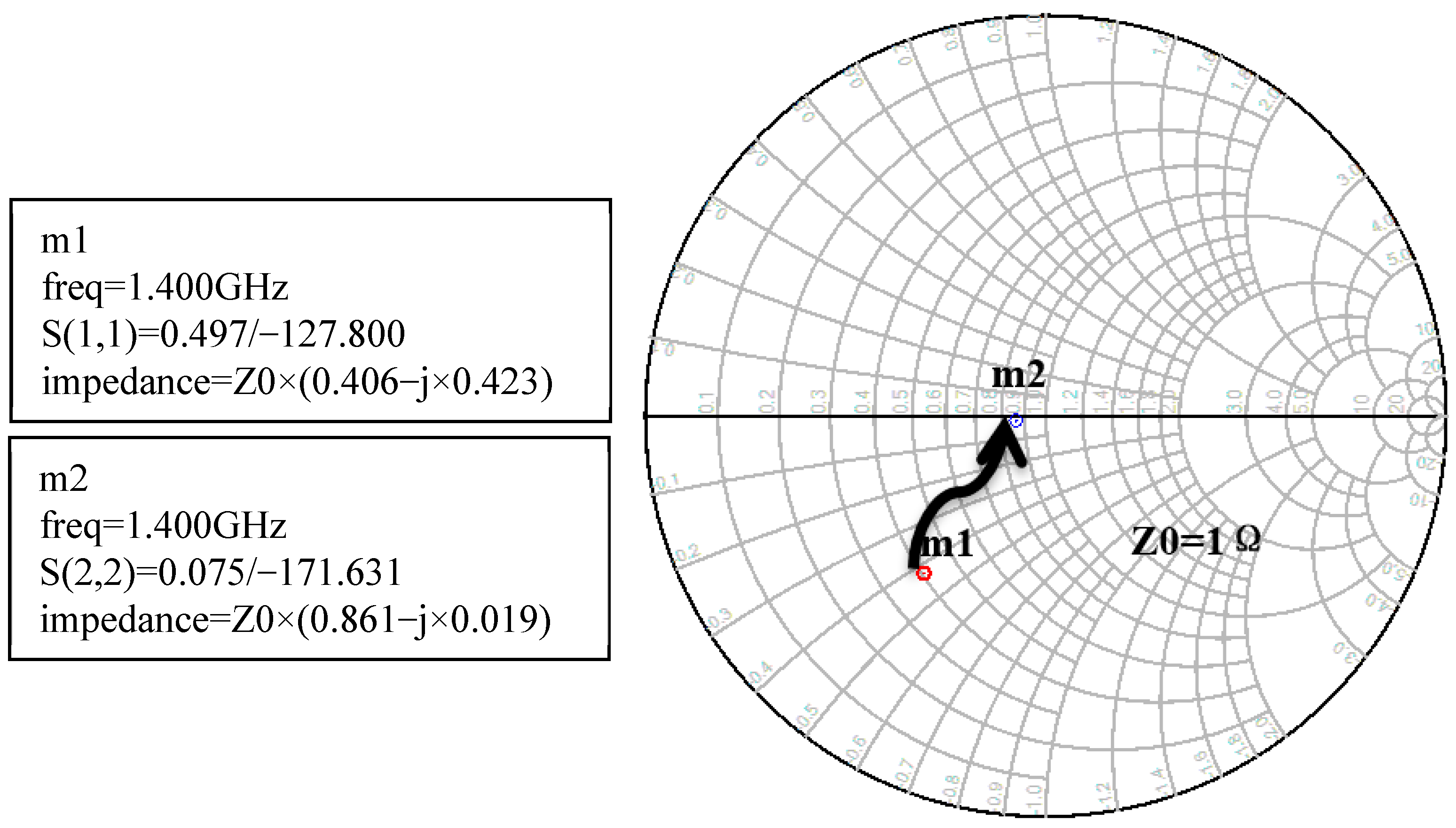

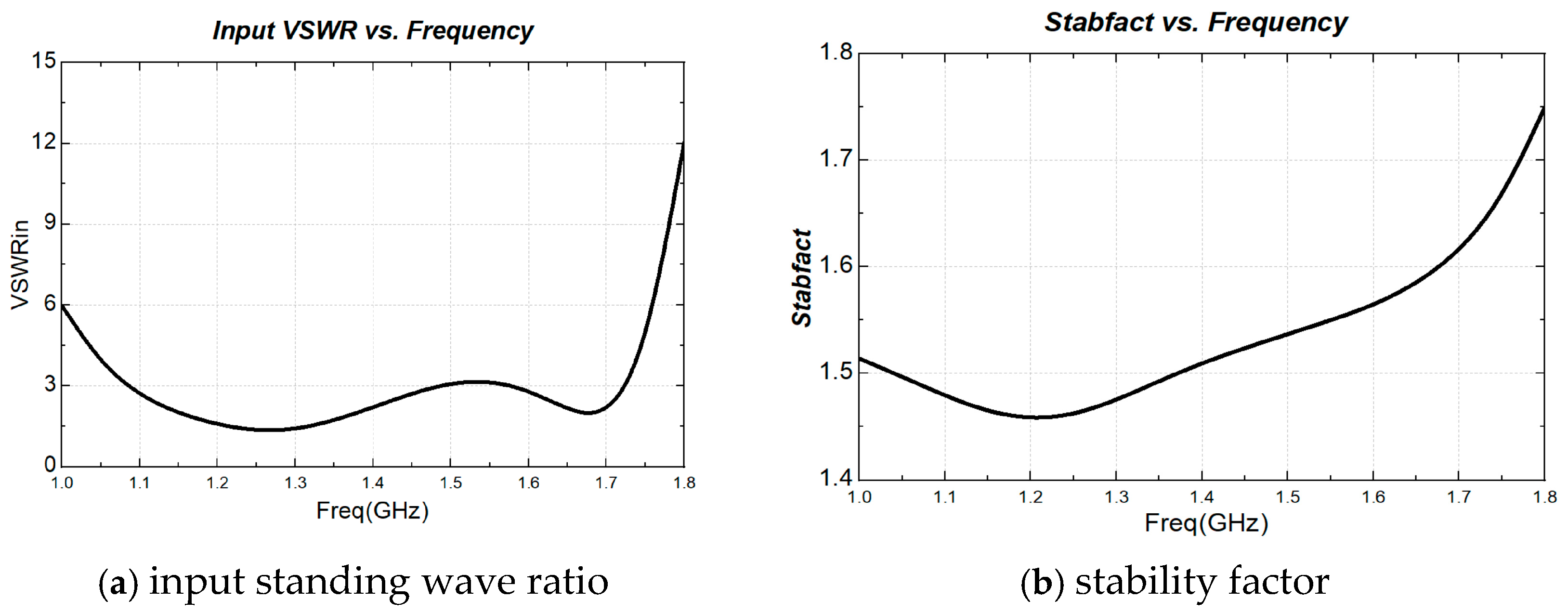

2.2. Input Matching Circuit Design

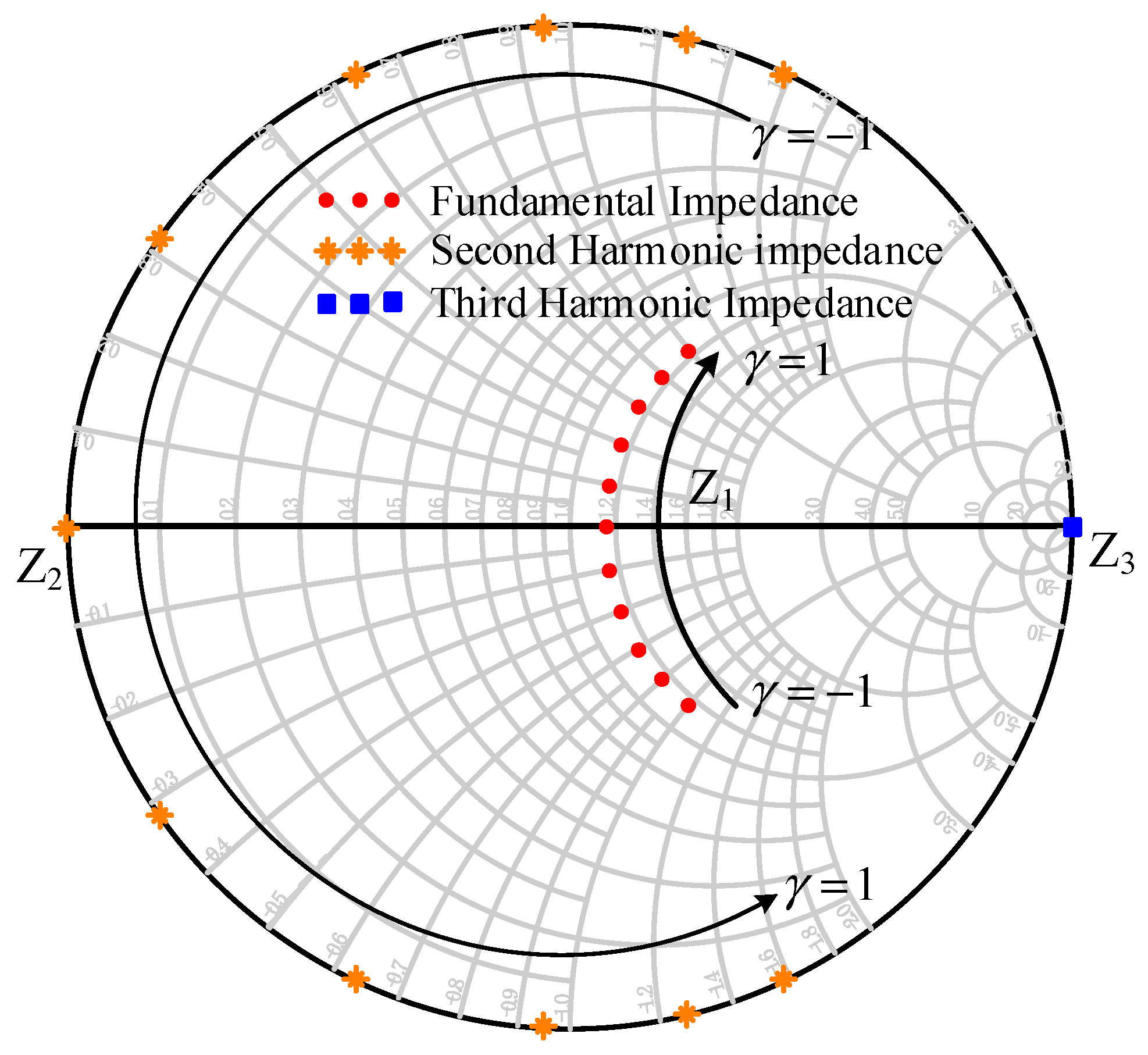

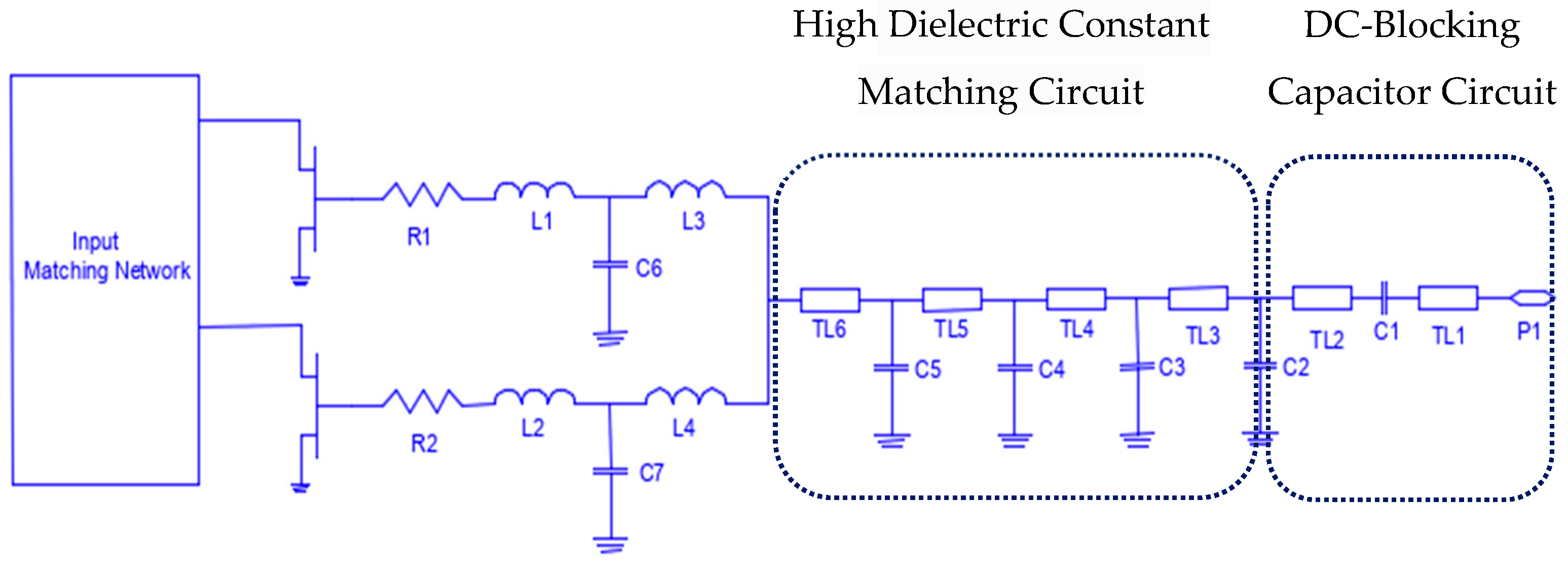

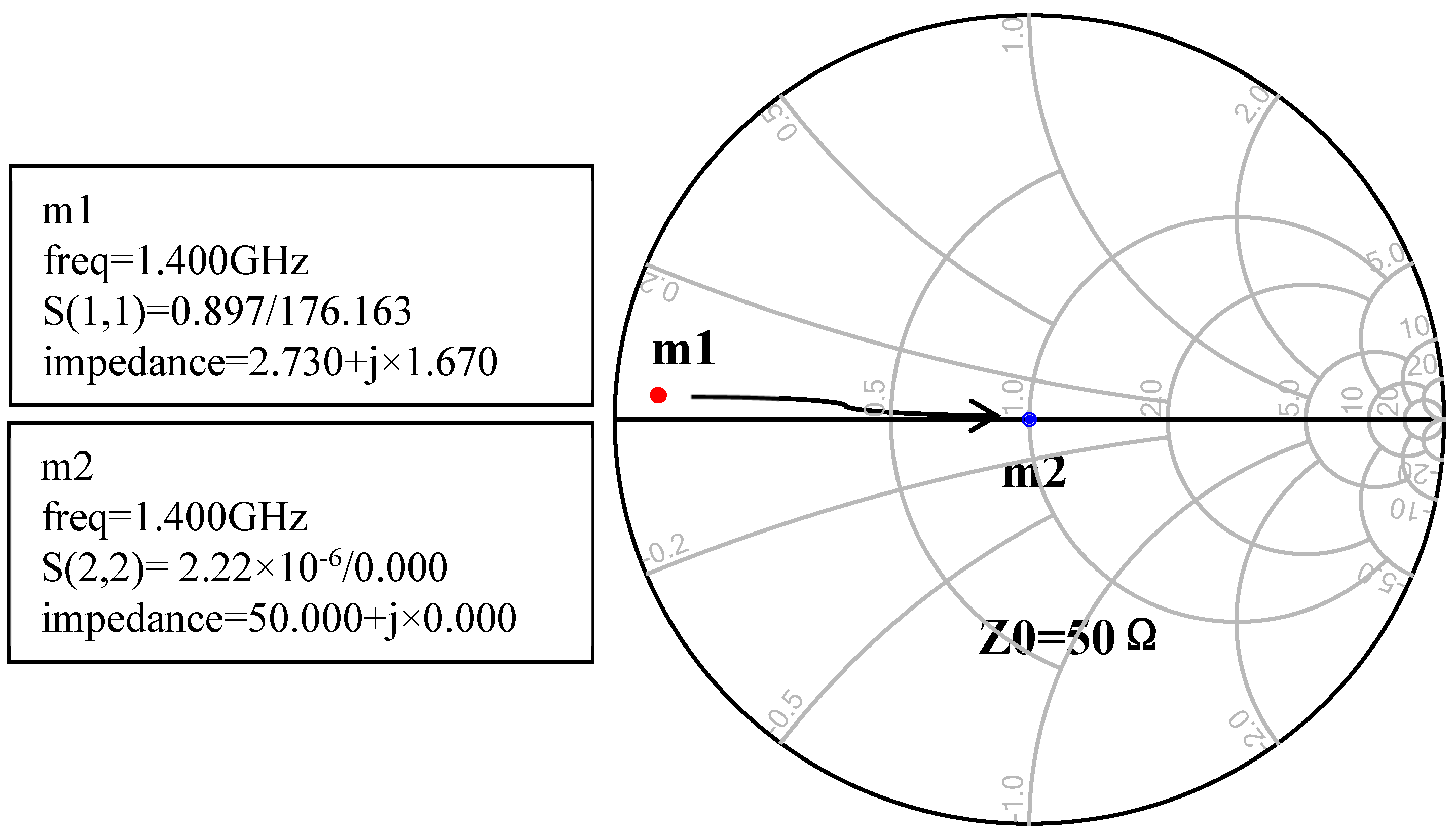

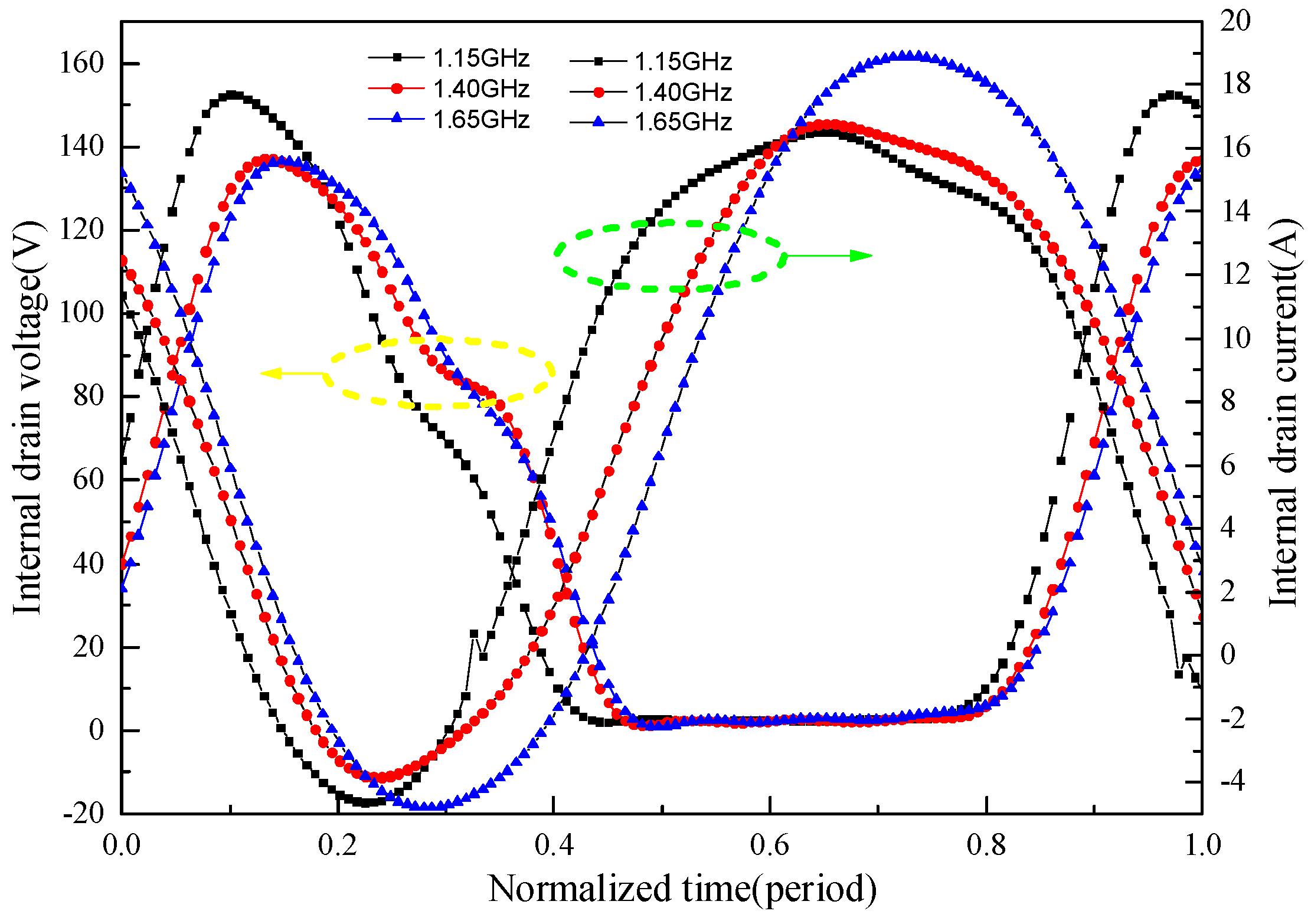

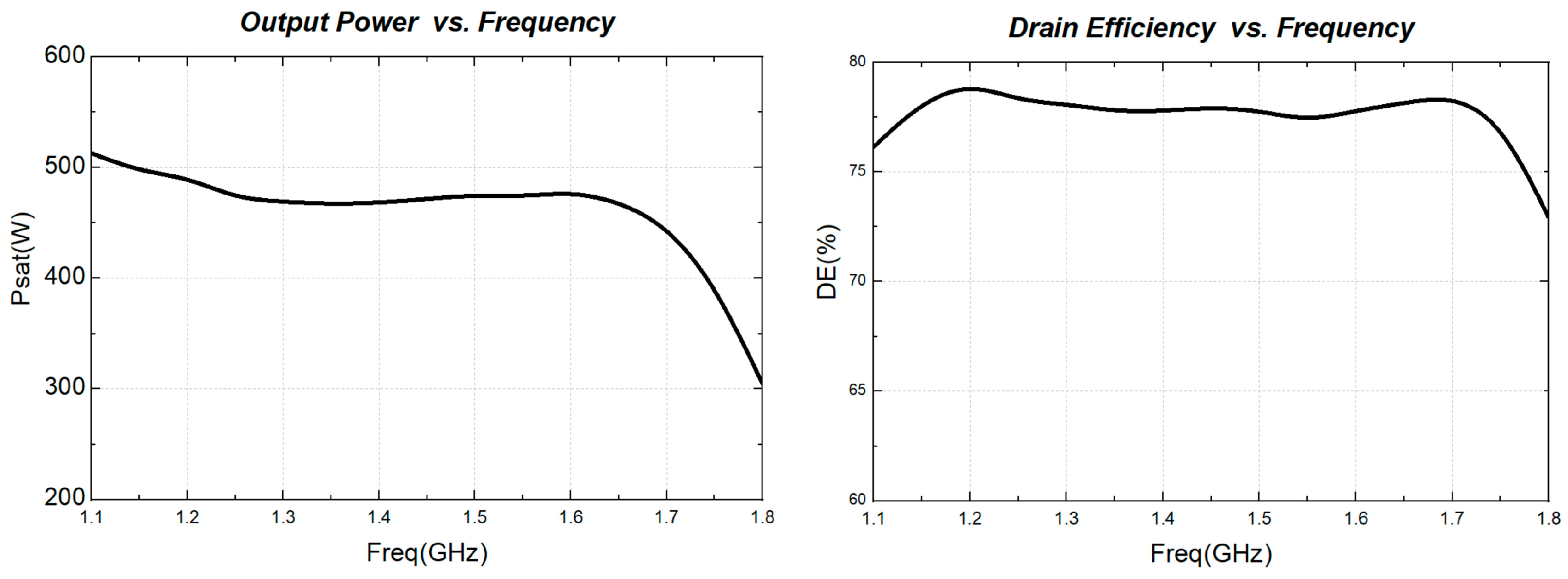

2.3. Output-Matching Circuit Design

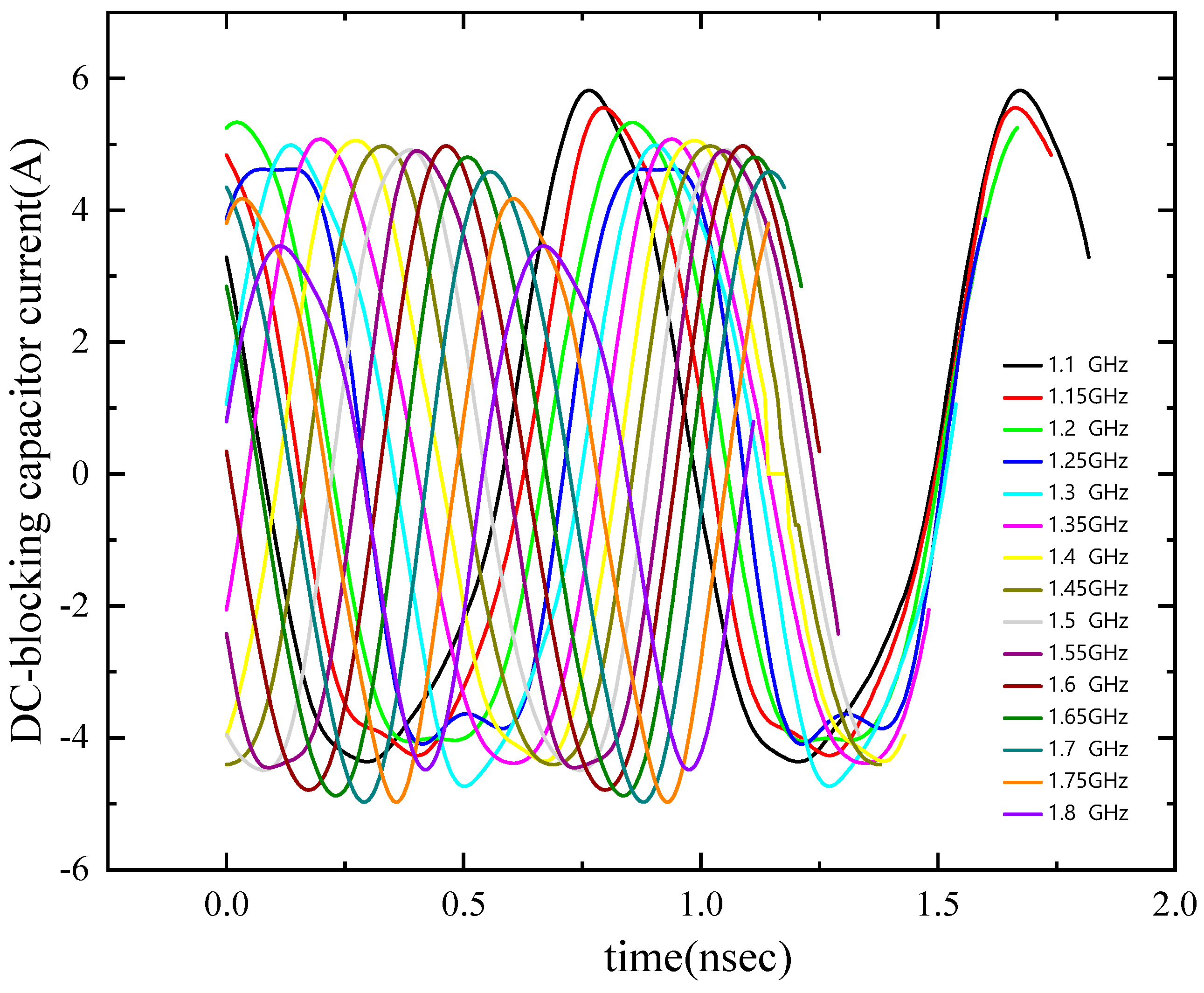

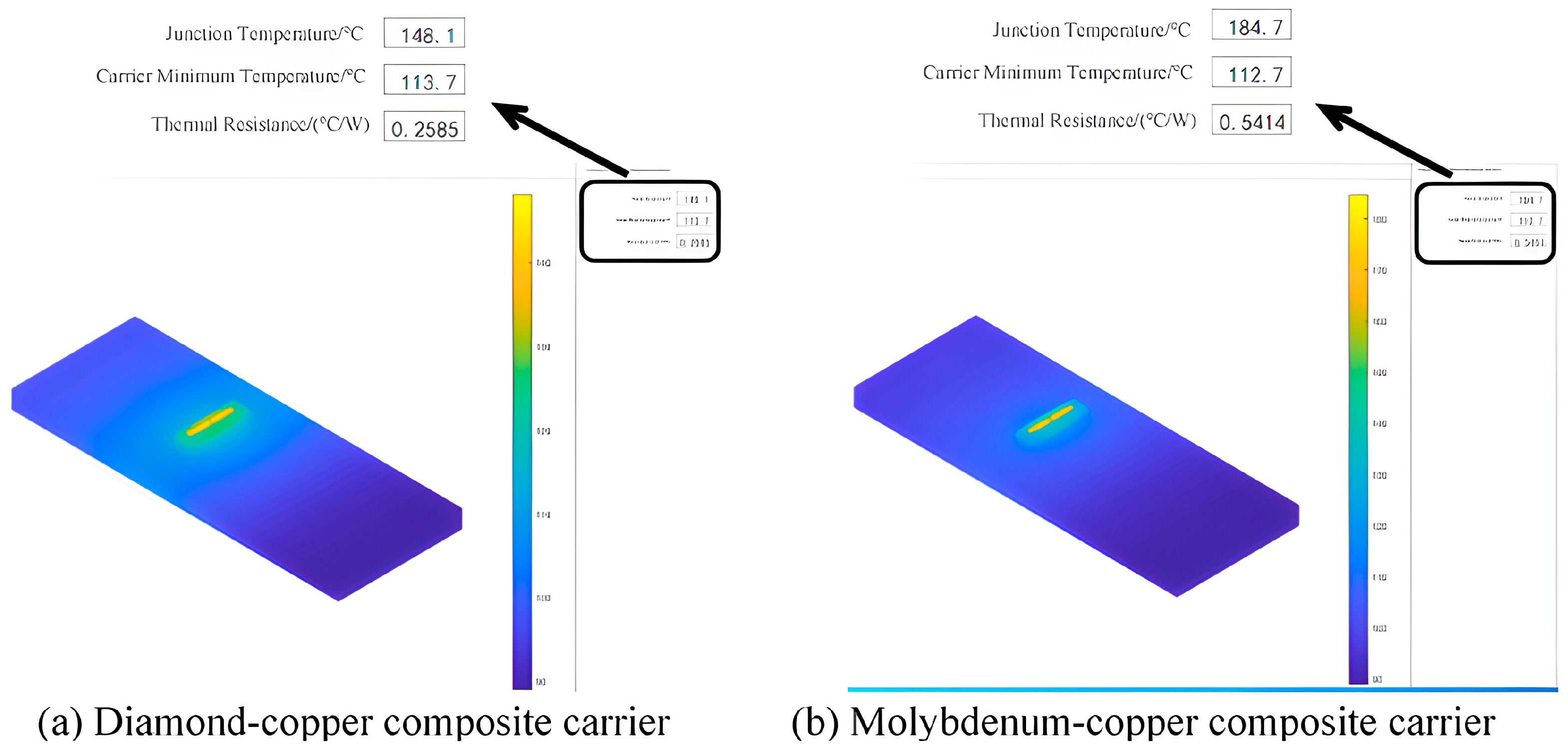

2.4. Reliability Design and Evaluation

3. Fabrication and Test Analysis of Power Amplifiers

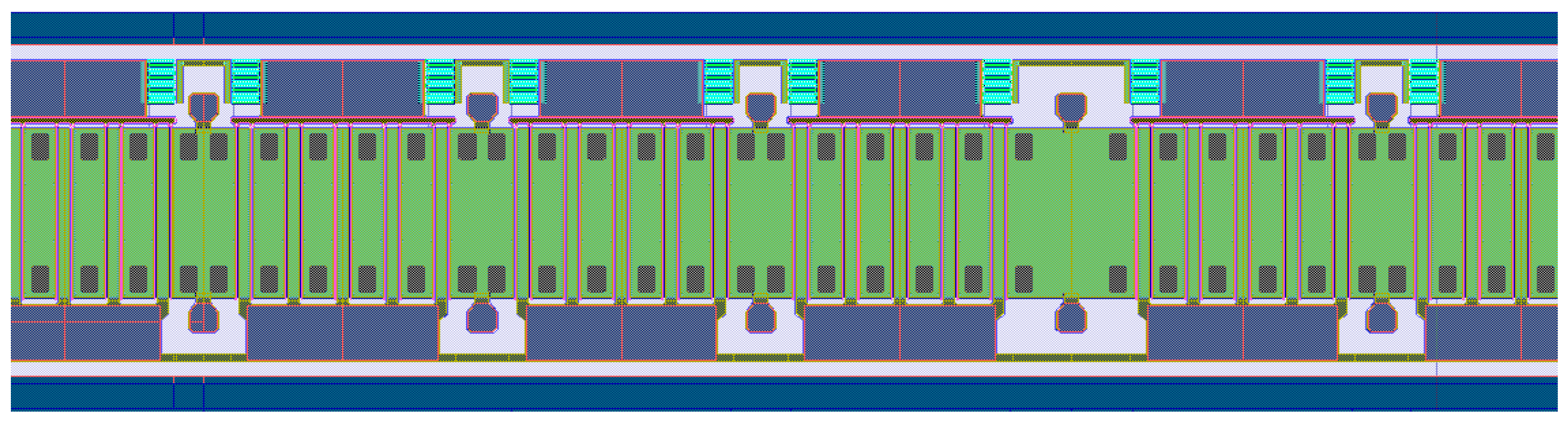

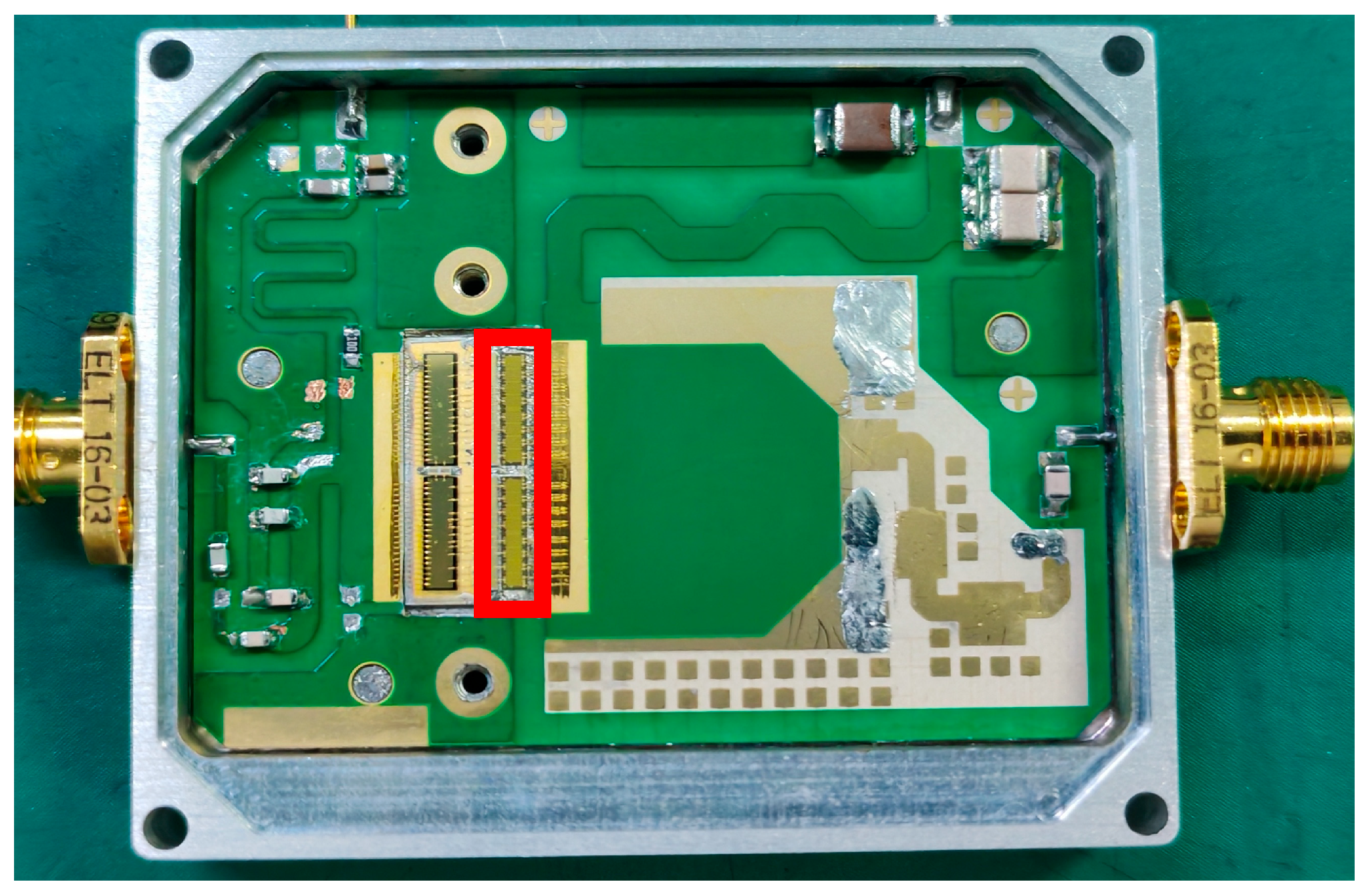

3.1. Fabrication of Power Amplifiers

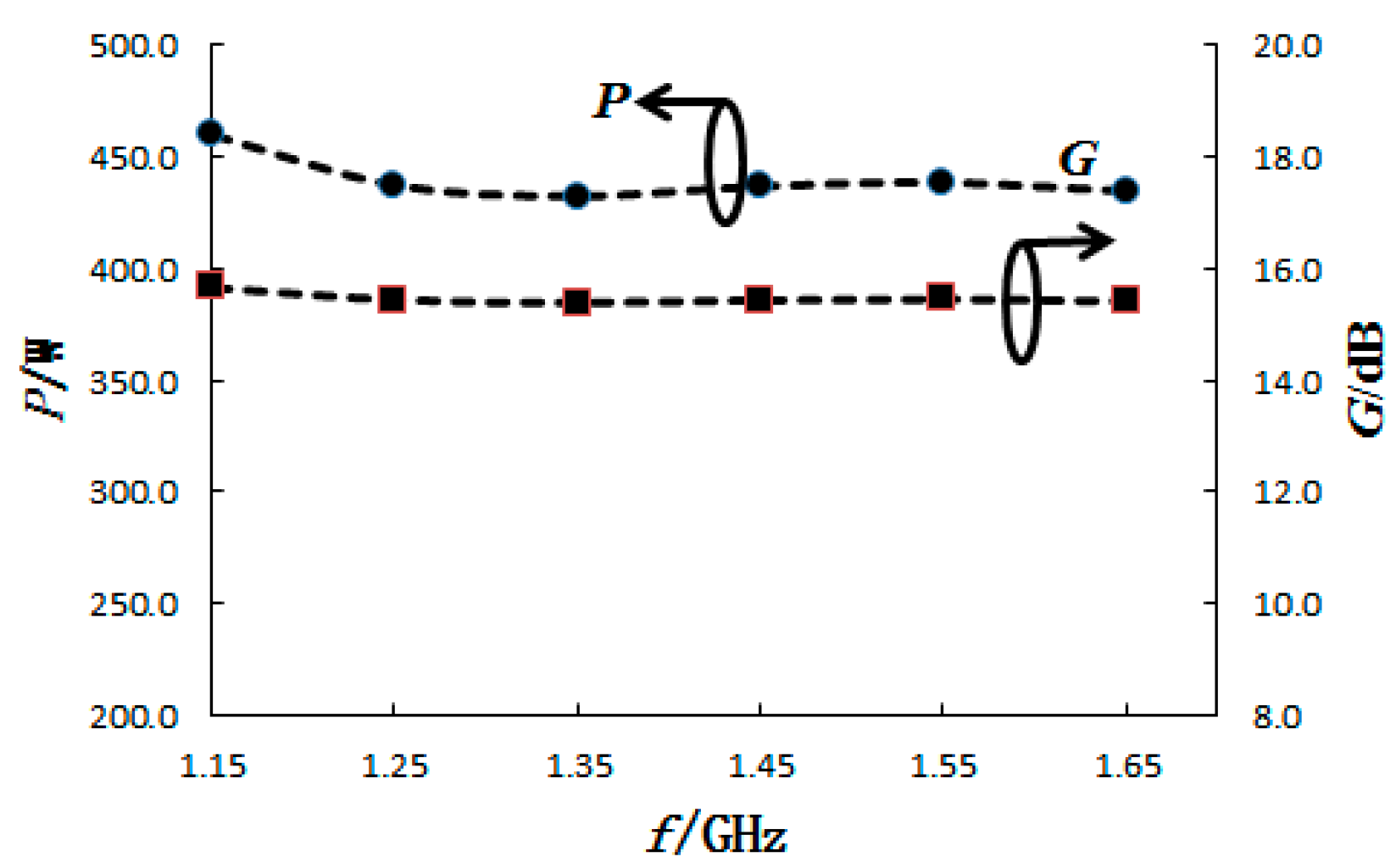

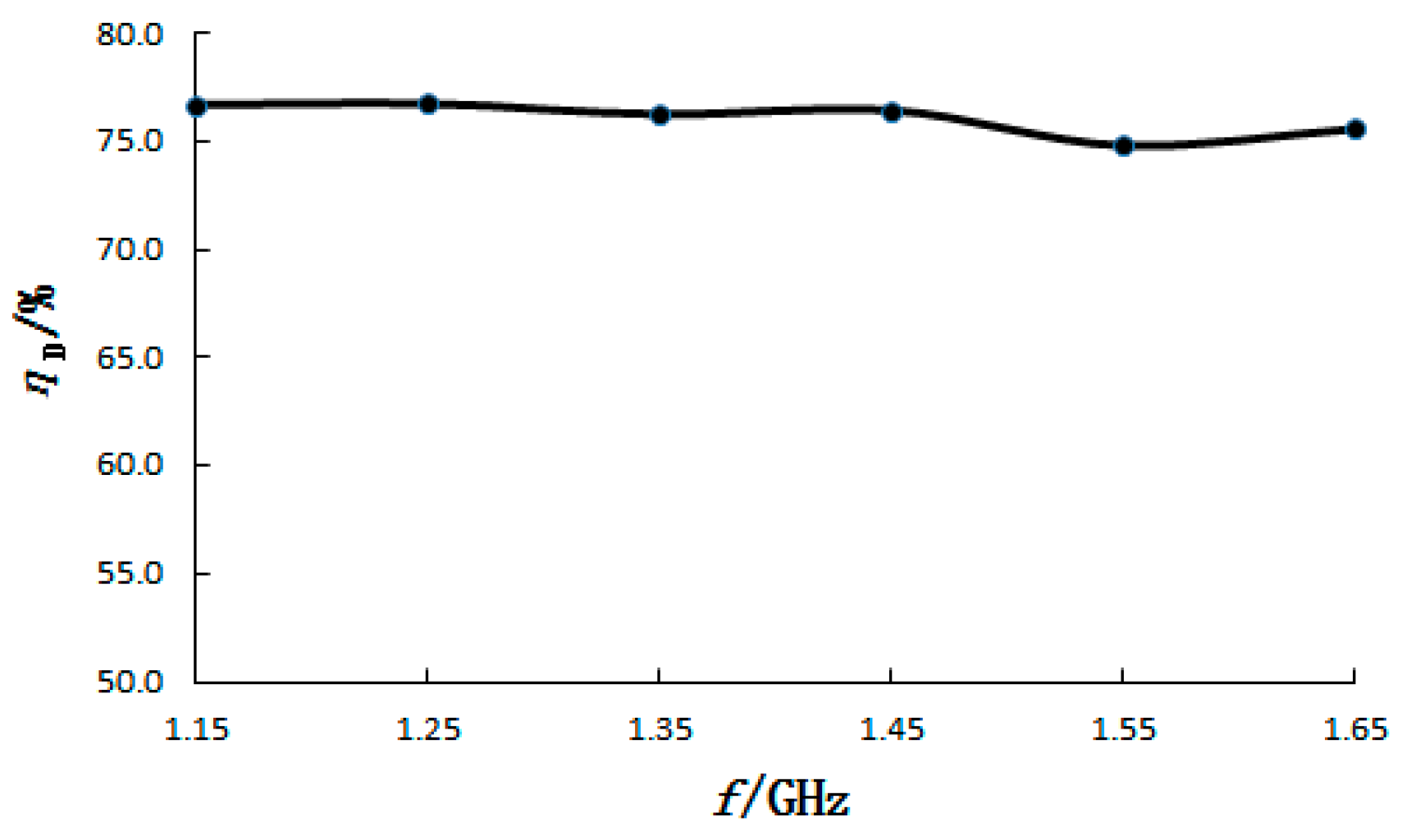

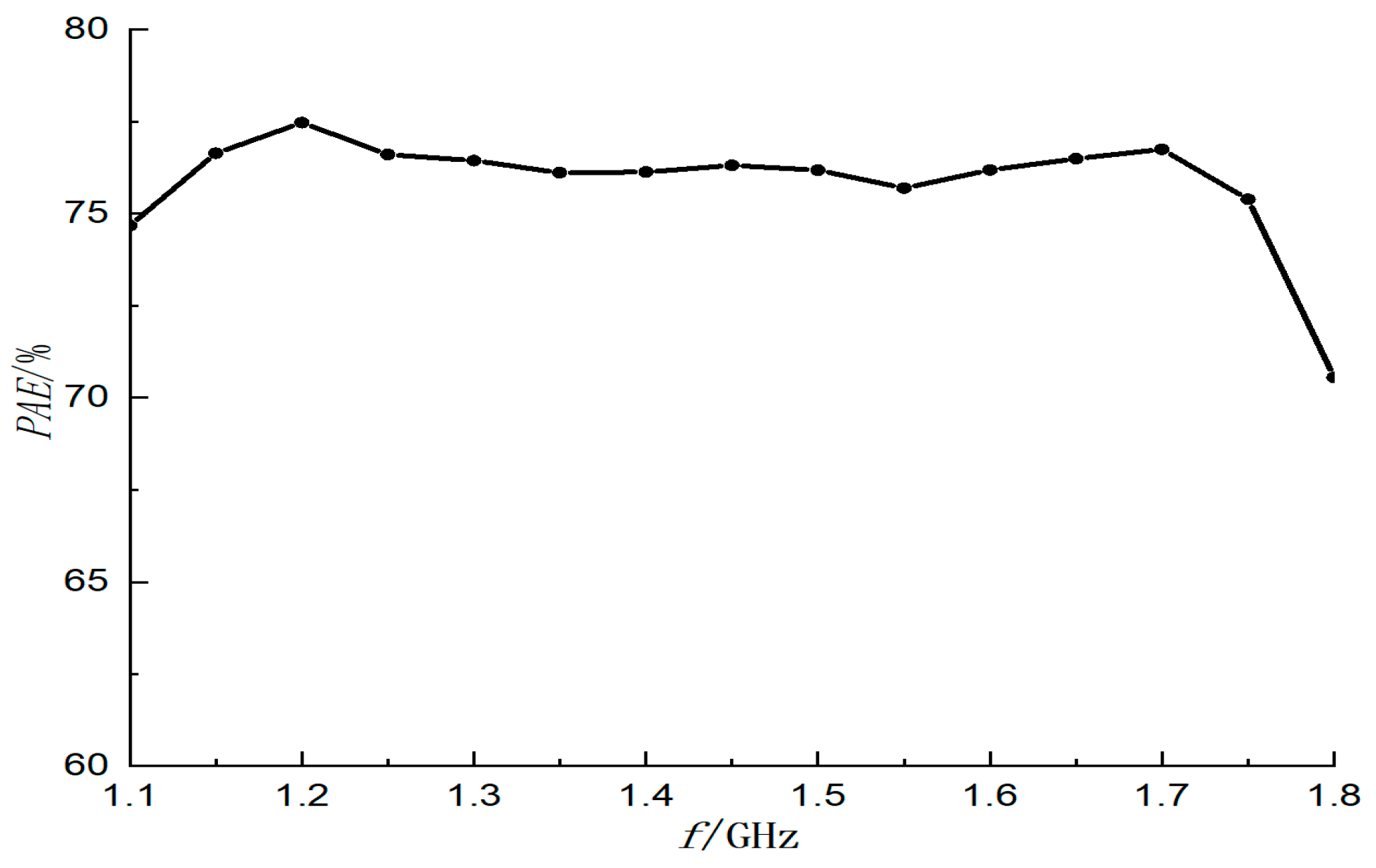

3.2. Test Results and Analysis

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Jing, X.-D.; Zhong, S.-C.; Wang, H.-L.; You, F. A 150-W Spaceborne GaN Solid-State Power Amplifier for BeiDou Navigation Satellite System. Int. IEEE Trans. Aerosp. Electron. Syst. 2022, 58, 2383–2393. [Google Scholar] [CrossRef]

- Andersson, C.M.; Gustafsson, D.; Cahuana, J.C.; Hellberg, R.; Fager, C. A 1–3-GHz digitally controlled dual-RF input power-amplifier design based on a Doherty-outphasing continuum analysis. IEEE Trans. Microw. Theory Tech. 2013, 61, 3743–3752. [Google Scholar] [CrossRef]

- Ruiz, M.N.; Benito, A.L.; Pérez-Cisneros, J.R.; Gilabert, P.L.; Montoro, G.; García, J.A. Constant-gain envelope tracking in a UHF outphasing transmitter based on continuous-mode class-E GaN HEMT PAs. In Proceedings of the 2016 IEEE MTT-S International Microwave Symposium (IMS), San Francisco, CA, USA, 22–27 May 2016; IEEE: New York, NY, USA, 2016; pp. 1–4. [Google Scholar]

- Giofré, R.; Colantonio, P.; González, L.; De Arriba, F.; Cabrìa, L.; Molina, D.L.; Garrido, E.C.; Vitobello, F. Design realization and tests of a space-borne gan solid state power amplifier for second generation Galileo navigation system. IEEE Trans. Aerosp. Electron. Syst. 2018, 54, 2383–2396. [Google Scholar] [CrossRef]

- Maassen, D.; Boet, J.D.; Zanden, J.V.D.; Heeres, R.M.; Rijs, F.V. Comparison between latest Si-LDMOS and GaN technology for RF-Power base station transistors. In Proceedings of the 2023 53rd European Microwave Conference (EuMC), Berlin, Germany, 19–21 September 2023; pp. 283–286. [Google Scholar] [CrossRef]

- Nuttinck, S.; Gebara, E.; Laskar, J.; Rorsman, N.; Olsson, J.; Zirath, H.; Eklund, K.; Harris, M. Comparison between Si-LDMOS and GaN-based microwave power transistors. In Proceedings of the IEEE Lester Eastman Conference on High Performance Devices, Newark, DE, USA, 8 August 2002; pp. 149–154. [Google Scholar]

- Wang, Y.; Cao, L. Status in U.S. AESA fighter radar and development trends. In Proceedings of the IET International Radar Conference 2013, Xi’an, China, 14–16 April 2013; pp. 1–6. [Google Scholar]

- Jiayu, L.; Su, P.; Yu, Z.; Zhang, H.; Peng, Y.; Chen, M. Near-junction heat dissipation of high-power chips by copper-diamond based heat sink. In Proceedings of the 2025 26th International Conference on Electronic Packaging Technology (ICEPT), Shanghai, China, 5–7 August 2025; pp. 1–3. [Google Scholar]

- Gibiino, G.P.; Nunes, L.C.; Miller, N.C. Advancing RF GaN HEMTs: A Perspective on Measurement and Characterization Techniques. IEEE Microw. Mag. 2025, 26, 18–31. [Google Scholar] [CrossRef]

- Rochette, S.; Vendier, O.; Langrez, D.; Cazaux, J.L.; Kuball, M.; Buchta, M.; Xiong, A. A high efficiency 140W power amplifier based on a single GaN HEMT device for space applications in L-band. In Proceedings of the 2012 7th European Microwave Integrated Circuit Conference, Amsterdam, The Netherlands, 29–30 October 2012; pp. 127–130. [Google Scholar]

- Available online: https://www.necspace.co.jp/en/products/payload/sspa.html (accessed on 22 November 2025).

- Osawa, K.; Yoshikoshi, H.; Nitta, A.; Tanaka, T.; Mitani, E.; Satoh, T. Over 74% efficiency, L-band 200W GaN-HEMT for space applications. In Proceedings of the 2016 46th European Microwave Conference (EuMC), London, UK, 4–6 October 2016; pp. 397–400. [Google Scholar]

- Yang, F.; Yin, K.; Zhao, H.; Zhao, Y.; Liu, J.; Yang, S. High power high efficiency solid state power amplifier used in space. Chin. Space Sci. Technol. 2023, 43, 55–62. [Google Scholar]

- Katz, A.; MacDonald, J.; Dorval, R.; Eggleston, B.; Drexler, P.; Liang, C. High-efficiency high-power linearized L-band SSPA for navigational satellites. In Proceedings of the 2017 IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 4–9 June 2017; pp. 1834–1837. [Google Scholar]

- Shen, X.; Zhang, L.; Dai, J.; Yang, J.; Zhou, B. L-band SSPA for Future Payloads exploiting GaN Technology. In Proceedings of the 2020 International Conference on Microwave and Millimeter Wave Technology (ICMMT), Shanghai, China, 17–20 May 2020; pp. 1–3. [Google Scholar]

- Giofre, R.; Cabria, L.; De Arriba, F.; Rapisarda, M.; Cipriani, E.; Colantonio, P. A flexible and efficient GaN-Based SSPA for next-generation L-Band reconfigurable payloads. IEEE Trans. Microw. Theory Tech. 2025, 1–15. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.

Share and Cite

Jing, X.; Wang, H.; You, F.; Zhang, X.; Ma, K. Design and Implementation of an L-Band 400 W Continuous-Wave GaN Power Amplifier. Electronics 2026, 15, 203. https://doi.org/10.3390/electronics15010203

Jing X, Wang H, You F, Zhang X, Ma K. Design and Implementation of an L-Band 400 W Continuous-Wave GaN Power Amplifier. Electronics. 2026; 15(1):203. https://doi.org/10.3390/electronics15010203

Chicago/Turabian StyleJing, Xiaodong, Hailong Wang, Fei You, Xiaofan Zhang, and Kuo Ma. 2026. "Design and Implementation of an L-Band 400 W Continuous-Wave GaN Power Amplifier" Electronics 15, no. 1: 203. https://doi.org/10.3390/electronics15010203

APA StyleJing, X., Wang, H., You, F., Zhang, X., & Ma, K. (2026). Design and Implementation of an L-Band 400 W Continuous-Wave GaN Power Amplifier. Electronics, 15(1), 203. https://doi.org/10.3390/electronics15010203