Sub-6 GHz GaAs SPDT Switch Co-Designed with Shunt Inductor for ESD Protection

Abstract

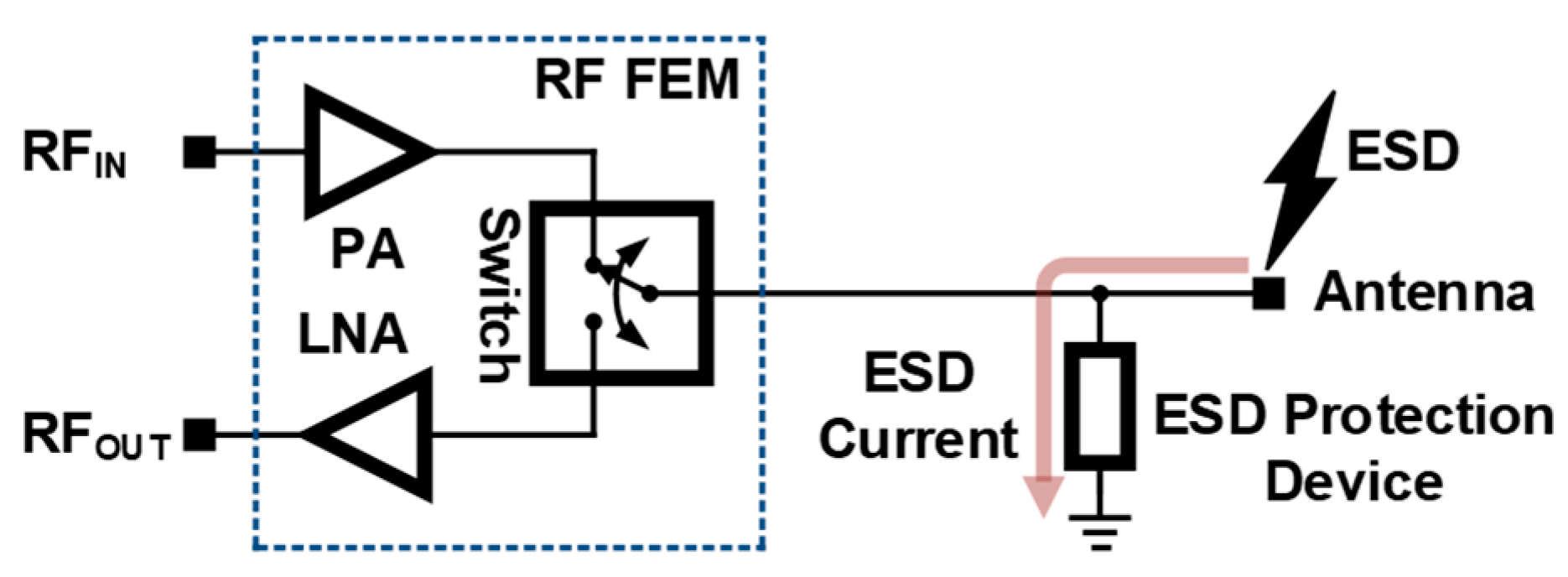

1. Introduction

2. Proposed SPDT Switch with ESD Protection

2.1. ESD Protection Technique Using Shunt Inductor

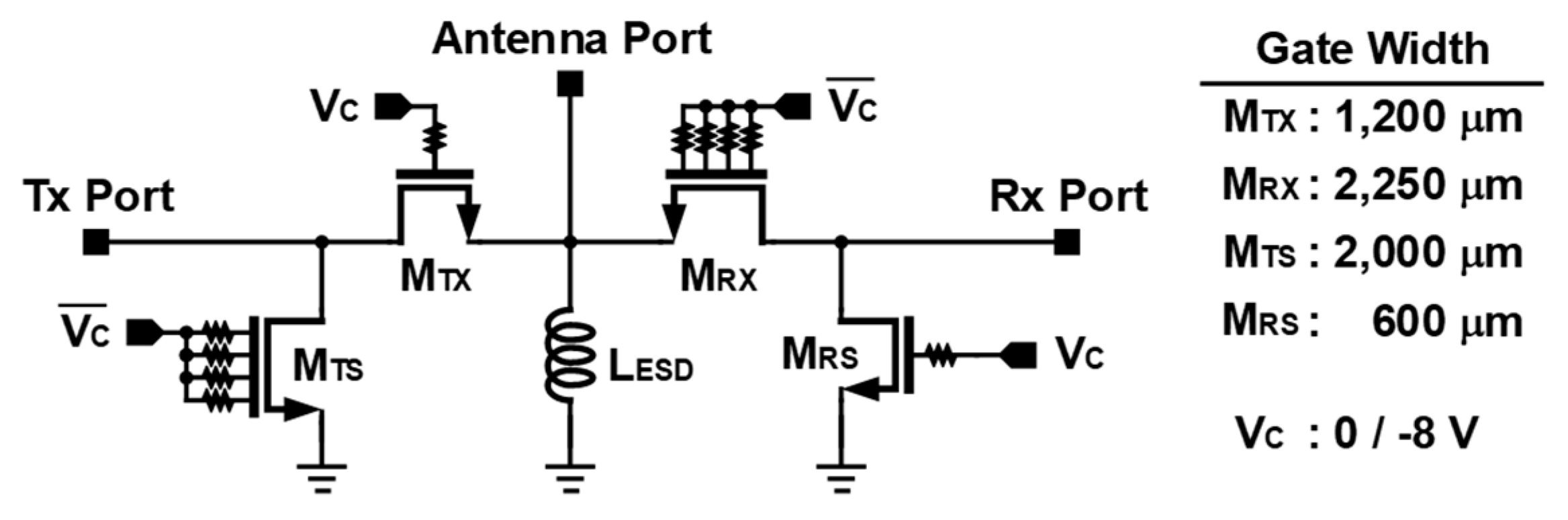

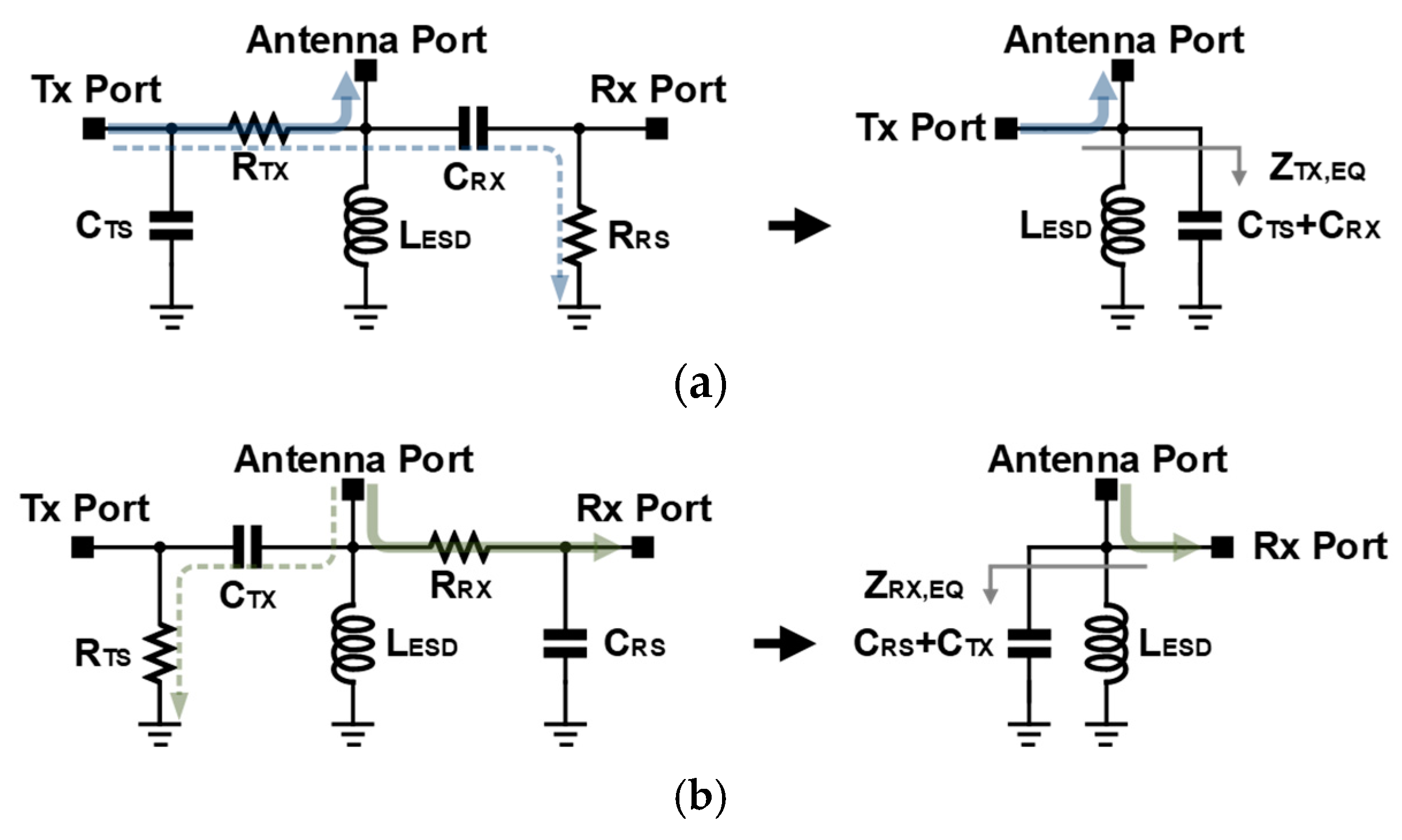

2.2. Operation of the Proposed SPDT Switch

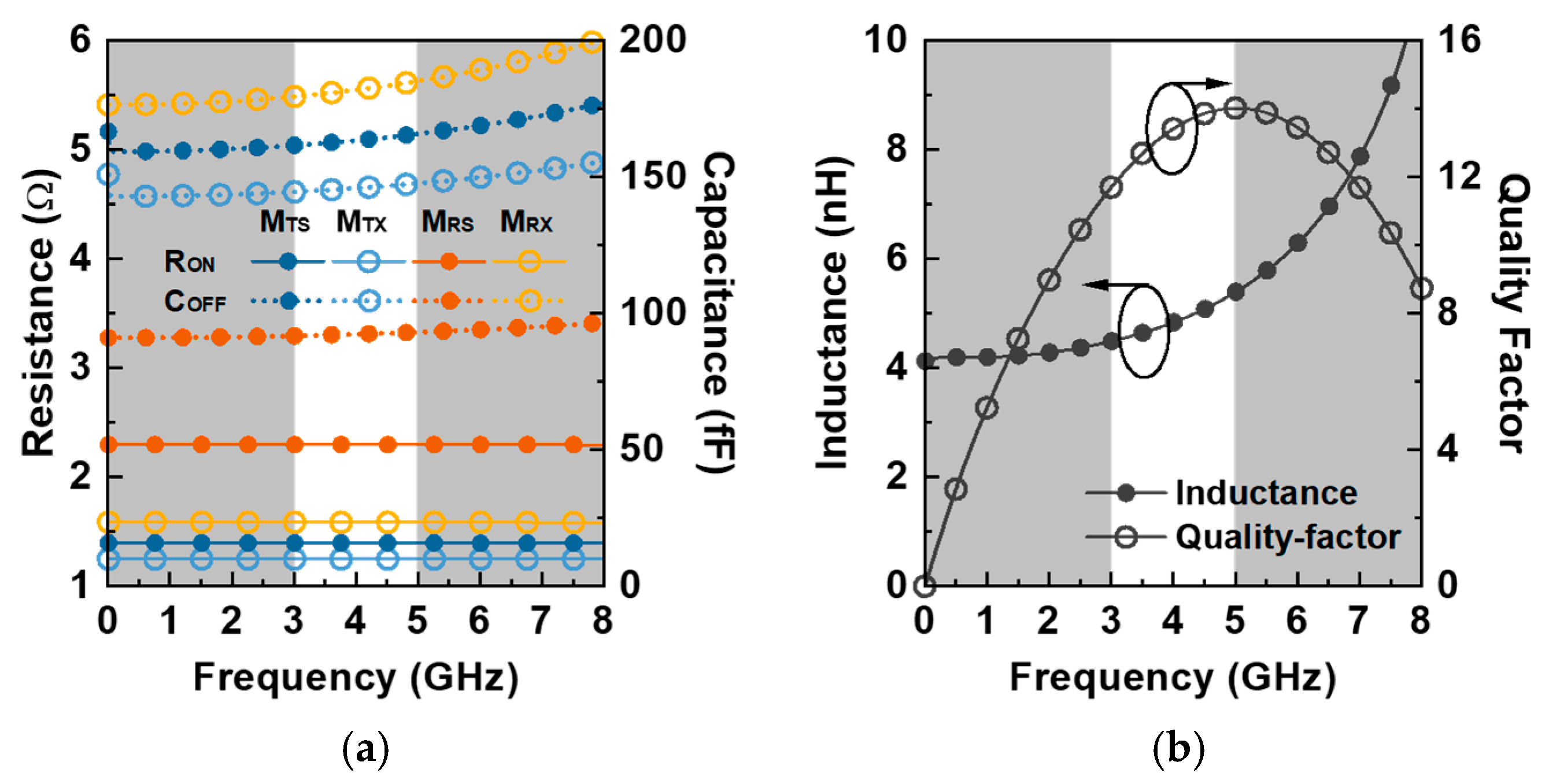

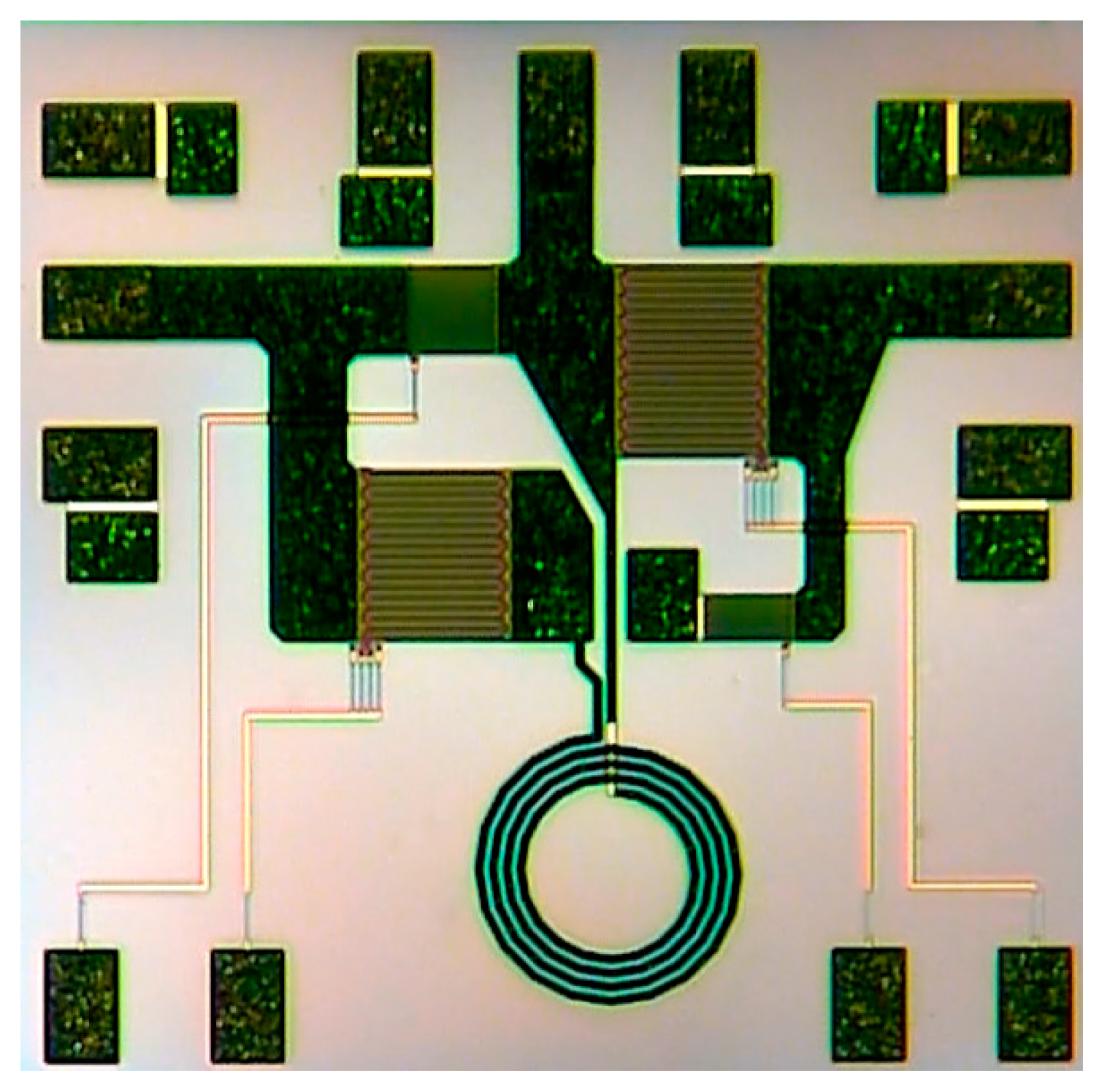

2.3. Design of the Proposed SPDT Switch

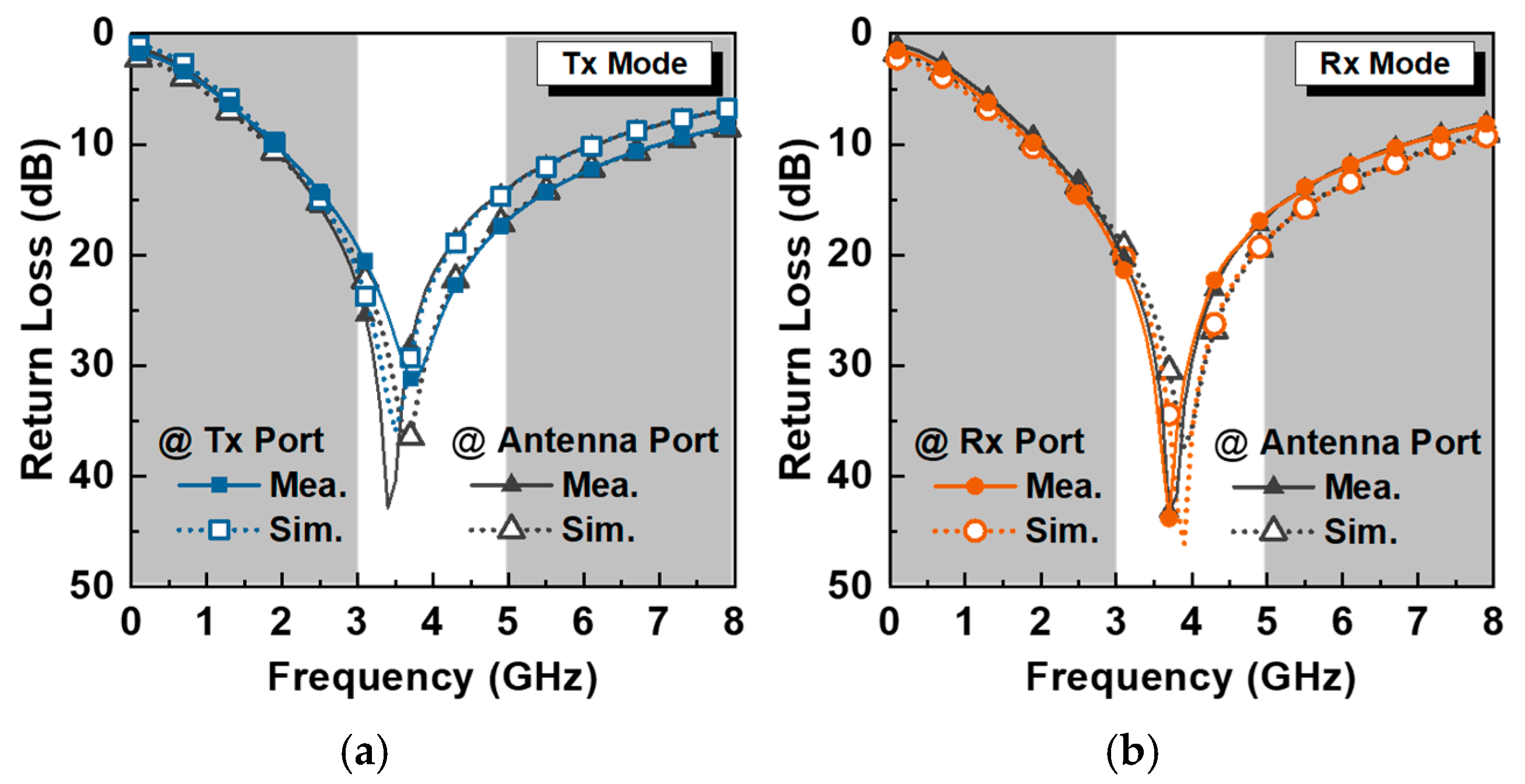

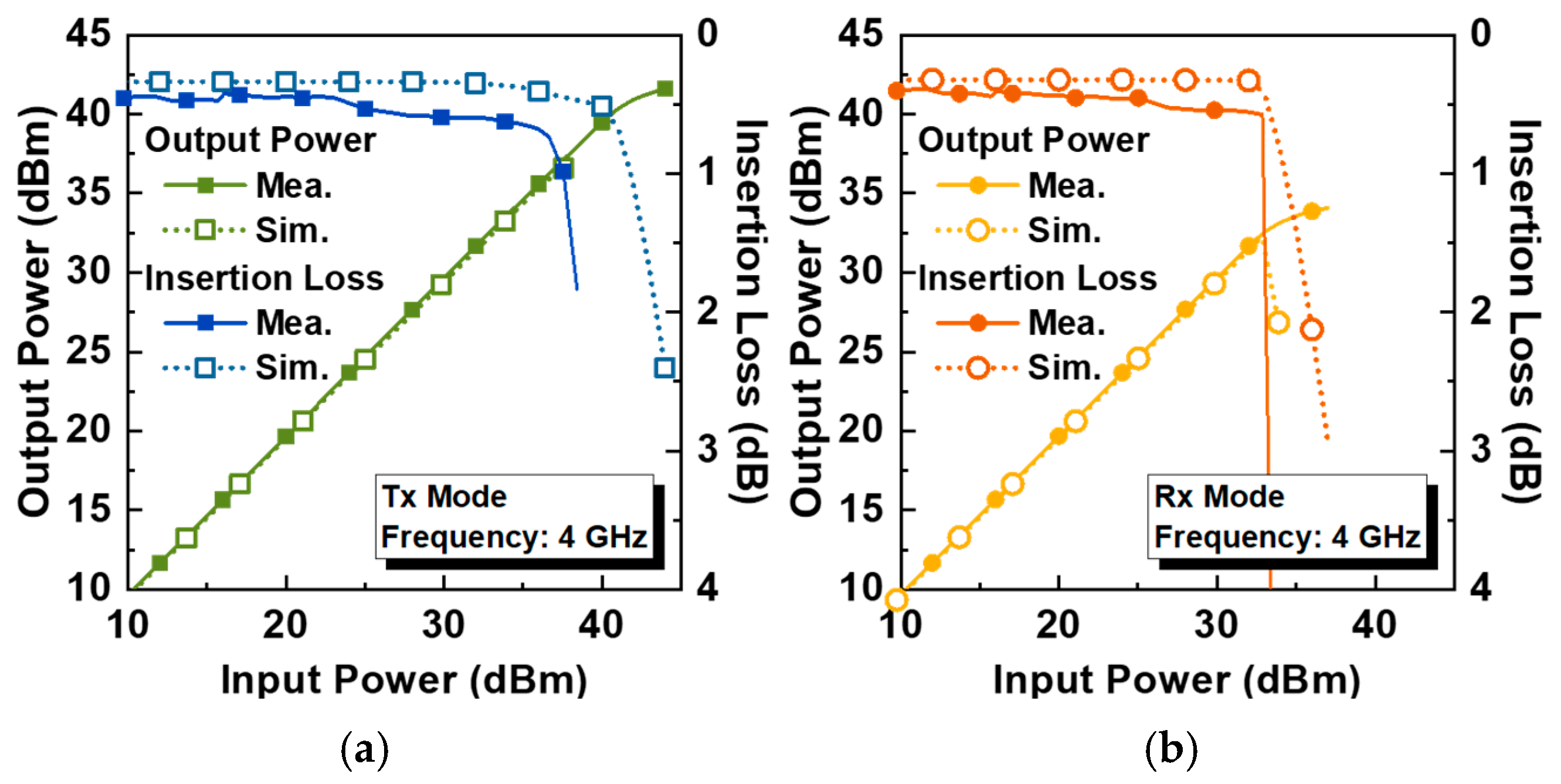

3. Design Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Takenaka, K.; Noguchi, Y.; Arayashiki, S.; Wada, T. Load-Modulated Balanced Amplifier Design for Handset Applications. IEEE Microw. Wirel. Technol. Lett. 2023, 33, 855–858. [Google Scholar] [CrossRef]

- Kong, M.; Wu, Y.; Wang, W. The Co-Design of Broadband Diplexer and Quasi-Reflectionless Lowpass/Highpass TFIPD Filter Chip. IEEE Trans. Circuits Syst. II-Express Briefs 2023, 70, 486–490. [Google Scholar] [CrossRef]

- Bo, S.F.; Ou, J.-H.; Peng, Y.J.; Xuan, K.; Xu, J.-X.; Zhang, X.Y. Broadband GaAs HBT Doherty Power Amplifier for 5G NR Mobile Handset. IEEE Trans. Circuits Syst. II-Express Briefs 2024, 71, 527–531. [Google Scholar] [CrossRef]

- Ariturk, G.; Almuqati, N.R.; Yu, Y.; Yen, E.T.-T.; Fruehling, A.; Sigmarsson, H.H. Exact Synthesis of Hybrid Acoustic-Electromagnetic Filters with Wideband Chebyshev Responses. IEEE Trans. Microw. Theory Tech. 2024, 72, 3185–3199. [Google Scholar] [CrossRef]

- Kim, D.; Im, D. A 2.4 GHz Reconfigurable Cascode/Folded-Cascode Inductive Source Degenerated LNA with Enhanced OP1dB and OIP3 over Gain Reduction. IEEE Trans. Circuits Syst. II-Express Briefs 2023, 70, 1831–1835. [Google Scholar] [CrossRef]

- Yang, F.; Zhang, B.; Song, L.; Xu, Y. A Compact RF Front-End SiP with Improved Harmonic Suppression for Dual Polarization Phased Array Radar. IEEE Microw. Wirel. Technol. Lett. 2024, 34, 350–353. [Google Scholar] [CrossRef]

- Lee, S.; Seo, W.; Kim, S.; Ko, B.; Lee, S.; Kim, M.-S.; Kim, J. A Concurrent 26/48 GHz Low-Noise Amplifier with an Optimal Dual-Band Noise Matching Method Using GaAs 0.15 μm pHEMT. IEEE Trans. Circuits Syst. II-Express Briefs 2024, 3, 1096–1100. [Google Scholar] [CrossRef]

- Park, J.; Lee, S.; Hong, S. A 24–40 GHz Differential SPDT Switch with an NMOS and PMOS Alternating Structure and Leakage-Canceling Capacitors. IEEE Trans. Circuits Syst. II-Express Briefs 2023, 70, 86–90. [Google Scholar] [CrossRef]

- Lin, Y.-S.; Lan, K.-S.; Chen, B.-S. Wideband Millimeter-Wave Power Divider and SPDT Switch Using Inverting Spiral-Coupled-Line. IEEE Trans. Circuits Syst. II-Express Briefs 2023, 70, 1575–1579. [Google Scholar] [CrossRef]

- Lee, S.; Park, J.; Hong, S. W-Band Compact Balun-Embedded SPDT Switch with Leakage-Canceled Overlapped Transformers. IEEE Microw. Wireless Technol. Lett. 2023, 33, 1532–1535. [Google Scholar] [CrossRef]

- Ma, G.; Yang, Z.; Meng, F. An Ultracompact Frequency-Reconfigurable SPDT Switch with 42-dB Isolation. IEEE Microw. Wirel. Technol. Lett. 2024, 34, 45–48. [Google Scholar] [CrossRef]

- Kwon, J.; Lee, J.; Kim, T.; Seo, D.; Yoo, J.; Cho, J.; Park, C. Asymmetric SOI CMOS Switch with Series and Parallel Resonators to Enhance Isolation. IEEE Trans. Circuits Syst. II-Express Briefs 2024, 71, 1964–1968. [Google Scholar] [CrossRef]

- Jang, S.; Kong, S.; Lee, H.-D.; Park, J.; Kim, K.-S.; Park, B. A 28 GHz >30 dBm Output P1dB SPDT switch with integrated ESD protection in CMOS 65 nm. In Proceedings of the 2020 50th European Microwave Conference (EuMC), Utrecht, The Netherlands, 12–14 January 2021; pp. 140–143. [Google Scholar]

- Hao, W.; Di, M.; Pan, Z.; Li, X.; Miao, R.; Cahoon, N.; Wang, A. A 60GHz Traveling-Wave SPDT Switch with HBM and CDM ESD Protection in 45nm SOI CMOS. In Proceedings of the 2022 IEEE 16th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Nangjing, China, 25–28 October 2022; pp. 1–4. [Google Scholar]

- Ker, M.-D.; Chou, C.-I.; Lee, C.-M. A novel LC-tank ESD protection design for Giga-Hz RF circuits. In Proceedings of the IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Philadelphia, PA, USA, 9–10 June 2003; pp. 115–118. [Google Scholar]

- Lin, C.-Y.; Chu, L.-W.; Tasi, S.-Y.; Ker, M.-D.; Lu, T.-H.; Hsu, T.-L.; Hung, P.-F.; Song, M.-H.; Tseng, J.-C.; Chang, T.-H.; et al. Modified LC-tank ESD protection design for 60-GHz RF applications. In Proceedings of the 2011 20th European Conference on Circuit Theory and Design (ECCTD), Linköping, Sweden, 29–31 August 2011; pp. 57–60. [Google Scholar]

- Park, C.-K.; Kim, M.-G.; Kim, C.-H.; Hong, S. Ku-band low noise amplifier with using short-stub ESD protection. In Proceedings of the IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Philadelphia, PA, USA, 9–10 June 2003; pp. 671–674. [Google Scholar] [CrossRef]

- Yoon, J.; Park, C. 5-GHz low noise amplifier with ESD protection method using transformer. Microw. Opt. Technol. Lett. 2014, 56, 684–689. [Google Scholar] [CrossRef]

- CG2185X2: 6GHz Medium Power SPDT Switch; CEL: Santa Clara, CA, USA, August 2017.

- TQP4M0008: Low Loss Reflective SPDT Switch; Qorvo: Greensboro, CA, USA, June 2018.

- SKY13320-374LFM: 0.1–6.0 GHz GaAs SPDT Switch; Skyworks: Irvine, CA, USA, January 2018.

- Kwon, J.; Yoo, J.; Lee, J.; Kim, T.; Park, C. Sub-6 GHz GaAs pHEMT SPDT switch with low insertion loss and high power handling capability using dual-gate technique. In Proceedings of the IEEE Wireless and Microwave Technology Conference (WAMICON), Melbourne, FL, USA, 17–18 April 2023; pp. 49–52. [Google Scholar]

- Lee, J.-E.; Song, J.-H.; Baek, M.-S.; Son, J.-T.; Kim, J.-H.; Lee, E.-G.; Choi, S.; Kim, C.-Y. A Sub-6 GHz Asymmetric GaAs SPDT Switch with High Tx-to-Rx Isolation and Low Insertion Loss. IEEE Microw. Wirel. Technol. Lett. 2024, 34, 490–492. [Google Scholar] [CrossRef]

- Ali, L.; Wang, G.; Meng, F.; Ding, X.; Adhikari, K.K.; Wang, C. MXene-Coated Planar Microwave Resonator Sensor for Ultrasensitive Humidity Monitoring. IEEE Microw. Wirel. Technol. Lett. 2023, 33, 1572–1575. [Google Scholar] [CrossRef]

- Wang, S.; Wan, C.; Zheng, Y. Microwave Characterization of Glucose Level Using Composite PMS-HMSIW Cavity Resonator Integrated with Microfluidic Channel. IEEE Trans. Instrum. Meas. 2024, 73, 6009116. [Google Scholar] [CrossRef]

| Reference | Tech. | Freq. (GHz) | Fractional Bandwidth (%) | Return Loss (dB) | Insertion Loss (dB) | Isolation (dB) | IP1dB (dBm) | Chip Size (mm2) | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Tx | Rx | Tx | Rx | Tx | Rx | Tx | Rx | |||||

| CEL’17 [19] | GaAs | 2–6 | 100 | >18 | <0.4 | >26 | 32 @ 6 GHz | - | ||||

| Qorvo’18 [20] | GaAs | 0.1–6 | 193 | >15 | <0.85 | >17 | 35 @ 3 GHz | - | ||||

| Skyworks’18 [21] | GaAs | 0.1–6 | 193 | >20 | <0.6 | >24 | 34 @ 2.45 GHz | - | ||||

| WAMICON’23 [22] | 500 nm GaAs | 3–5 | 50 | >15 | <0.3 | >32.7 | >34.2 @ 3 GHz | 0.83 | ||||

| MWTL’24 [23] | 500 nm GaAs | 3.3–5 | 41 | >15.8 | <0.53 | <0.39 | >36.4 | >25.4 | >40 (1) | - | 0.84 | |

| This work | 500 nm GaAs | 3–5 | 50 | >14.0 | >16.2 | <0.35 | <0.32 | >31.6 | >33.9 | 38.0 (1) | 33.0 (1) | 0.78 |

| 3–6 | 66.7 | >10.3 | >12.2 | <0.62 | <0.46 | >28.5 | >30.2 | |||||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kwon, J.; Lee, J.; Yoo, J.; Kim, T.; Park, C. Sub-6 GHz GaAs SPDT Switch Co-Designed with Shunt Inductor for ESD Protection. Electronics 2025, 14, 1707. https://doi.org/10.3390/electronics14091707

Kwon J, Lee J, Yoo J, Kim T, Park C. Sub-6 GHz GaAs SPDT Switch Co-Designed with Shunt Inductor for ESD Protection. Electronics. 2025; 14(9):1707. https://doi.org/10.3390/electronics14091707

Chicago/Turabian StyleKwon, Jaehyun, Jaeyong Lee, Jinho Yoo, Taehun Kim, and Changkun Park. 2025. "Sub-6 GHz GaAs SPDT Switch Co-Designed with Shunt Inductor for ESD Protection" Electronics 14, no. 9: 1707. https://doi.org/10.3390/electronics14091707

APA StyleKwon, J., Lee, J., Yoo, J., Kim, T., & Park, C. (2025). Sub-6 GHz GaAs SPDT Switch Co-Designed with Shunt Inductor for ESD Protection. Electronics, 14(9), 1707. https://doi.org/10.3390/electronics14091707