On the Use of Ridge Waveguides to Synthesize Impedances

Abstract

1. Introduction

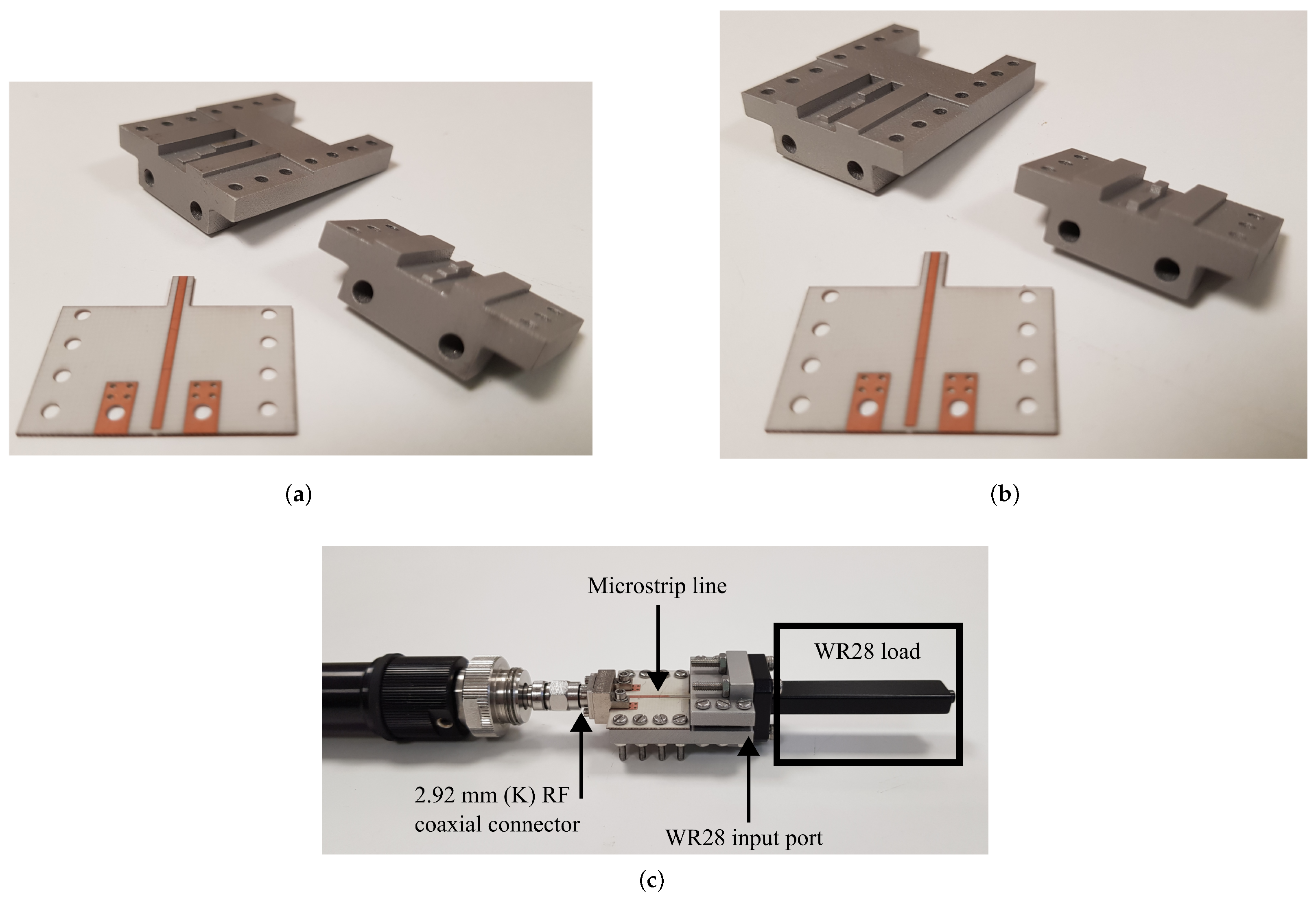

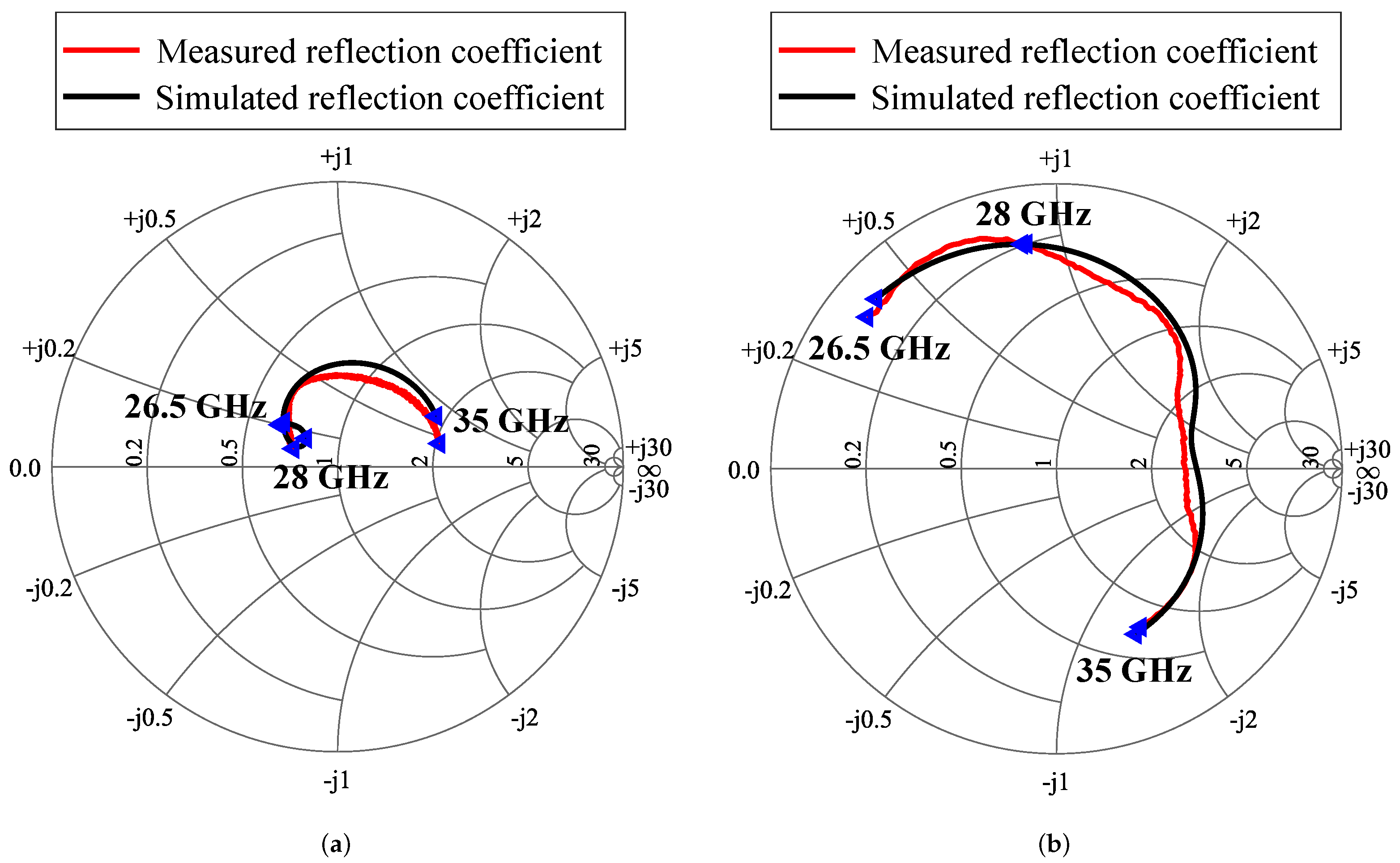

2. Materials and Methods

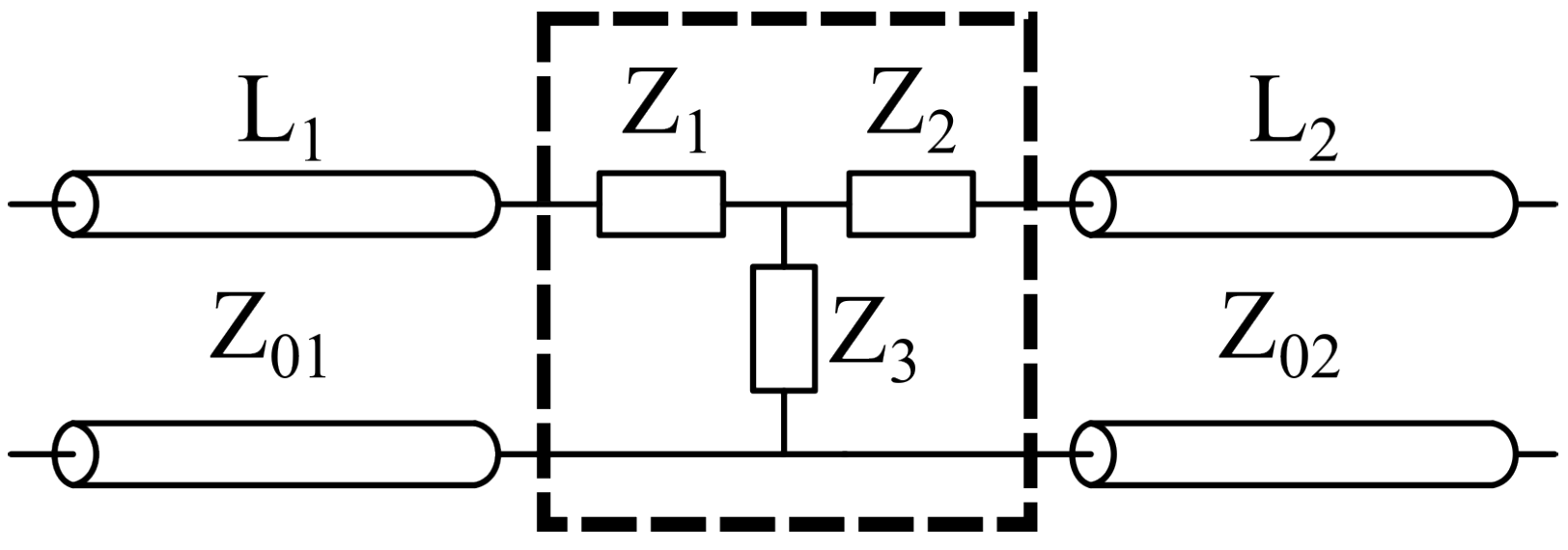

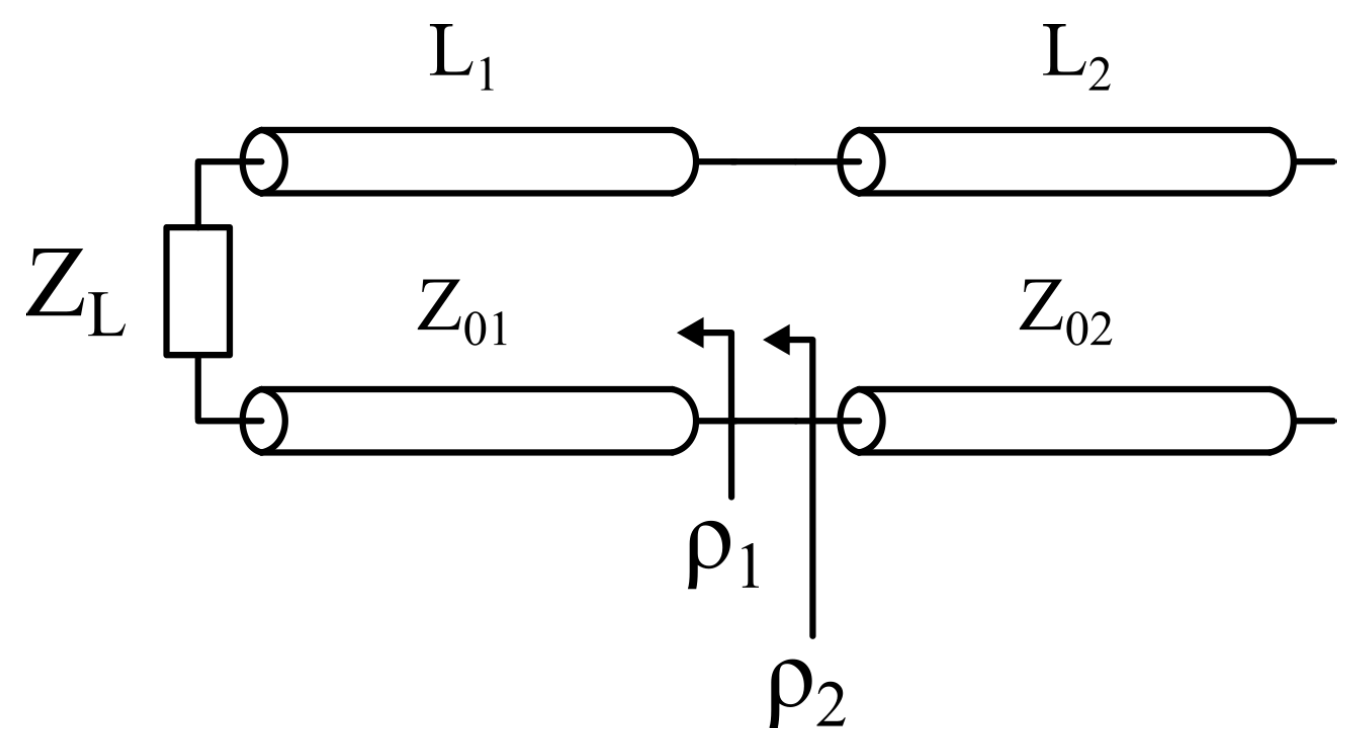

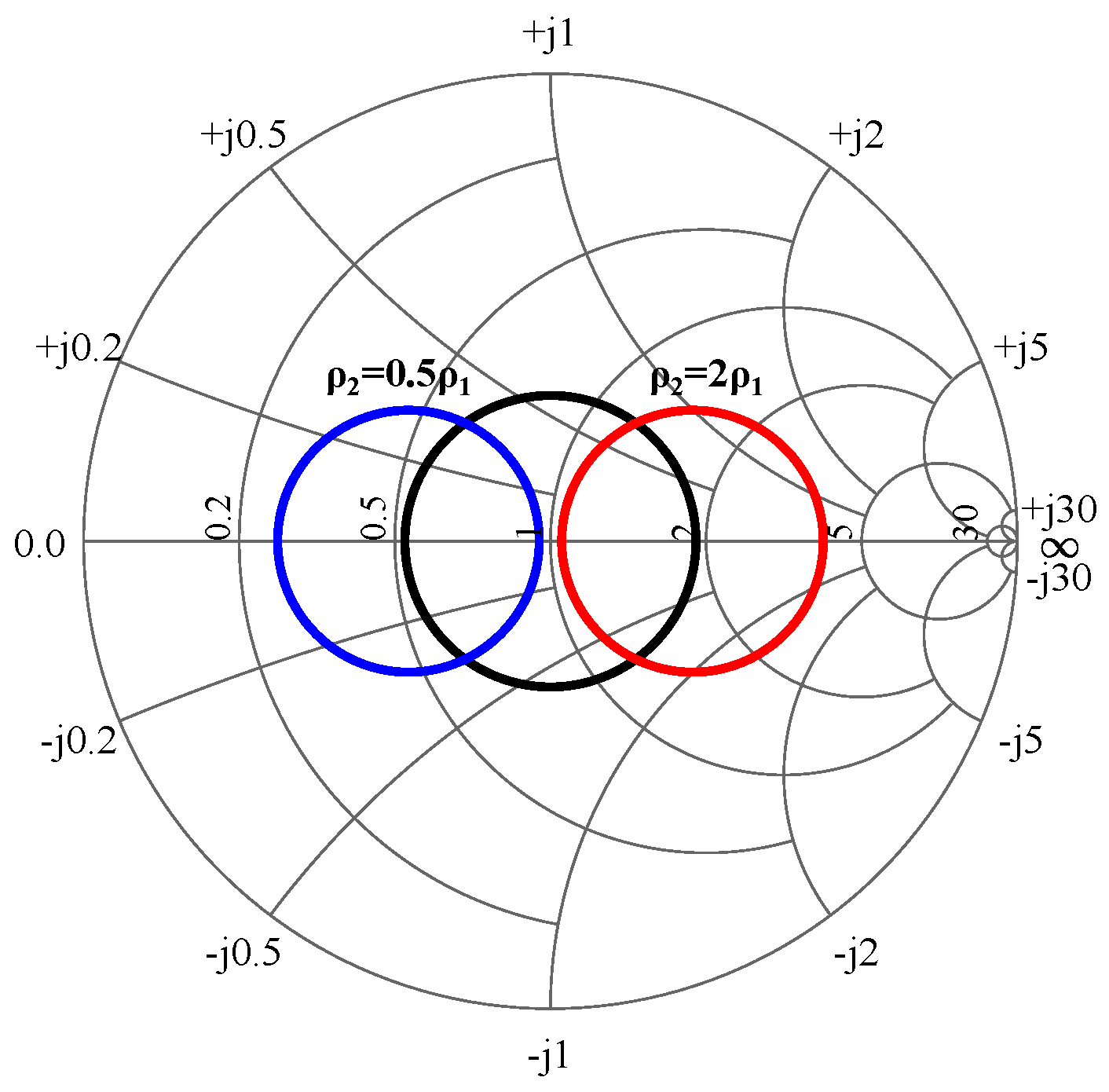

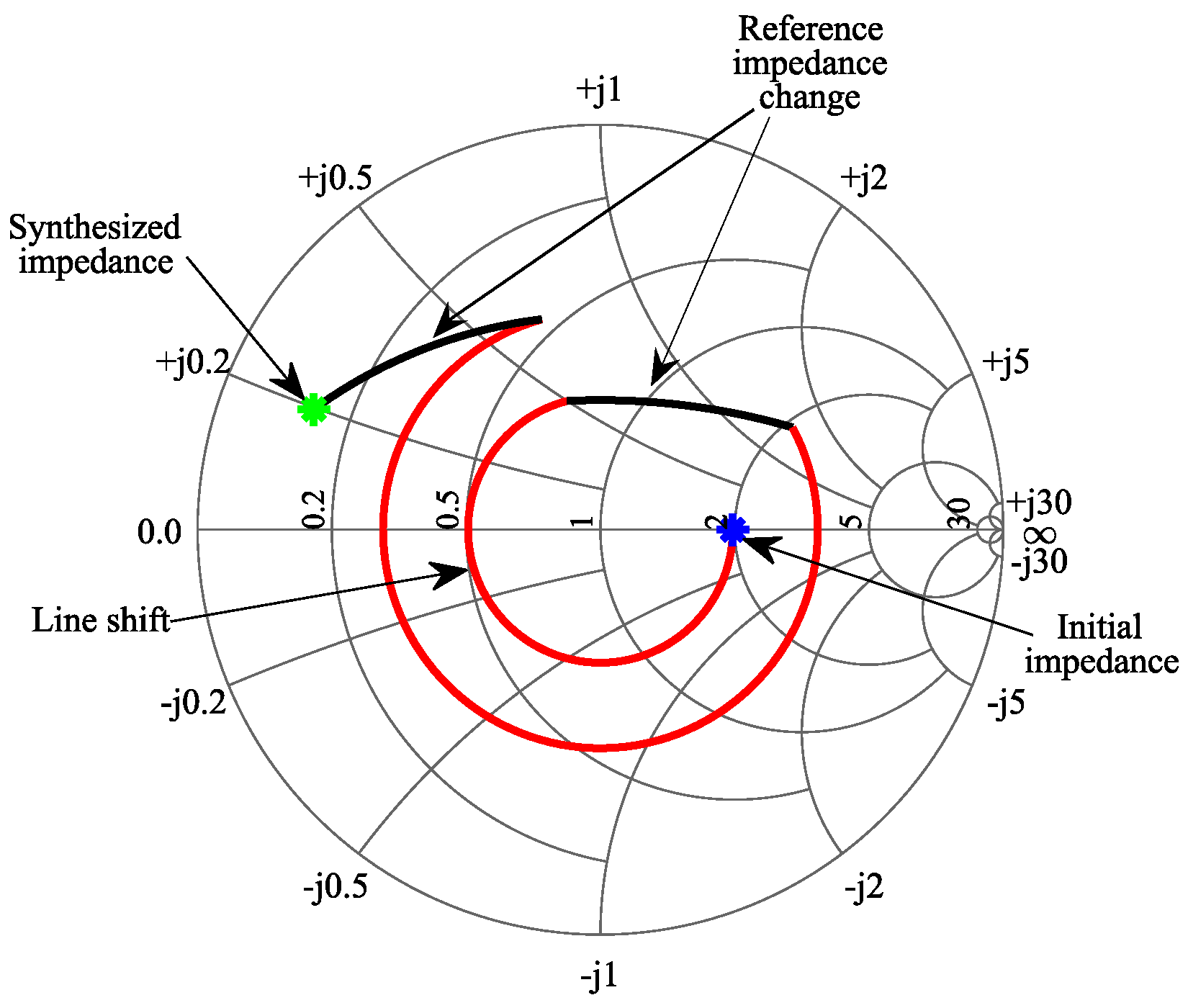

2.1. Design of the Impedance Synthesis Network

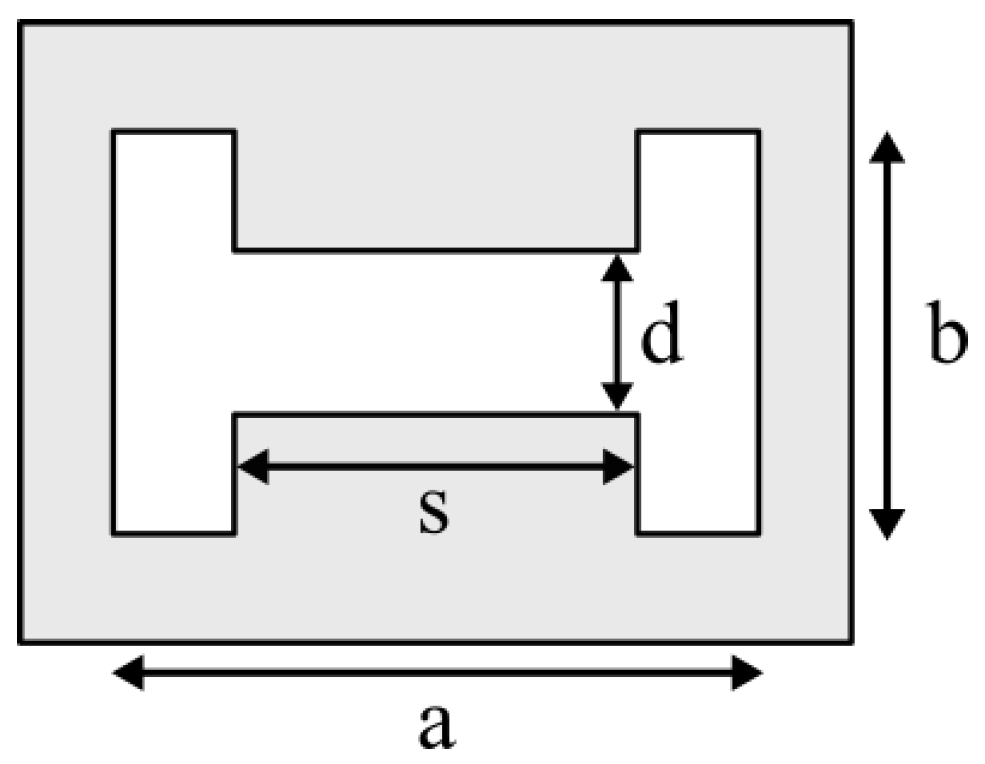

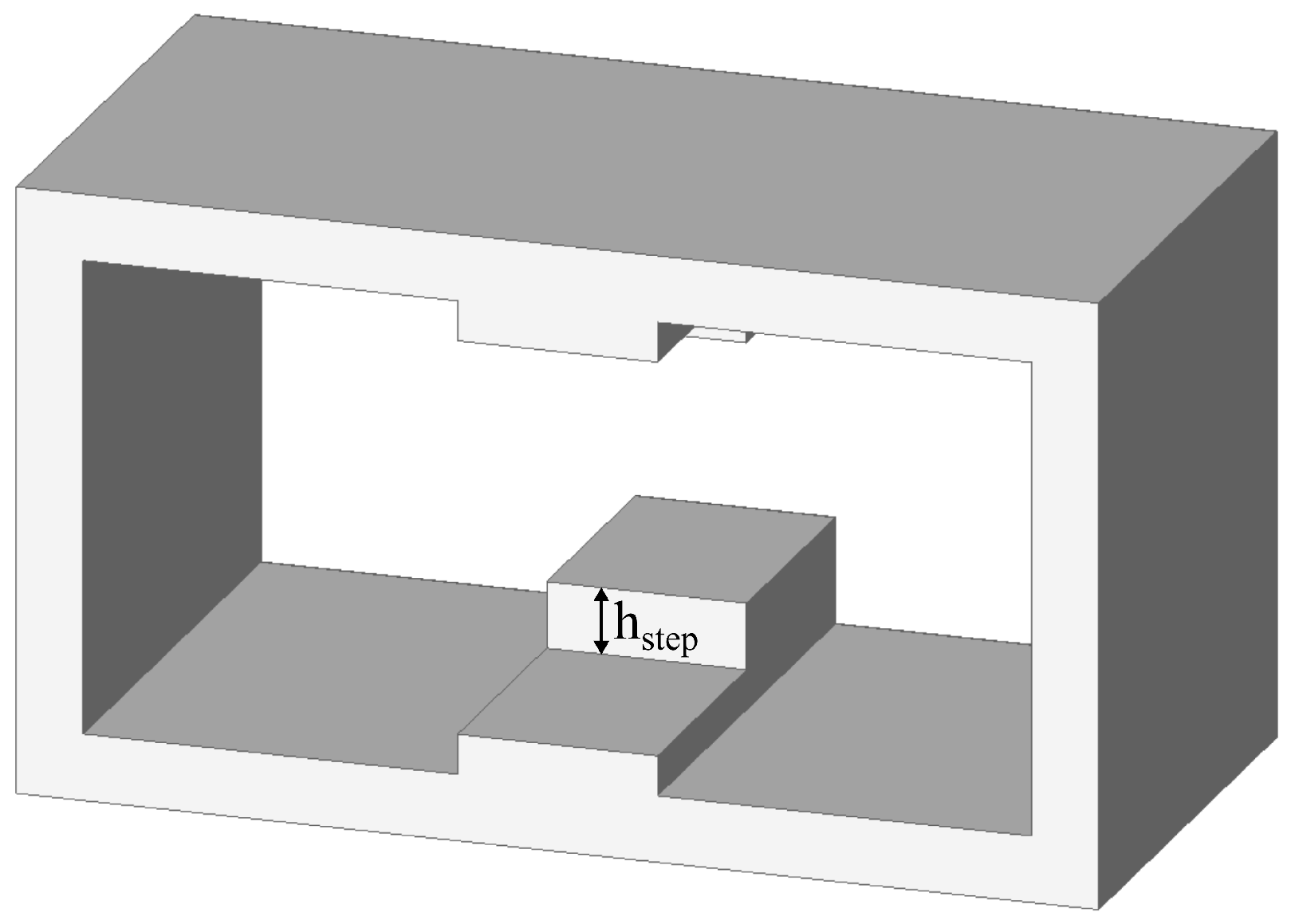

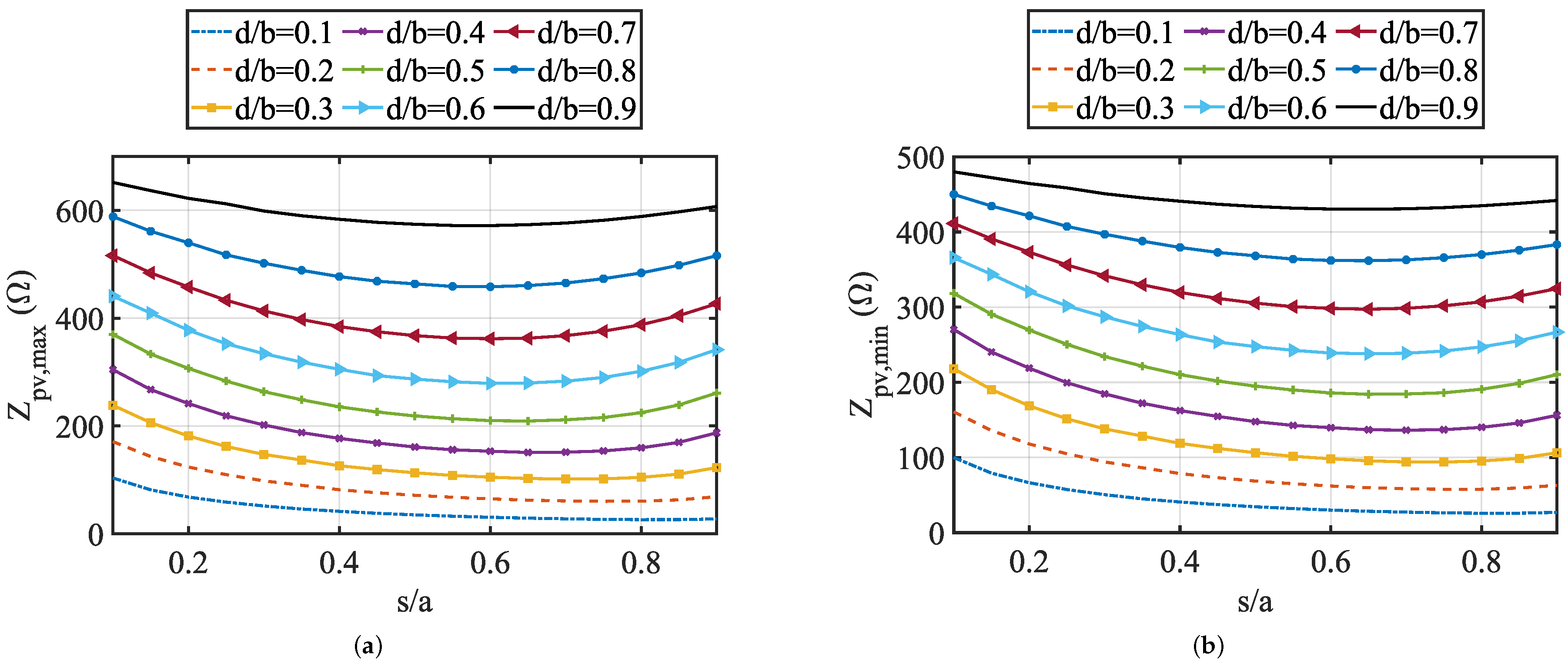

2.2. Ridge Discontinuity Analysis

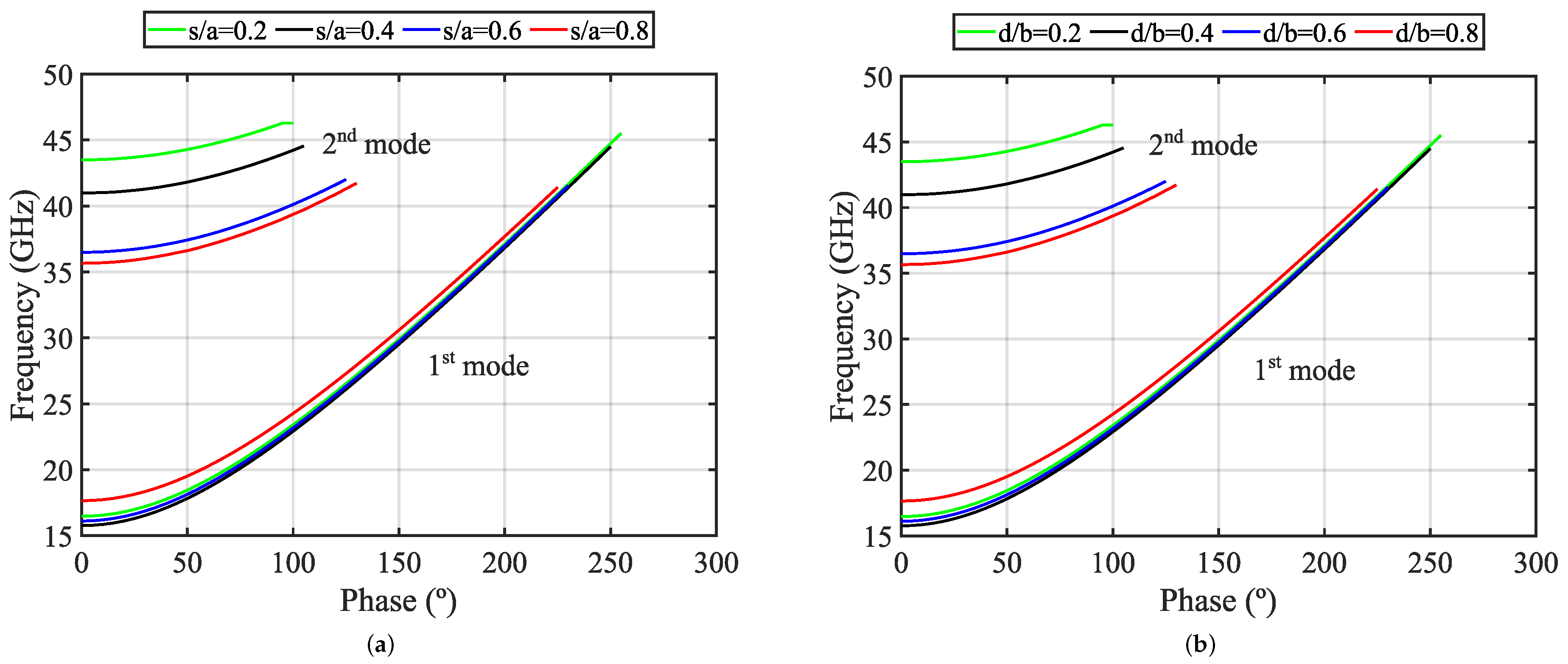

2.3. Analysis of a Single DRW

3. Results

4. Discussion

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| DRW | Double-ridge waveguide |

| RWG | Rectangular waveguide |

| RW | Ridge waveguide |

| SIW | Substrate-integrated waveguide |

| SRW | Single-ridge waveguide |

References

- Taryana, Y.; Sulaeman, Y.; Wahyu, Y.; Armi, N.; Paramayudha, K.; Rojak, R.A. Design of two stage low noise amplifier using double stub matching network. In Proceedings of the 2015 IEEE International Conference on Aerospace Electronics and Remote Sensing Technology (ICARES), Bali, Indonesia, 3–5 December 2015; pp. 1–5. [Google Scholar] [CrossRef]

- Thian, M. High-Efficiency Wilkinson-Power-Combining Class-EF Amplifier with Lumped-Element Load Network. In Proceedings of the 2018 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Chengdu, China, 26–30 October 2018; pp. 199–202. [Google Scholar] [CrossRef]

- Hoefer, W.; Burton, M. Closed-Form Expressions for the Parameters of Finned and Ridged Waveguides. IEEE Trans. Microw. Theory Tech. 1982, 30, 2190–2194. [Google Scholar] [CrossRef]

- Moreira, J.; Churkin, S.; Hesselbarth, J. A Double-Ridged Waveguide Design for 5G mmWave Applications. In Proceedings of the 2022 Asia-Pacific Microwave Conference (APMC), Yokohama, Japan, 29 November–2 December 2022; pp. 824–826. [Google Scholar] [CrossRef]

- Michailidis, A.; Noulis, T. Algorithm-based Wide-Band Impedance Matching Network Synthesis and Optimization. In Proceedings of the 2024 20th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Volos, Greece, 2–5 July 2024; pp. 1–4. [Google Scholar] [CrossRef]

- Uz Zaman, A.; Vukusic, T.; Alexanderson, M.; Kildal, P.S. Design of a Simple Transition From Microstrip to Ridge Gap Waveguide Suited for MMIC and Antenna Integration. IEEE Antennas Wirel. Propag. Lett. 2013, 12, 1558–1561. [Google Scholar] [CrossRef]

- Vilenskiy, A.R.; Zhang, Y. A Compact and Wideband MMIC-to-Ridge Gap Waveguide Contactless Transition for Phased Array Antenna Front Ends. IEEE Antennas Wirel. Propag. Lett. 2024, 23, 990–994. [Google Scholar] [CrossRef]

- Cano, J.L.; Mediavilla, A.; Perez, A.R. Full-Band Air-Filled Waveguide-to-Substrate Integrated Waveguide (SIW) Direct Transition. IEEE Microw. Wirel. Components Lett. 2015, 25, 79–81. [Google Scholar] [CrossRef]

- Shi, X.; Xue, Y.; Yang, Y.J.; Chen, J.X. A Wideband DRWG Balun With Low Loss and Compact Size. IEEE Microw. Wirel. Technol. Lett. 2024, 34, 379–382. [Google Scholar] [CrossRef]

- Helszajn, J. Ridge Waveguides and Passive Microwave Components; The Institution of Engineering and Technology: London, UK, 2000. [Google Scholar]

- Steer, M. Microwave and RF Design: Networks, Volume 3; NC State University: Raleigh, NC, USA, 2019. [Google Scholar]

- Yao, H.W.; Abdelmonem, A.; Liang, J.F.; Zaki, K. Analysis and Design of Microstrip-to-Wavguide Transitions. IEEE Trans. Microw. Theory Tech. 1994, 42, 2371–2380. [Google Scholar] [CrossRef]

| d (mm) | s (mm) | Length (mm) | Electrical Length (°) | (Ω) | ||

|---|---|---|---|---|---|---|

| Center- located impedance | First Ridge | 2.616 | 1.5 | 3.4 | 86.4 | 424.3 |

| Second Ridge | 1.896 | 1.5 | 2.95 | 79.2 | 301 | |

| Third Ridge | 0.544 | 1.5 | 4.68 | 144 | 93.4 | |

| Edge- located impedance | First Ridge | 1.556 | 1.5 | 4.8 | 133.2 | 244 |

| Second Ridge | 2.556 | 1.5 | 3 | 75.6 | 413 | |

| Third Ridge | 0.544 | 1.5 | 3.2 | 100.8 | 93.4 |

| Electrical Length 1 (EL1) (°) | Electrical Length 2 (EL2) (°) | Electrical Length 3 (EL3) (°) | (Ω) | (Ω) | (Ω) | (Ω) | (Ω) | (Ω) | (Ω) | (Ω) | (Ω) | (Ω) | (Ω) | (Ω) | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Center- located impedance | 86.4 | 79.2 | 144 | 424.3 | 301 | 93.4 | 4552.4 j | 4597.2 j | −2310.8 j | 428.3 j | 449.2 j | −329.8 j | 206.4 j | 203.7 j | −123.3 j |

| Edge- located impedance | 133.2 | 75.6 | 100.8 | 244 | 413 | 93.4 | −1215.8 j | −1242.1 j | 6300.5 j | 505.9 j | 544 j | −429.6 j | 227.7 j | 236.9 j | −133.6 j |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Flórez Rodríguez, J.J.; Herrán, L.F. On the Use of Ridge Waveguides to Synthesize Impedances. Electronics 2025, 14, 1060. https://doi.org/10.3390/electronics14061060

Flórez Rodríguez JJ, Herrán LF. On the Use of Ridge Waveguides to Synthesize Impedances. Electronics. 2025; 14(6):1060. https://doi.org/10.3390/electronics14061060

Chicago/Turabian StyleFlórez Rodríguez, Juan J., and Luis F. Herrán. 2025. "On the Use of Ridge Waveguides to Synthesize Impedances" Electronics 14, no. 6: 1060. https://doi.org/10.3390/electronics14061060

APA StyleFlórez Rodríguez, J. J., & Herrán, L. F. (2025). On the Use of Ridge Waveguides to Synthesize Impedances. Electronics, 14(6), 1060. https://doi.org/10.3390/electronics14061060