A 512 KBytes Highly Reliable and High-Speed Embedded NOR Flash Memory

Abstract

1. Introduction

2. Implementation of Enhanced Flash Architecture and Optimized Sense Amplifier

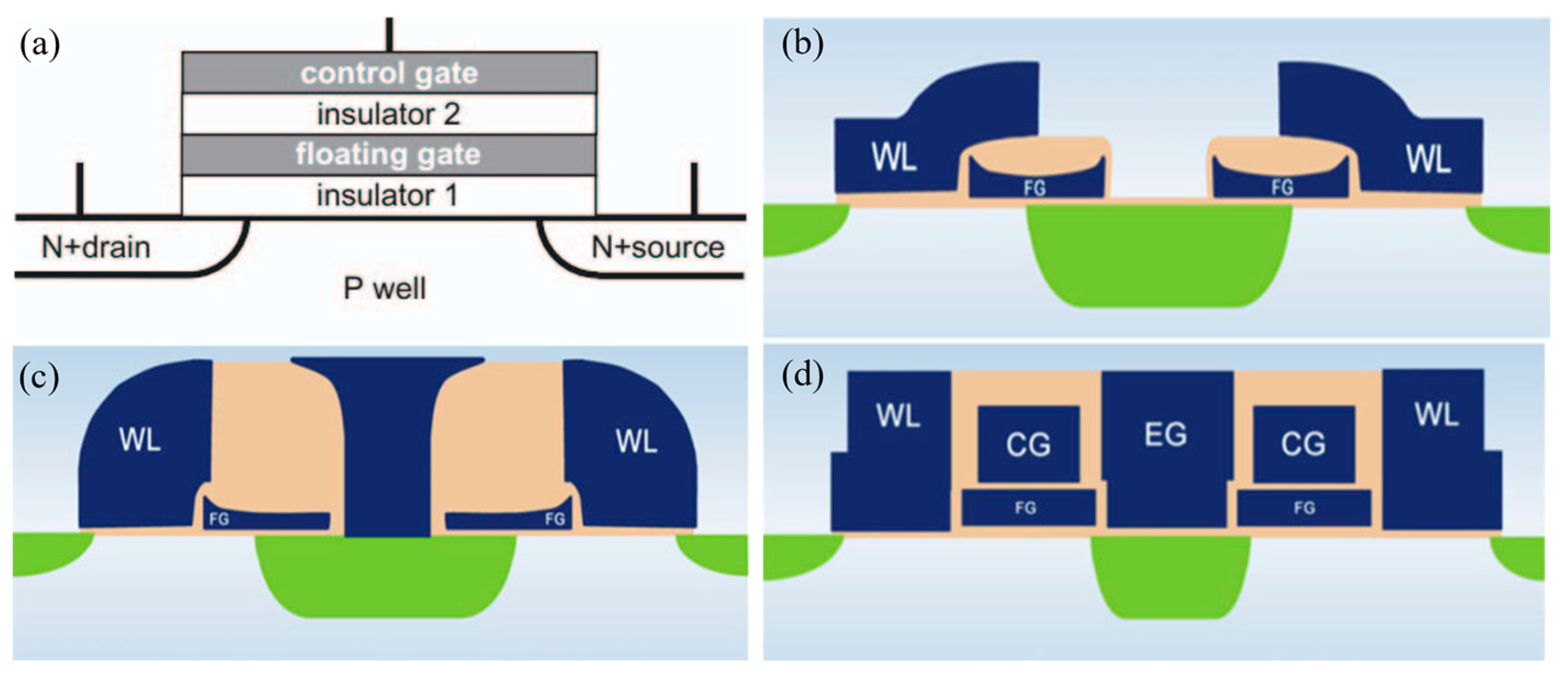

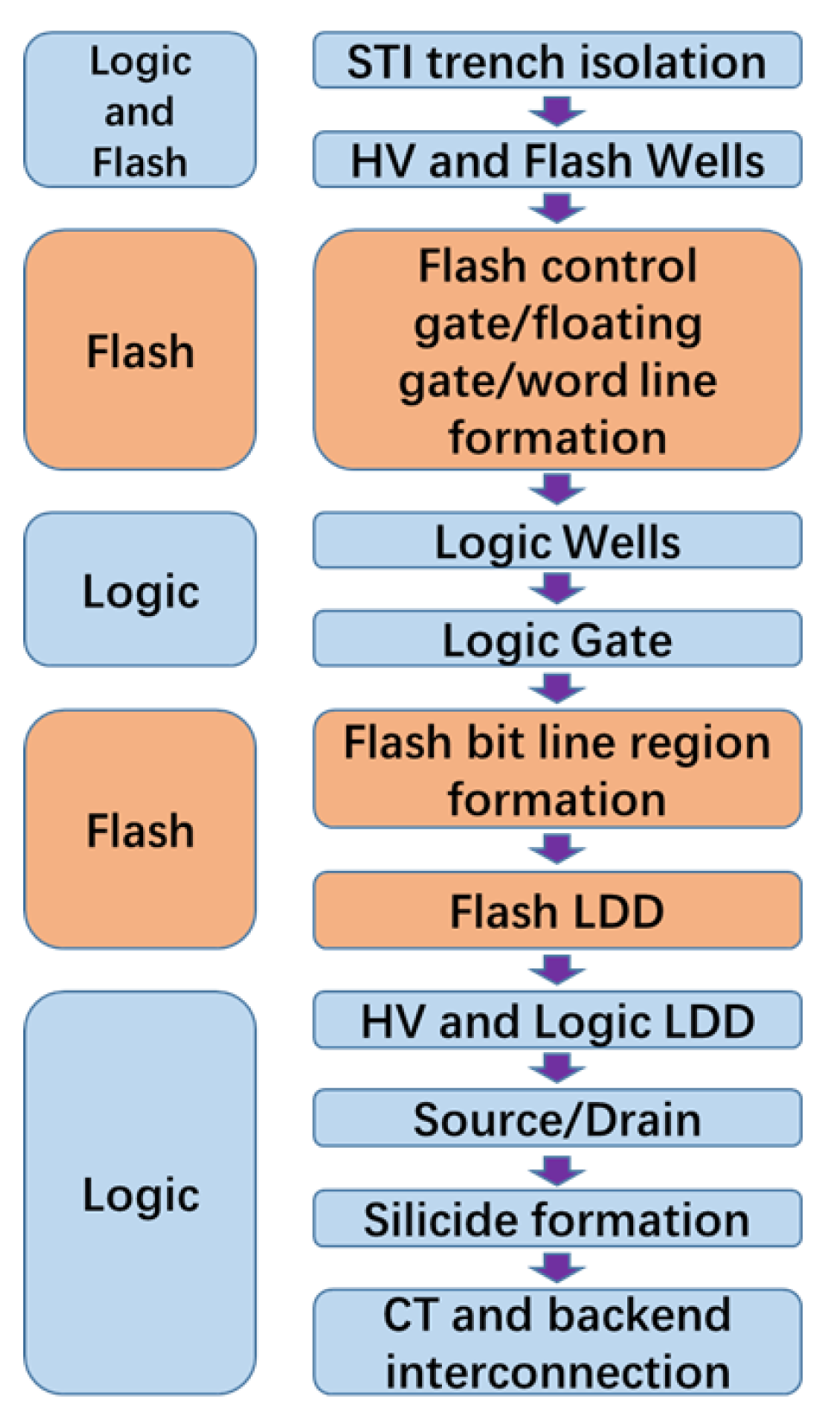

2.1. NORD Flash Cell Structure and Enhanced Flash Memory Array Architecture

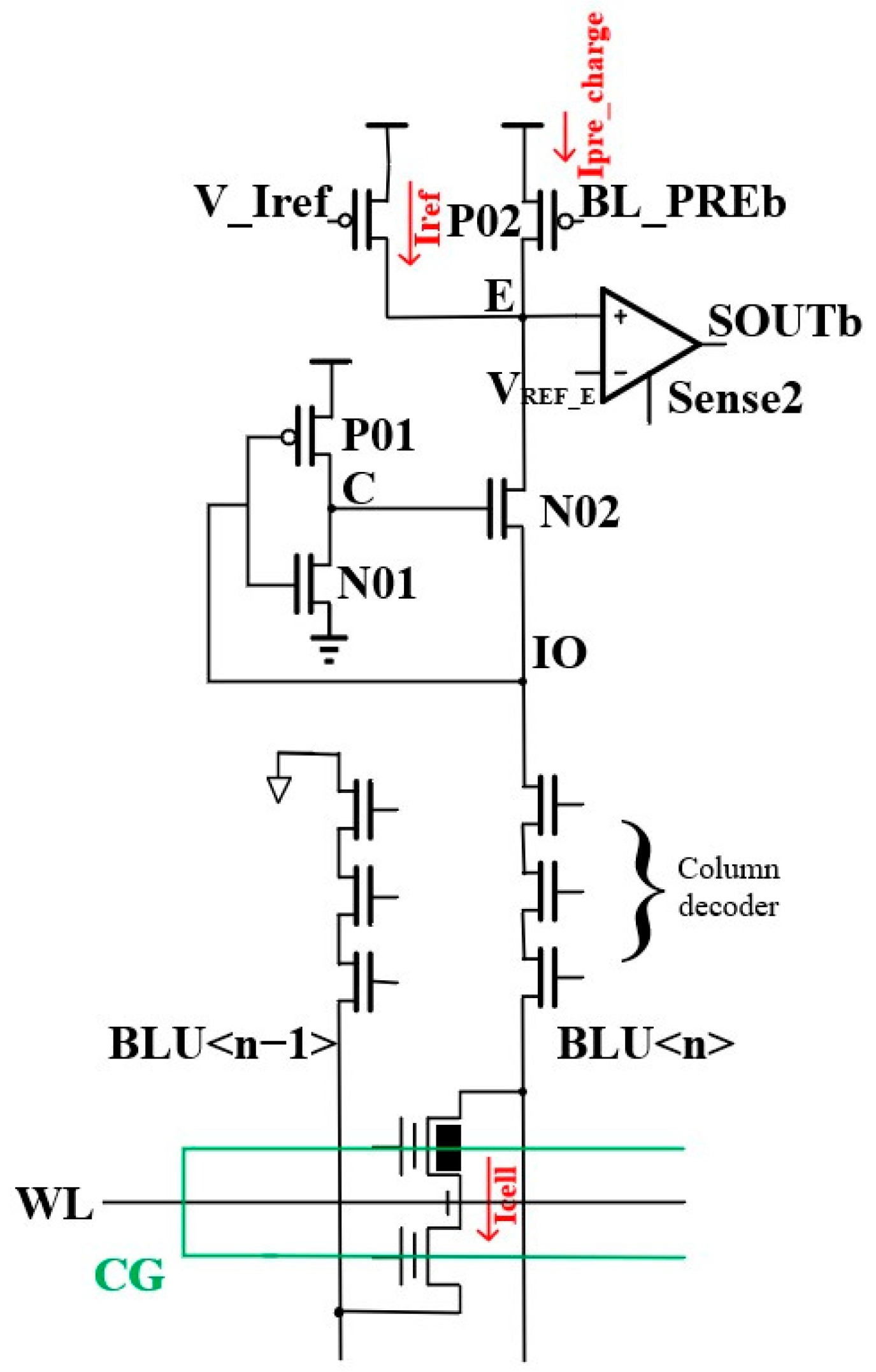

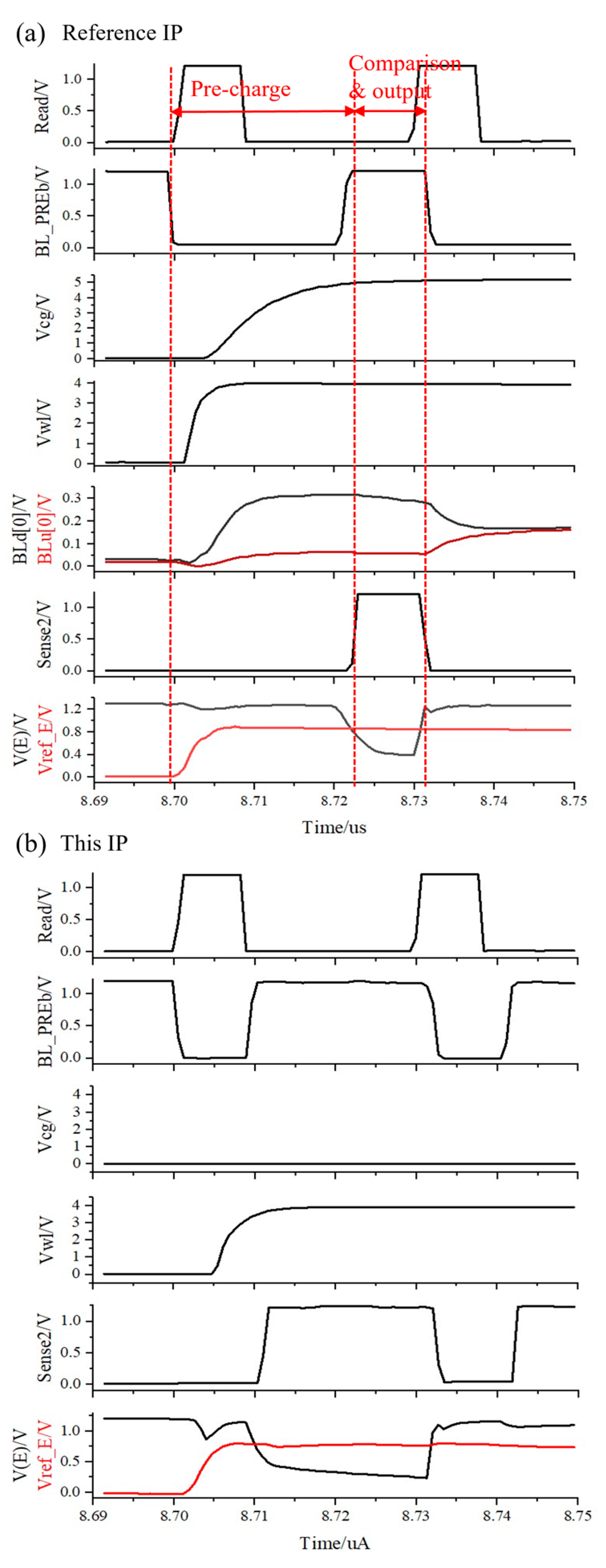

2.2. Implementation of High Noise Immunity Sense Amplifier

3. Highly Reliable and High-Speed Reading Performance and Measurement Results

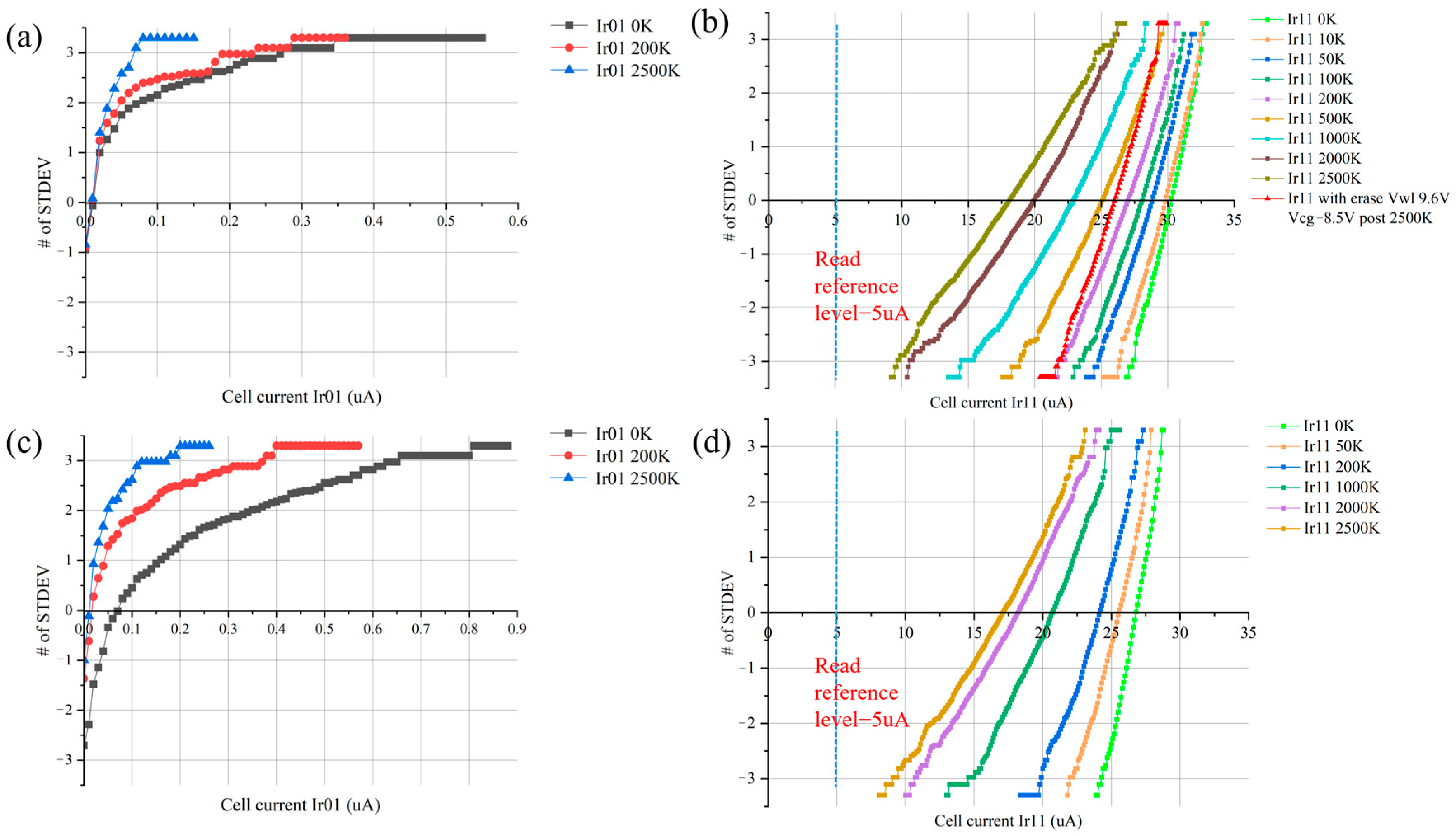

3.1. High Endurance Performance

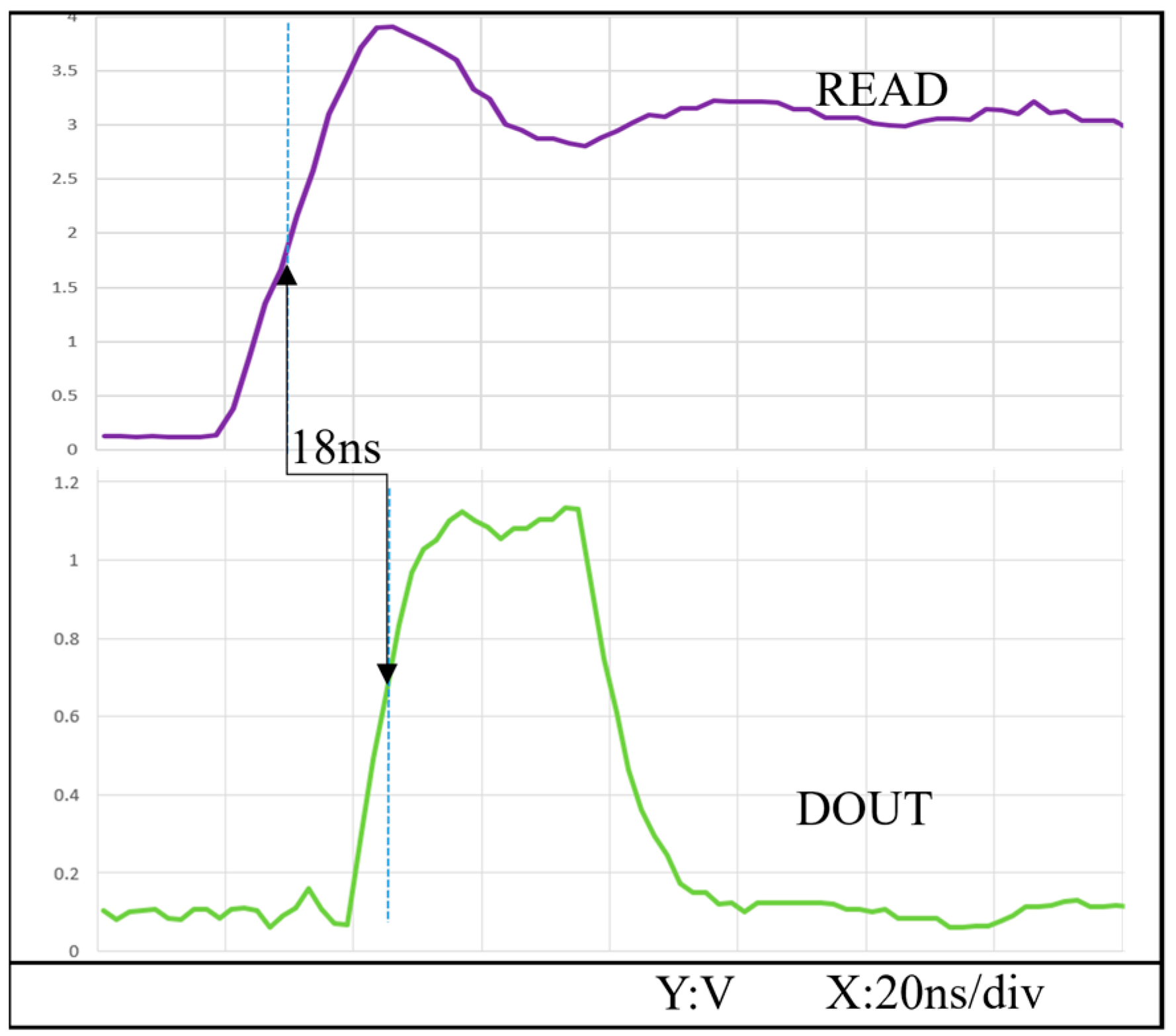

3.2. High-Speed Reading Performance

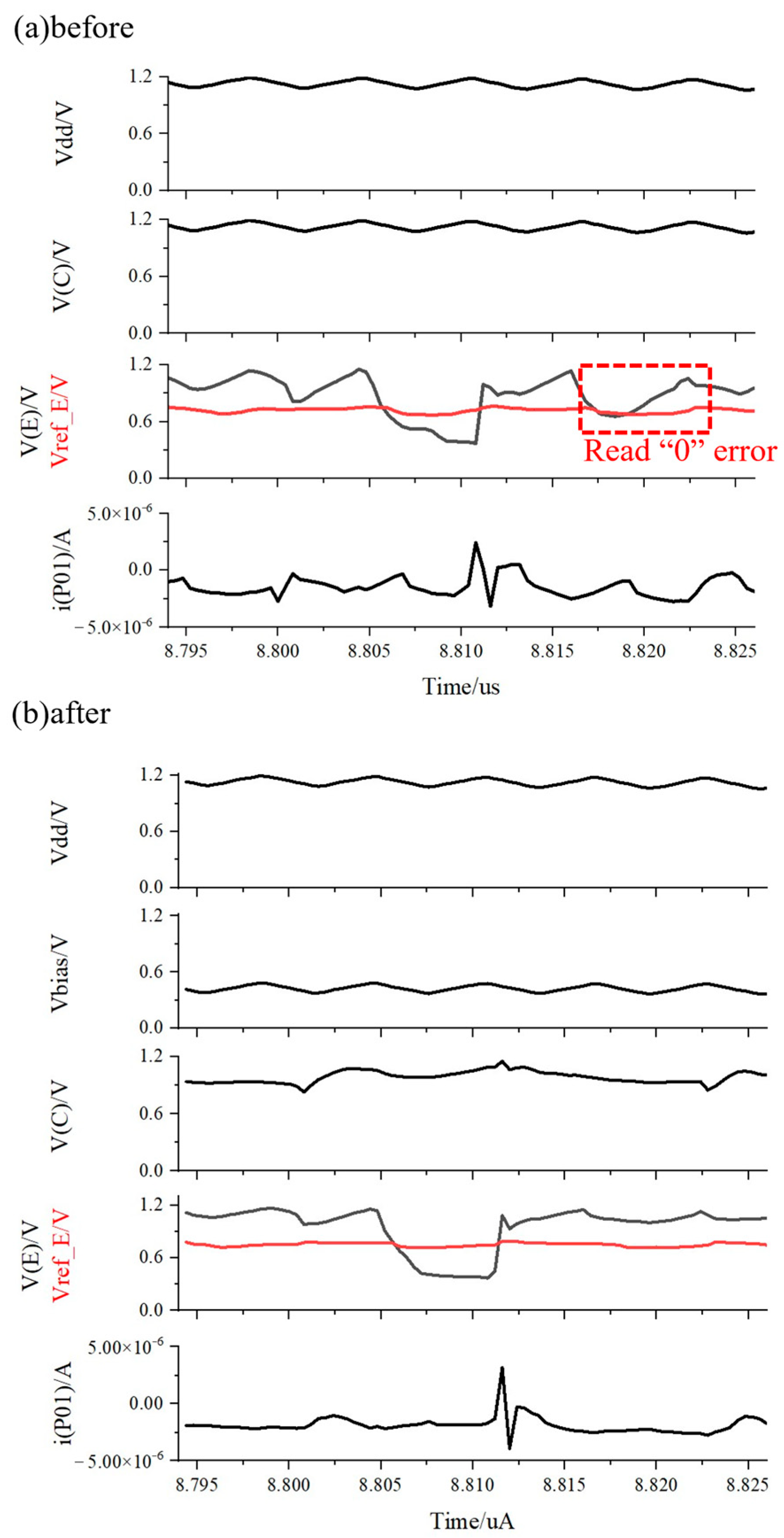

3.3. High Noise Immunity Performance

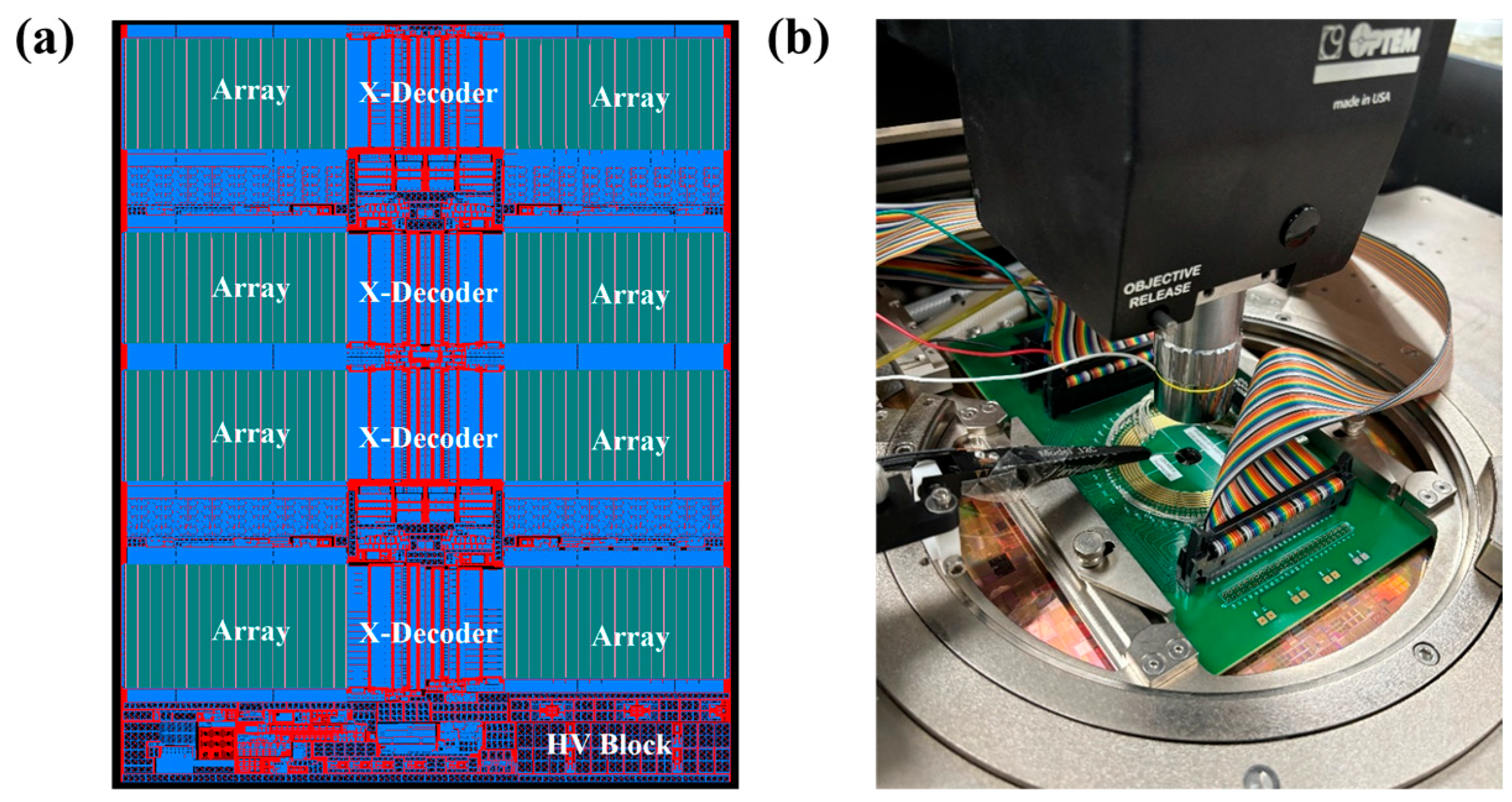

3.4. Full-Chip Measurement and Comparison Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Masuoka, F.; Asano, M.; Iwahashi, H.; Komuro, T.; Tanaka, S. A new Flash EEPROM cell using triple polysilicon technology. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 9–12 December 1984; pp. 464–467. [Google Scholar]

- Chen, Y.T. SST SuperFlash Modeling and Simulation Under Ionizing Radiation; Master of Science, Arizona State University: Tempe, AZ, USA, 2016. [Google Scholar]

- Kartiwa, G.M.; Hendrayana, Y.H.; Prihatiningrum, N.; Sulthoni, M.A.; Surawijaya, A.; Idris, I. Effect of Lsg/Lfg ratio variation to the IV curve of split-gate 1st generation superFlash. In Proceedings of the International Symposium on Electronics and Smart Devices (ISESD), Yogyakarta, Indonesia, 17–19 October 2017; pp. 264–267. [Google Scholar]

- Verma, G.; Mielke, N. Reliability performance of ETOX based Flash memories. In Proceedings of the 26th Annual Proceedings Reliability Physics Symposium, Monterey, CA, USA, 12–14 April 1988; pp. 158–166. [Google Scholar]

- Atwood, G. Future Directions and Challenges for Etox Flash Memory Scaling. Device Mater. Reliab. IEEE Trans. 2004, 4, 301–305. [Google Scholar] [CrossRef]

- Yeh, B. Single Transistor Non-Volatile Electrically Alterable Semiconductor Memory Device. U.S. Patent 5,029,130, 2 July 1991. [Google Scholar]

- Kianian, S.; Levi, A.; Lee, D.; Hu, Y. A novel 3 volts-only, small sector erase, high density Flash E/sup 2/PROM. In Proceedings of the VLSI Technology Symposium, Honolulu, HI, USA, 7–9 June 1994; pp. 71–72. [Google Scholar]

- Chandra, Z.; Mubarokah, I.; Sulthoni, M.A. Split-Gate Flash Memory: From Planar to 3D. In Proceedings of the International Symposium on Electronics and Smart Devices (ISESD), Bandung, Indonesia, 29–30 June 2021; pp. 1–5. [Google Scholar]

- Dong, Y.Q.; Kong, W.R.; Nhan, D.; Wang, S.L.; Lee, G. Erase voltage impact on 0.18 µm triple self-aligned split-gate Flash memory endurance. Semiconductors 2010, 31, 064012. [Google Scholar]

- Do, N.; Van Tran, H.; Kotov, A.; Tiwari, V. Split-Gate Floating Poly SuperFlash® Memory Technology, Design, and Reliability. In Embedded Flash Memory for Embedded Systems: Technology, Design for Sub-Systems, and Innovations, 1st ed.; Hidaka, H., Ed.; Springer: Cham, Switzerland, 2018; Volume 5, pp. 131–178. [Google Scholar]

- Liu, X.; Markov, V.; Kotov, A.; Dang, T.; Levi, A. Endurance Characteristics of SuperFlash® Memory. In Proceedings of the International Conference on Solid-State and Integrated Circuit Technology (ICSSCIT), Shanghai, China, 23–26 October 2006; pp. 763–765. [Google Scholar]

- Zhang, S.B.; Xiao, J.; Yang, G.J.; Hu, J.; Huang, M.Y.; Zou, S.C. A 1.35-V 16-Mb Twin-Bit-Cell Virtual-Ground-Architecture Embedded Flash Memory with a Sensing Current Protection Technique. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 2862–2868. [Google Scholar] [CrossRef]

- Bez, R.; Camerlenghi, E.; Modelli, A.; Visconti, A. Introduction to Flash memory. Proc. IEEE 2003, 91, 489–502. [Google Scholar] [CrossRef]

- Strenz, R. Review and Outlook on Embedded NVM Technologies-From Evolution to Revolution. In Proceedings of the IEEE International Memory Workshop (IMW), Dresden, Germany, 17–20 May 2020; pp. 1–4. [Google Scholar]

- Yasuhiko, T.; Masaya, N.; Hiromi, O.; Daisuke, O.; Takashi, I.; Takashi, K.; Kenji, N.; Hideto, H.; Tadaaki, Y. A 28nm embedded SG-MONOS Flash macro for automotive achieving 200MHz read operation and 2.0MB/S write throughput at Ti, of 170 °C. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 22–26 February 2015. [Google Scholar]

- Kadowaki, T.; Yamakawa, Y.; Nakamura, H.; Kimura, Y.; Niwano, M.; Masuoka, F. A New Architecture for High-Density High-Performance SGT nor Flash Memory. IEEE Trans. Circuits Syst. II Express Briefs 2008, 55, 551–555. [Google Scholar] [CrossRef]

- Kobayashi, K.; Nakayama, T.; Miyawaki, Y.; Hayashikoshi, M.; Terada, Y.; Yoshihara, T. A high-speed parallel sensing architecture for multi-megabit Flash EEPROMs. IEEE J. Solid-State Circuits 1990, 25, 551–555. [Google Scholar] [CrossRef]

- Yan, R.H.; Monroe, D.; Weis, J.; Mujtaba, A.; Westerwick, E. Reducing operating voltage from 3, 2 to 1 volt and below-challenges and guidelines for possible solutions [CMOS]. In Proceedings of the International Electron Devices Meetings, Washington, DC, USA, 10–13 December 1995. [Google Scholar]

- Kang, D.; Shin, H. Improving the cell characteristics using arch-active profile in NAND Flash memory having 60nm design rule. In Proceedings of the IEEE Silicon Nano-Electronics Workshop, Honolulu, HI, USA, 15–16 June 2008; pp. 1–2. [Google Scholar]

- Fang, L.; Gu, J.; Zhang, B.; Kong, W.R.; Zou, S.C. A Highly Reliable 2-bits/cell Split- Gate Flash Memory Cell with A New Program-Disturbs Immune Array Configuration. Electron. Devices IEEE Trans. 2014, 61, 2350–2356. [Google Scholar]

- Xu, Y.R.; Zhu, W.Y.; Xiao, J.; Yang, G.J.; Hu, J.; Zhang, S.B.; Huang, M.Y.; Kong, W.R.; Zou, S.C. A 280-KBytes Twin-Bit-Cell Embedded NOR Flash Memory with a Novel Sensing Current Protection Enhanced Technique and High-Voltage Generating Systems. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1569–1573. [Google Scholar] [CrossRef]

- Zhang, Y.; Wang, Z.; Zhu, C.; Zhang, L. 28-nm Latch-Type Sense Amplifier Modification for Coupling Suppression. IEEE Trans. Very Large-Scale Integr. (VLSI) Syst. 2017, 25, 1767–1773. [Google Scholar] [CrossRef]

- Xu, Y.R.; Hu, J.; Xiao, J.; Yang, G.J.; Kong, W.R. Design Techniques for a 30-ns Access Time 1.5-V 200-KB Embedded EEPROM Memory. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 1064–1068. [Google Scholar] [CrossRef]

- Luo, L.Q.; Kong, Y.J.; Deng, F.X.; Qu, X.; Teo, Z.Q.; Liu, J.Q.; Zhang, F.; Cai, X.S.; Tan, K.M.; Lim, K.Y.; et al. 40 nm Embedded Self-Aligned Split-Gate Flash Technology for High-Density Automotive Microcontrollers. In Proceedings of the IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–4. [Google Scholar]

| Selected Bit(s) | Vwl | Vcg1 | Vcg2 | V(S) | V(D) | Time | |

|---|---|---|---|---|---|---|---|

| read | bit 1 | 4 | 0 | 5 | 0 | 0.5 | |

| bit 2 | 4 | 5 | 0 | 0.5 | 0 | ||

| prog | bit 1 | 1.5 | 9 | 5.5 | 5 | Vdp/Iprog | 5 μs |

| bit 2 | 1.5 | 5.5 | 9 | Vdp/Iprog | 5 | 5 μs | |

| erase | 2 bits | 8.5 | −8 | −8 | 0 | 0 | 2 ms |

| Selected Bit(s) | Vwl | Vcg | V(S) | V(D) | Time | |

|---|---|---|---|---|---|---|

| read | used bit | 4 | 0 | 0 | 0.5 | |

| prog | used bit | 1.5 | 9 | 5 | Vdp/Iprog | 5 μs |

| erase | 2 bits | 8.5 | −8 | 0 | 0 | 2 ms |

| ESF3 [24] | This Work | |

|---|---|---|

| Sector Size | 256 × 38 Kbits | 512 KBytes |

| Power Supply | 1.1 V ± 10%; 2.5 V ± 10% | 1.2 V ± 10% |

| Program Time | 10 μs | 5 μs |

| Read access Time | Random 10 ns | 18 ns |

| Sector Erase Time | 10 ms | 2 ms |

| P/E Endurance | ≥100 K | ≥2500 K |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, Y.; Wang, Z.; Yang, G.; Du, T. A 512 KBytes Highly Reliable and High-Speed Embedded NOR Flash Memory. Electronics 2025, 14, 721. https://doi.org/10.3390/electronics14040721

Jiang Y, Wang Z, Yang G, Du T. A 512 KBytes Highly Reliable and High-Speed Embedded NOR Flash Memory. Electronics. 2025; 14(4):721. https://doi.org/10.3390/electronics14040721

Chicago/Turabian StyleJiang, Yinuo, Zhexian Wang, Guangjun Yang, and Tao Du. 2025. "A 512 KBytes Highly Reliable and High-Speed Embedded NOR Flash Memory" Electronics 14, no. 4: 721. https://doi.org/10.3390/electronics14040721

APA StyleJiang, Y., Wang, Z., Yang, G., & Du, T. (2025). A 512 KBytes Highly Reliable and High-Speed Embedded NOR Flash Memory. Electronics, 14(4), 721. https://doi.org/10.3390/electronics14040721