Fabrication and Characterization of Back-Gate and Front-Gate Ge-on-Insulator Transistors for Low-Power Applications

Abstract

1. Introduction

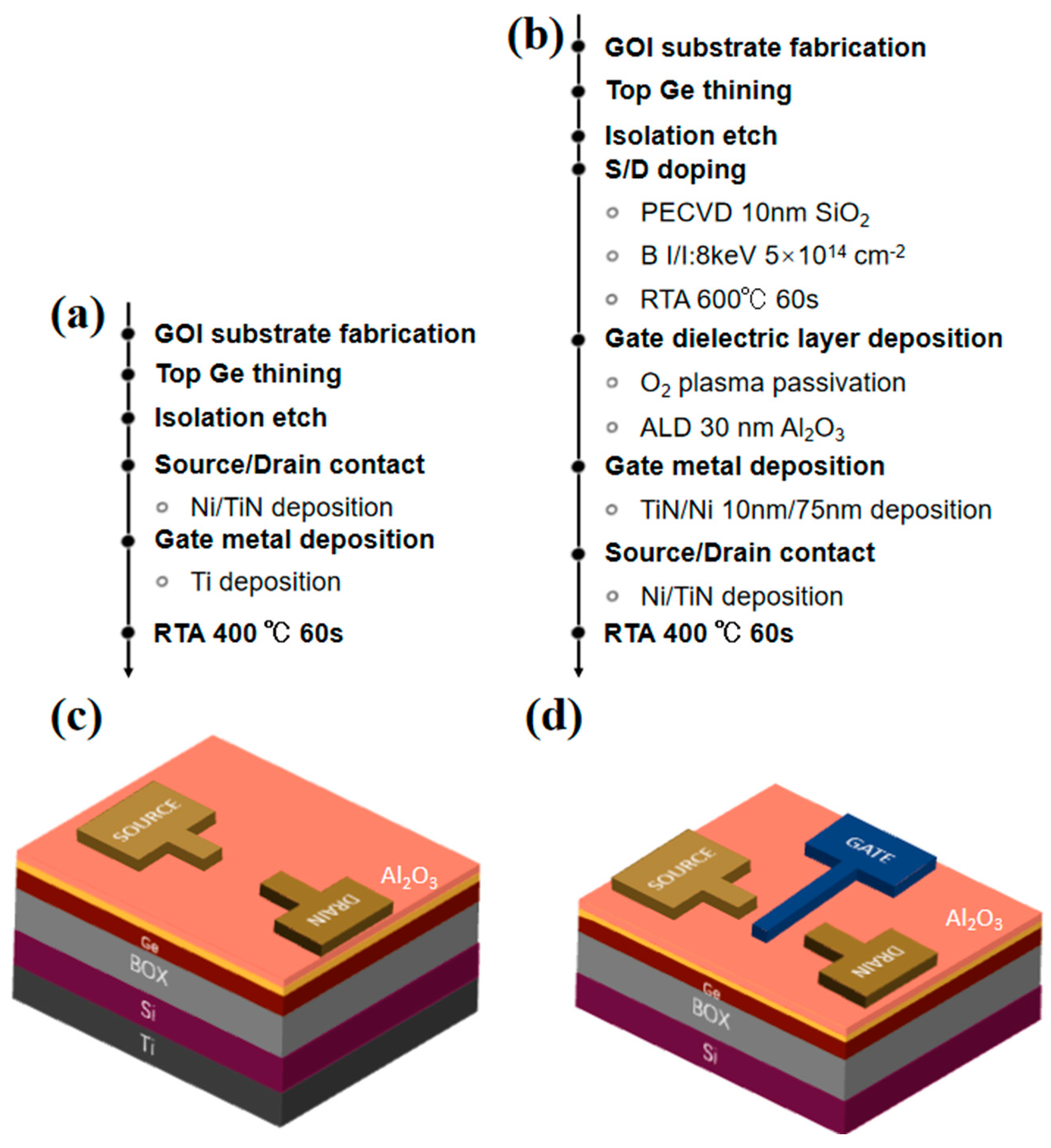

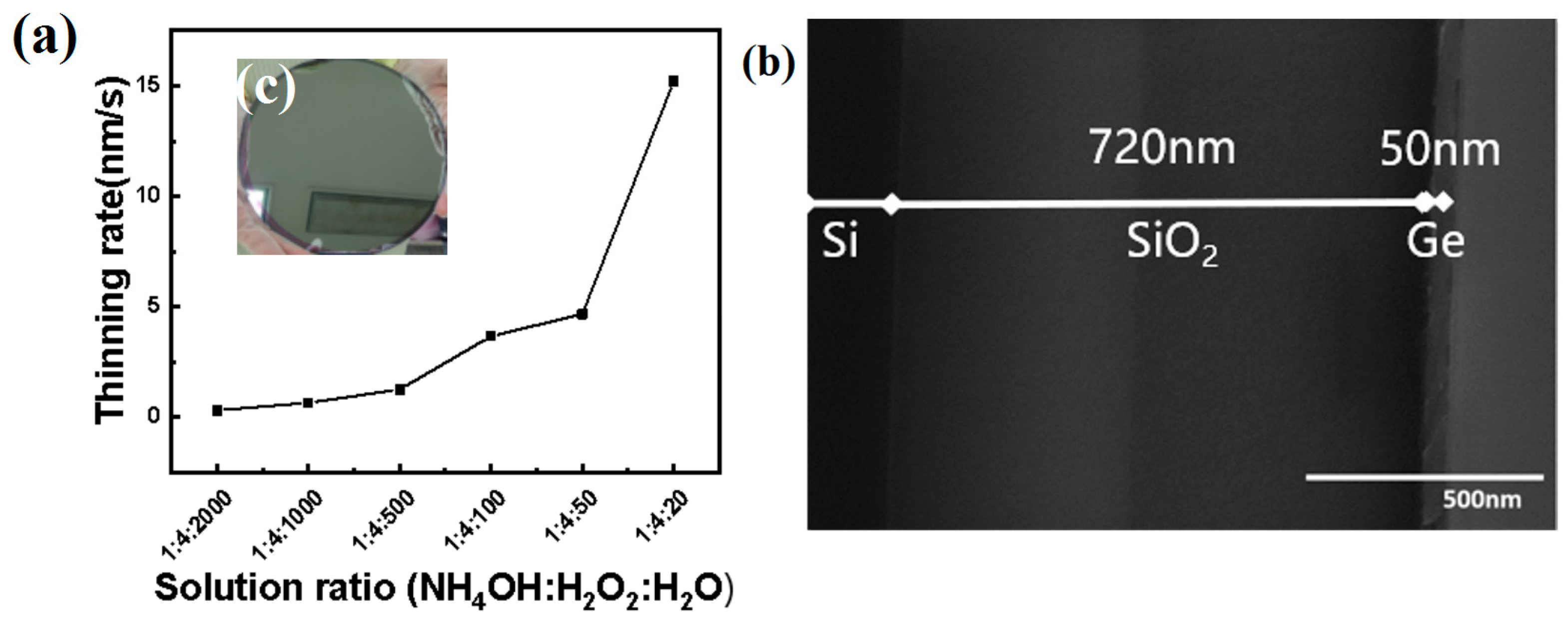

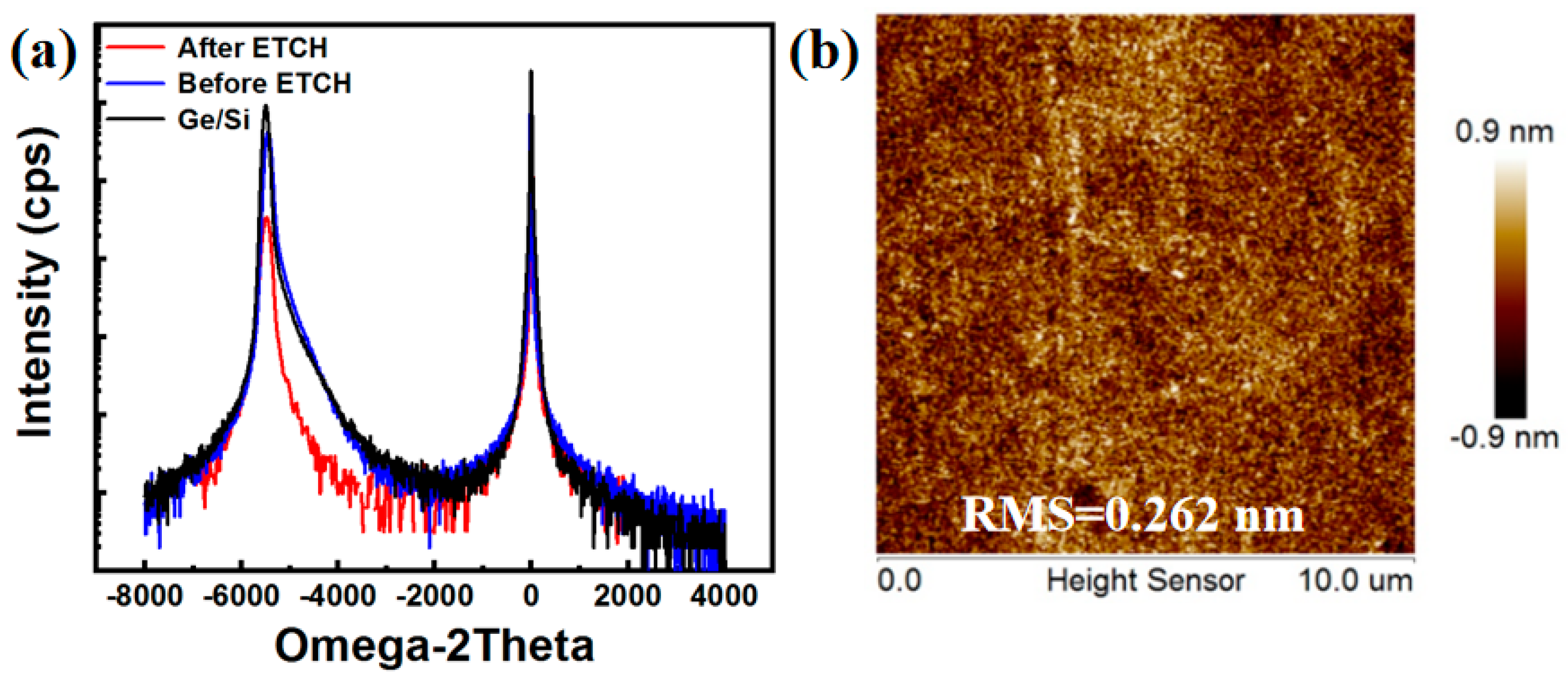

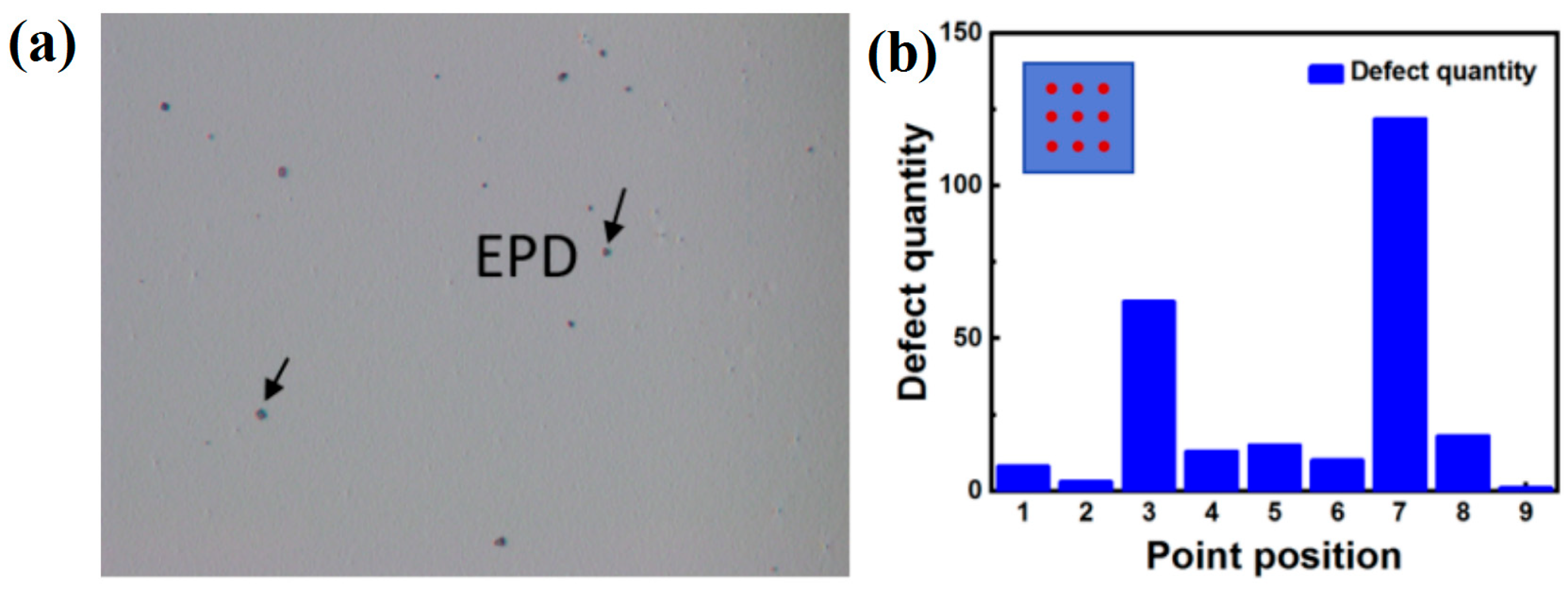

2. Experimental and Characterization Method

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Radamson, H.H. CMOS past, present and future. In Chapter One: Basics of Metal–Oxide–Semiconductor Field-Effect Transistor (MOSFET); Woodhead Publishing: Cambridge, UK, 2018; pp. 1–17. ISBN 9780081021392. [Google Scholar] [CrossRef]

- International Roadmap for Devices and Systems. Available online: https://irds.ieee.org (accessed on 1 October 2025).

- Radamson, H.H.; Miao, Y.; Zhou, Z.; Wu, Z.; Kong, Z.; Gao, J.; Yang, H.; Ren, Y.; Zhang, Y.; Shi, J.; et al. CMOS scaling for the 5 nm node and beyond: Device, process and technology. Nanomaterials 2024, 14, 837. [Google Scholar] [CrossRef] [PubMed]

- Dong, L.; Li, P.; Zhao, Y.; Miao, Y.; Peng, B.; Xin, B.; Liu, W. First-principles study on the electronic properties of layered Ga2O3/TeO2 heterolayers for high-performance electronic devices. Appl. Surf. Sci. 2022, 602, 154382. [Google Scholar] [CrossRef]

- Wang, G.L.; Moeen, M.; Abedin, A.; Gudmundsson, V.; Kolahdouz, M.; Luo, J.; Zhao, C.; Li, J.; Liu, H.; Zhong, Z.X.; et al. Optimization of SiGe selective epitaxy for source/drain engineering in 22 nm node complementary metal-oxide semiconductor (CMOS). J. Appl. Phys. 2013, 114, 123511. [Google Scholar] [CrossRef]

- Radamson, H.H.; Joelsson, K.B.; Ni, W.-X.; Hultman, L.; Hansson, G.V. Characterization of highly boron-doped Si, Si1−xGex and Ge layers by high-resolution transmission electron microscopy. J. Cryst. Growth 1995, 157, 80–84. [Google Scholar] [CrossRef]

- Hu, C. Thin-body FinFET as scalable low voltage transistor. In Proceedings of the Technical Program of 2012 VLSI Technology, System and Application, Hsinchu, Taiwan, 23–25 April 2012; IEEE: Piscataway Township, NJ, USA, 2012; pp. 1–4. [Google Scholar]

- Wang, G.; Luo, J.; Qin, C.; Liang, R.; Xu, Y.; Liu, J.; Li, J.; Yin, H.; Yan, J.; Zhu, H.; et al. Integration of highly strained SiGe in source and drain with HK and MG for 22 nm bulk PMOS transistors. Nanoscale Res. Lett. 2017, 12, 123. [Google Scholar] [CrossRef]

- Lu, B.; Cui, Y.; Guo, A.; Wang, D.; Lv, Z.; Zhou, J.; Miao, Y. Characteristics of InAs/GaSb Line-Tunneling FETs with Buried Drain Technique. IEEE Trans. Electron Devices 2021, 68, 1537–1541. [Google Scholar] [CrossRef]

- Koliopoulou, S.; Dimitrakis, P.; Goustouridis, D.; Normand, P.; Pearson, C.; Petty, M.C.; Radamson, H.; Tsoukalas, D. Metal nano-floating gate memory devices fabricated at low temperature. Microelectron. Eng. 2006, 83, 1563–1566. [Google Scholar] [CrossRef]

- Liu, X.; Hu, H.; Wang, M.; Miao, Y.; Han, G.; Wang, B. Design and theoretical calculation of novel GeSn fully-depleted n-tunneling FET with quantum confinement model for suppression on GIDL effect. Superlattices Microstruct. 2018, 118, 266–274. [Google Scholar] [CrossRef]

- Hållstedt, J.; Hellström, P.-E.; Radamson, H.H. Sidewall transfer lithography for reliable fabrication of nanowires and deca-nanometer MOSFETs. Thin Solid Film. 2008, 517, 117–120. [Google Scholar] [CrossRef]

- Li, P.; Dong, L.; Li, C.; Lu, B.; Yang, C.; Peng, B.; Wang, W.; Miao, Y.; Liu, W. Indium doping-assisted monolayer Ga2O3 exfoliation for performance-enhanced MOSFETs. Nanoscale 2023, 15, 12105–12115. [Google Scholar] [CrossRef]

- Lu, B.; Wang, D.; Cui, Y.; Li, Z.; Chai, G.; Dong, L.; Zhou, J.; Wang, G.; Miao, Y.; Lv, Z.; et al. A Compact Model for Nanowire Tunneling-FETs. IEEE Trans. Electron Devices 2022, 69, 419–426. [Google Scholar] [CrossRef]

- Lu, B.; Chang, L.; Ahmed, S.; Wang, H.; Bell, S.; Yang, C.-Y.; Tabery, C.; Ho, C.; Xiang, Q.; King, T.-J.; et al. FinFET scaling to 10 nm gate length. In Proceedings of the IEEE International Electron Devices Meeting Technical Digest, San Francisco, CA, USA, 8–11 December 2002; pp. 251–254. [Google Scholar]

- Hållstedt, J.; Isheden, C.; Östling, M.; Baubinas, R.; Matukas, J.; Palenskis, V.; Radamson, H.H. Application of selective epitaxy for formation of ultra shallow SiGe-based junctions. Mater. Sci. Eng. B 2004, 114–115, 180–183. [Google Scholar] [CrossRef]

- Hållstedt, J.; Kolahdouz, M.; Ghandi, R.; Radamson, H.H.; Wise, R. Pattern dependency in selective epitaxy of B-doped SiGe layers for advanced metal oxide semiconductor field effect transistors. J. Appl. Phys. 2008, 103, 054907. [Google Scholar] [CrossRef]

- Grenouillet, L.; Liu, Q. UTBB FDSOI scaling enablers for the 10 nm node. In Proceedings of the 2013 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Monterey, CA, USA, 7–10 October 2013. [Google Scholar]

- Kolahdouz, M.; Hållstedt, J.; Östling, M.; Wise, R.; Radamson, H.H. Selective Epitaxial Growth with Full Control of Pattern Dependency Behavior for pMOSFET Structures. J. Electrochem. Soc. 2009, 156, H169. [Google Scholar] [CrossRef]

- Ren, Y.; Ke, J.; Lin, H.; Zhao, X.; Kong, Z.; Liang, R.; Xu, J.; Lu, B.; Miao, Y.; Radamson, H.H. Fabrication and characterization of ferroelectric junctionless GOI and GeSnOI transistors for low-power applications. J. Mater. Sci. Mater. Electron. 2025, 36, 148. [Google Scholar] [CrossRef]

- Ohori, D.; Fujii, T.; Noda, S.; Mizubayashi, W.; Endo, K.; Lee, Y.-J.; Tarng, J.-H.; Li, Y.; Samukawa, S. High Electron Mobility Germanium FinFET Fabricated by Atomic Layer Defect-Free and Roughness-Free Etching. IEEE Open J. Nanotechnol. 2021, 2, 26–30. [Google Scholar] [CrossRef]

- El-Aassar, O.; Rebeiz, G.M. A Stacked-Complementary 5 GHz Oscillator with Even-Only Differential Harmonic Shaping Achieving −150 dBc/Hz Phase Noise at 10-MHz Offset Using Body-Biased Thin-Oxide 22-nm FDSOI. IEEE Solid-State Circuits Lett. 2020, 3, 98–101. [Google Scholar] [CrossRef]

- Li, Z.; Elash, C.; Jin, C.; Chen, L.; Wen, S.-J.; Fung, R.; Xing, J.; Shi, S.; Yang, Z.W.; Bhuva, B.L. Efficacy of Transistor Stacking on Flip-Flop SEU Performance at 22-nm FDSOI Node. IEEE Trans. Nucl. Sci. 2023, 70, 596–602. [Google Scholar] [CrossRef]

- Fenouillet-Beranger, C. Efficient multi Vt FDSOI technology with UTBOX for low power circuit design. In Symposium on VLSI Technology; IEEE: Piscataway Township, NJ, USA, 2010; pp. 65–66. [Google Scholar] [CrossRef]

- Skotnicki, T. Competitive SOC with UTBB SOI. In Proceedings of the Soi Conference, Tempe, AZ, USA, 3–6 October 2011; pp. 1–61. [Google Scholar] [CrossRef]

- Liu, Q.; Yagishita, A.; Loubet, N.; Khakifirooz, A.; Kulkarni, P.; Yamamoto, T.; Cheng, K.; Fujiwara, M.; Cai, J.; Dorman, D.; et al. Ultra-thin-body and BOX (UTBB) fully depleted (FD) device integration for 22 nm node and beyond. In Proceedings of the 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; p. 61. [Google Scholar] [CrossRef]

- Fischer, A.C.; Belova, L.M.; Rikers, Y.G.M.; Malm, B.G.; Radamson, H.H.; Kolahdouz, M.; Gylfason, K.B.; Stemme, G.; Niklaus, F. 3D Free-Form Patterning of Silicon by Ion Implantation, Silicon Deposition, and Selective Silicon Etching. Adv. Funct. Mater. 2012, 22, 4004. [Google Scholar] [CrossRef]

- Grenouillet, L.; Gimbert, J. UTBB FDSOI transistors with dual STI and shrinked back gate architecture for a multi-VT strategy at 20 nm node and below. In Proceedings of the Technical Digest of International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 3.6.1–3.6.4. [Google Scholar] [CrossRef]

- Kim, S.; Park, H.; Choi, E.; Kim, Y.H.; Kim, D.; Shim, H.; Chung, S.; Jung, P. Reliability Assessment of 3 nm GAA Logic Technology Featuring Multi-Bridge-Channel FETs. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–8. [Google Scholar] [CrossRef]

- Lu, B.; Wang, D.-W.; Chen, Y.-L.; Cui, Y.; Miao, Y.-H.; Dong, L.-P. Capacitance model for nanowire gate-all-around tunneling field-effect-transistors. Acta Phys. Sin. 2021, 70, 218501. [Google Scholar] [CrossRef]

- Weckx, P.; Ryckaert, J.; Litta, E.D.; Yakimets, D.; Matagne, P.; Schuddinck, P.; Jang, D.; Chehab, B.; Baert, R.; Gupta, M.; et al. Novel forksheet device architecture as ultimate logic scaling device towards 2 nm. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 36.5.1–36.5.4. [Google Scholar] [CrossRef]

- Li, J.; Wang, W.; Li, Y.; Zhou, N.; Wang, G.; Kong, Z.; Fu, J.; Yin, X.; Li, C.; Wang, X.; et al. Study of selective isotropic etching Si1−xGex in process of nanowire transistors. J. Mater. Sci. Mater. Electron. 2020, 31, 134–143. [Google Scholar] [CrossRef]

- Chen, Y.-R.; Tu, C.-T.; Zhao, Z.; Liu, Y.-C.; Huang, B.-W.; Xing, Y.; Chen, G.-H.; Liu, C.W. Stacked Two Ge0.98Si0.02 Nanowire nFETs with High- κ Dielectrics Featuring High ION per Footprint of 4800 μA/μm at VOV = VDS = 0.5V. In Proceedings of the 2023 International VLSI Symposium on Technology, Systems and Applications (VLSI-TSA/VLSI-DAT), HsinChu, Taiwan, 17–20 April 2023; pp. 1–2. [Google Scholar] [CrossRef]

- Lin, H.; Zhao, X.; Luo, X.; Miao, Y.; Zhang, Y.; Kong, Z.; Wang, G.; Yang, H.; Wu, Z.; Shi, Y.; et al. High performance junctionless FDSOI SiGe channel p-FinFET with high ION/IOFF ratio and excellent SS. Mater. Sci. Semicond. Process. 2024, 171, 108007. [Google Scholar] [CrossRef]

- Zhang, Q.; Gu, J.; Xu, R.; Cao, L.; Li, J.; Wu, Z.; Wang, G.; Yao, J.; Zhang, Z.; Xiang, J.; et al. Optimization of Structure and Electrical Characteristics for Four-Layer Vertically-Stacked Horizontal Gate-All-Around Si Nanosheets Devices. Nanomaterials 2021, 3, 646. [Google Scholar] [CrossRef] [PubMed]

- Wu, H.; Wu, W.; Si, M.; Ye, P.D. First demonstration of Ge nanowire CMOS circuits: Lowest SS of 64 mV/dec, highest gmax of 1057 μS/μm in Ge nFETs and highest maximum voltage gain of 54 V/V in Ge CMOS inverters. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; IEEE: Piscataway Township, NJ, USA, 2015; pp. 2.1.1–2.1.4. [Google Scholar]

- Gomez, L.; Chléirigh, C.N.; Hashemi, P.; Hoyt, J.L. Enhanced Hole Mobility in High Ge Content Asymmetrically Strained-SiGe p-MOSFETs. IEEE Electron Device Lett. 2010, 31, 782–784. [Google Scholar] [CrossRef]

- Ni, W.-X.; Ekberg, J.O.; Joelsson, K.B.; Radamson, H.H.; Henry, A.; Shen, G.-D.; Hansson, G.V. A silicon molecular beam epitaxy system dedicated to device-oriented material research. J. Cryst. Growth 1995, 157, 285–294. [Google Scholar] [CrossRef]

- Wan, P.; Zhang, B.; Ran, Y.; Zheng, S.; Li, Y.; Zhou, J.; Liang, J. Si–Ge Axial Heterojunction RFET with Enhanced On-State Current and Low Subthreshold Swing. IEEE Trans. Electron Devices 2025, 72, 2640–2646. [Google Scholar] [CrossRef]

- Radamson, H.H.; Noroozi, M.; Jamshidi, A.; Thompson, P.E.; Östling, M. Strain engineering in GeSnSi materials. ECS Trans. 2013, 50, 527. [Google Scholar] [CrossRef]

- Wirths, S.; Buca, D.; Mussler, G.; Tiedemann, A.T.; Holländer, B.; Bernardy, P.; Stoica, T.; Grutzmacher, T.; Mantl, S. Reduced pressure CVD growth of Ge and Ge1−xSnx alloys. ECS J. Solid State Sci. Tech. 2013, 2, N99. [Google Scholar] [CrossRef]

- Hassein-Bey, A.; Cristoloveanu, S. Simulation of Interface Coupling and Short-Channel Effects in Fully-Depleted Soi Mosfet’s. In Proceedings of the 1992 IEEE International SOI Conference, Ponte Vedra Beach, FL, USA, 6–8 October 1992; pp. 68–69. [Google Scholar] [CrossRef]

- Colinge, J.-P.; Lee, C.-W.; Afzalian, A.; Akhavan, N.D.; Yan, R.; Ferain, I.; Razavi, P.; O’Neill, B.; Blake, A.; White, M.; et al. Nanowire transistors without junctions. Nat. Nanotechnol. 2010, 5, 225–229. [Google Scholar] [CrossRef]

- Loo, R.; Shimura, Y.; Ike, S.; Vohra, A.; Stoica, T.; Stange, D.; Buca, D.; Kohen, D.; Margetis, J.; Tolle, J. Epitaxial GeSn: Impact of process conditions on material quality. Semicond. Sci. Technol. 2018, 33, 114010. [Google Scholar] [CrossRef]

- Grant, P.C.; Dou, W.; Alharthi, B.; Grant, J.M.; Tran, H.; Abernathy, G.; Mosleh, A.; Du, W.; Li, B.; Mortazavi, M.; et al. UHV-CVD Growth of High Quality GeSn Using SnCl4: From Growth Optimization to Prototype Devices. arXiv 2018, arXiv:1810.02523. [Google Scholar]

- Zhao, D.D.; Nishimura, T.; Lee, C.H.; Nagashio, K.; Kita, K.; Toriumi, A. Junctionless Ge p-channel metal–oxide–semiconductor field-effect transistors fabricated on ultrathin Ge-on-insulator substrate. Appl. Phys. Express 2011, 4, 031302. [Google Scholar] [CrossRef]

- Chou, C.P.; Lin, Y.X.; Huang, Y.K.; Chan, C.Y.; Wu, Y.H. Junctionless Poly-GeSn Ferroelectric TFTs with Improved Reliability by Interface Engineering for Neuromorphic Computing. ACS Appl. Mater. Interfaces 2019, 12, 1014–1023. [Google Scholar] [CrossRef] [PubMed]

- Chen, D.; Xue, Z.; Wei, X.; Wang, G.; Ye, L.; Zhang, M.; Wang, D.; Liu, S. Ultralow temperature ramping rate of LT to HT for the growth of high quality Ge epilayer on Si (100) by RPCVD. Appl. Surf. Sci. 2014, 299, 1–5. [Google Scholar] [CrossRef]

- Chong, H.; Wang, Z.; Chen, C.; Xu, Z.; Wu, K.; Wu, L.; Xu, B.; Ye, H. Optimization of hetero-epitaxial growth for the threading dislocation density reduction of germanium epilayers. J. Cryst. Growth 2018, 488, 8–15. [Google Scholar] [CrossRef]

- Kong, Z.; Wang, G.; Liang, R.; Su, J.; Xun, M.; Miao, Y.; Gu, S.; Li, J.; Cao, K.; Lin, H.; et al. Growth and strain modulation of GeSn alloys for photonic and electronic applications. Nanomaterials 2022, 12, 981. [Google Scholar] [CrossRef]

- Moto, K.; Yamamoto, K.; Imajo, T.; Suemasu, T.; Nakashima, H.; Toko, K. Sn Concentration Effects on Polycrystalline GeSn Thin Film Transistors. IEEE Electron. Device Lett. 2021, 42, 1735–1738. [Google Scholar] [CrossRef]

- Moto, K.; Yamamoto, K.; Imajo, T.; Suemasu, T.; Nakashima, H.; Toko, K. Polycrystalline thin-film transistors fabricated on high-mobility solid-phase-crystallized Ge on glass. Appl. Phys. Lett. 2019, 114, 212107. [Google Scholar] [CrossRef]

- Menon, C.; Bentzen, A.; Radamson, H.H. Loading effect in SiGe layers grown by dichlorosilane- and silane-based epitaxy Available to Purchase. J. Appl. Phys. 2001, 90, 4805–4809. [Google Scholar] [CrossRef]

- Kang, Y.; Xu, S.; Han, K.; Kong, E.Y.-J.; Song, Z.; Luo, S.; Kumar, A.; Wang, C.; Fan, W.; Liang, G.; et al. Ge0.95Sn0.05 Gate-All-Around p-Channel Metal-Oxide-Semiconductor Field-Effect Transistors with Sub-3 nm Nanowire Width. Nano Lett. 2021, 21, 5555–5563. [Google Scholar] [CrossRef] [PubMed]

- Vincent, B.; Gencarelli, F.; Bender, H.; Merckling, C.; Douhard, C.; Petersen, D.H.; Hansen, O.; Henrichsen, H.; Meersschaut, J.; Caymax, M.; et al. Undoped and in-situ B doped GeSn epitaxial growth on Ge by atmospheric pressure-chemical vapor deposition. Appl. Phys. Lett. 2011, 99, 152103. [Google Scholar] [CrossRef]

- Yang, J.; Hu, H.; Miao, Y.; Dong, L.; Wang, B.; Wang, W.; Su, H.; Xuan, R.; Zhang, H. High-quality GeSn layer with Sn composition up to 7% grown by low-temperature magnetron sputtering for optoelectronic application. Materials 2019, 12, 2662. [Google Scholar] [CrossRef]

- Radamson, H.H.; Kolahdouz, M. Selective epitaxy growth of Si1-xGex layers for MOSFETs and FinFET. J. Mater. Sci. Mater. Electron. 2015, 26, 4584–4603. [Google Scholar] [CrossRef]

- Margetis, J.; Mosleh, A.; Al-Kabi, S.; Ghetmiri, S.A.; Du, W.; Dou, W.; Benamara, M.; Li, B.; Mortazavi, M.; Naseem, H.A.; et al. Study of low-defect and strain-relaxed GeSn growth via reduced pressure CVD in H2 and N2 carrier gas. J. Cryst. Growth 2017, 463, 128–133. [Google Scholar] [CrossRef]

- Miao, Y.; Wang, Y.; Hu, H.; Liu, X.; Su, H.; Zhang, J.; Yang, J.; Tang, Z.; Wu, X.; Song, J.; et al. Characterization of crystalline GeSn layer on tensile-strained Ge buffer deposited by magnetron sputtering. Mater. Sci. Semicond. Process. 2018, 85, 134–140. [Google Scholar] [CrossRef]

- Du, Y.; Kong, Z.; Toprak, M.S.; Wang, G.; Miao, Y.; Xu, B.; Yu, J.; Li, B.; Lin, H.; Han, J.; et al. Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD. Nanomaterials 2021, 11, 928. [Google Scholar] [CrossRef]

- Miao, Y.; Wang, G.; Kong, Z.; Xu, B.; Zhao, X.; Luo, X.; Lin, H.; Dong, Y.; Lu, B.; Dong, L.; et al. Review of Si-Based GeSn CVD Growth and Optoelectronic Applications. Nanomaterials 2021, 11, 2556. [Google Scholar] [CrossRef] [PubMed]

- Al-Kabi, S.; Ghetmiri, S.A.; Margetis, J.; Du, W.; Mosleh, A.; Dou, W.; Sun, G.; Soref, R.; Tolle, J.; Yu, S.Q.; et al. Study of High-Quality GeSn Alloys Grown by Chemical Vapor Deposition towards Mid-Infrared Applications. J. Electron. Mater. 2016, 45, 6251–6257. [Google Scholar] [CrossRef]

- Malta, P.D.; Posthill, B.J.; Markunas, J.R.; Humphreys, T.P. Low-defect-density germanium on silicon obtained by a novel growth phenomenon. Appl. Phys. Lett. 1992, 60, 844. [Google Scholar] [CrossRef]

- Kil, Y.-H.; Yang, J.-H.; Kang, S.; Kim, D.-J.; Jeong, T.S.; Choi, C.-J.; Kim, T.S.; Shim, K.-H. Growth of a Ge layer on 8in. Si (100) substrates by rapid thermal chemical vapor deposition. Mater. Sci. Semicond. Process. 2014, 21, 58–65. [Google Scholar] [CrossRef]

- Kil, Y.-H.; Yuk, S.-H.; Kim, J.H.; Kim, T.S.; Kim, Y.T.; Choi, C.-J.; Shim, K.-H. The low temperature epitaxy of Ge on Si (100) substrate using two different precursors of GeH4 and Ge2H6. Solid-State Electron. 2016, 124, 35–41. [Google Scholar] [CrossRef]

- Radamson, H.H. X-Ray Techniques. In Analytical Methods and Instruments for Micro- and Nanomaterials; Springer International Publishing: Berlin/Heidelberg, Germany, 2023; pp. 3–53. [Google Scholar] [CrossRef]

- Hansson, G.V.; Radamsson, H.H.; Ni, W.X. Strain and relaxation in Si-MBE structures studied by reciprocal space mapping using high resolution X-ray diffraction. J. Mater. Sci. Mater. Electron. 1995, 6, 292–297. [Google Scholar] [CrossRef]

- Nur, O.; Willander, M.; Radamson, H.H.; Sardela, M.R., Jr.; Hansson, G.V.; Petersson, C.S.; Maex, K. Strain characterization of CoSi2/n-Si0.9Ge0.1/p-Si heterostructures. Appl. Phys. Lett. 1994, 64, 440–442. [Google Scholar] [CrossRef]

- Stavitski, N.; van Dal, M.J.H.; Lauwers, A.; Vrancken, C.; Kovalgin, A.Y.; Wolters, R.A.M. Systematic TLM Measurements of NiSi and PtSi Specific Contact Resistance to n- and p-Type Si in a Broad Doping Range. IEEE Electron Device Lett. 2008, 29, 378–381. [Google Scholar] [CrossRef]

- Nur, O.; Willander, M.; Hultman, L.; Radamson, H.H.; Hansson, G.V.; Sardela, M.R., Jr.; Greene, J.E. CoSi2/Si1−xGex/Si(001) heterostructures formed through different reaction routes: Silicidation-induced strain relaxation, defect formation, and interlayer diffusion. J. Appl. Phys. 1995, 78, 7063. [Google Scholar] [CrossRef]

- Ha, J. The effect of carbon and germanium on phase transformation of nickel on Si1−x−yGexCy epitaxial layers. J. Appl. Phys. 2004, 95, 2397–2402. [Google Scholar] [CrossRef]

- Miyoshi, H.; Ueno, T.; Akiyama, K.; Hirota, Y.; Kaitsuka, T. In-Situ contact formation for ultra-low contact resistance NiGe using carrier activation enhancement (CAE) techniques for Ge CMOS. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar] [CrossRef]

- Hu, C.; Xu, P.; Fu, C.; Zhu, Z.; Gao, X.; Jamshidi, A.; Noroozi, M.; Radamson, H.; Wu, D.; Zhang, S.-L. Characterization of Ni(Si,Ge) films on epitaxial SiGe(100) formed by microwave annealing. Appl. Phys. Lett. 2012, 101, 092101. [Google Scholar] [CrossRef]

- Majumdar, K.; Vivekanand, S.; Huffman, C.; Matthews, K.; Ngai, T.; Chen, C.H.; Baek, R.H.; Loh, W.Y.; Rodgers, M.; Stamper, H.; et al. STLM: A Sidewall TLM Structure for Accurate Extraction of Ultralow Specific Contact Resistivity. IEEE Electron Device Lett. 2013, 34, 1082–1084. [Google Scholar] [CrossRef]

- Yang, J.; Hu, H.; Miao, Y.; Wang, B.; Wang, W.; Su, H.; Ma, Y. Single-crystalline GePb alloys formed by rapid thermal annealing-induced epitaxy. J. Phys. D Appl. Phys. 2020, 53, 265105. [Google Scholar] [CrossRef]

- Smith, C.E.; Adhikari, H.; Lee, S.-H.; Coss, B.; Parthasarathy, S.; Young, C.; Sassman, B.; Cruz, M.; Hobbs, C.; Majhi, P.; et al. Dual channel FinFETs as a single high-k/metal gate solution beyond 22 nm node. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Xu, B.; Du, Y.; Wang, G.; Xiong, W.; Kong, Z.; Zhao, X.; Miao, Y.; Wang, Y.; Lin, H.; Su, J.; et al. Dual-Step Selective Homoepitaxy of Ge with Low Defect Density and Modulated Strain Based on Optimized Ge/Si Virtual Substrate. Materials 2022, 15, 3594. [Google Scholar] [CrossRef]

- Tang, X.; Reckinger, N.; Larrieu, G.; Dubois, E.; Flandre, D.; Raskin, J.-P.; Nysten, B.; Jonas, A.M.; Bayot, V. Characterization of ultrathin SOI film and application to short channel MOSFETs. Nanotechnology 2008, 19, 165703. [Google Scholar] [CrossRef]

- Sun, C.; Liang, R.; Wang, J.; Xu, J. Preparation of Ultrathin Germanium on Insulator Films Using a Wet Etching Process. ECS Solid State Lett. 2015, 4, P43. [Google Scholar] [CrossRef]

- Huygens, I.M.; Gomes, W.P.; Strubbe, K. Etching of germanium in hydrogenperoxide solutions. ECS Trans. 2007, 6, 375. [Google Scholar] [CrossRef]

- Onsia, B.; Conard, T.; De Gendt, S.; Heyns, M.M.; Hoflijk, I.; Mertens, P.W.; Meuris, M.; Raskin, G.; Sioncke, S.; Teerlinck, I.; et al. A Study of the Influence of Typical Wet Chemical Treatments on the Germanium Wafer Surface. Solid State Phenom. 2005, 103–104, 27–30. [Google Scholar] [CrossRef]

- Onsia, B.; Caymax, M.; Conard, T.; De Gendt, S.; De Smedt, F.; Delabie, A.; Gottschalk, C.; Heyns, M.M.; Green, M.; Lin, S.; et al. On the Application of a Thin Ozone Based Wet Chemical Oxide as an Interface for ALD High-k Deposition. Solid State Phenom. 2005, 103–104, 19–22. [Google Scholar] [CrossRef]

- Brunco, D.P.; De Jaeger, B.; Eneman, G.; Mitard, J.; Hellings, G.; Satta, A.; Terzieva, V.; Souriau, L.; Leys, F.E.; Pourtois, G.; et al. Germanium MOSFET devices: Advances in materials understanding, process development, and electrical performance. J. Electrochem. Soc. 2008, 155, H552. [Google Scholar] [CrossRef]

- Itano, M.; Kern, F.W.; Miyashita, M.; Ohmi, T. Particle removal from silicon wafer surface in wet cleaning process. IEEE Trans. Semicond. Manuf. 1993, 6, 258–267. [Google Scholar] [CrossRef]

- Radamson, H.H. CMOS past, present and future. In Chapter Three: Strain Engineering; Woodhead Publishing: Cambridge, UK, 2018; pp. 41–67. ISBN 9780081021392. [Google Scholar] [CrossRef]

- Kolbensen, B.O.; Claeys, C.; Stallhofer, P.; Tardif, F.; Benton, K.; Shaffner, T.J.; Schroder, D.; Kishino, S.; Rai-Choudhury, P. Analytical and Diagnostic Techniques for Semiconductor Materials, Devices, and Processes; The Electrochemical Society: San Francisco, CA, USA, 1999; pp. 173–185. [Google Scholar]

- Takagi, S.; Toriumi, A.; Iwase, M.; Tango, H. On the universality of inversion layer mobility in Si MOSFET’s: Part II-effects of surface orientation. IEEE Trans. Electron Devices 1994, 41, 2363–2368. [Google Scholar] [CrossRef]

- Takagi, S.; Toriumi, A.; Iwase, M.; Tango, H. On the universality of inversion layer mobility in Si MOSFET’s: Part I-effects of substrate impurity concentration. IEEE Trans. Electron Devices 1994, 41, 2357–2362. [Google Scholar] [CrossRef]

- Sun, C.; Liang, R.; Xiao, L.; Liu, L.; Xu, J.; Wang, J. Cryogenic Characteristics of Ge channel Junctionless Nanowire Transistors. In Proceedings of the 2018 IEEE 2nd Electron Devices Technology and Manufacturing Conference (EDTM), Kobe, Japan, 13–16 March 2018; pp. 286–288. [Google Scholar] [CrossRef]

- Van Den Daele, W.; Augendre, E.; Le Royer, C.; Damlencourt, J.-F.; Grandchamp, B.; Cristoloveanu, S. Low-temperature characterization and modeling of advanced GeOI pMOSFETs: Mobility mechanisms and origin of the parasitic conduction. Solid-State Electron. 2010, 54, 205–212. [Google Scholar] [CrossRef]

- Miyawaki, A.; Hayashi, T.; Ghosh, P.; Tanemura, M.; Hayashi, Y.; Tokunaga, T. Low-temperature fabrication and characterization of ion-induced Ge nanostructures. In Proceedings of the 2010 3rd International Nanoelectronics Conference (INEC), Hong Kong, China, 3–8 January 2010; pp. 398–399. [Google Scholar] [CrossRef]

- Sun, C.; Liang, R.; Xiao, L.; Liu, L.; Xu, J.; Wang, J. Effect of traps and defects on high temperature performance of Ge channel junctionless nanowire transistors. AIP Adv. 2017, 7, 075009. [Google Scholar] [CrossRef]

- Zhang, Y.; Lu, T.; Wang, W.; Zhang, Y.; Xu, J.; Luo, C.; Guo, G. Characterization and Modeling of Native MOSFETs Down to 4.2 K. IEEE Trans. Electron Devices 2021, 68, 4267–4273. [Google Scholar] [CrossRef]

- Azarov, A.; Hallén, A.; Radamson, H.H. Electrical Characterization of Semiconductors: I–V, C–V and Hall Measurements. In Analytical Methods and Instruments for Micro- and Nanomaterials; Springer International Publishing: Berlin/Heidelberg, Germany, 2023; pp. 197–240. [Google Scholar] [CrossRef]

- Yu, X.; Kang, J.; Zhang, R.; Takenaka, M.; Takagi, S. Characterization of ultrathin-body Germanium-on-insulator (GeOI) structures and MOSFETs on flipped Smart-Cut™ GeOI substrates. Solid State Electron. 2016, 115, 120–125. [Google Scholar] [CrossRef]

- Zhu, H.; Luo, J.; Zhang, Q.; Yin, H.; Zhong, H.; Zhao, C. FinFETs on insulator with silicided source/drain. In Proceedings of the 2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 16–19 October 2017; pp. 1–2. [Google Scholar] [CrossRef]

- Chen, C.T.; Yokogawa, R.; Toprasertpong, K.; Ogura, A.; Takenaka, M.; Takagi, S. Impact of asymmetric strain on performance of extremely-thin body (100) GOI and (110) SGOI pMOSFETs. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [Google Scholar]

- Mao, S.; Gao, J.; He, X.; Liu, W.; Zhou, N.; Luo, Y.; Cao, L.; Hu, Y.; Zhang, Y.; Liu, J.; et al. Low-temperature (≤ 550 °C) pchannel Schottky barrier SOI FinFETs for monolithic 3D integration. Microelectron. Eng. 2022, 260, 111805. [Google Scholar] [CrossRef]

- Jo, K.-W.; Kim, W.-K.; Takenaka, M.; Takagi, S. Hole Mobility Boosters of (110)-Oriented Extremely Thin Body SiGe-on- Insulator (SGOI) pMOSFETs. IEEE Trans. Electron Devices 2023, 70, 3963–3969. [Google Scholar] [CrossRef]

| Year | Type | W/L (μm) | SS (mV/dec) | ION/IOFF | μeff (cm2/V·s) | Ref. |

|---|---|---|---|---|---|---|

| 2016 | p-Ge-BG | 100/500 | —— | 104 | 350 | [95] |

| 2017 | p-Si-FG | 0.015/0.02 | 79 | 105 | —— | [96] |

| 2021 | p-Ge-BG | 10/100 | 500 | 105 | 300 | [97] |

| 2022 | p-Si-FG | 0.033/0.5 | 61 | 105 | —— | [98] |

| 2023 | p-GeSi-BG | 100/100 | 6000 | 107 | 380 | [99] |

| 2023 | p-SiGe-FG | 0.025/0.5 | 86 | 106 | —— | [34] |

| 2024 | p-Ge-FG | 10/50 | 37.7 | 104 | 300 | [20] |

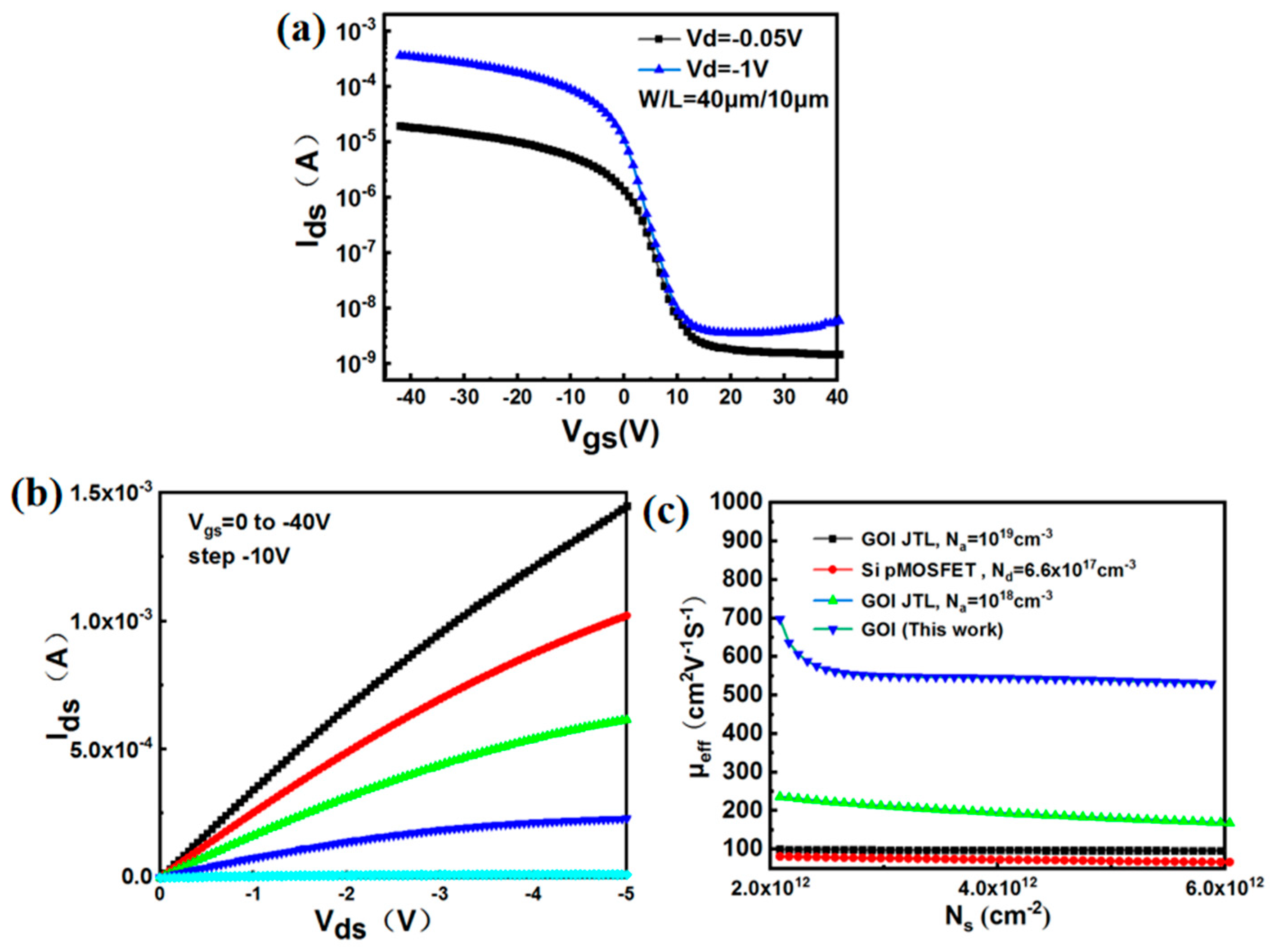

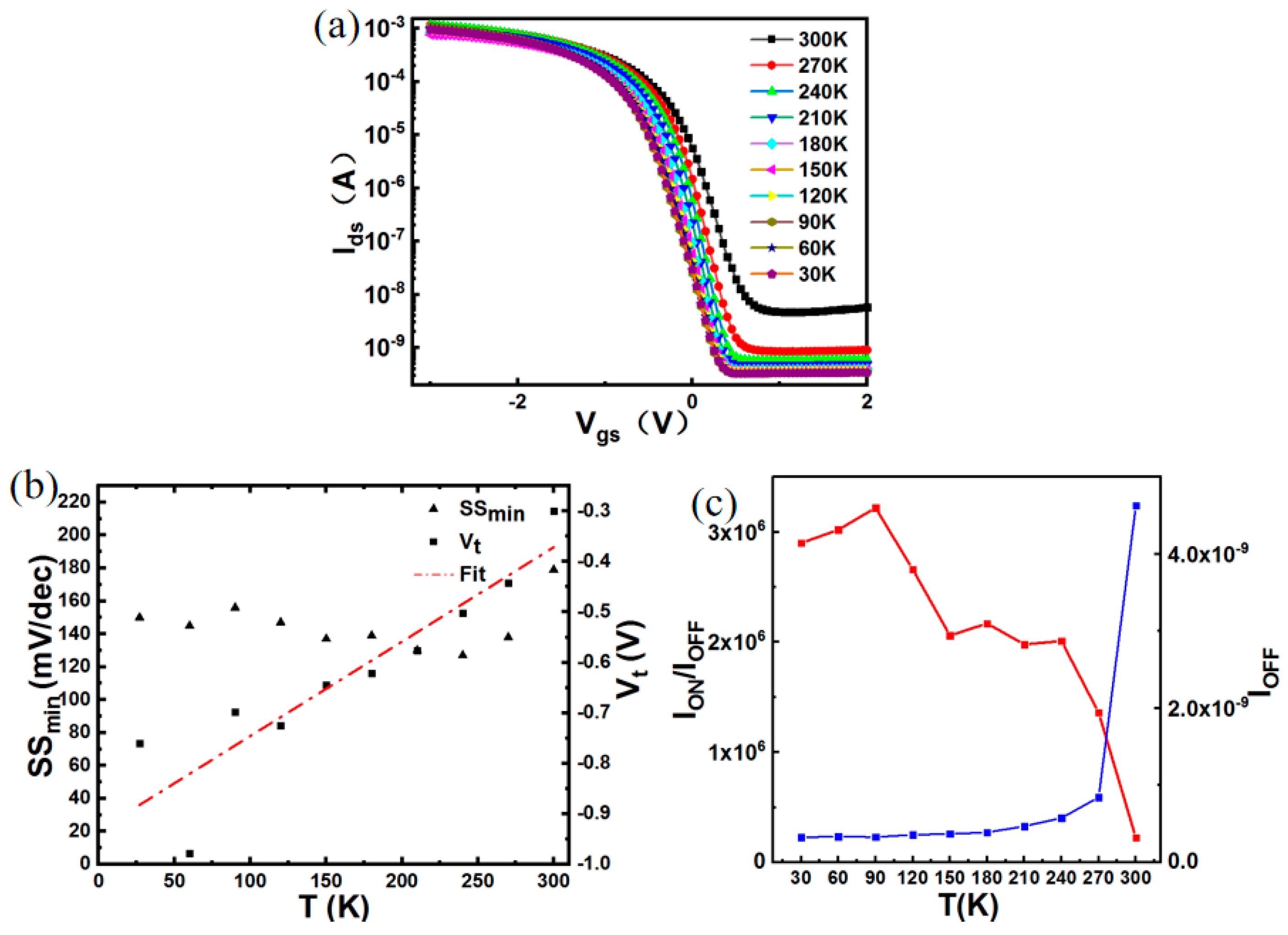

| 2025 | p-Ge-BG | 40/10 | 5370 | 105 | 550 | This work |

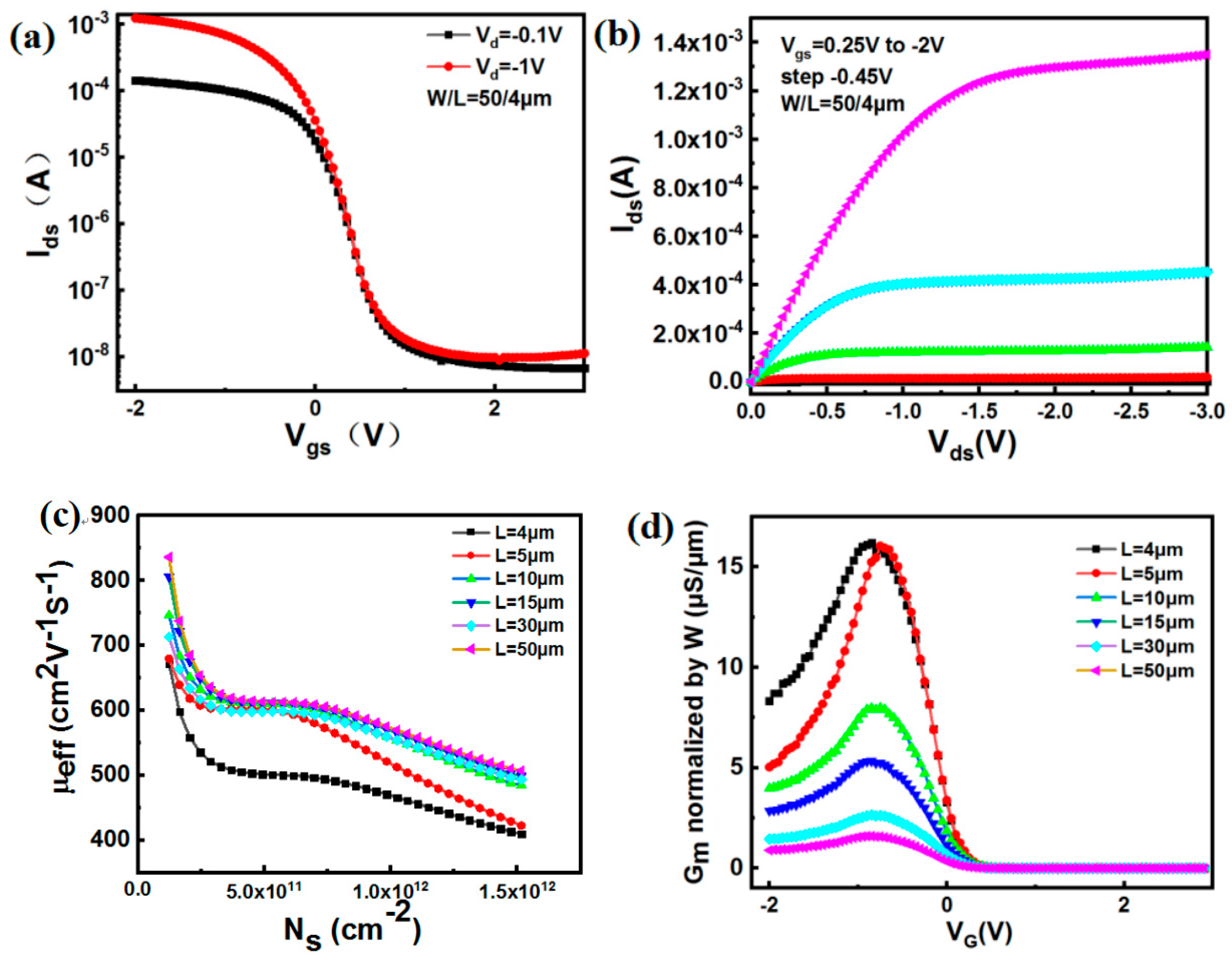

| 2025 | p-Ge-FG | 50/4 | 179 | 105 | 400 | This work |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ren, Y.; Su, J.; Ke, J.; Lin, H.; Li, B.; Kong, Z.; Zhang, Y.; Du, J.; Liang, R.; Xu, J.; et al. Fabrication and Characterization of Back-Gate and Front-Gate Ge-on-Insulator Transistors for Low-Power Applications. Electronics 2025, 14, 4646. https://doi.org/10.3390/electronics14234646

Ren Y, Su J, Ke J, Lin H, Li B, Kong Z, Zhang Y, Du J, Liang R, Xu J, et al. Fabrication and Characterization of Back-Gate and Front-Gate Ge-on-Insulator Transistors for Low-Power Applications. Electronics. 2025; 14(23):4646. https://doi.org/10.3390/electronics14234646

Chicago/Turabian StyleRen, Yuhui, Jiale Su, Jiahan Ke, Hongxiao Lin, Ben Li, Zhenzhen Kong, Yiwen Zhang, Junhao Du, Renrong Liang, Jun Xu, and et al. 2025. "Fabrication and Characterization of Back-Gate and Front-Gate Ge-on-Insulator Transistors for Low-Power Applications" Electronics 14, no. 23: 4646. https://doi.org/10.3390/electronics14234646

APA StyleRen, Y., Su, J., Ke, J., Lin, H., Li, B., Kong, Z., Zhang, Y., Du, J., Liang, R., Xu, J., Duan, X., Dong, T., Su, X., Ye, T., Zhao, X., Miao, Y., & Radamson, H. H. (2025). Fabrication and Characterization of Back-Gate and Front-Gate Ge-on-Insulator Transistors for Low-Power Applications. Electronics, 14(23), 4646. https://doi.org/10.3390/electronics14234646