A 12-bit 100 MSPS Full-Swing Current-Steering Digital-to-Analog Converter with Half-Power Supply Calibration Technique

Abstract

1. Introduction

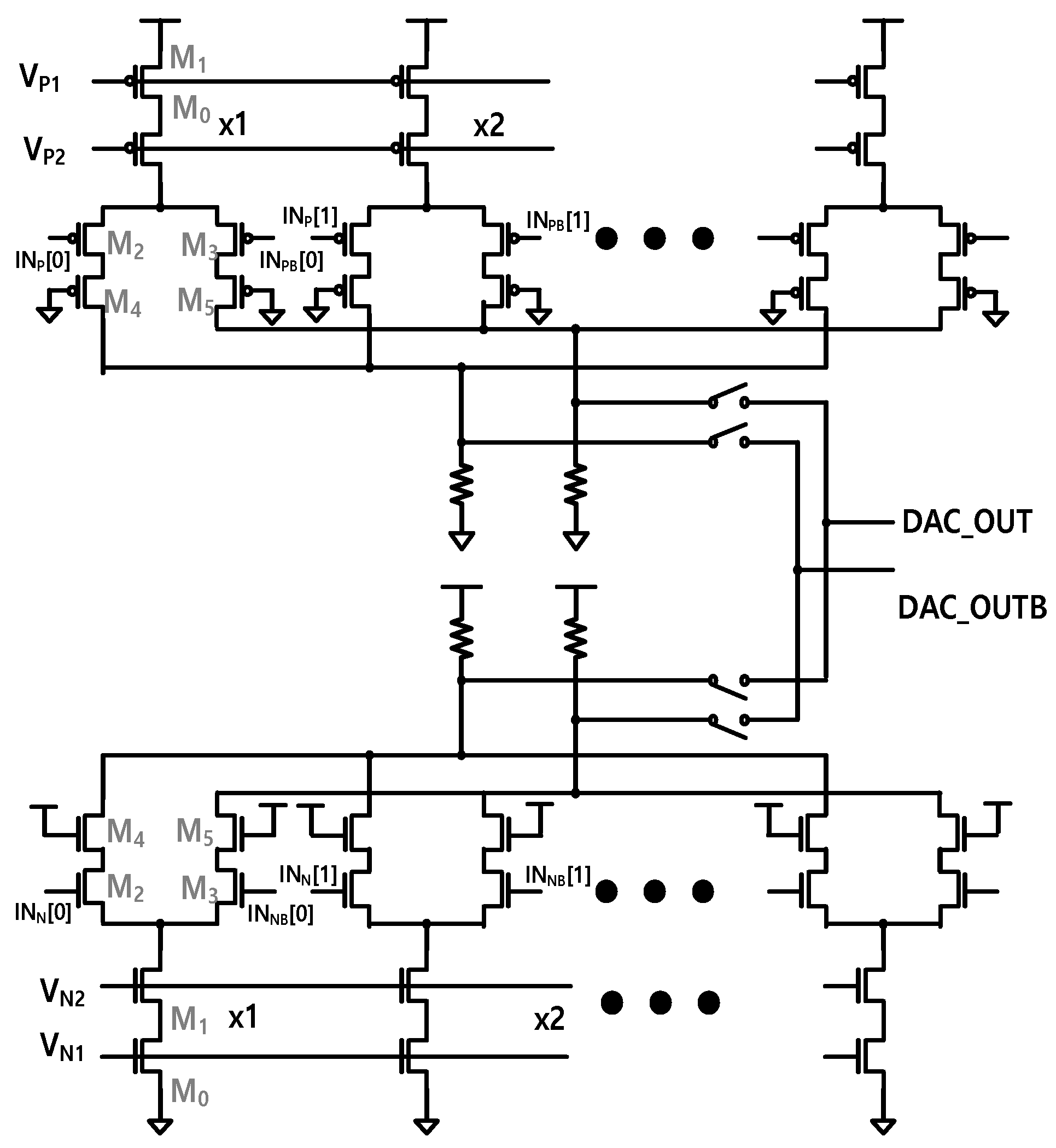

2. Proposed DAC Structure

2.1. Switching Logic and Symmetric Thermometer Decoder

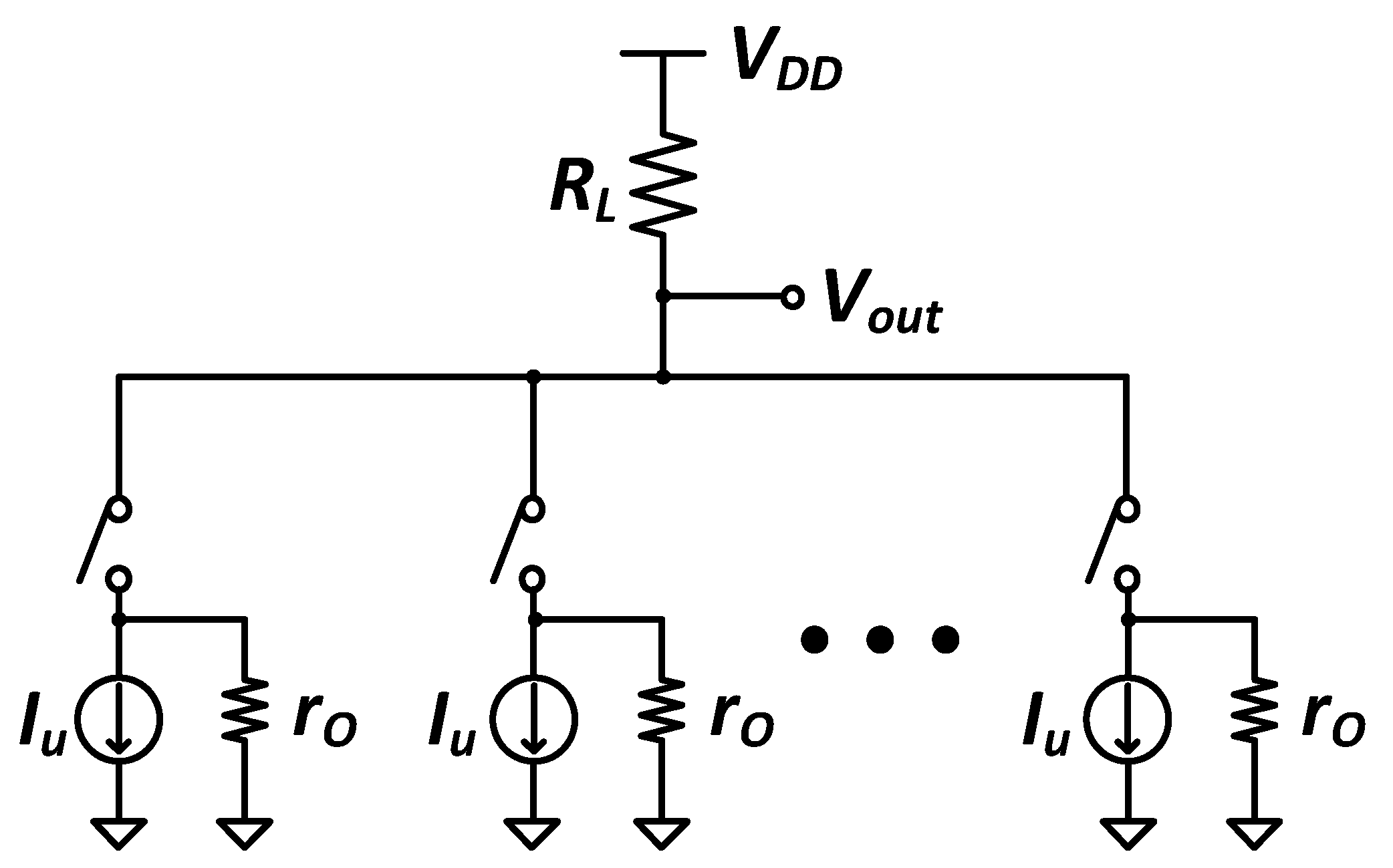

2.2. Current Cells

2.3. Quaternary Driver and Output Selector

2.4. Half-Power Supply Calibration Technique

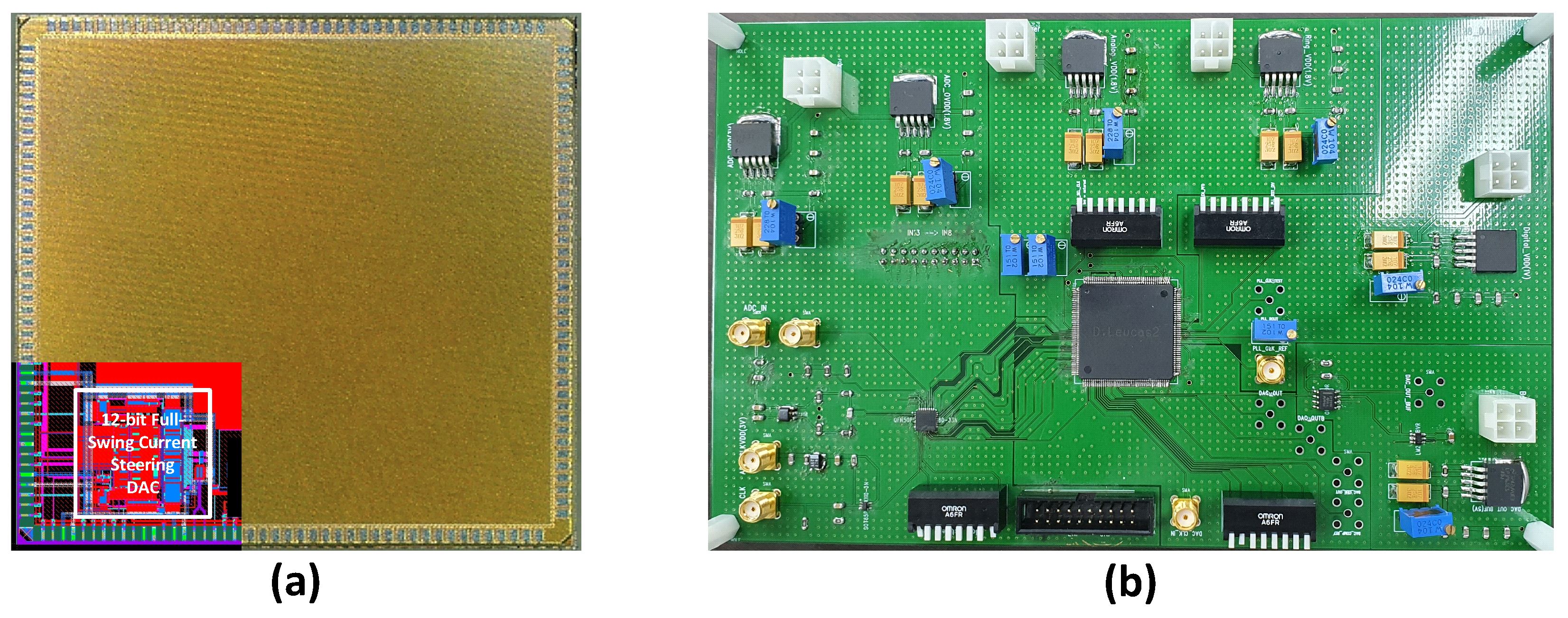

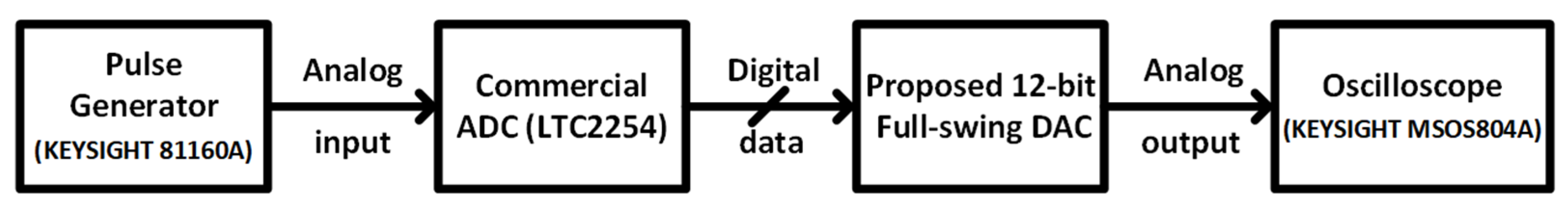

3. Experimental Results

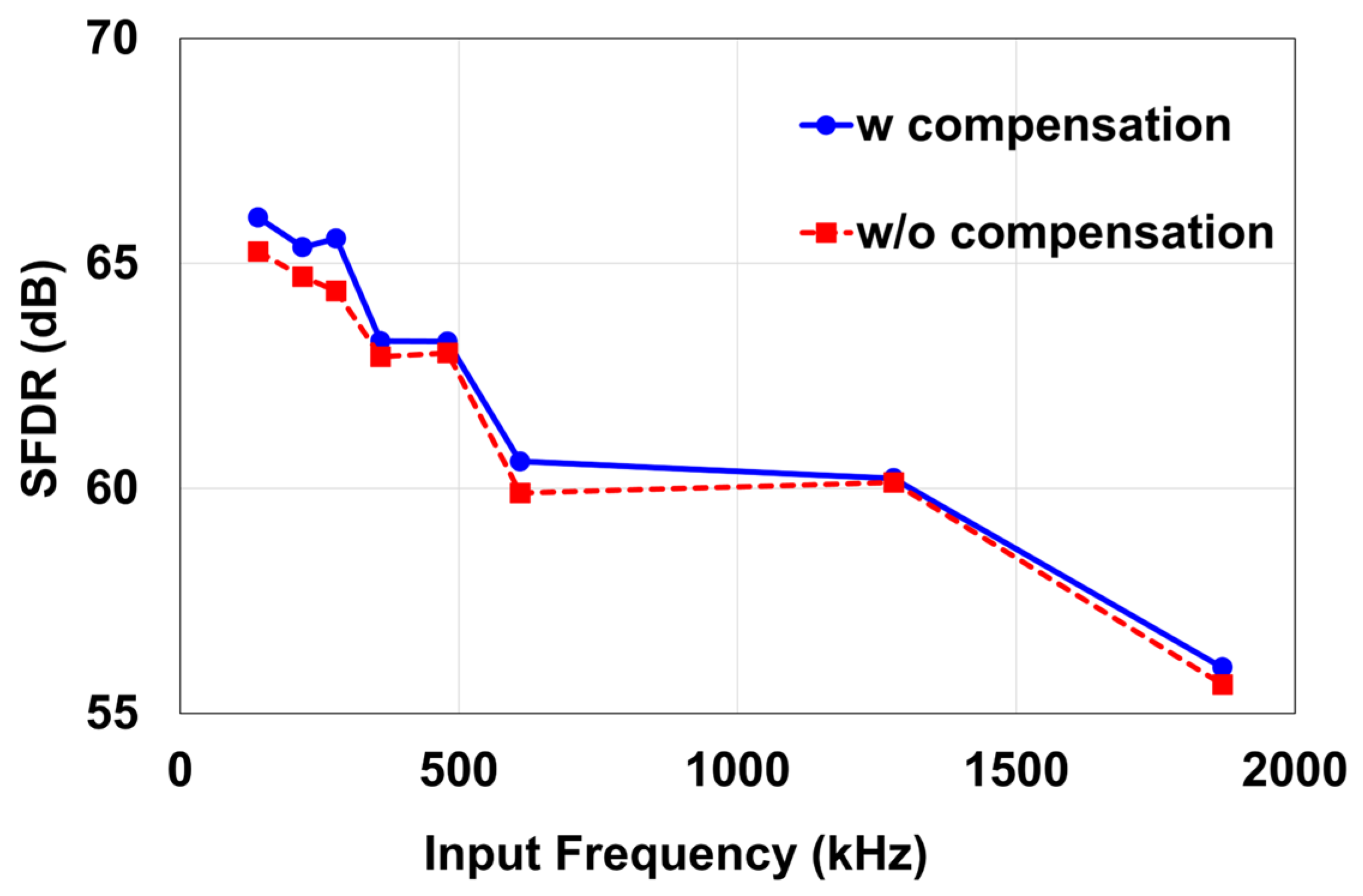

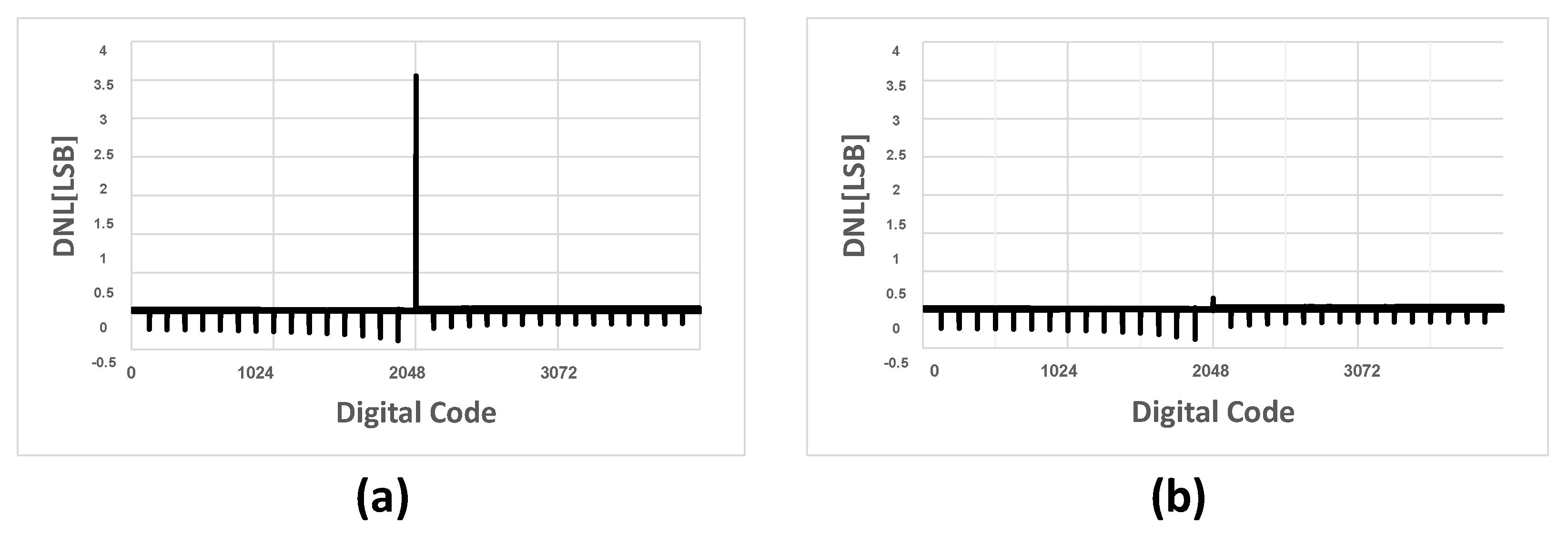

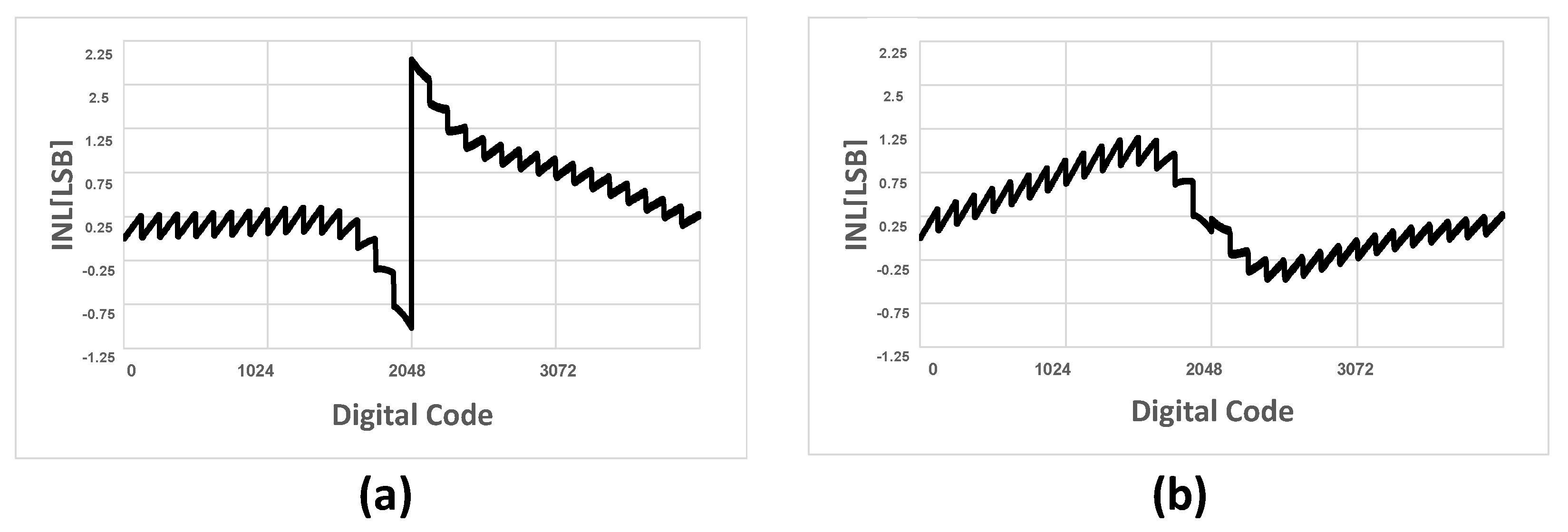

Static/Dynamic Performance

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Li, X.; Liu, Y.; Zhang, Q.; Wu, N.; Lee, H. A 14-Bit 500 MS/s CMOS DAC Using Complementary Switched Current Sources and Time-Relaxed Interleaving DRRZ. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 2337–2347. [Google Scholar] [CrossRef]

- Park, C.U.; Chung, J.H.; Ryu, S.T. A 12-bit 1 GS/s Current-Steering DAC with Paired Current Source Switching Background Mismatch Calibration. In Proceedings of the 2023 IEEE Custom Integrated Circuits Conference (CICC), San Antonio, TX, USA, 23–26 April 2023; IEEE: Piscataway, NJ, USA, 2023. [Google Scholar] [CrossRef]

- Sun, Y.; Zhang, Z.; Shan, Y.; Lang, L.; Dong, Y. Modeling and Mitigating Output-Dependent Modulation in Current-Steering DAC Based on Differential-Quad Switching Scheme. Electronics 2024, 13, 1992. [Google Scholar] [CrossRef]

- Duan, B.; Bi, J.; Xu, H.; Li, G.; Tian, Y.; Yan, N. A 12-bit 2 GS/s Current-Steering DAC with 27 mW Power Consumption in 28 nm CMOS. Microelectron. J. 2025, 163, 106756. [Google Scholar] [CrossRef]

- Zhuang, Y.; Zhang, L.; Zhang, Y.; Zhang, H. High-Purity Sine Wave Generation Using Nonlinear DAC with Predistortion Based on Low-Cost Accurate DAC–ADC Co-Testing. IEEE Trans. Instrum. Meas. 2018, 67, 279–287. [Google Scholar] [CrossRef]

- Park, G.; Song, M. A CMOS Current-Steering D/A Converter with Full-Swing Output Voltage and a Quaternary Driver. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 671–675. [Google Scholar] [CrossRef]

- Kim, J.M.; Jung, W.Y. A Fully Integrated Circuit for High Current Multiple-Output. IDEC J. Integr. Circuits Syst. 2023, 9, 11–15. [Google Scholar] [CrossRef]

- Song, D.; Cho, G.; Kim, J. A 2.5 GHz, 87-fs Step, Temperature-and-Voltage-Tolerant 6-bit Digital-to-Time Converter in 28 nm CMOS. IDEC J. Integr. Circuits Syst. 2025, 11, 14–19. [Google Scholar] [CrossRef]

- Razavi, B. The Current-Steering DAC [A Circuit for All Seasons]. IEEE Solid-State Circuits Mag. 2018, 10, 11–15. [Google Scholar] [CrossRef]

- Li, X.; Zhou, L. A Survey of High-Speed High-Resolution Current Steering DACs. J. Semicond. 2020, 41, 111402. [Google Scholar] [CrossRef]

- Wang, F.; Wang, Z.; Liu, J.; Yu, F. A 14-Bit 3-GS/s DAC Achieving SFDR > 63 dB Up to 1.4 GHz With Random Differential-Quad Switching Technique. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 879–883. [Google Scholar] [CrossRef]

- Ravinuthula, V.R.; Sahoo, B.; Halder, S.; Seshan, M.; Cao, C. A 14-Bit 8.9 GS/s RF DAC in 40 nm CMOS Achieving >71 dBc LTE ACPR at 2.9 GHz. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 15–17 June 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Luo, F.J.; Li, X.Y.; Tang, X.F.; Wang, H.Y.; Xu, X.W. Current Switch Driver and Current Source Designs for High-Speed Current-Steering DAC. In Proceedings of the 2008 2nd International Conference on Anti-Counterfeiting, Security and Identification, Guiyang, China, 20–23 August 2008; IEEE: Piscataway, NJ, USA, 2008; pp. 364–367. [Google Scholar] [CrossRef]

- Tong, X.; Liu, D. High SFDR Current-Steering DAC With Splitting-and-Binary Segmented Architecture and Dynamic-Element-Matching Technique. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 4233–4237. [Google Scholar] [CrossRef]

- Mehrjoo, M.S.; Buckwalter, J.F. A 10-Bit, 300 MS/s Nyquist Current-Steering Power DAC with 6 V Output Swing. IEEE J. Solid-State Circuits 2014, 49, 1408–1418. [Google Scholar] [CrossRef]

- Huang, C.Y.; Chen, Y.H.; Lin, T.Y.; Liu, S.I. Design of 12-Bit 100-MHz Current-Steering DAC for SoC Applications. In Proceedings of the Fifth International Workshop on System-on-Chip for Real-Time Applications (IWSOC’05), Banff, AB, Canada, 20–24 July 2005; IEEE: Piscataway, NJ, USA, 2005; pp. 117–122. [Google Scholar] [CrossRef]

- Wang, D.; Liu, J.; Jin, X.; Ren, J.; Zhang, X.; He, Z. A 3 GS/s 12-Bit Current-Steering Digital-to-Analog Converter with Partial Randomization Dynamic Element Matching (PRDEM). Electronics 2019, 8, 464. [Google Scholar] [CrossRef]

- Remple, J.; Panigada, A.; Galton, I. An ISI Scrambling Technique for Dynamic Element Matching Current-Steering DACs. IEEE J. Solid-State Circuits 2021, 56, 2702–2713. [Google Scholar] [CrossRef]

- Lin, W.-T.; Huang, H.-Y.; Kuo, T. A 12-bit 40-nm DAC Achieving SFDR > 70 dB at 1.6 GS/s with DEMDRZ Technique. IEEE J. Solid-State Circuits 2020, 55, 3300–3312. [Google Scholar] [CrossRef]

- Bonsu, G.; Tamakloe, K.; Bruce, I.; Nti Darko, E.; Chen, D. Redundancy-Interpolated Three-Segment DAC with On-Chip Digital Calibration for Improved Static Linearity. Electronics 2025, 14, 3477. [Google Scholar] [CrossRef]

- Deng, Y.; Yang, P.; Huang, G.; Liu, J.; Ren, Z.; Fan, Y.; Song, Z. A 14-Bit Digital to Analog Converter for a Topmetal-CEE Pixel Readout Chip. Electronics 2024, 13, 3074. [Google Scholar] [CrossRef]

| Segments | nMOS Cells | pMOS Cells | ||

|---|---|---|---|---|

| W/L (μm/μm) | σ/μ of Current (%) | W/L (μm/μm) | σ/μ of Current (%) | |

| LLSB | 1/1.04 | 0.45 | 1/1.04 | 0.47 |

| LSB | 5/1.04 | 0.23 | 10/1.04 | 0.19 |

| MSB | 40/0.26 | 0.12 | 73.5/0.26 | 0.09 |

| This Work | [6] | [15] | [16] | [20] | [21] | |

| Full-swing | Yes | Yes | Yes | No | No | No |

| Resolution | 12-b | 6-b | 10-b | 12-b | 16-b | 14-b |

| Technology | 28 nm CMOS | 0.11 μm CMOS | 40 nm CMOS | 0.35 μm CMOS | 0.18 μm CMOS | 0.18 μm CMOS |

| Sampling rate | 100 MS/s | 1 GS/s | 300 MS/s | 100 MS/s | 500 MS/s | 500 MS/s |

| INL/DNL | 0.39 LSB 1.15 LSB | 0.7 LSB 0.7 LSB | 0.6 LSB 0.4 LSB | 0.4 LSB 0.25 LSB | 0.48 LSB 0.68 LSB | 1.57 LSB 1.07 LSB |

| Power consumption | 79.65 mW | 19.1 mW | 476 mW | 47 mW | 630 mW | 0.3 mW |

| Core area | 0.89 mm2 | 0.46 mm2 | 2.25 mm2 | 6.9 mm2 | - | 0.02 mm2 |

| FoM (Walden) | 194.46 fJ | 298.4 fJ | 1550 fJ | 114.7 fJ | 0.21 fJ | 13 fJ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, K.; Choi, S.G.; Kim, J.; Kim, M.; Song, H.; Song, M.; Kim, S.Y. A 12-bit 100 MSPS Full-Swing Current-Steering Digital-to-Analog Converter with Half-Power Supply Calibration Technique. Electronics 2025, 14, 3955. https://doi.org/10.3390/electronics14193955

Park K, Choi SG, Kim J, Kim M, Song H, Song M, Kim SY. A 12-bit 100 MSPS Full-Swing Current-Steering Digital-to-Analog Converter with Half-Power Supply Calibration Technique. Electronics. 2025; 14(19):3955. https://doi.org/10.3390/electronics14193955

Chicago/Turabian StylePark, Kwangjin, Seung Gu Choi, Jintae Kim, Myungsik Kim, Hyunjin Song, Minkyu Song, and Soo Youn Kim. 2025. "A 12-bit 100 MSPS Full-Swing Current-Steering Digital-to-Analog Converter with Half-Power Supply Calibration Technique" Electronics 14, no. 19: 3955. https://doi.org/10.3390/electronics14193955

APA StylePark, K., Choi, S. G., Kim, J., Kim, M., Song, H., Song, M., & Kim, S. Y. (2025). A 12-bit 100 MSPS Full-Swing Current-Steering Digital-to-Analog Converter with Half-Power Supply Calibration Technique. Electronics, 14(19), 3955. https://doi.org/10.3390/electronics14193955