Isolated Bipolar Bidirectional Three-Port Converter with Voltage Self-Balancing Capability for Bipolar DC Microgrids

Abstract

1. Introduction

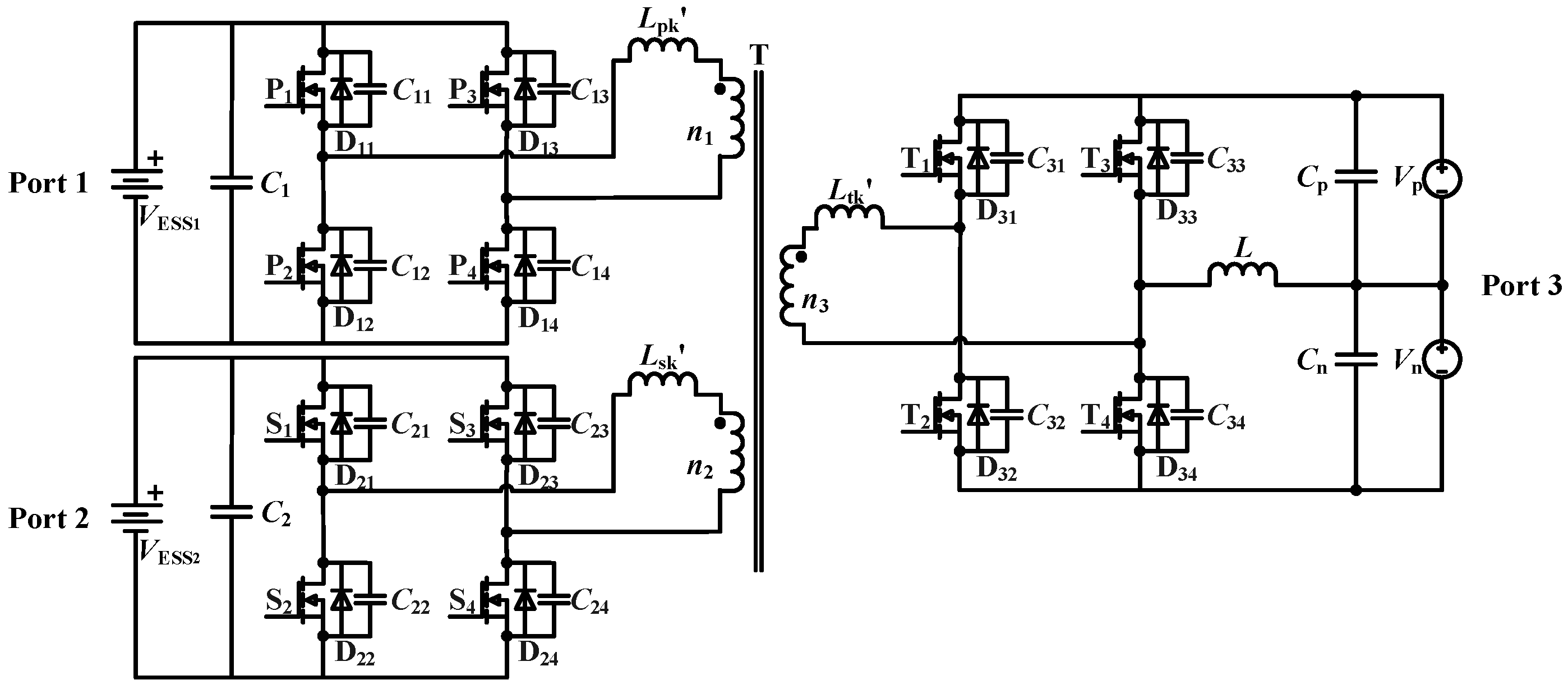

2. Working Principle

3. Performance Characteristics

3.1. Analysis of Transmitted Power

3.2. Analysis of Voltage and Current Stress

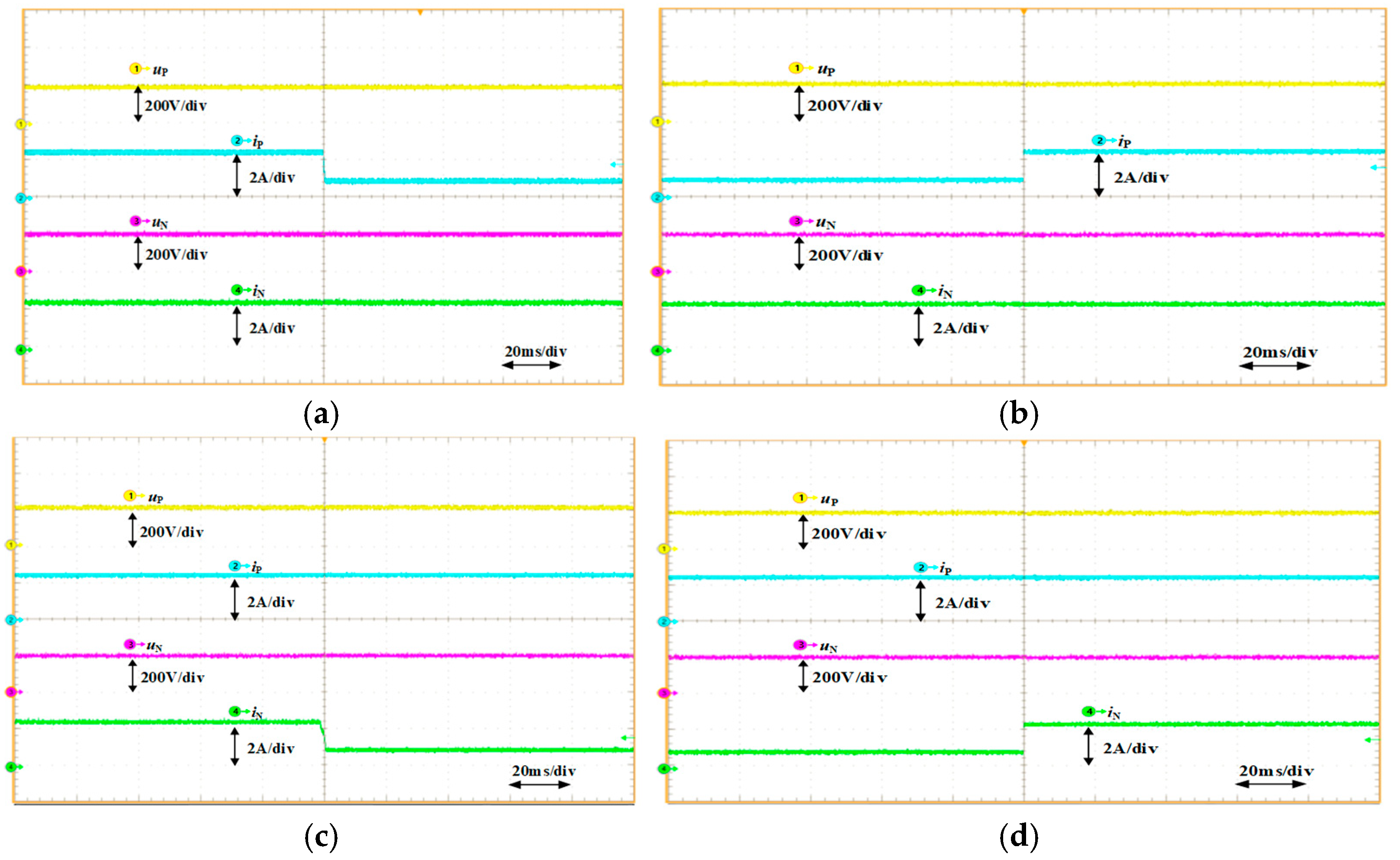

3.3. Analysis of the Voltage Self-Balancing Mechanism

3.3.1. The Principle of the Inter-Pole Voltage Self-Balancing

3.3.2. Balancing Inductor Design

3.3.3. Analysis of the Voltage Self-Balancing Ability of the Proposed Converter

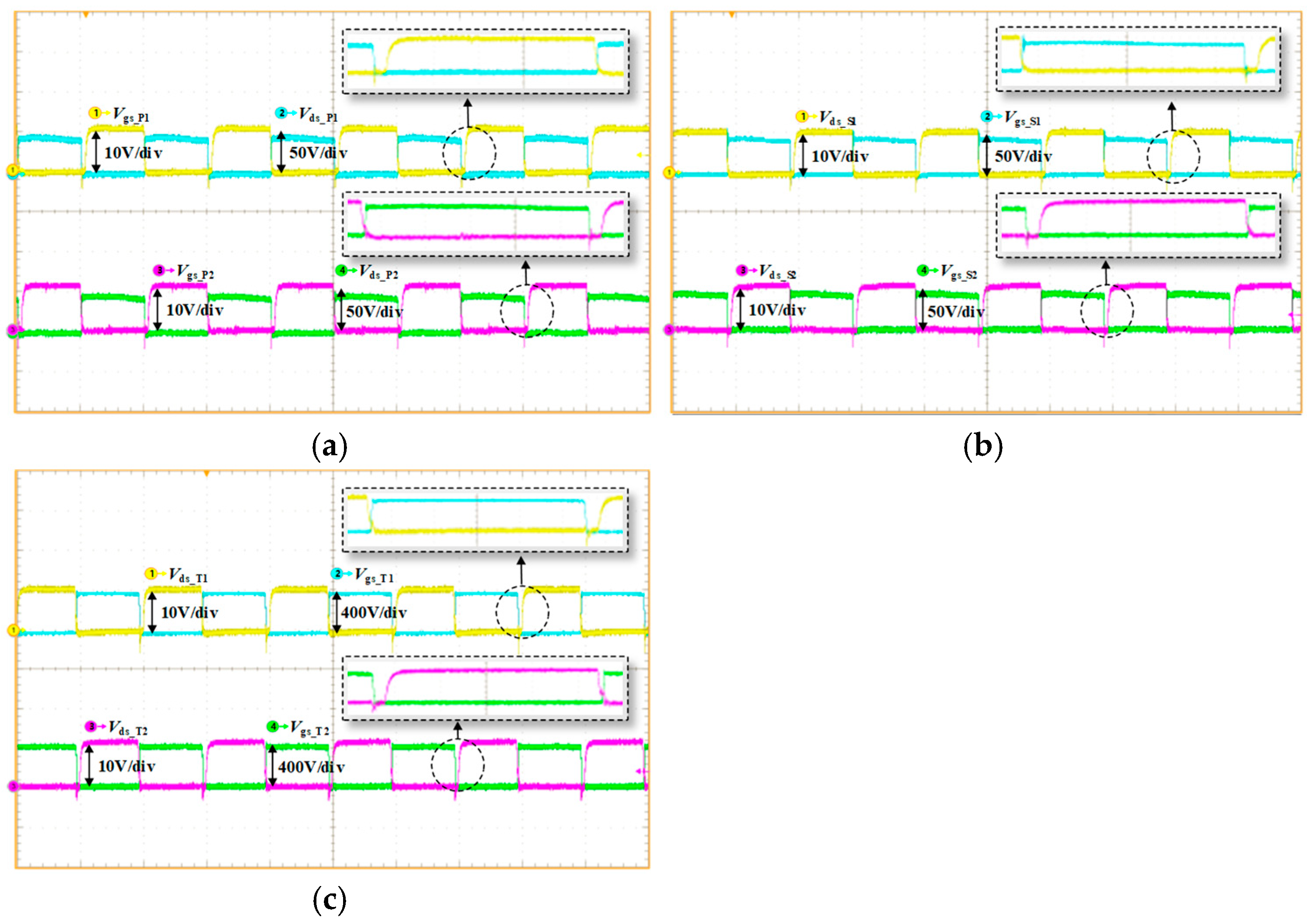

4. Analysis of Soft Switch Implementation Range

5. Simulation and Experimental Verification

6. Performance Comparison and Analysis

7. Conclusions

- (1)

- The proposed converter features inherent self-balancing output voltage characteristics. Under unbalanced load conditions, it can autonomously redistribute power between the poles to maintain balanced output voltages, without relying on complex voltage sampling and control systems to sustain symmetric operation of the bipolar output.

- (2)

- The proposed converter supports multi-port input and bidirectional energy exchange. Phase shift control enables flexible power flow regulation and precise management of energy distribution among multiple input ports. Additionally, the high-frequency transformer provides electrical isolation, making the converter well-suited for high-power applications with enhanced operational safety and reliability.

- (3)

- The proposed converter achieves Zero Voltage Switching (ZVS) for its power switches, significantly reducing switching losses. This capability enhances overall efficiency and extends the operational lifespan of the components, thereby ensuring highly efficient performance even under high-frequency switching conditions.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhu, B.; Liu, Y.; Zhi, S.; Wang, K.; Liu, J. A Family of Bipolar High Step-Up Zeta–Buck–Boost Converter Based on “Coat Circuit”. IEEE Trans. Power Electron. 2023, 38, 3328–3339. [Google Scholar] [CrossRef]

- Ali, Z.; Raisz, D. Development and laboratory validation of an LVDC back-to-back system with residential inverter, PV, and battery-based power generation. Energy Convers. Manag. X 2025, 26, 100997. [Google Scholar] [CrossRef]

- Ren, Q.; Han, Y.; Zhou, M.; Yan, C.; Yang, P.; Wang, C. Overview of Voltage Balancing Schemes in Bipolar DC Microgrids. IEEE Trans. Power Electron. 2025, 40, 3469–3489. [Google Scholar] [CrossRef]

- Pires, V.F.; Cordeiro, A.; Roncero-Clemente, C.; Rivera, S.; Dragičević, T. DC-DC Converters for Bipolar Microgrid Voltage Balancing: A Comprehensive Review of Architectures and Topologies. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 981–998. [Google Scholar] [CrossRef]

- Zhu, B.; Hu, H.; Wang, H.; Li, Y. A multi-input-port bidirectional DC/DC converter for DC microgrid energy storage system applications. Energies 2020, 13, 2810. [Google Scholar] [CrossRef]

- Khosravi, N.; Oubelaid, A.; Belkhier, Y. Energy management in networked microgrids: A comparative study of hierarchical deep learning and predictive analytics techniques. Energy Convers. Manag. X 2025, 25, 100828. [Google Scholar] [CrossRef]

- Wang, F.; Lei, Z.; Xu, X.; Shu, X. Topology Deduction and Analysis of Voltage Balancers for DC Microgrid. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 672–680. [Google Scholar] [CrossRef]

- Al-Hysam, A.; Raisz, D. A hybrid high-gain bipolar converter for LVDC microgrid with average current mode control. Energy Convers. Manag. X 2025, 25, 100857. [Google Scholar] [CrossRef]

- Rivera, S.; Lizana, R.; Kouro, S.; Dragicevic, T.; Wu, B. Bipolar DC Power Conversion: State-of-the-Art and Emerging Technologies. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 1192–1204. [Google Scholar] [CrossRef]

- Prabhakaran, P.; Agarwal, V. Novel Boost-SEPIC Type Interleaved DC-DC Converter for Mitigation of Voltage Imbalance in a Low-Voltage Bipolar DC Microgrid. IEEE Trans. Ind. Electron. 2020, 67, 6494–6504. [Google Scholar] [CrossRef]

- Prabhakaran, P.; Agarwal, V. Novel Four-Port DC-DC Converter for Interfacing Solar PV-Fuel Cell Hybrid Sources with Low-Voltage Bipolar DC Microgrids. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1330–1340. [Google Scholar] [CrossRef]

- Rezayi, S.; Iman-Eini, H.; Hamzeh, M.; Bacha, S.; Farzamkia, S. Dual-output DC/DC boost converter for bipolar DC microgrids. IET Renew. Power Gener. 2019, 13, 1402–1410. [Google Scholar] [CrossRef]

- Kim, S.; Nam, H.-T.; Cha, H.; Kim, H.-G. Investigation of Self-Output Voltage Balancing in Input-Parallel Output-Series DC-DC Converter. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 2850–2860. [Google Scholar] [CrossRef]

- Tan, L.; Wu, B.; Yaramasu, V.; Rivera, S.; Guo, X. Effective Voltage Balance Control for Bipolar-DC-Bus-Fed EV Charging Station with Three-Level DC-DC Fast Charger. IEEE Trans. Ind. Electron. 2016, 63, 4031–4041. [Google Scholar] [CrossRef]

- Monteiro, V.; Oliveira, C.F.; Afonso, J.L. Experimental Validation of a Bidirectional Multilevel dc-dc Power Converter for Electric Vehicle Battery Charging Operating under Normal and Fault Conditions. Electronics 2023, 12, 851. [Google Scholar] [CrossRef]

- Tan, L.; Wu, B.; Rivera, S.; Yaramasu, V. Comprehensive DC Power Balance Management in High-Power Three-Level DC-DC Converter for Electric Vehicle Fast Charging. IEEE Trans. Power Electron. 2016, 31, 89–100. [Google Scholar] [CrossRef]

- Kim, S.-H.; Byun, H.-J.; Yi, J.; Won, C.-Y. A bi-directional dual-input dual-output converter for voltage balancer in bipolar DC microgrid. Energies 2022, 15, 5043. [Google Scholar] [CrossRef]

- Wei, R.; Liu, R.; Ding, L.; Li, Y.R. A Partial-Power-Processed CLLC-DAB DC/DC Transformer with Voltage Self-Balancing Capability for Bipolar LVDC Distribution Systems. In Proceedings of the 2024 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 25–29 February 2024; pp. 481–485. [Google Scholar]

- Lee, J.Y.; Cho, Y.P.; Jung, J.H. Single-Stage Voltage Balancer with High-Frequency Isolation for Bipolar LVDC Distribution System. IEEE Trans. Ind. Electron. 2020, 67, 3596–3606. [Google Scholar] [CrossRef]

- Kolahian, P.; Tarzamni, H.; Nikafrooz, A.; Hamzeh, M. Multi-port DC-DC converter for bipolar medium voltage DC micro-grid applications. IET Power Electron. 2019, 12, 1841–1849. [Google Scholar] [CrossRef]

- Lee, J.Y.; Jung, J.H. Modified Three-Port DAB Converter Employing Voltage Balancing Capability for Bipolar DC Distribution System. IEEE Trans. Ind. Electron. 2022, 69, 6710–6721. [Google Scholar] [CrossRef]

- Ahmad, U.; Cha, H. Coupled Inductor Based Voltage Balancing in Dual-Output CLL Resonant Converter for Bipolar DC Distribution System. IEEE Trans. Power Electron. 2023, 38, 1262–1274. [Google Scholar] [CrossRef]

- Naseem, N.; Cha, H. Triple-Active-Bridge Converter with Automatic Voltage Balancing for Bipolar DC Distribution. IEEE Trans. Power Electron. 2022, 37, 8640–8648. [Google Scholar] [CrossRef]

- Yang, Y.; Zhu, B.; She, X.; Wang, K.; Liu, A. A Family of Bipolar DC-DC Converters with Interpolar Voltage Self-Balancing Based on FB-BVMs for BLVDC Microgrid. IEEE Trans. Ind. Electron. 2025, 72, 9229–9238. [Google Scholar] [CrossRef]

- Tian, Q.; Zhang, X.; Zhou, G.; Wang, X.; Guo, B.; Ma, H. A Family of Symmetrical Bipolar Output Converters Based on Voltage-Multiplying Rectifiers for Interfacing Renewable Energy with Bipolar DC Microgrid. IEEE Trans. Power Electron. 2023, 38, 9157–9172. [Google Scholar] [CrossRef]

- Yang, Y.; Zhu, B.; She, X.; Wang, K.; Liu, A. A Family of Voltage Balancers with Fault-Tolerance and Interpolar Voltage Self-Balancing Ability for Bipolar DC Power Systems. IEEE Trans. Transp. Electrif. 2025, 11, 9864–9876. [Google Scholar] [CrossRef]

- Lee, J.Y.; Kim, H.S.; Jung, J.H. Enhanced Dual-Active-Bridge DC-DC Converter for Balancing Bipolar Voltage Level of DC Distribution System. IEEE Trans. Ind. Electron. 2020, 67, 10399–10409. [Google Scholar] [CrossRef]

- Li, B.; Fu, Q.; Mao, S.; Zhao, X.; Xu, D.; Gong, X.; Wang, Q. DC/DC Converter for Bipolar LVdc System with Integrated Voltage Balance Capability. IEEE Trans. Power Electron. 2021, 36, 5415–5424. [Google Scholar] [CrossRef]

| Parameters | Model and Value |

|---|---|

| Input voltage VESS1, VESS2/V | 48 V,48 V |

| Output voltage Vo/V | 400 V (±200 V) |

| Output power P/kW | 1 kW |

| Switching frequency fs/kHz | 100 kHz |

| Inductor Lpk, Lsk, Ltk, L/µH | 1.678 µH, 1.678 µH, 1.2 µH, 470 µH |

| Capacitance C1, C2, Cp, Cn/µF | 20 µF, 20 µF, 100 µF, 100 µF |

| Power switch of port 1 S1~S4 | IPP200N25N3 |

| Power switch of port 2 P1~P4 | IPP200N25N3 |

| Power switch of port 3 T1~T4 | STW88N65M5 |

| Converter | The Number of Devices | Self-Balancing Capability | Electrical Isolation | Number of Ports (Input + Output) | ||||

|---|---|---|---|---|---|---|---|---|

| Switch | Diode | Transformer | Inductor | Capacitor | ||||

| Reference [10] | 4 | 0 | 0 | 3 | 4 | No | Non-isolation | 1 + 2 |

| Reference [17] | 6 | 0 | 0 | 3 | 4 | Yes | Non-isolation | 2 + 2 |

| Reference [23] | 12 | 0 | 1 | 2 | 3 | No | Isolation | 1 + 2 |

| Reference [27] | 8 | 0 | 1 | 2 | 3 | Yes | Isolation | 1 + 2 |

| The proposed converter | 12 | 0 | 1 | 1 | 4 | Yes | Isolation | 2 + 2 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, S.; Lian, C.; Li, Z.; Zheng, Z.; Zhou, H.; Zhu, B. Isolated Bipolar Bidirectional Three-Port Converter with Voltage Self-Balancing Capability for Bipolar DC Microgrids. Electronics 2025, 14, 3672. https://doi.org/10.3390/electronics14183672

Wang S, Lian C, Li Z, Zheng Z, Zhou H, Zhu B. Isolated Bipolar Bidirectional Three-Port Converter with Voltage Self-Balancing Capability for Bipolar DC Microgrids. Electronics. 2025; 14(18):3672. https://doi.org/10.3390/electronics14183672

Chicago/Turabian StyleWang, Shusheng, Chunxing Lian, Zhe Li, Zhenyu Zheng, Hai Zhou, and Binxin Zhu. 2025. "Isolated Bipolar Bidirectional Three-Port Converter with Voltage Self-Balancing Capability for Bipolar DC Microgrids" Electronics 14, no. 18: 3672. https://doi.org/10.3390/electronics14183672

APA StyleWang, S., Lian, C., Li, Z., Zheng, Z., Zhou, H., & Zhu, B. (2025). Isolated Bipolar Bidirectional Three-Port Converter with Voltage Self-Balancing Capability for Bipolar DC Microgrids. Electronics, 14(18), 3672. https://doi.org/10.3390/electronics14183672