Injection-Locked Frequency Multipliers with Single Inductor Component

Abstract

1. Introduction

2. Multiply-by-2 ILFM

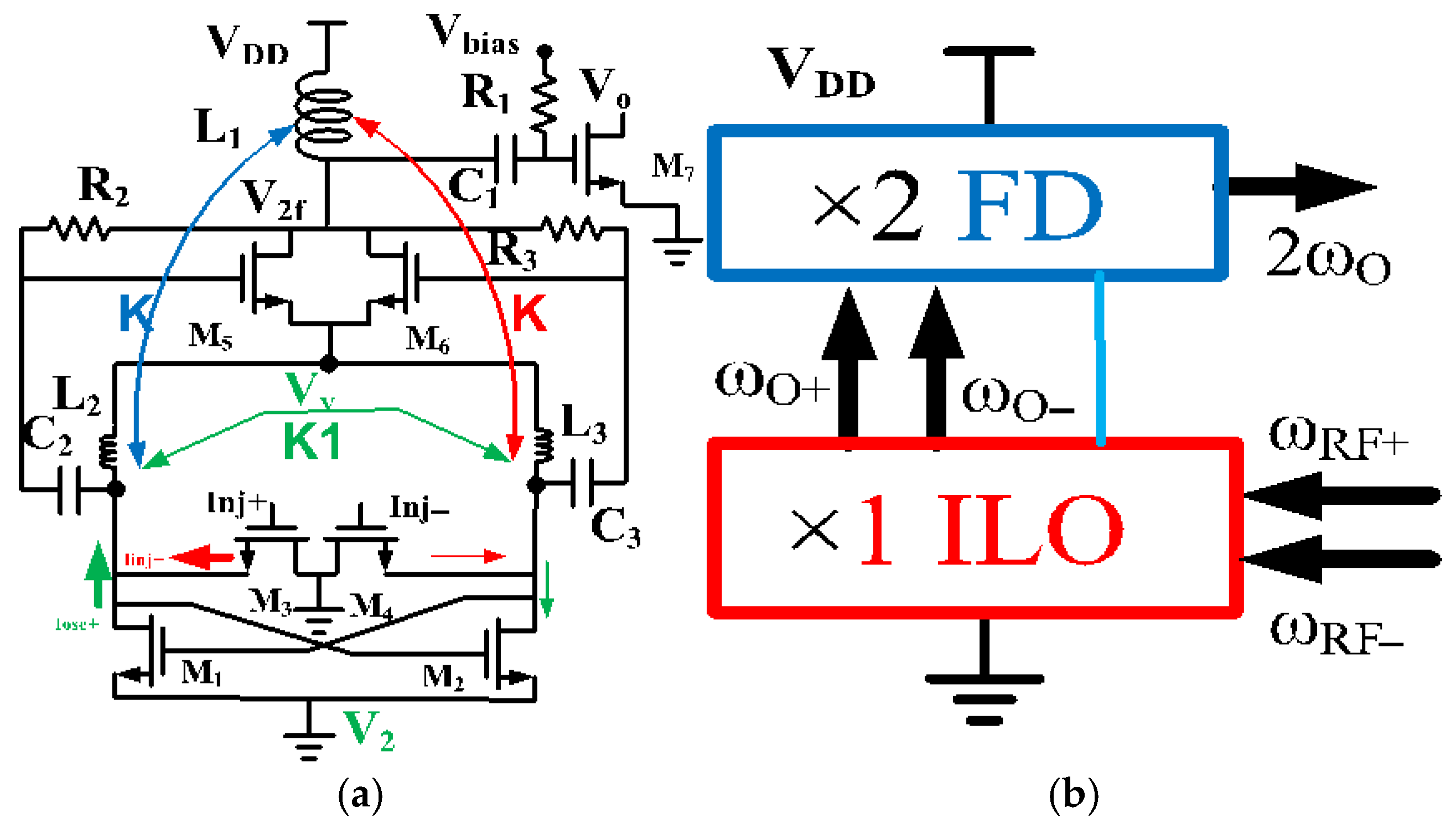

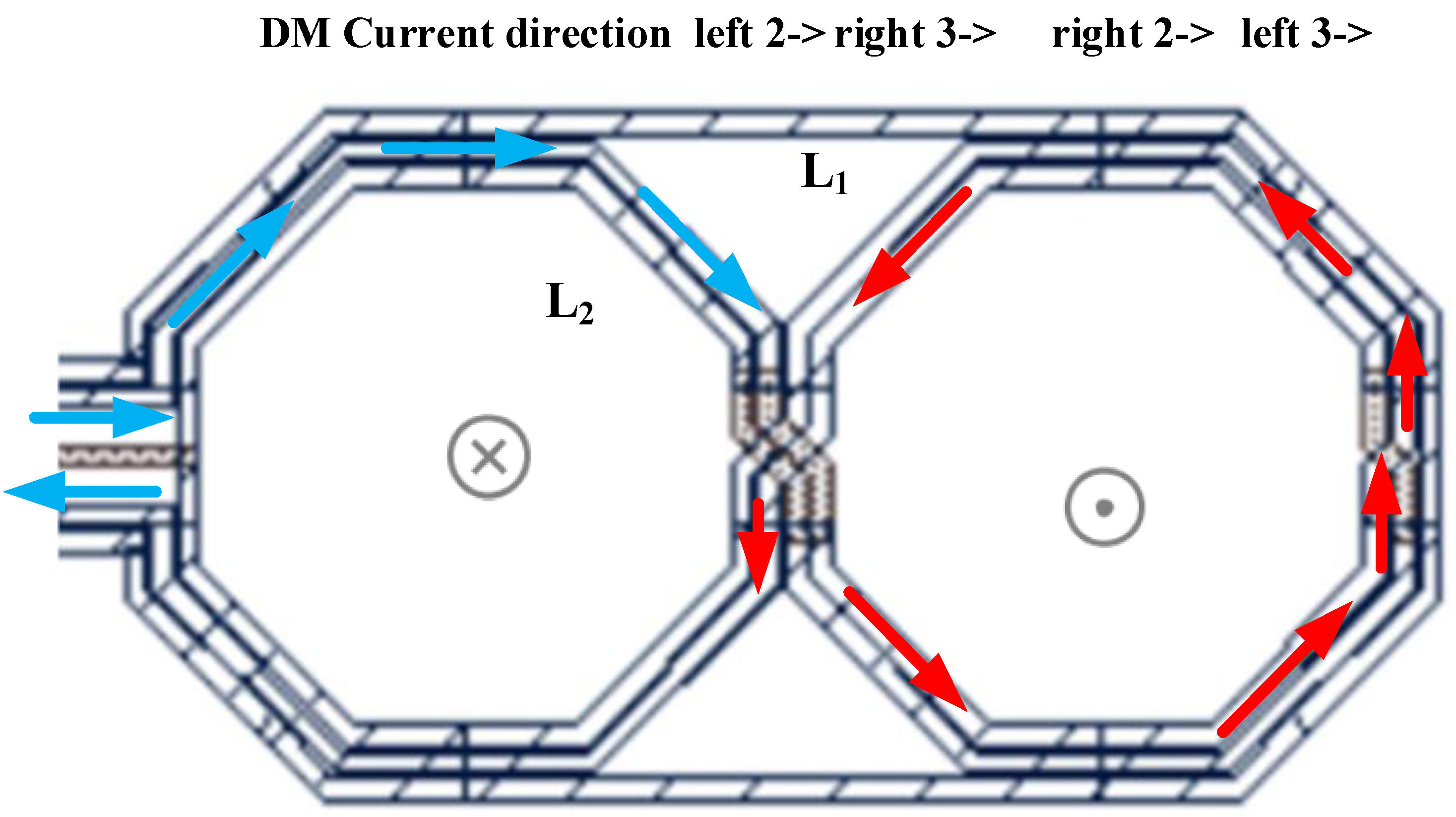

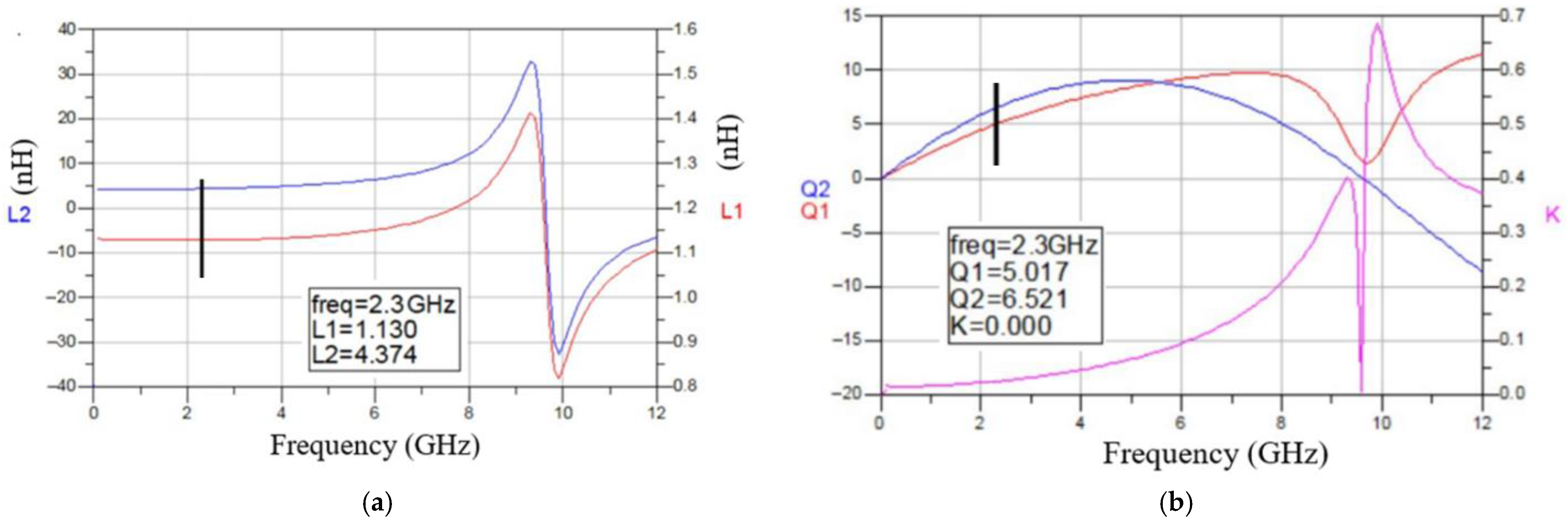

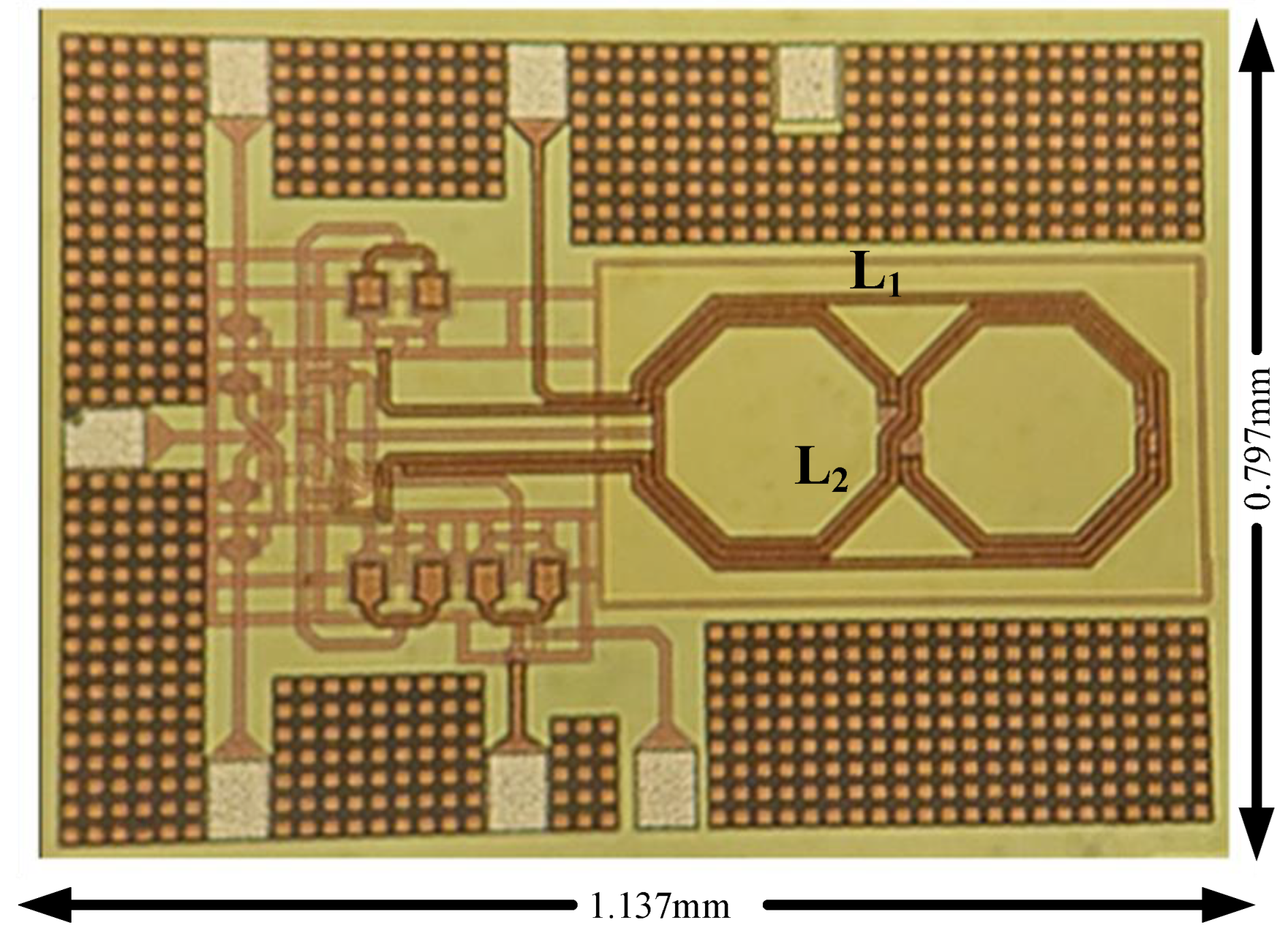

2.1. ×2 Circuit Design with Single Inductive Component

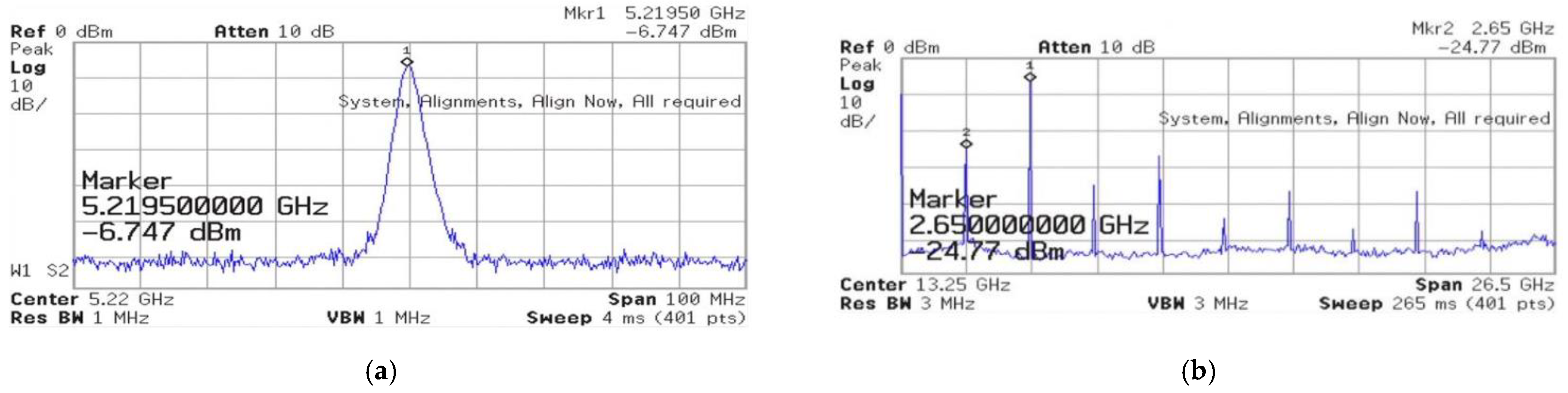

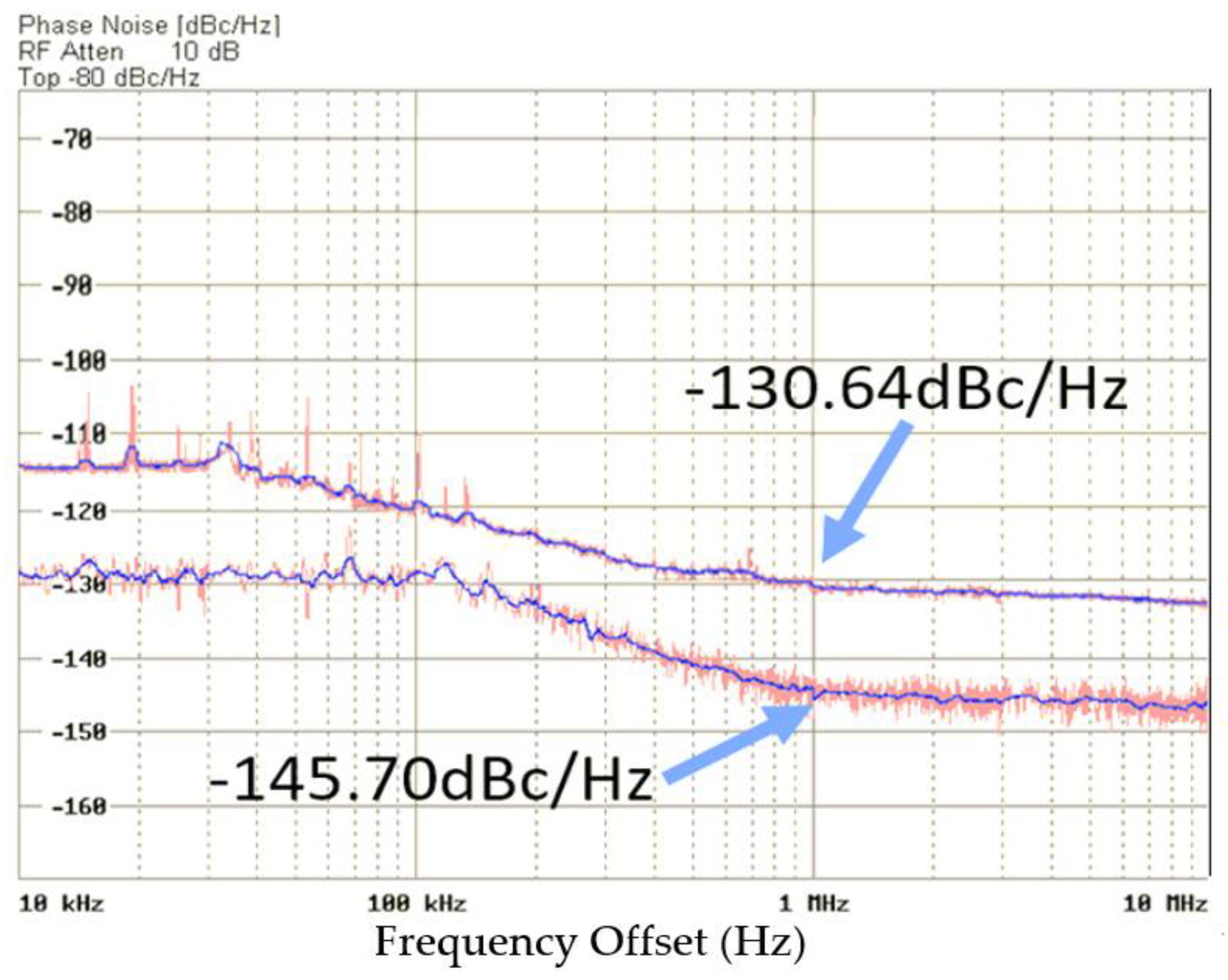

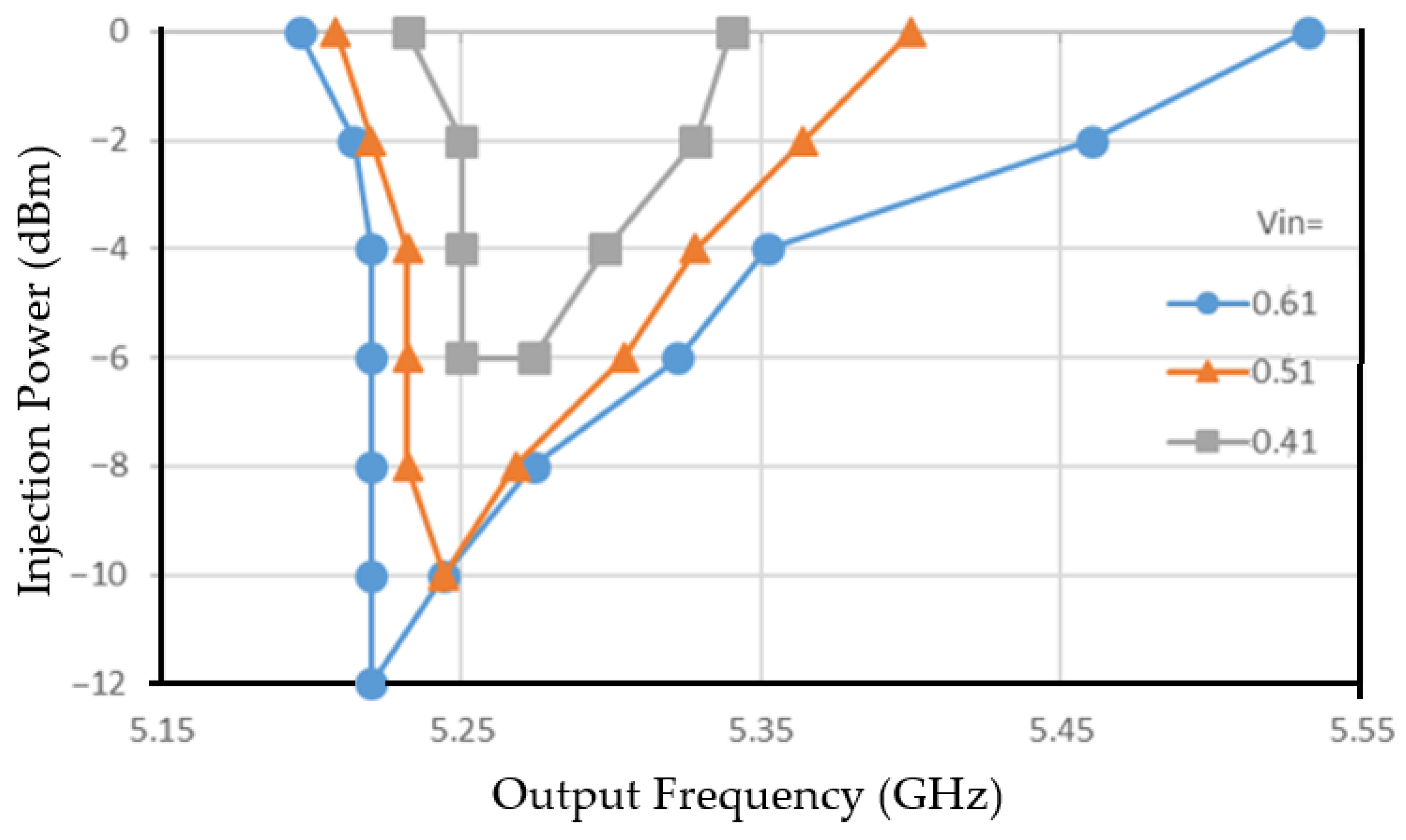

2.2. Experiment of the ×2 ILFM

3. Multiply-by-3 ILFM

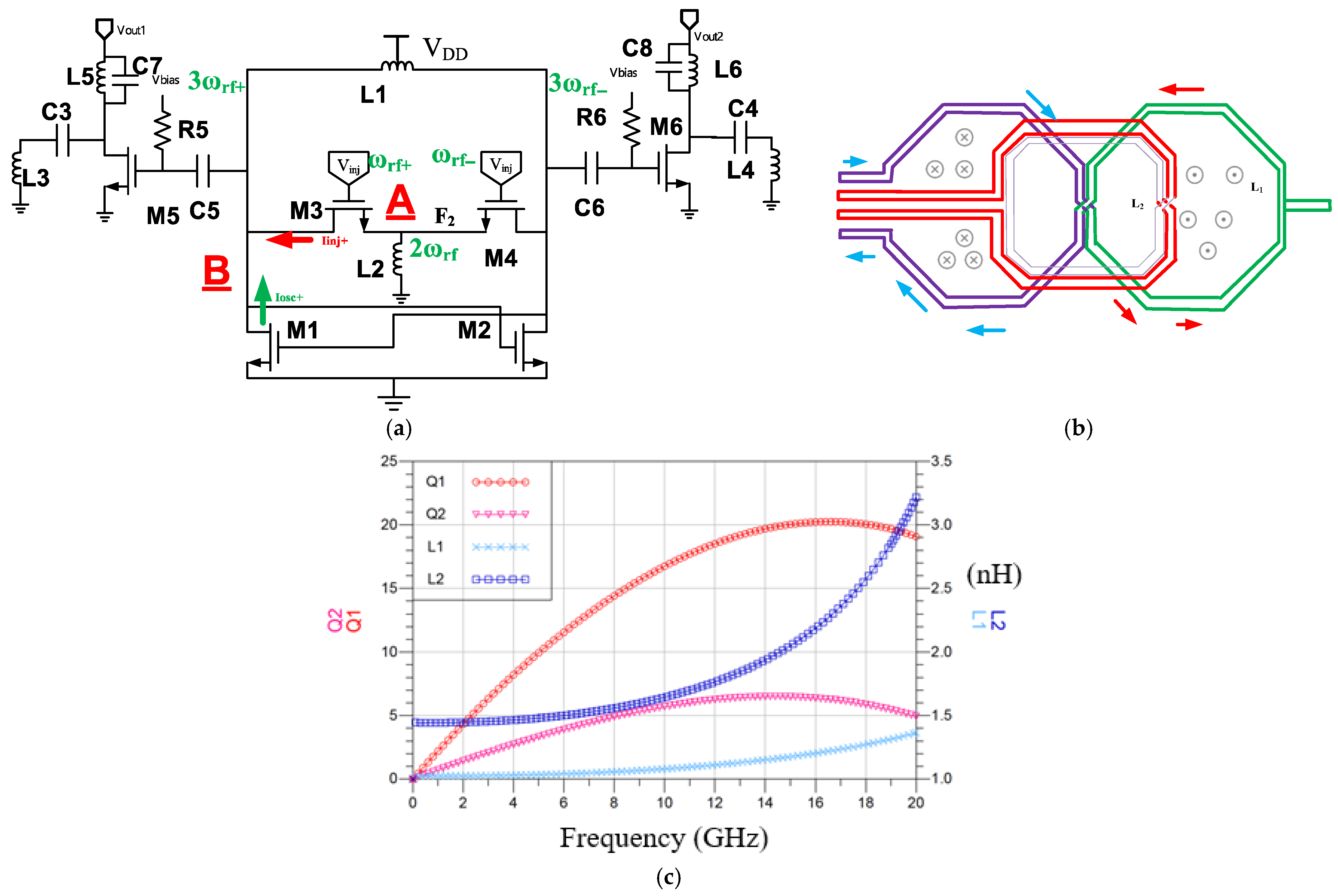

3.1. Circuit Design

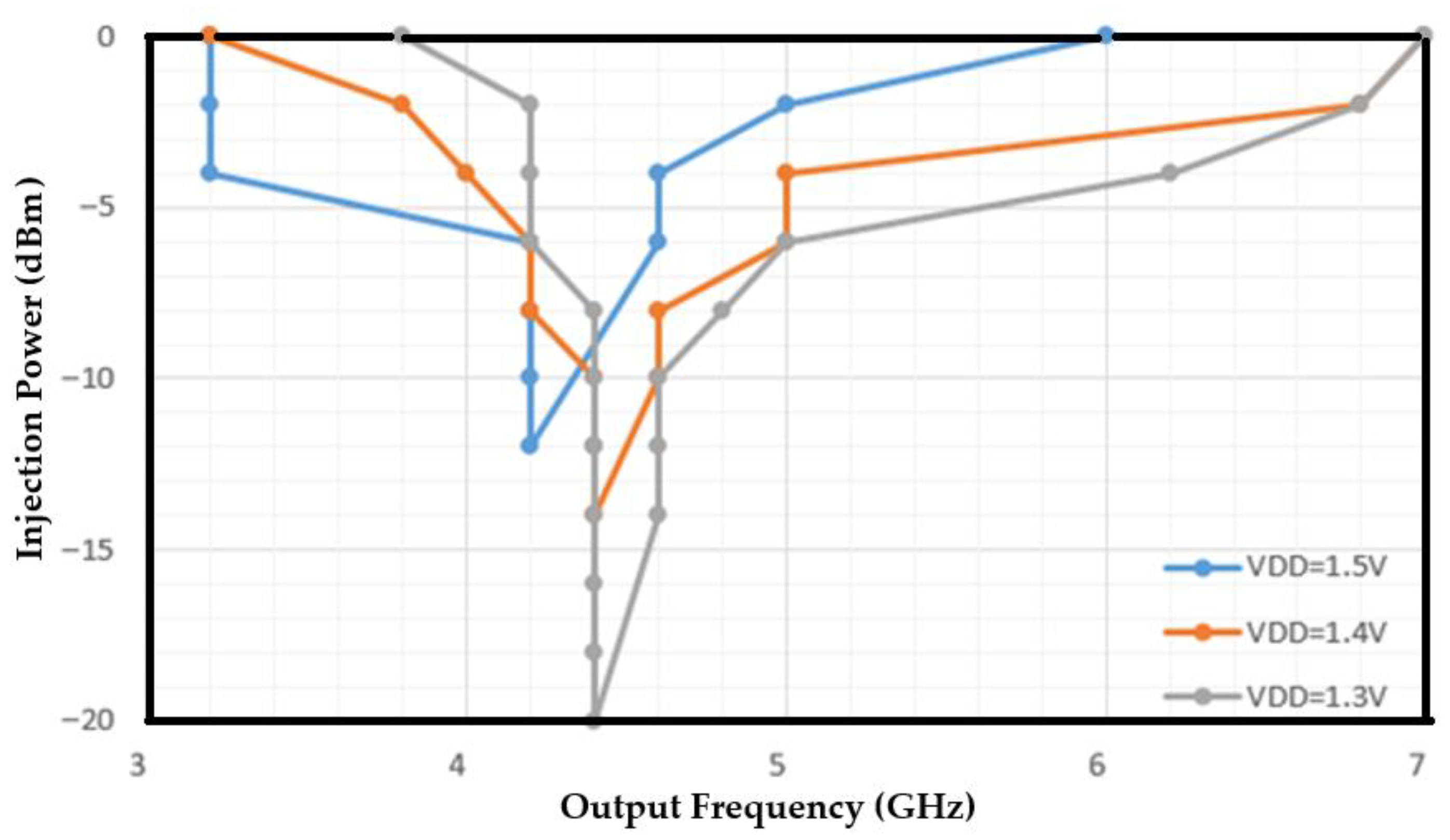

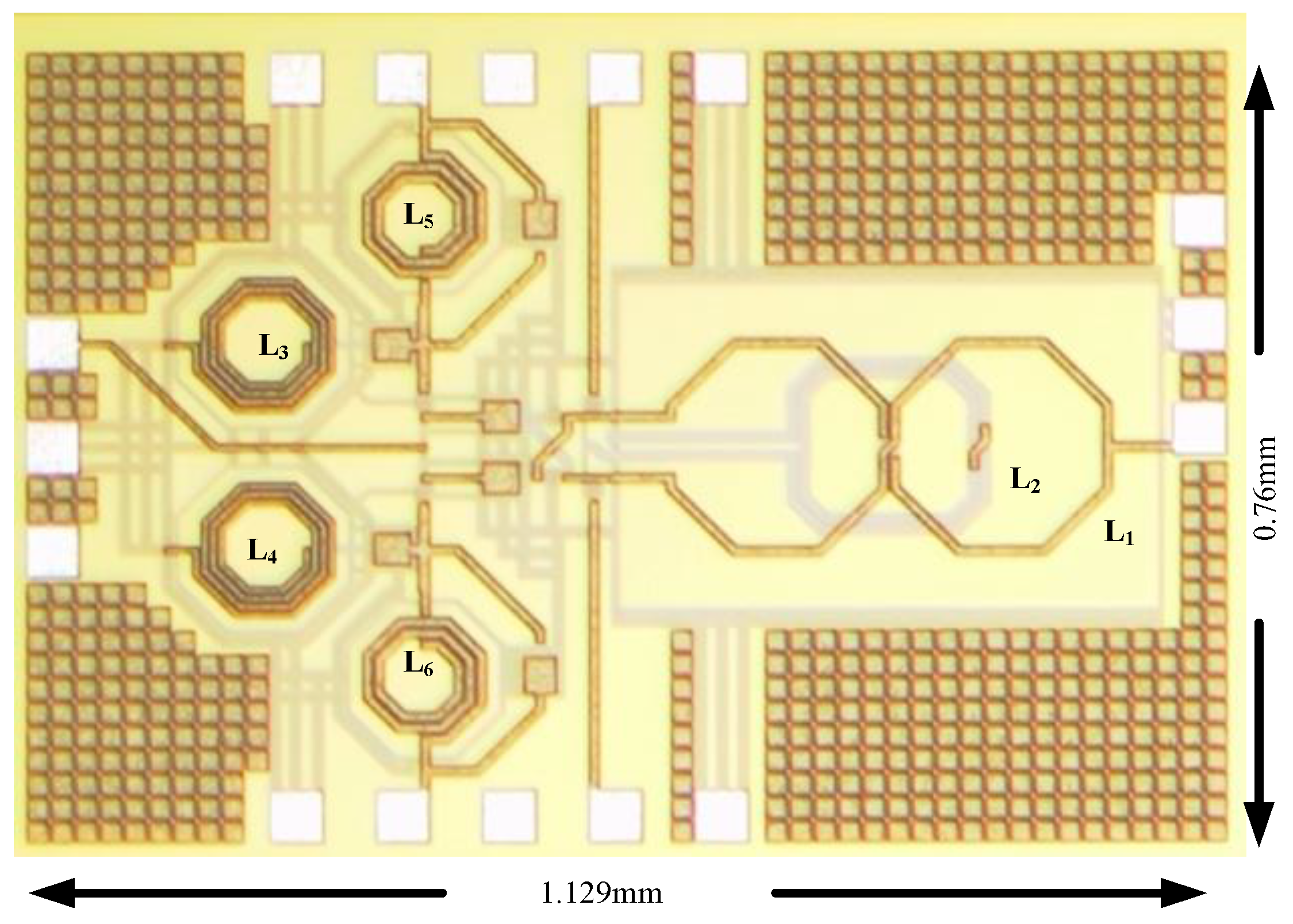

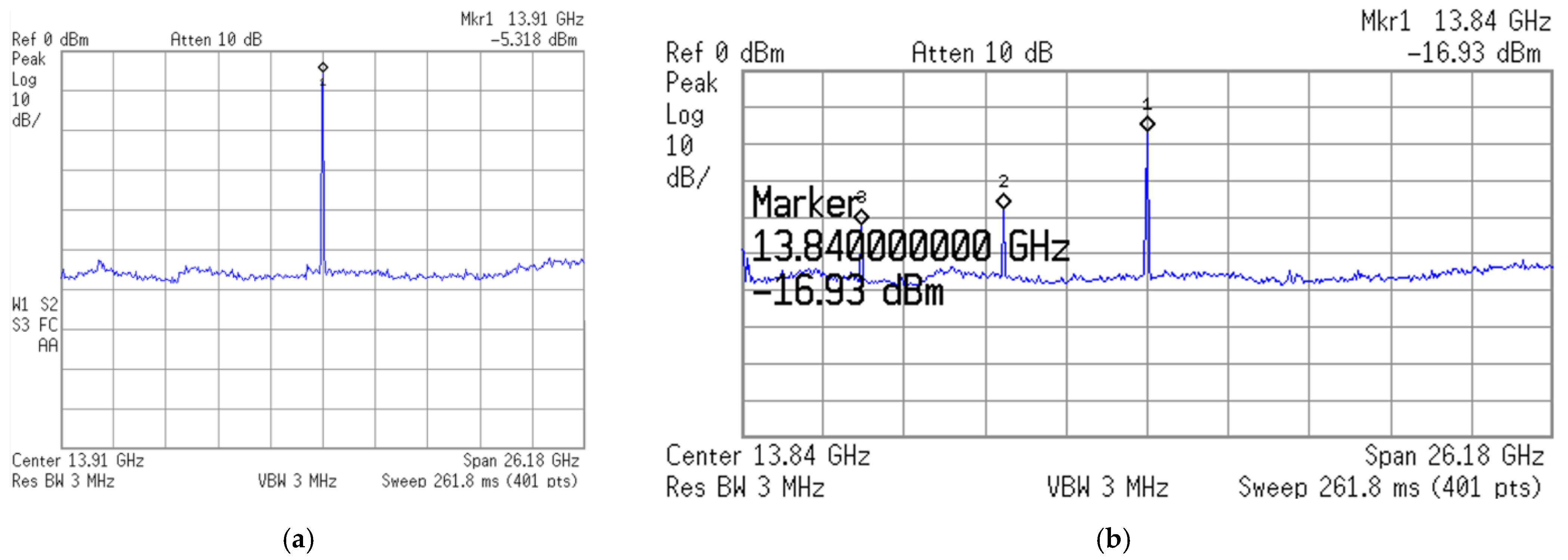

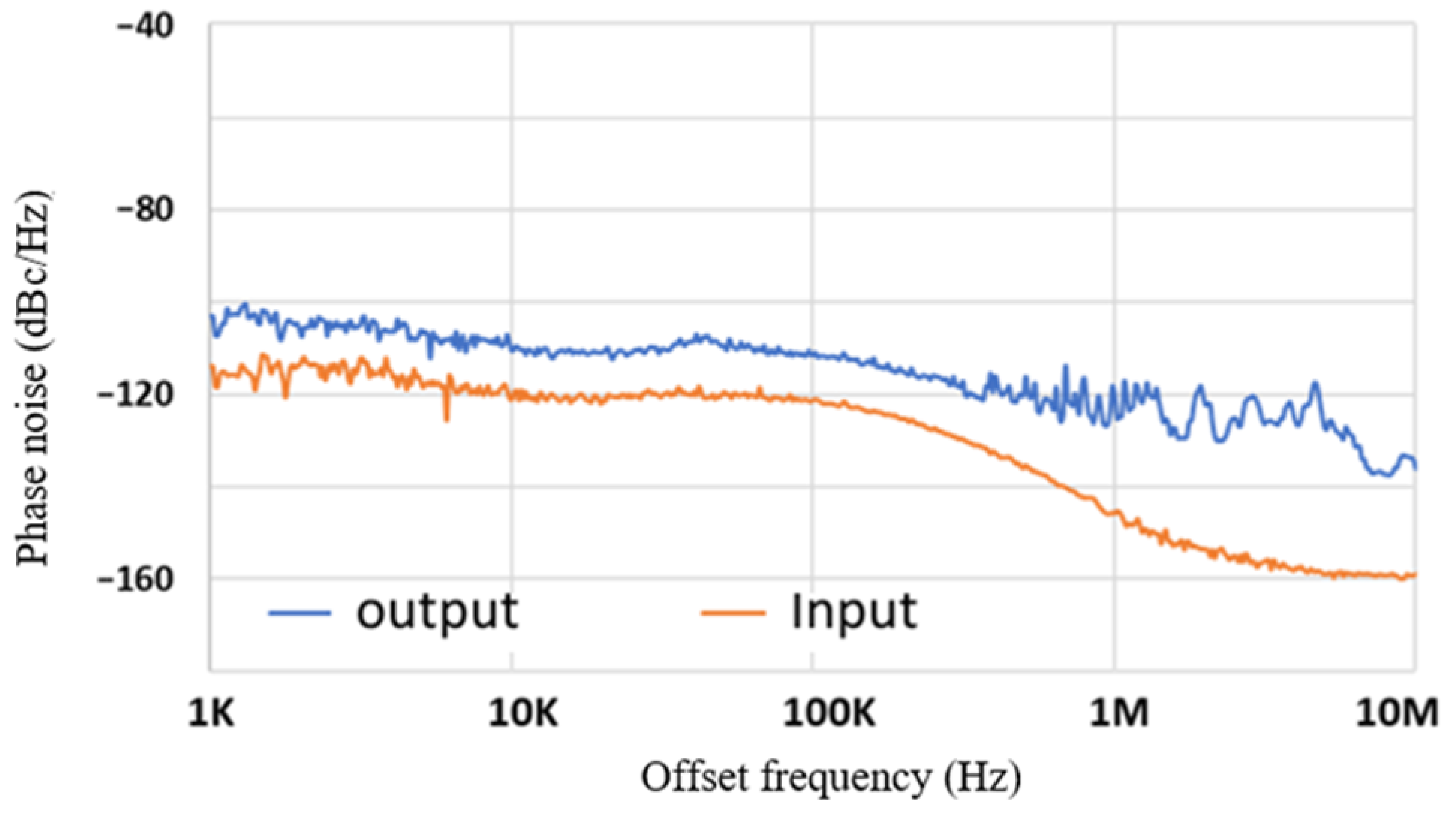

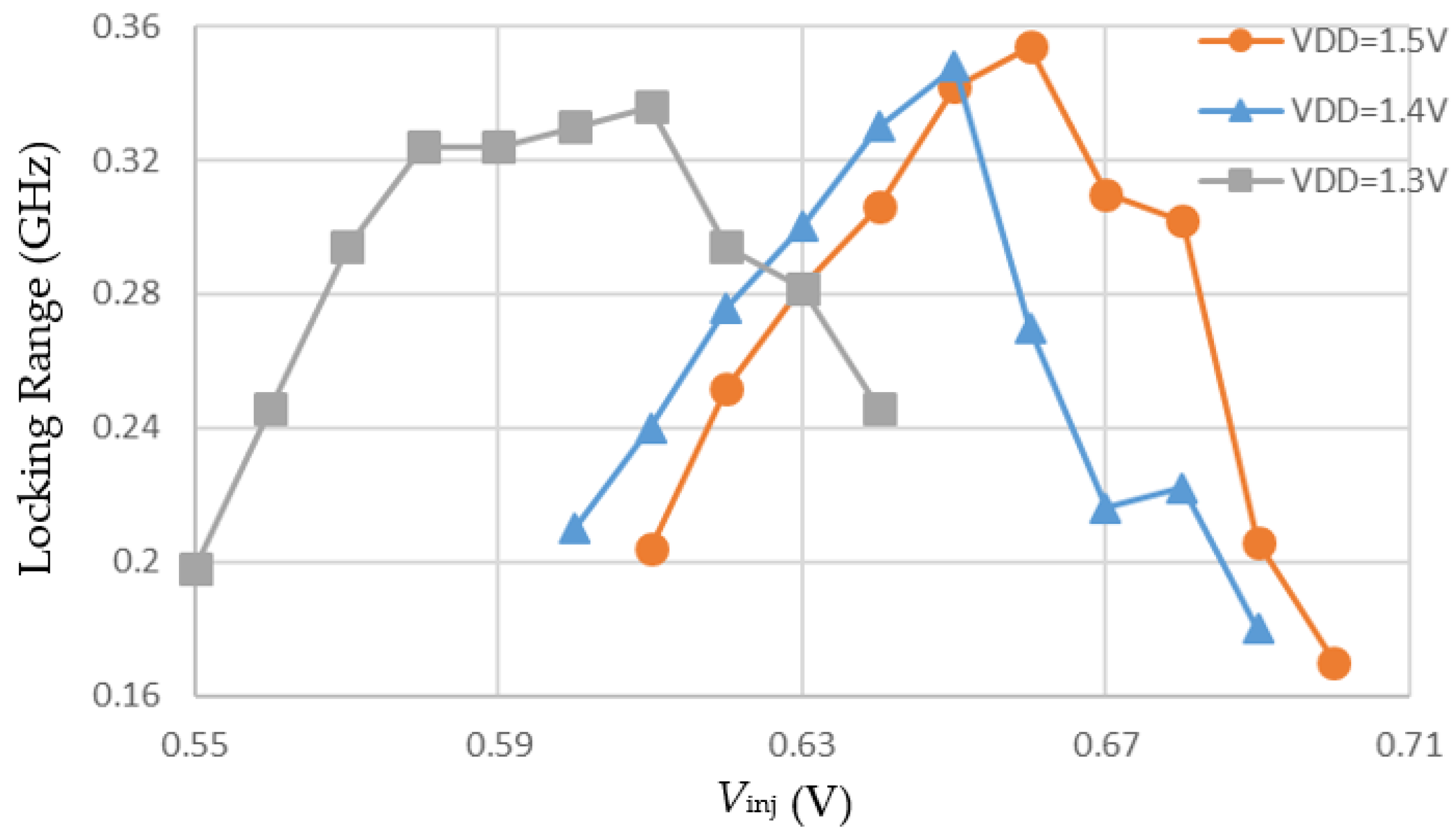

3.2. Experimental Results

4. Multiply-by-6 ILFM

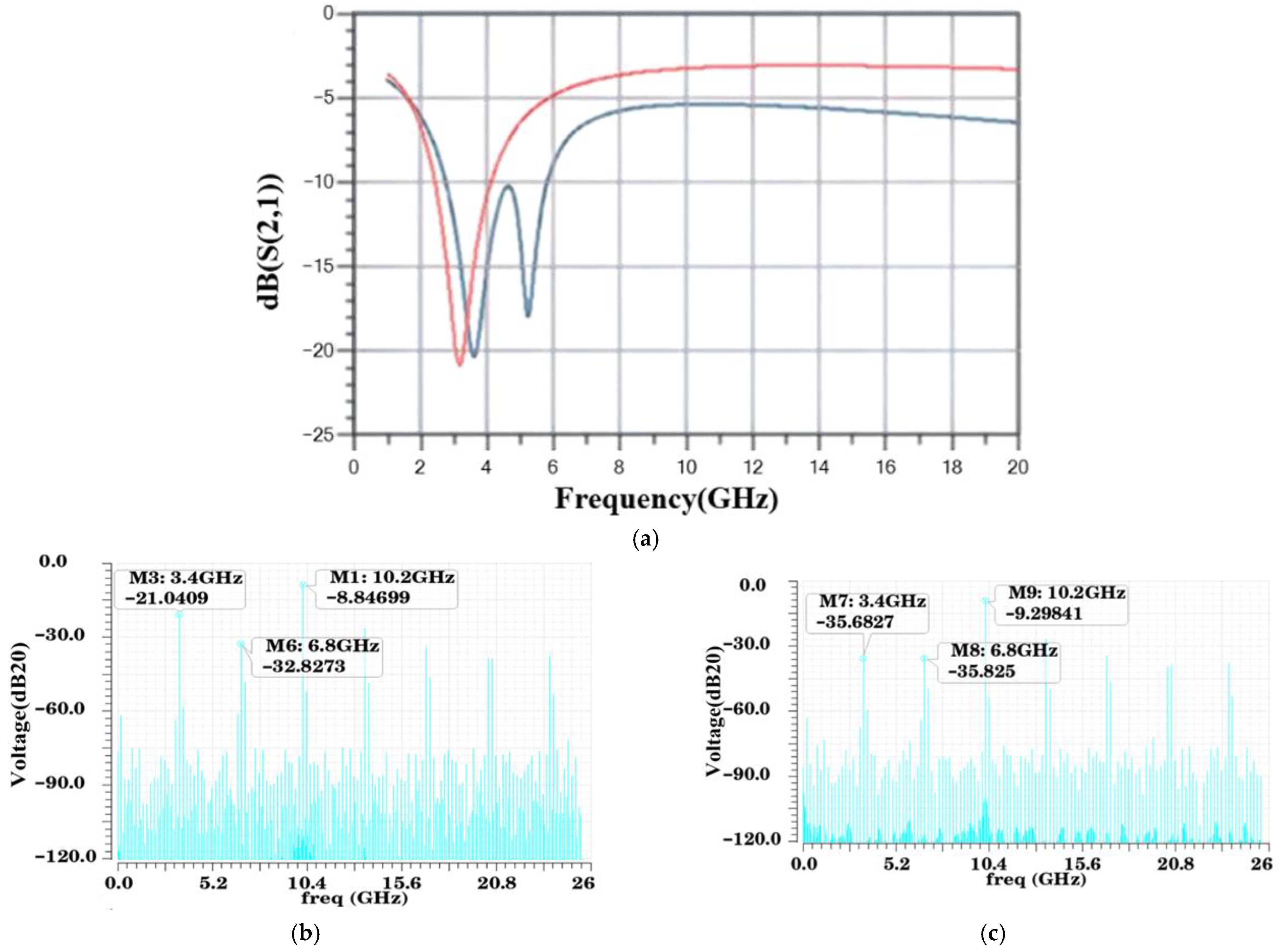

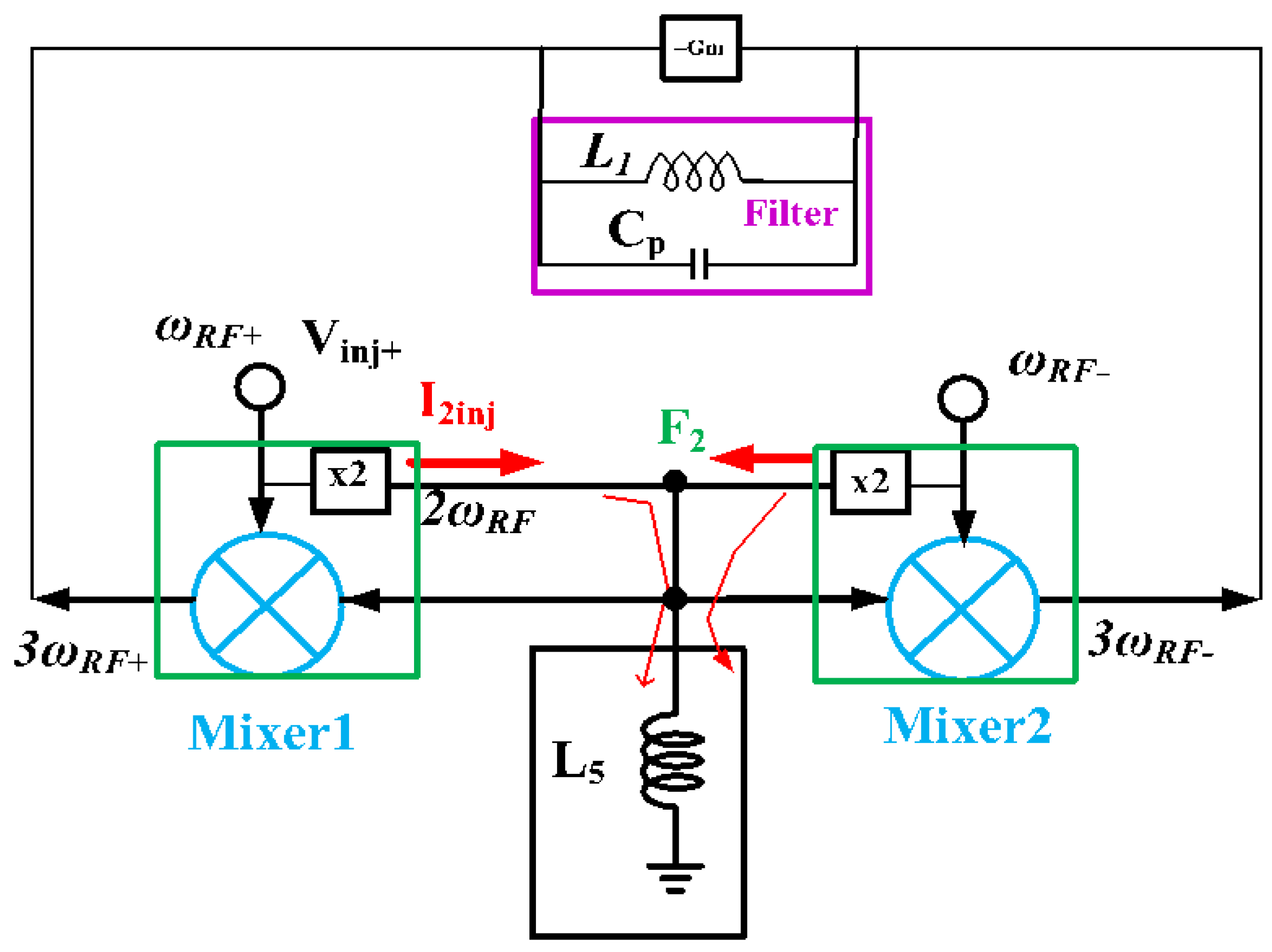

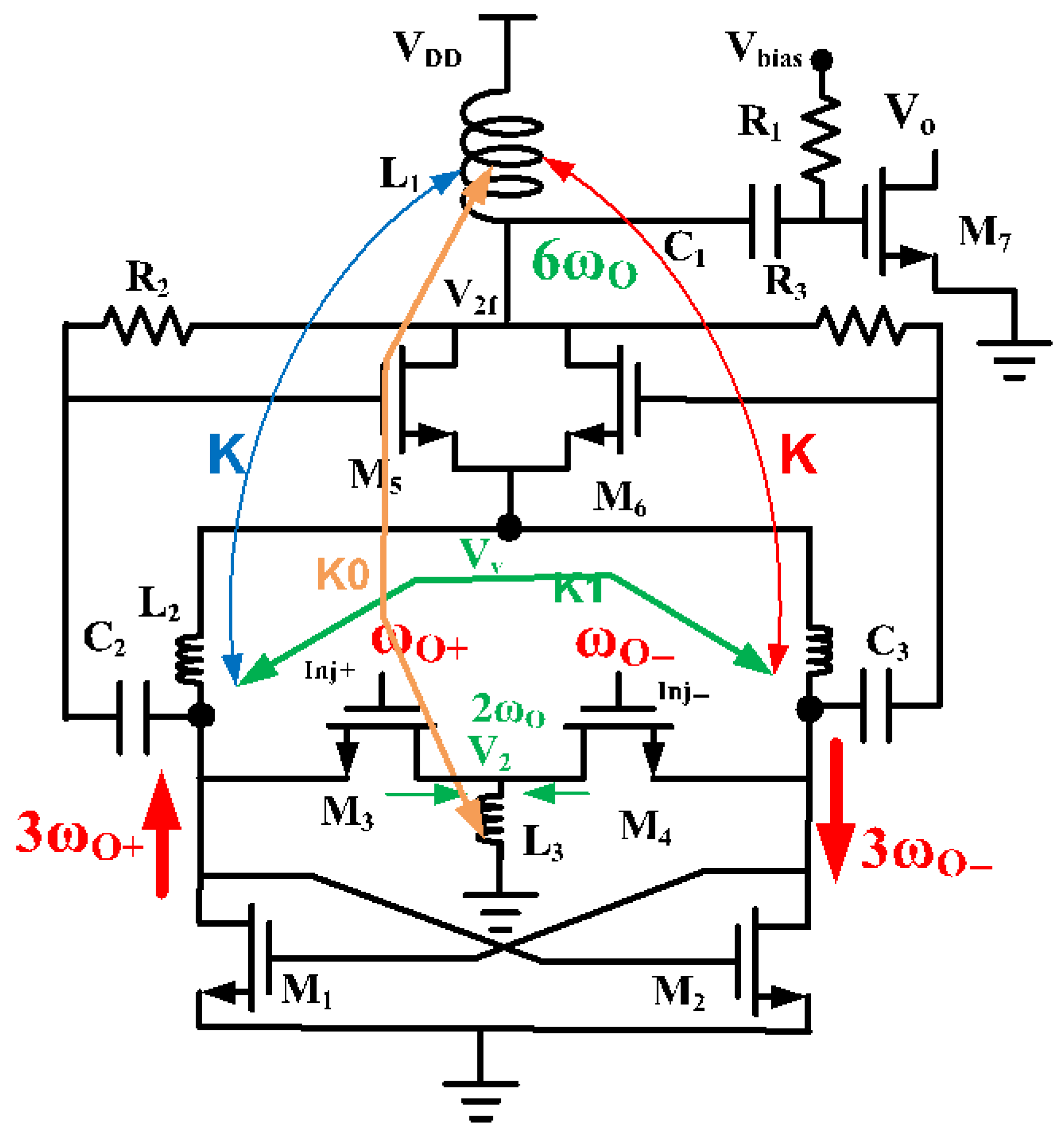

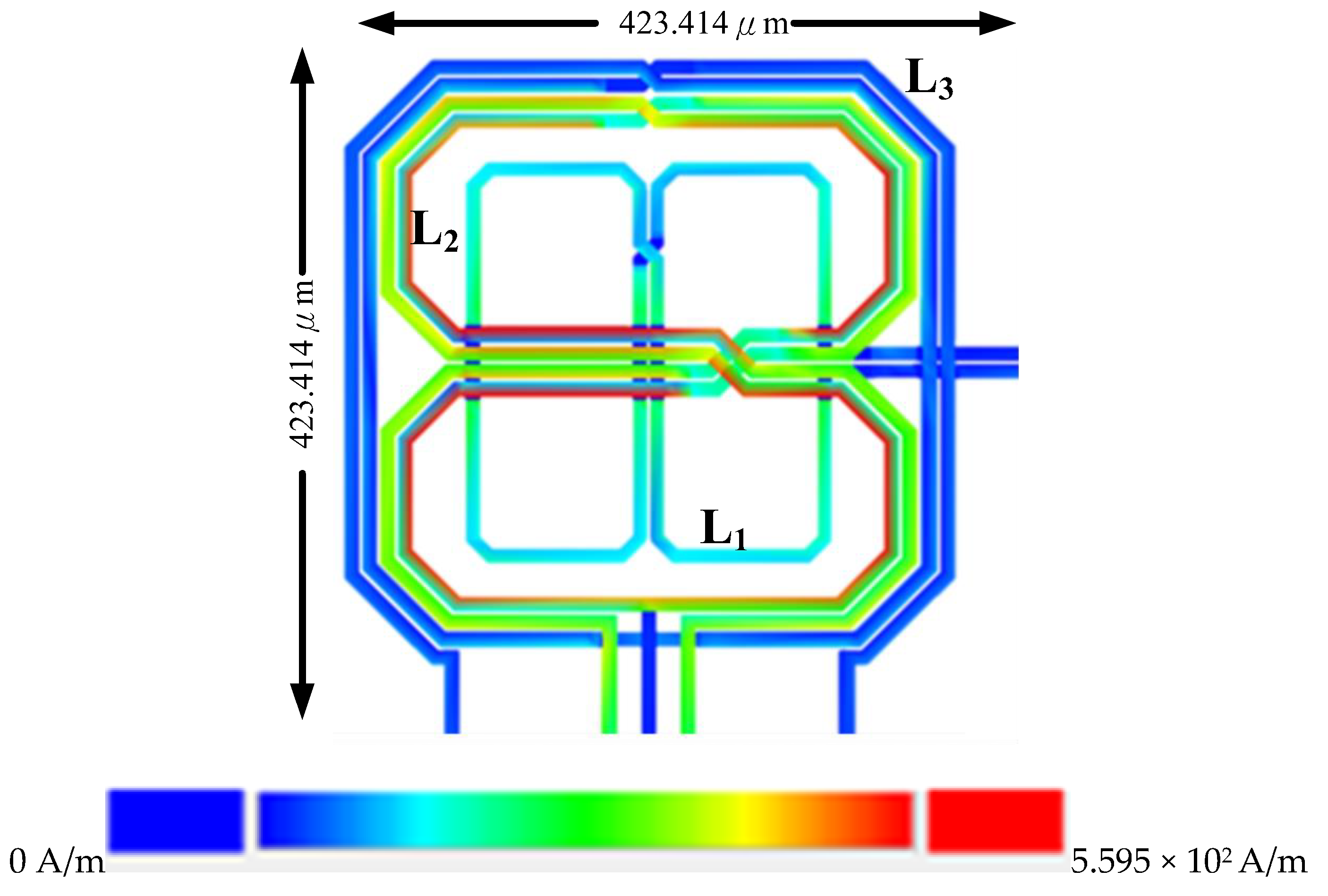

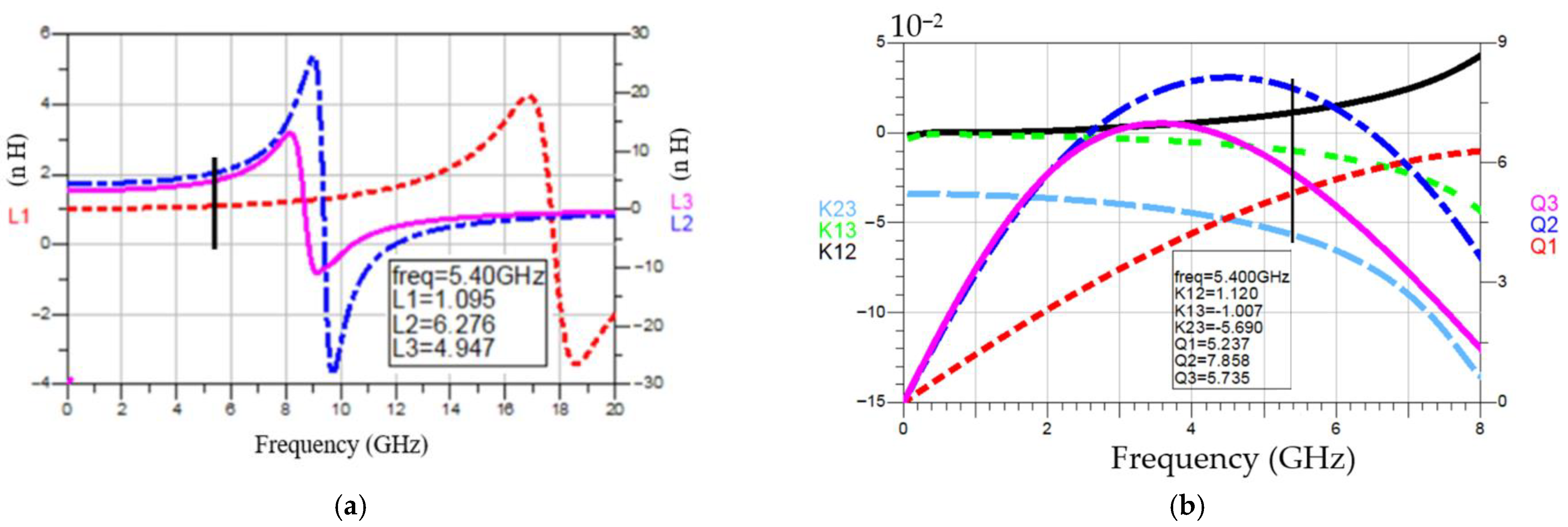

4.1. Circuit Design

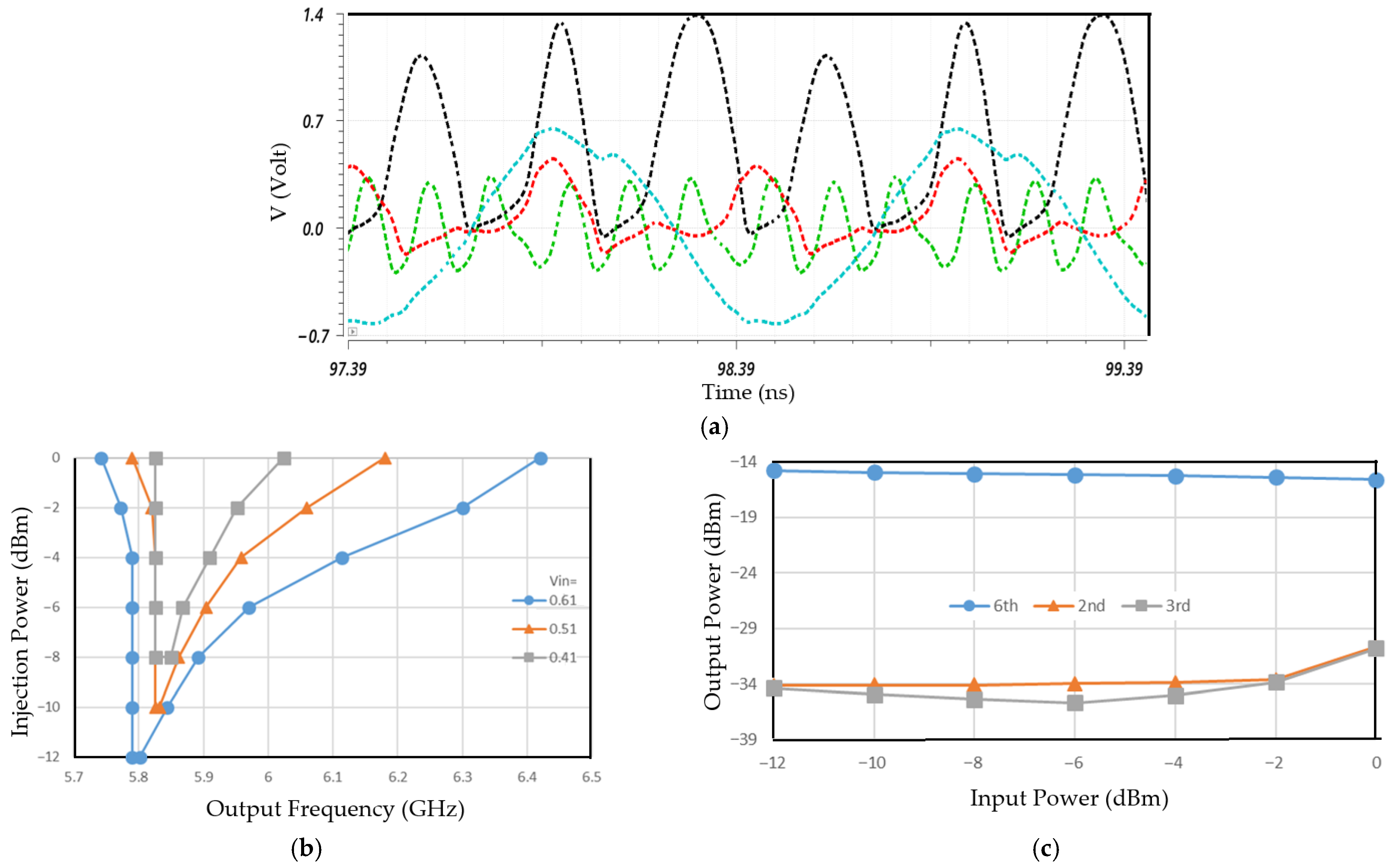

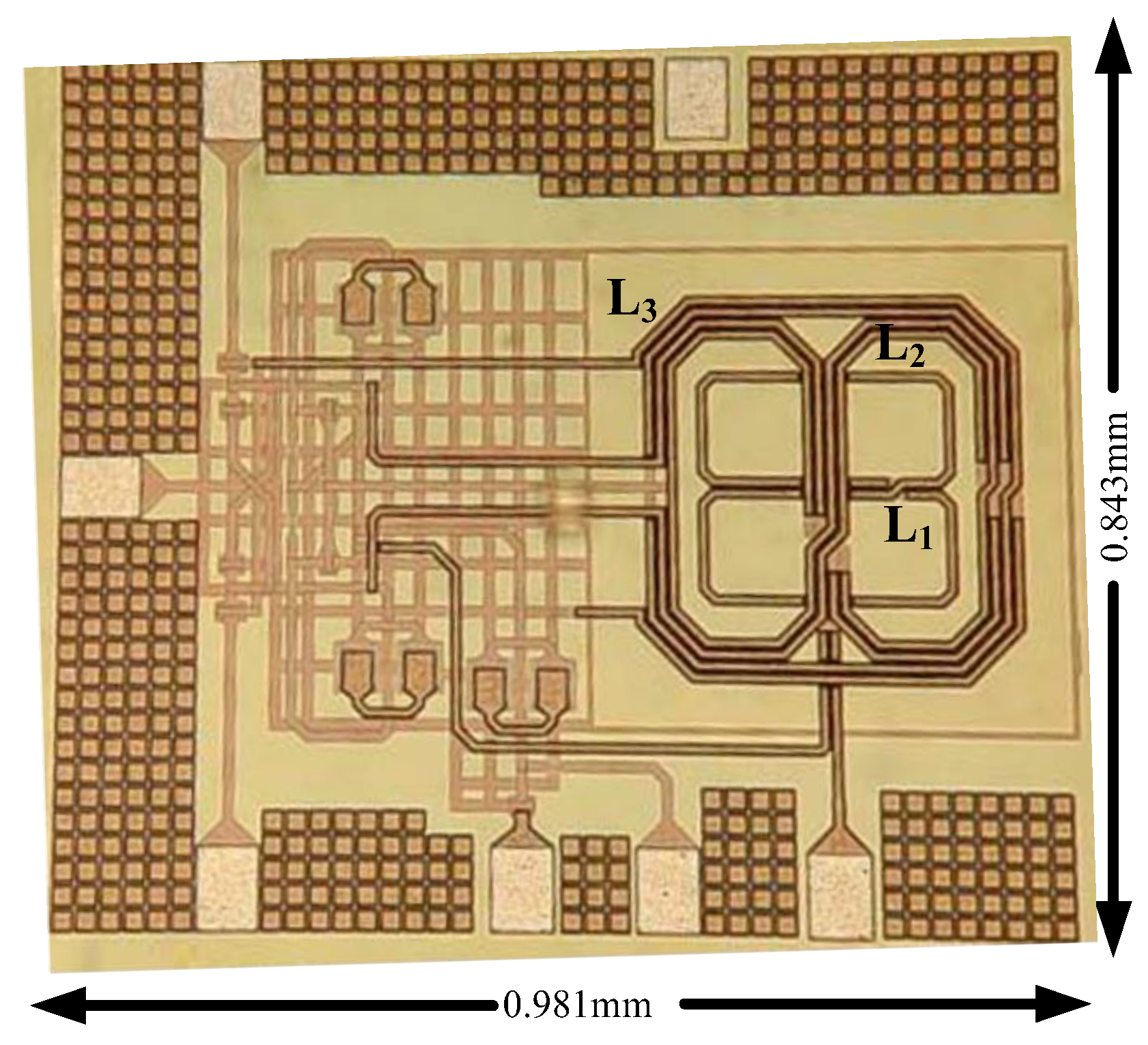

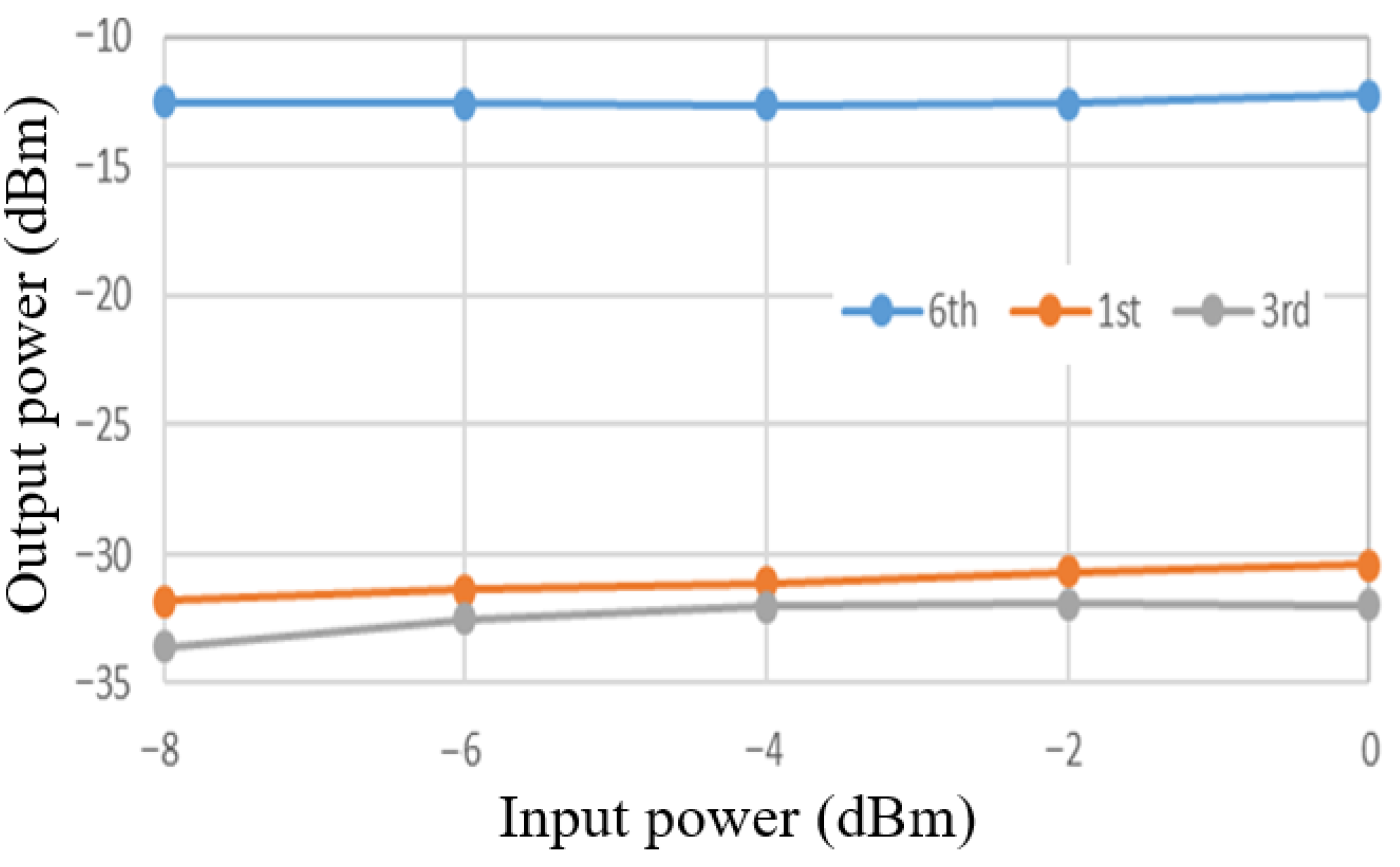

4.2. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Liu, X.; Luong, H.C. A fully Integrated 0.27-THz injection-locked frequency synthesizer with a frequency-tracking loop in 65-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 1051–1063. [Google Scholar] [CrossRef]

- Monaco, E.; Pozzoni, M.; Svelto, F.; Mazzanti, A. Injection-locked CMOS frequency doublers for μ-wave and mm-wave applications. IEEE J. Solid-State Circuits 2010, 45, 1565–1574.

- Kursu, O.; Rahkonen, T.; Pärssinen, A. A 14.6 GHz–19.2 GHz digitally controlled injection-locked frequency doubler in 45 nm SOI CMOS. In Proceedings of the 2021 16th European Microwave Integrated Circuits Conference (EuMIC), London, UK, 3–4 April 2022; pp. 104–107. [Google Scholar] [CrossRef]

- Jia, H.; Kuang, L.; Wang, Z.; Chi, B. A W-band injection-locked frequency doubler based on the top-injected coupled resonator. IEEE Trans. Microw. Theory Tech. 2016, 64, 210–218. [Google Scholar] [CrossRef]

- Iotti, L.; LaCaille, G.; Niknejad, A.M. A 57–74-GHz tail-switching injection-locked frequency tripler in 28-nm CMOS. IEEE Solid-State Circuits Lett. 2019, 2, 115–118. [Google Scholar] [CrossRef]

- Chang, Y.-H.; Chiang, Y.-C. A novel injection-locked frequency tripler for V-band applications. In Proceedings of the 2019 14th European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 30 September–1 October 2019; pp. 290–293. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lai, H.-W.; Sung, J.-Y.; Juang, M.-H. Injection-locked frequency tripler with boosted locking range. IEEE Microw. Wirel. Tech. Lett. 2023, 33, 423–426. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lai, W.-C.; Lu, R.-H. Single-stage injection-locked frequency sixtupler in CMOS process. IEEE Access 2022, 10, 40316–40323. [Google Scholar] [CrossRef]

- Cheng, S.-J.; Shen, P.-N.; Hong, C.-H.; Chen, Z.-W.; Chen, C.-P.; Jang, S.-L. Injection-locked frequency sixtuplers in 90 nm CMOS by using the push-push doubler. IEEE Access 2023, 11, 130048–130059. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lee, Y.-C.; Lai, W.-C. Left-Hand Resonator VCO Using an Orthogonal Transformer. Electronics 2025, 14, 2765. [Google Scholar] [CrossRef]

- Jang, S.-L.; Lin, Z.-J.; Juang, M.-H. State-of-the-Art VCO with Eight-Shaped Resonator-Type Transmission Line. Electronics 2025, 14, 2322. [Google Scholar] [CrossRef]

- Hsu, M.-H.; Jang, S.; Lin, M.-T.; Lai, W.-C.; Juang, M.-H. Differential injection-locked frequency tripler with a low-coupling 8-shaped transformer. In Proceedings of the 2024 21st International SoC Design Conference (ISOCC), Sapporo, Japan, 19–22 August 2024; pp. 388–389. [Google Scholar] [CrossRef]

- Razavi, B. A study of injection locking and pulling in oscillators. IEEE J. Solid-State Circuits 2004, 39, 1415–1424. [Google Scholar] [CrossRef]

- Takatsu, K.; Tamura, H.; Yamamoto, T.; Doi, Y.; Kanda, K.; Shibasaki, T.; Kuroda, T. A 60-GHz 1.65 mW 25.9% locking range multi-order LC oscillator based injection locked frequency divider in 65nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 9–12 September 2012; pp. 1–4. [Google Scholar]

- Jang, S.-L.; Lin, W.-C.; Lai, W.-C.; Juang, M.-H. Area-efficient UWB CMOS power amplifier with hybrid trifilar. In Proceedings of the 2025 IEEE Wireless and Microwave Technology Conference (WAMICON), Cocoa Beach, FL, USA, 14–15 April 2025; pp. 1–4. [Google Scholar] [CrossRef]

| Ref. ×2 | Tech (nm) | Inductor Structure | Pin (dBm) | Vdd(V) Pdis(mW) | Die Area (mm2) | FOM | Locking Range (GHz) |

|---|---|---|---|---|---|---|---|

| [4] TMTT 2016 ×2 | 65 | Spiral tran | 0 | 1/9 | 0.39 × 0.41 | 3.2 | 71~95.0 (28.9%) |

| [3] EuMIC 2022 ×2 | 45 | Spiral indu | 0 | 1/5–11 | 0.12 | 4.55~ | 14.0~17.6 (22.78%) |

| [2] JSSC 2010 ×2 | 65 | Spiral indu | 3 | 1/6 | 0.014 | 2.18 | 106~128 (13.1%) * |

| [12] ISOCC 2024 ×3 | 180 | 8-sha tran | 0 | 0.65/3.25 | 1.146 × 0.484 | 10.75 ** | 7.2~10.25 (34.95%) ** |

| [9] Access 2023 ×6 | 90 | Spiral indu | 0 | 0.4/9.03 | 0.49 | 1.13 | 39~43.2 (10.21%) |

| [8] Access 2022 ×6 | 180 | Spiral indu | 0 | 1/20.8 | 1.141 × 1.2 | 0.4947 | 5.62~6.23 (10.29%) |

| This 1 ×2 | 180 | 8-sha tran | 0 | 1.5/3.966 | 1.137 × 0.797 | 15.347 | 3.2~6 (60.96%) * |

| This 2 ×3 | 180 | 8-sha tran | 0 | 0.7/10.5 | 1.129 × 0.76 | 7.14 | 3~6.6 (75%) *** |

| This 3 ×6 | 180 | 8-s trifilar | 0 | 1.3/13 | 0.843 × 0.981 | 0.3325 | 5.16~5.388 (4.32%) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jang, S.-L.; Lee, C.-Y.; Lee, Y.-C. Injection-Locked Frequency Multipliers with Single Inductor Component. Electronics 2025, 14, 3360. https://doi.org/10.3390/electronics14173360

Jang S-L, Lee C-Y, Lee Y-C. Injection-Locked Frequency Multipliers with Single Inductor Component. Electronics. 2025; 14(17):3360. https://doi.org/10.3390/electronics14173360

Chicago/Turabian StyleJang, Sheng-Lyang, Cheng-Yi Lee, and Yun-Chien Lee. 2025. "Injection-Locked Frequency Multipliers with Single Inductor Component" Electronics 14, no. 17: 3360. https://doi.org/10.3390/electronics14173360

APA StyleJang, S.-L., Lee, C.-Y., & Lee, Y.-C. (2025). Injection-Locked Frequency Multipliers with Single Inductor Component. Electronics, 14(17), 3360. https://doi.org/10.3390/electronics14173360