On the SCA Resistance of TMR-Protected Cryptographic Designs

Abstract

1. Introduction

- We presented the first detailed experimental results of the impact of triple modular redundancy (TMR) on side-channel resistance of FPGA-based asymmetric cryptography designs.

- We demonstrated that TMR can both reduce and amplify SCA leakage depending on design factors such as selective redundancy application.

- We provide guidelines for hardware designers aiming at balancing fault tolerance and side-channel resistance.

2. SCA Attacks Against TMR: State of the Art

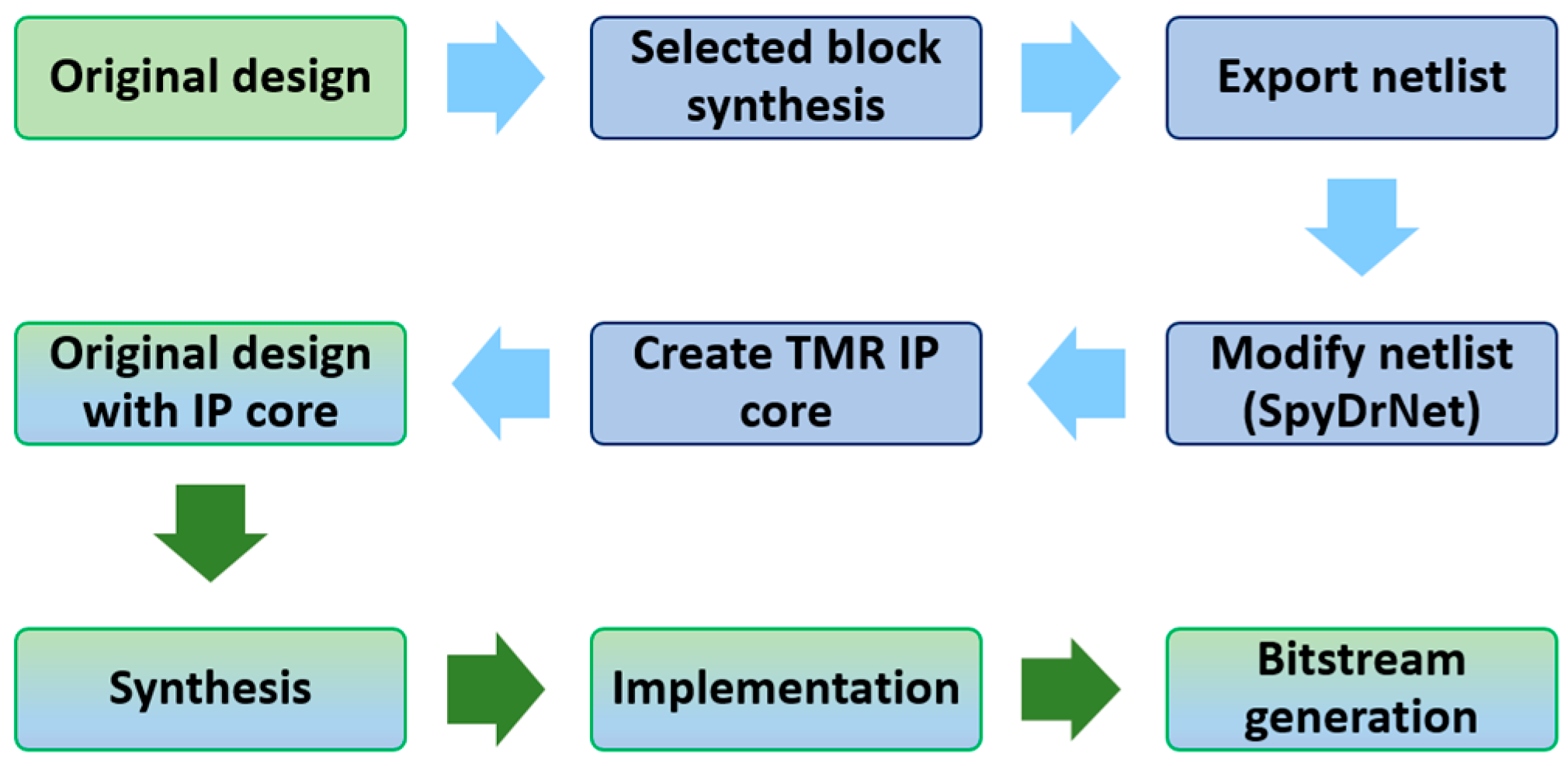

3. Tools for Automated Triple Modular Redundancy Implementation

4. Investigated Designs

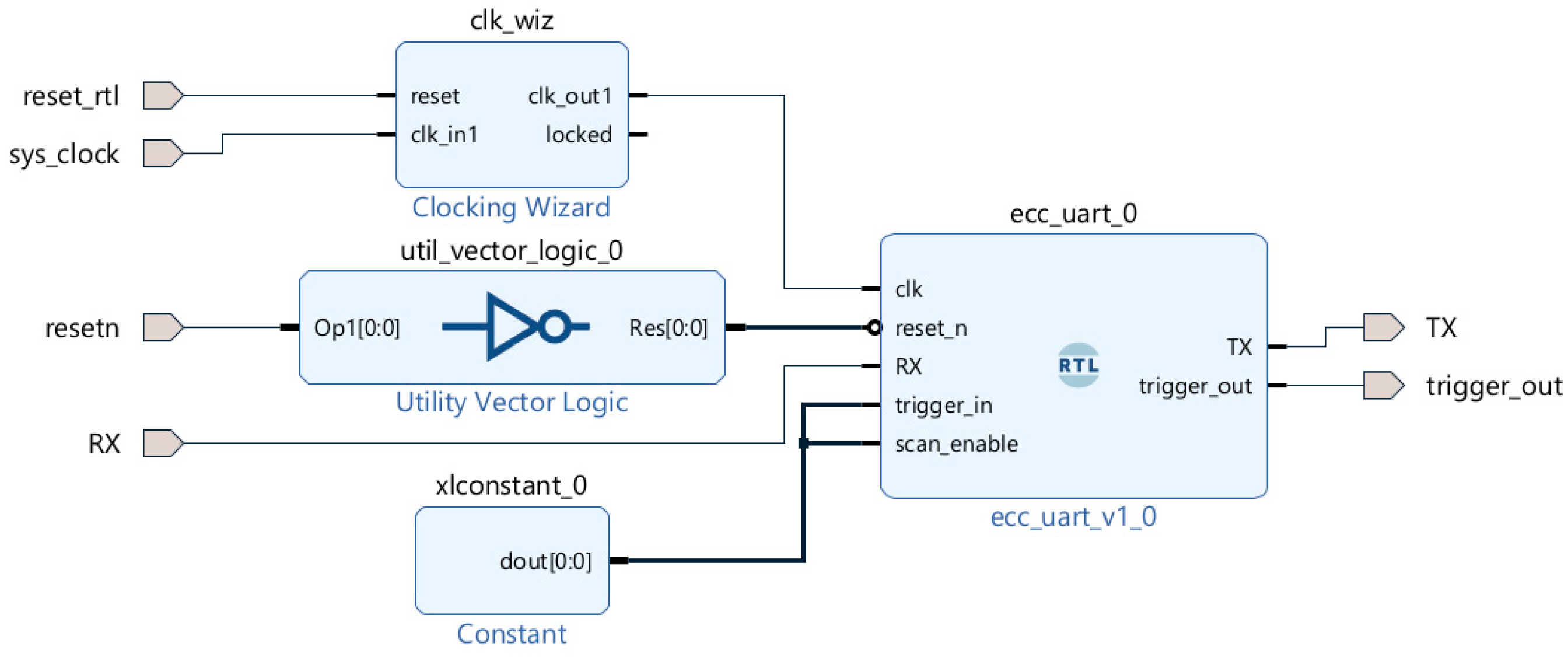

4.1. Original Design

- controller (i_cntr)—manages the sequence of the field operations and data flow between the rest of the components;

- arithmetic logic unit (i_alu)—performs squaring or addition of operands;

- multiplier (i_multiply)—calculates the field product of 233-bit-long operands using 9 partial products according to a fixed calculation plan [26], implemented according to the iterative 4-segment Karatsuba multiplication method;

- partial multiplier (u1)—calculates partial products for the multiplier, implemented using only the classical multiplication formula [29];

- 233-bit-long registers: for the implementation of the main loop of the algorithm (i_x1, i_x2, i_x3, i_x4, i_z1, i_z2), input/output registers (i_x, i_y), and the registers that hold the value of scalar k and the parameter b of the elliptic curve equation (i_ext_reg, i_b);

- muxer (i_sys_mux)—ensures data exchange between design components.

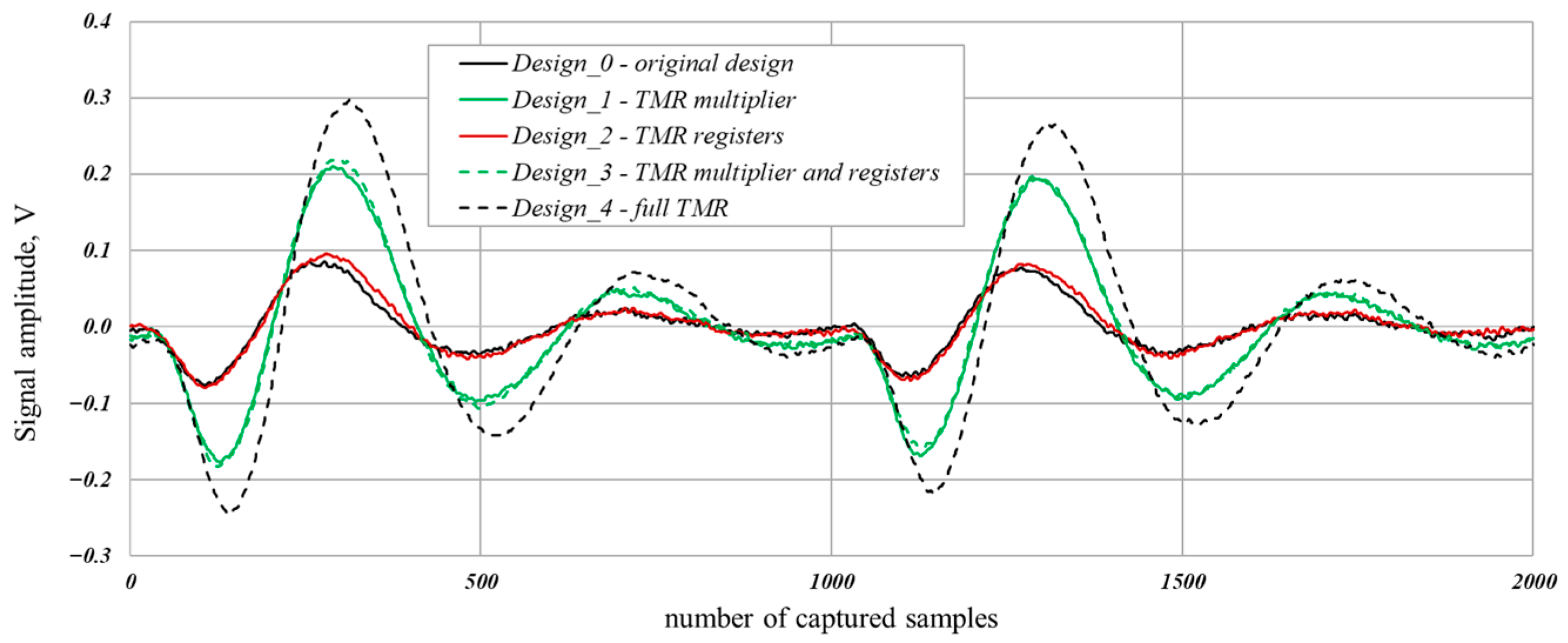

4.2. TMR Instances of the Original Design

- Design_1: contains a multiplier (i.e., the i_multiply component) implemented using TMR;

- Design_2: triple modular redundancy was applied to six registers used in the main loop of the algorithm, i.e., registers i_x1, i_x2, i_x3, i_x4, i_z1, i_z2;

- Design_3: combines the components implemented using TMR logic in Design_1 and Design_2 (i.e., the multiplier and six registers);

- Design_4: the i_ecc part of the ecc_uart_0 block (see Figure 3), responsible for the calculation of the kP operation was implemented using TMR logic.

5. SCA Attack and Results Discussion

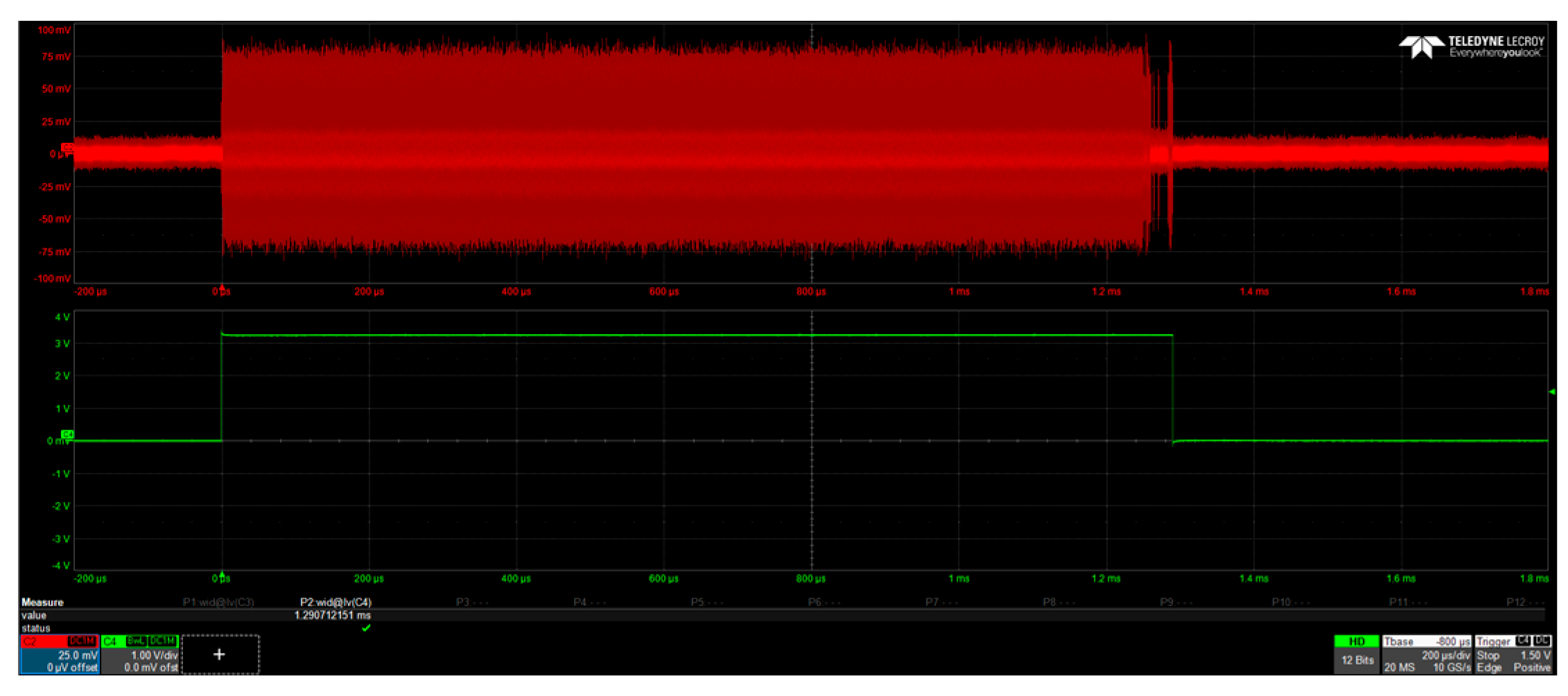

5.1. Measurements

5.2. Performed Attack

5.3. Attack Results and Discussion

6. Conclusions and Future Work

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| AES | Advanced encryption standard |

| CPA | Correlation power analysis |

| CRC | Cyclic redundancy check |

| DPA | Differential power analysis |

| DMR | Double modular redundancy |

| SNR | Signal-to-noise ratio |

| TMR | Triple modular redundancy |

Appendix A

| Algorithm A1: Modified Montgomery algorithm for the kP operation corresponding to [27] |

| Input: k = (kl−1 … k1 k0)2 with kl−1 = 1, P = (x,y) is a point of EC over GF(2l) Output: kP = (x1, y1) 1: X1 ← x, X2 ← x4 + b, Z2 ← x2 //initialization 2: if kl−2 = 1 then //processing second most significant bit 3: T ← Z2, Z1 ← (X1Z2 + X2)2, X1 ← X1Z2X2 + xZ1, 4: T ← X2, U ← b Z24, X2 ← X24+ U, U ← TZ2, Z2 ← U2. 5: else 6: T ← Z2, Z2 ← (X1Z2 + X2)2, X2 ← X1X2T + xZ2, 7: T ← X1, U ← bX24, X1 ← X14 + b, U ← TX2, Z1 ← T2. 8: end if 9: for i from l − 3 downto 0 do //start of the main loop 10: if ki = 1 then 11: T ← Z1, Z1 ← (X1Z2 + X2Z1)2, X1 ← xZ1 + X1X2TZ2, 12: T ← X2, X2 ← X24 + bZ24, Z2 ← T2 Z22. 13: else 14: T ← Z2, Z2 ← (X2Z1 + X1Z2)2, X2 ← xZ2 + X1X2TZ1, 15: T ← X1, X1 ← X14 + b Z14, Z1 ← T2 Z12. 16: end if 17: end for //end of the main loop //calculating affine coordinates of the kP result 18: x1 ← 1/(xZ1Z2) 19: y1 ← y + (x + x1)[(X1 + xZ1)(X2 + xZ2) + (x2 + y)(Z1Z2)] ∙ x1 20: x1 ← X1x1xZ2 // i.e., x1 = X1/Z1 21: return (x1, y1) |

| Design_0 | Design_1 | Design_2 | Design_3 | Design_4 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Logic LUTs | FFs | Logic LUTs | FFs | Logic LUTs | FFs | Logic LUTs | FFs | Logic LUTs | FFs | |

| bd_ecc_i | 5466 | 3706 | 12,285 | 5366 | 6790 | 6502 | 13,687 | 8162 | 22,705 | 10,702 |

| clk_wiz | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| util_vector_logic_0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| ecc_uart_0 | 5465 | 3706 | 12,284 | 5366 | 6789 | 6502 | 13,686 | 8162 | 22,704 | 10,702 |

| (U0 | 2 | 60 | 2 | 60 | 2 | 60 | 2 | 60 | 10 | 60 |

| ❖ i_ecc | 4278 | 3498 | 12,020 | 5158 | 6526 | 6294 | 13,422 | 7954 | 22,465 | 10,494 |

| (i_ecc) | - | - | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| • i_alu | 0 | 233 | 0 | 233 | 0 | 233 | 0 | 233 | 466 | 699 |

| • i_b | 0 | 233 | 0 | 233 | 233 | 233 | 233 | 233 | 478 | 699 |

| • i_cntr | 661 | 104 | 896 | 104 | 895 | 104 | 895 | 104 | 3241 | 312 |

| • i_ext_mux | * | * | 161 | 0 | * | * | 161 | 0 | * | * |

| • i_ext_reg | 0 | 233 | 0 | 233 | 0 | 233 | 0 | 233 | 478 | 699 |

| • i_multiply | 2417 | 830 | 9258 | 2490 | 2368 | 830 | 9262 | 2490 | 8810 | 2490 |

| ◦ u1 | * | * | * | * | 1546 | 0 | * | * | 4762 | 0 |

| • i_sys_mux | 932 | 0 | 932 | 0 | 932 | 0 | 932 | 0 | 2796 | 0 |

| • i_testbit | 64 | 1 | 64 | 1 | 64 | 1 | 65 | 1 | 194 | 3 |

| • i_x | 64 | 233 | 0 | 233 | 297 | 233 | 233 | 233 | 542 | 699 |

| • i_x1 | 18 | 233 | 699 | 233 | 233 | 699 | 233 | 699 | 2563 | 699 |

| • i_x2 | 0 | 233 | 0 | 233 | 233 | 699 | 233 | 699 | 466 | 699 |

| • i_x3 | 0 | 233 | 0 | 233 | 233 | 699 | 233 | 699 | 466 | 699 |

| • i_x4 | 0 | 233 | 0 | 233 | 233 | 699 | 233 | 699 | 466 | 699 |

| • i_y | 122 | 233 | 9 | 233 | 338 | 233 | 242 | 233 | 575 | 699 |

| • i_z1 | 0 | 233 | 0 | 233 | 233 | 699 | 233 | 699 | 466 | 699 |

| • i_z2 | 0 | 233 | 0 | 233 | 233 | 699 | 233 | 699 | 466 | 699 |

| ❖ i_uart | 1187 | 148 | 265 | 148 | 264 | 148 | 265 | 148 | 231 | 148 |

| • up | 1103 | 84 | 186 | 84 | 185 | 84 | 186 | 84 | 143 | 84 |

| • ut | 84 | 64 | 80 | 64 | 80 | 64 | 80 | 64 | 88 | 64 |

| ◦ bg | 21 | 17 | 20 | 17 | 20 | 17 | 20 | 17 | 21 | 17 |

| ◦ ur | 45 | 28 | 44 | 28 | 44 | 28 | 44 | 28 | 49 | 28 |

| ◦ ut | 18 | 19 | 16 | 19 | 16 | 19 | 16 | 19 | 18 | 19 |

References

- Regazzoni, F.; Eisenbarth, T.; Grobschadl, J.; Breveglieri, L.; Ienne, P.; Koren, I.; Paar, C. Power Attacks Resistance of Cryptographic S-boxes with added Error Detection Circuits. In Proceedings of the 22nd IEEE International Symposium on Defect and Fault-Tolerance in VLSI Systems (DFT 2007), Rome, Italy, 26–28 September 2007; pp. 508–516. [Google Scholar] [CrossRef]

- Regazzoni, F.; Eisenbarth, T.; Breveglieri, L.; Ienne, P.; Koren, I. Can Knowledge Regarding the Presence of Countermeasures Against Fault Attacks Simplify Power Attacks on Cryptographic Devices? In Proceedings of the 2008 IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems, Boston, MA, USA, 1–3 October 2008; pp. 202–210. [Google Scholar] [CrossRef]

- UMC. Available online: https://www.umc.com/en/Home/Index (accessed on 19 June 2025).

- Luo, P.; Fei, Y.; Zhang, L.; Ding, A.A. Side-channel power analysis of different protection schemes against fault attacks on AES. In Proceedings of the 2014 International Conference on ReConFigurable Computing and FPGAs (ReConFig14), Cancun, Mexico, 8–10 December 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Pahlevanzadeh, H.; Dofe, J.; Yu, Q. Assessing CPA resistance of AES with different fault tolerance mechanisms. In Proceedings of the 2016 21st Asia and South Pacific Design Automation Conference (ASP-DAC), Macao, China, 25–28 January 2016; pp. 661–666. [Google Scholar] [CrossRef]

- Dofe, J.; Pahlevanzadeh, H.; Yu, Q. A Comprehensive FPGA-Based Assessment on Fault-Resistant AES against Correlation Power Analysis Attack. J. Electron. Test. 2016, 32, 611–624. [Google Scholar] [CrossRef]

- SAKURA-G. Available online: http://www.meytang.com/h-pd-18.html (accessed on 19 June 2025).

- Miškovský, V.; Kubátová, H.; Novotný, M. Influence of fault-tolerant design methods on differential power analysis resistance of AES cipher: Methodics and challenges. In Proceedings of the 2016 5th Mediterranean Conference on Embedded Computing (MECO), Bar, Montenegro, 12–16 June 2016; pp. 14–17. [Google Scholar] [CrossRef]

- Říha, J.; Miškovský, V.; Kubátová, H.; Novotný, M. Influence of Fault-Tolerance Techniques on Power-Analysis Resistance of Cryptographic Design. In Proceedings of the 2017 Euromicro Conference on Digital System Design (DSD), Vienna, Austria, 30 August–1 September 2017; pp. 260–267. [Google Scholar] [CrossRef]

- Bochard, N.; Marchand, C.; Petura, O.; Bossuet, L.; Fischer, V. Evariste III: A new multi-FPGA system for fair benchmarking of hardware dependent cryptographic primitives. In Proceedings of the International Conference on Cryptographic Hardware and Embedded Systems—CHES 2015, Saint Malo, France, 13–16 September 2015. [Google Scholar] [CrossRef]

- Wiki-Evariste. Available online: https://labh-curien.univ-st-etienne.fr/wiki-evariste/index.php/Main_Page (accessed on 19 June 2025).

- Miškovský, V.; Kubátová, H.; Novotný, M. Secure and dependable: Area-efficient masked and fault-tolerant architectures. In Proceedings of the 2021 24th Euromicro Conference on Digital System Design (DSD), Palermo, Italy, 1–3 September 2021; pp. 333–338. [Google Scholar] [CrossRef]

- Bogdanov, A.; Knudsen, L.R.; Leander, G.; Paar, C.; Poschmann, A.; Robshaw, M.J.; Seurin, Y.; Vikkelsoe, C. PRESENT: An Ultra-Lightweight Block Cipher. In Proceedings of the Cryptographic Hardware and Embedded Systems—CHES 2007, Vienna, Austria, 10–13 September 2007; Paillier, P., Verbauwhede, I., Eds.; Springer: Berlin/Heidelberg, Germany, 2007; pp. 450–466. [Google Scholar] [CrossRef]

- Welch, B.L. The Generalization of ‘Student’s’ Problem when Several Different Population Variances are Involved. Biometrika 1947, 34, 28–35. [Google Scholar] [CrossRef] [PubMed]

- Almeida, F.; Aksoy, L.; Raik, J.; Pagliarini, S. Side-Channel Attacks on Triple Modular Redundancy Schemes. In Proceedings of the 2021 IEEE 30th Asian Test Symposium (ATS), Matsuyama, Japan, 22–25 November 2021; pp. 79–84. [Google Scholar] [CrossRef]

- Synopsys. FPGA Design Solution for High-Reliability Applications. Available online: https://www.synopsys.com/content/dam/synopsys/implementation&signoff/datasheets/fpga-design-solution-for-high-reliability-applications-brochure.pdf (accessed on 19 June 2025).

- Precision Hi-Rel, Siemens Digital Industries Software. Available online: https://eda.sw.siemens.com/en-US/ic/precision/hi-rel/ (accessed on 19 June 2025).

- Xilinx TMRTool: Industry’s First Triple Modular Redundancy Development Tool for Reconfigurable FPGAs. Available online: https://www.xilinx.com/publications/prod_mktg/CS11XX_TRMTool_Product_Brief_FINAL0806.pdf (accessed on 13 August 2025).

- SourceForge. BYU EDIF Tools. Available online: https://sourceforge.net/projects/byuediftools/ (accessed on 19 June 2025).

- SpyDrNet|Home. Available online: https://byuccl.github.io/spydrnet-tmr/ (accessed on 19 June 2025).

- Python. byuccl/spydrnet BYU Configurable Computing Lab (29 May 2025). Available online: https://github.com/byuccl/spydrnet (accessed on 19 June 2025).

- AMD. AMD VivadoTM Design Suite. Available online: https://www.amd.com/en/products/software/adaptive-socs-and-fpgas/vivado.html (accessed on 25 June 2025).

- NIST SP 800-186; Recommendations for Discrete Logarithm-Based Cryptography: Elliptic Curve Domain Parameters. National Institute of Standards and Technology: Gaithersburg, MD, USA, 2023.

- Kabin, I.; Dyka, Z.; Klann, D.; Langendoerfer, P. Horizontal DPA Attacks against ECC: Impact of Implemented Field Multiplication Formula. In Proceedings of the 2019 14th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Mykonos, Greece, 16–18 April 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Kabin, I.; Dyka, Z.; Klann, D.; Langendoerfer, P. Methods increasing inherent resistance of ECC designs against horizontal attacks. Integration 2020, 73, 50–67. [Google Scholar] [CrossRef]

- Kabin, I.; Dyka, Z.; Langendoerfer, P. Atomicity and Regularity Principles Do Not Ensure Full Resistance of ECC Designs against Single-Trace Attacks. Sensors 2022, 22, 3083. [Google Scholar] [CrossRef] [PubMed]

- Kabin, I. Horizontal Address-Bit SCA Attacks Against ECC and Appropriate Countermeasures. Ph.D. Thesis, BTU Cottbus-Senftenberg, Senftenberg, Germany, 2023. [Google Scholar] [CrossRef]

- Arty Z7—Digilent Reference. Available online: https://digilent.com/reference/programmable-logic/arty-z7/start (accessed on 19 June 2025).

- Hankerson, D.; Menezes, A.J.; Vanstone, S. Guide to Elliptic Curve Cryptography; Springer: Berlin/Heidelberg, Germany, 2003. [Google Scholar]

- Langer EMV—ICS 105 set, IC Scanner 4-Axis Positioning System. Available online: https://www.langer-emv.de/en/product/langer-scanner/41/ics-105-set-ic-scanner-4-axis-positioning-system/144 (accessed on 25 June 2025).

- Langer EMV—MFA-R 0.2-75, Near-Field Micro Probe 1 MHz up to 1 GHz. Available online: https://www.langer-emv.de/en/product/mfa-active-1mhz-up-to-6-ghz/32/mfa-r-0-2-75-near-field-micro-probe-1-mhz-up-to-1-ghz/854 (accessed on 25 June 2025).

- Arty Z7—Schematic. Available online: https://files.digilent.com/resources/programmable-logic/arty-z7/arty-z7-d0-sch.PDF (accessed on 19 June 2025).

- Teledyne LeCroy—WavePro 254HD. Available online: https://www.teledynelecroy.com/oscilloscope/wavepro-hd-oscilloscope/wavepro-254hd (accessed on 25 June 2025).

- Kabin, I.; Dyka, Z.; Klann, D.; Mentens, N.; Batina, L.; Langendoerfer, P. Breaking a fully Balanced ASIC Coprocessor Implementing Complete Addition Formulas on Weierstrass Elliptic Curves. In Proceedings of the 2020 23rd Euromicro Conference on Digital System Design (DSD), Kranj, Slovenia, 26–28 August 2020; pp. 270–276. [Google Scholar] [CrossRef]

| FPGA Resources | Available | Used (Utilization) | ||||

|---|---|---|---|---|---|---|

| Design | Design_0 | Design_1 | Design_2 | Design_3 | Design_4 | |

| Slice | 13,300 | 1775 (13.35%) | 3721 (27.98%) | 2302 (17.31%) | 4304 (32.36%) | 7542 (56.71%) |

| SLICEL | 1308 | 2664 | 1720 | 3071 | 5094 | |

| SLICEM | 467 | 1057 | 582 | 1233 | 2448 | |

| LUT as Logic | 53,200 | 5466 (10.27%) | 12,285 (23.09%) | 6790 (12.76%) | 13,687 (25.73%) | 22,705 (42.68%) |

| Using O6 output only | 4631 | 9723 | 6259 | 11,129 | 18,090 | |

| Using O5 and O6 | 835 | 2562 | 531 | 2558 | 4615 | |

| Slice Registers | 106,400 | 3706 (3.48%) | 5366 (5.04%) | 6502 (6.11%) | 8162 (7.67%) | 10,702 (10.06%) |

| Register driven from within the Slice | 1891 | 2727 | 2014 | 2804 | 5274 | |

| Register driven from outside the Slice | 1815 | 2639 | 4488 | 5358 | 5428 | |

| LUT in front of the register is unused | 1169 | 1045 | 1394 | 1339 | 1775 | |

| LUT in front of the register is used | 646 | 1594 | 3094 | 4019 | 3653 | |

| Unique Control Sets | 13,300 | 69 (0.52%) | 71 (0.53%) | 69 (0.52%) | 71 (0.53%) | 163 (1.23%) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kabin, I.; Langendoerfer, P.; Dyka, Z. On the SCA Resistance of TMR-Protected Cryptographic Designs. Electronics 2025, 14, 3318. https://doi.org/10.3390/electronics14163318

Kabin I, Langendoerfer P, Dyka Z. On the SCA Resistance of TMR-Protected Cryptographic Designs. Electronics. 2025; 14(16):3318. https://doi.org/10.3390/electronics14163318

Chicago/Turabian StyleKabin, Ievgen, Peter Langendoerfer, and Zoya Dyka. 2025. "On the SCA Resistance of TMR-Protected Cryptographic Designs" Electronics 14, no. 16: 3318. https://doi.org/10.3390/electronics14163318

APA StyleKabin, I., Langendoerfer, P., & Dyka, Z. (2025). On the SCA Resistance of TMR-Protected Cryptographic Designs. Electronics, 14(16), 3318. https://doi.org/10.3390/electronics14163318