A Hybrid Recursive Trigonometric Technique for Direct Digital Frequency Synthesizer

Abstract

1. Introduction

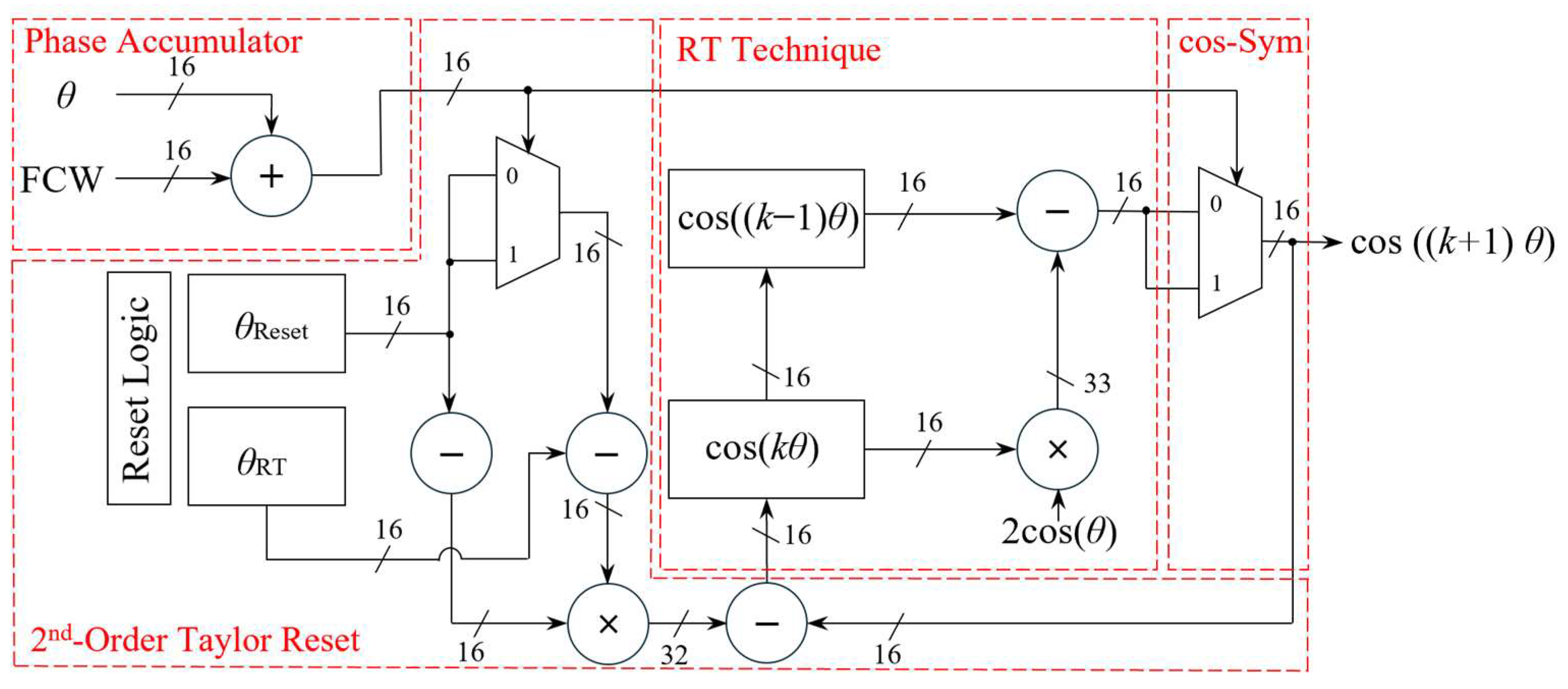

2. Proposed Hybrid RT Technique

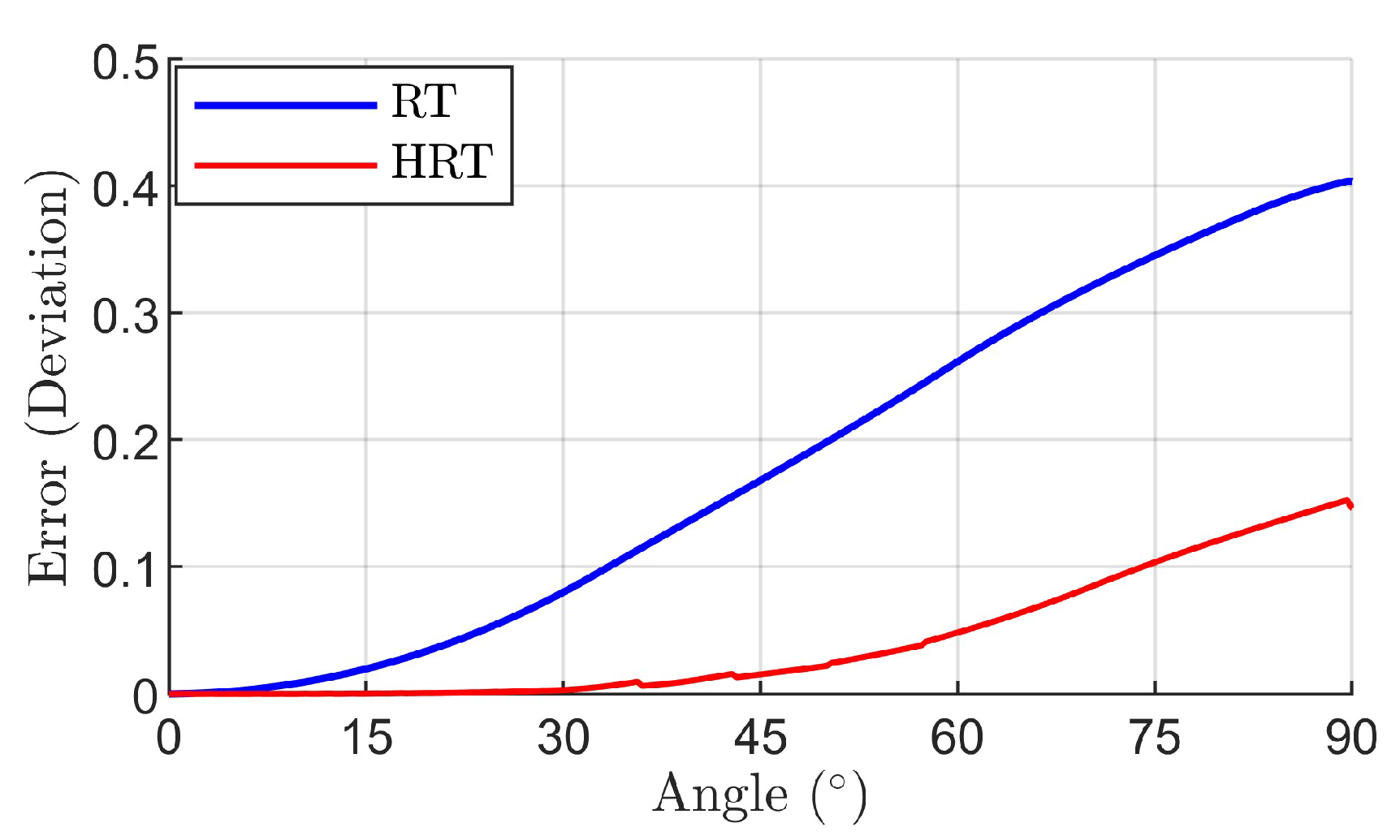

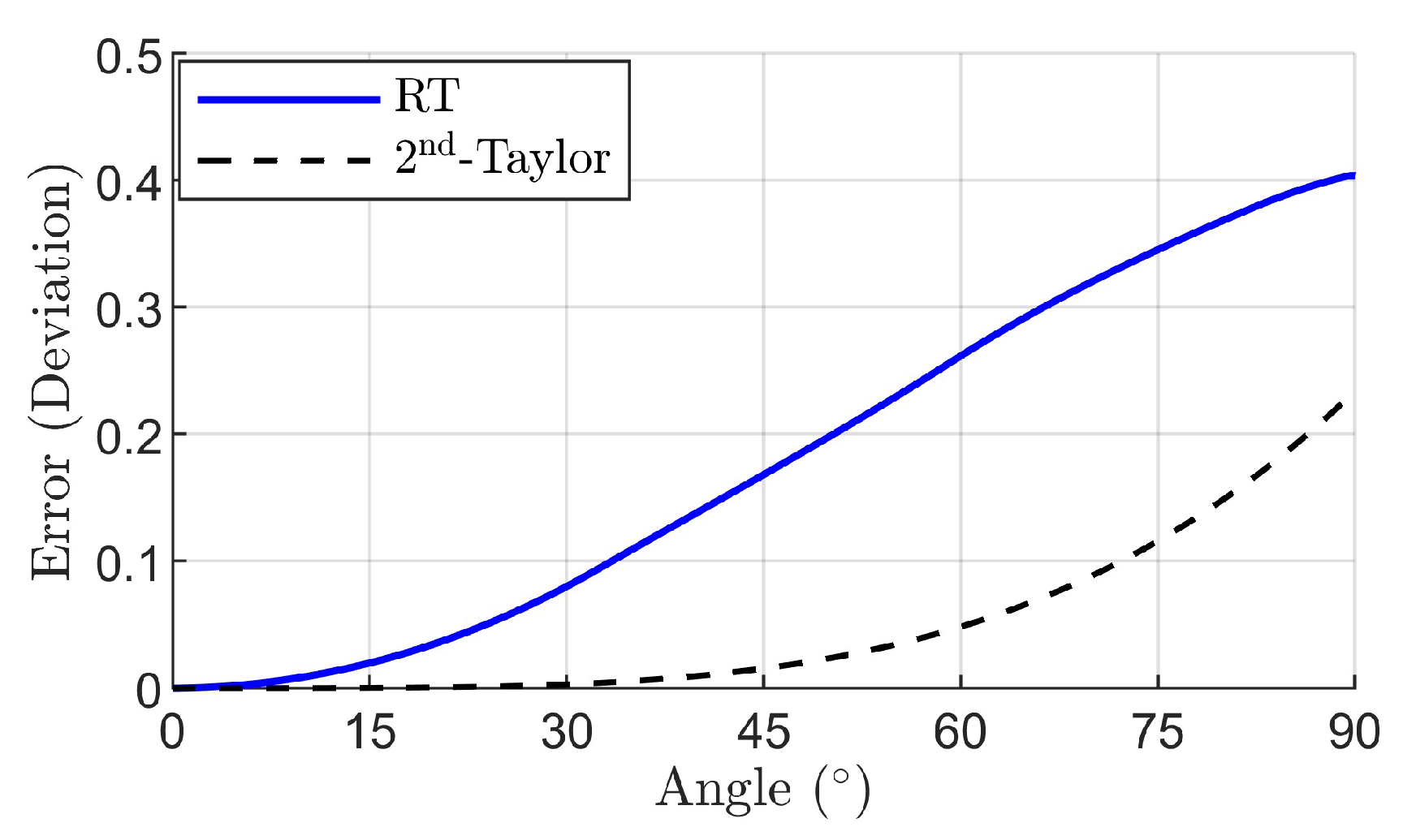

2.1. Fundamentals of the RT Technique

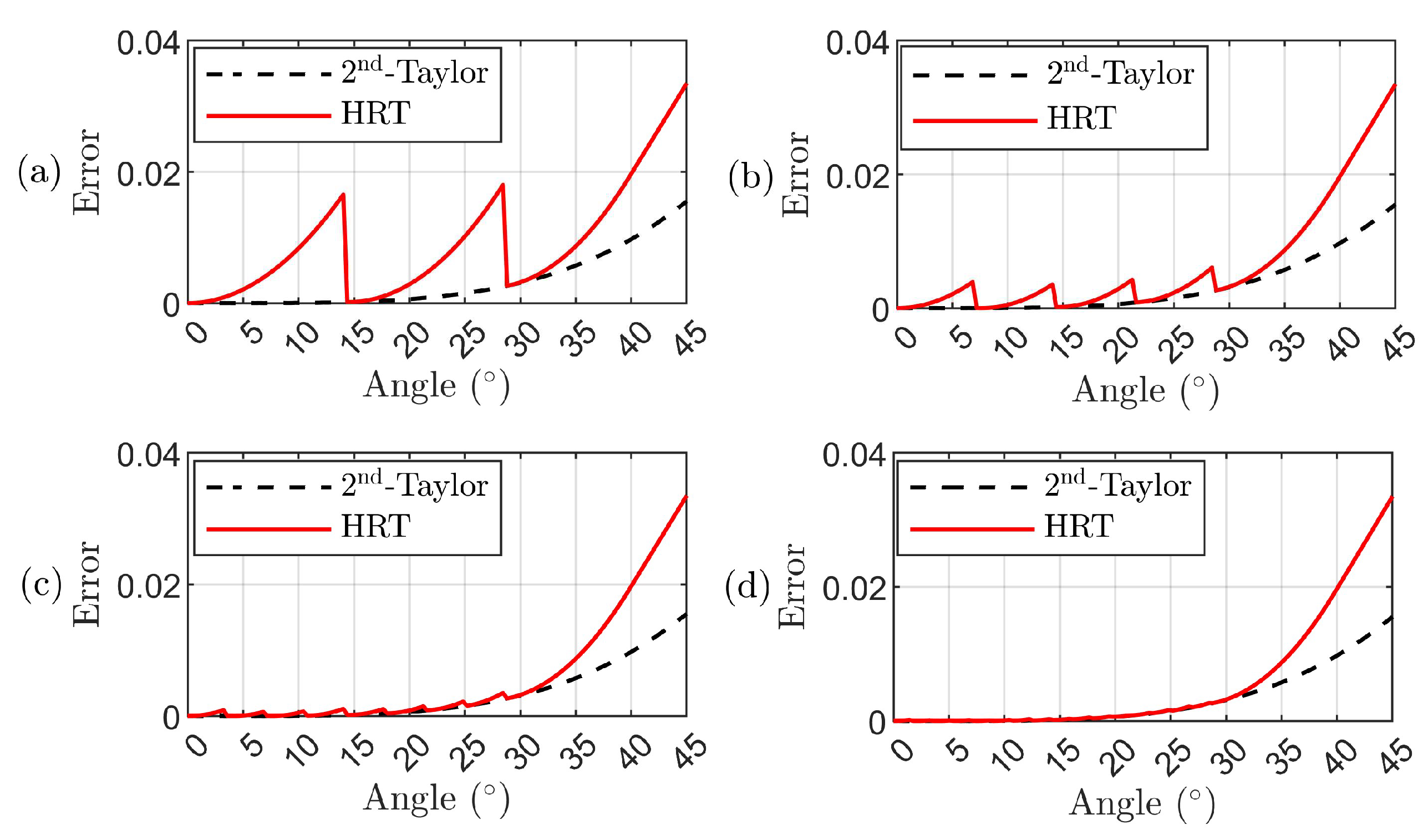

2.2. Principle of the Proposed HRT Technique

2.3. Implementation of Taylor-Based Reset Interpolation

3. Measurement Results and Analysis

3.1. Simulation Result

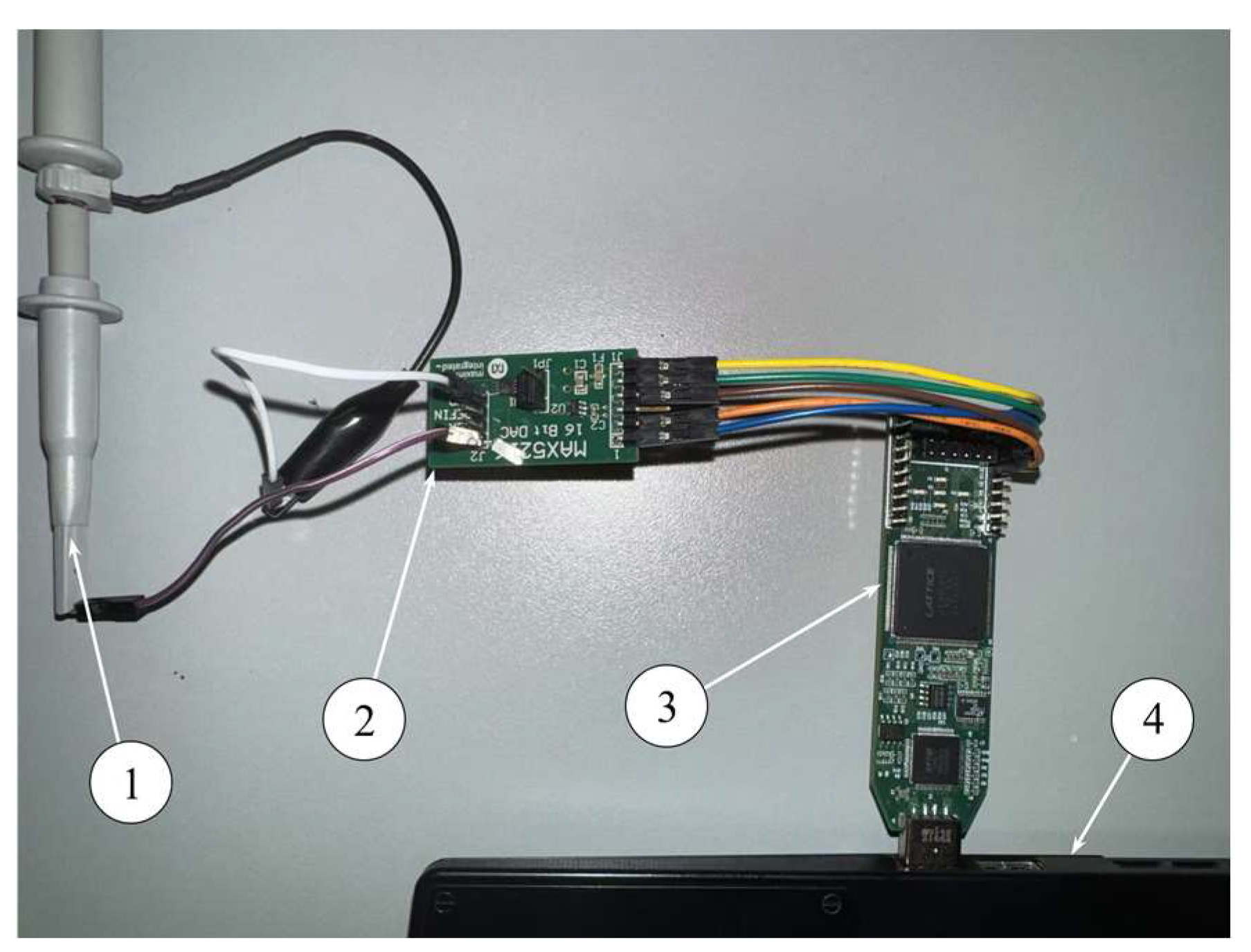

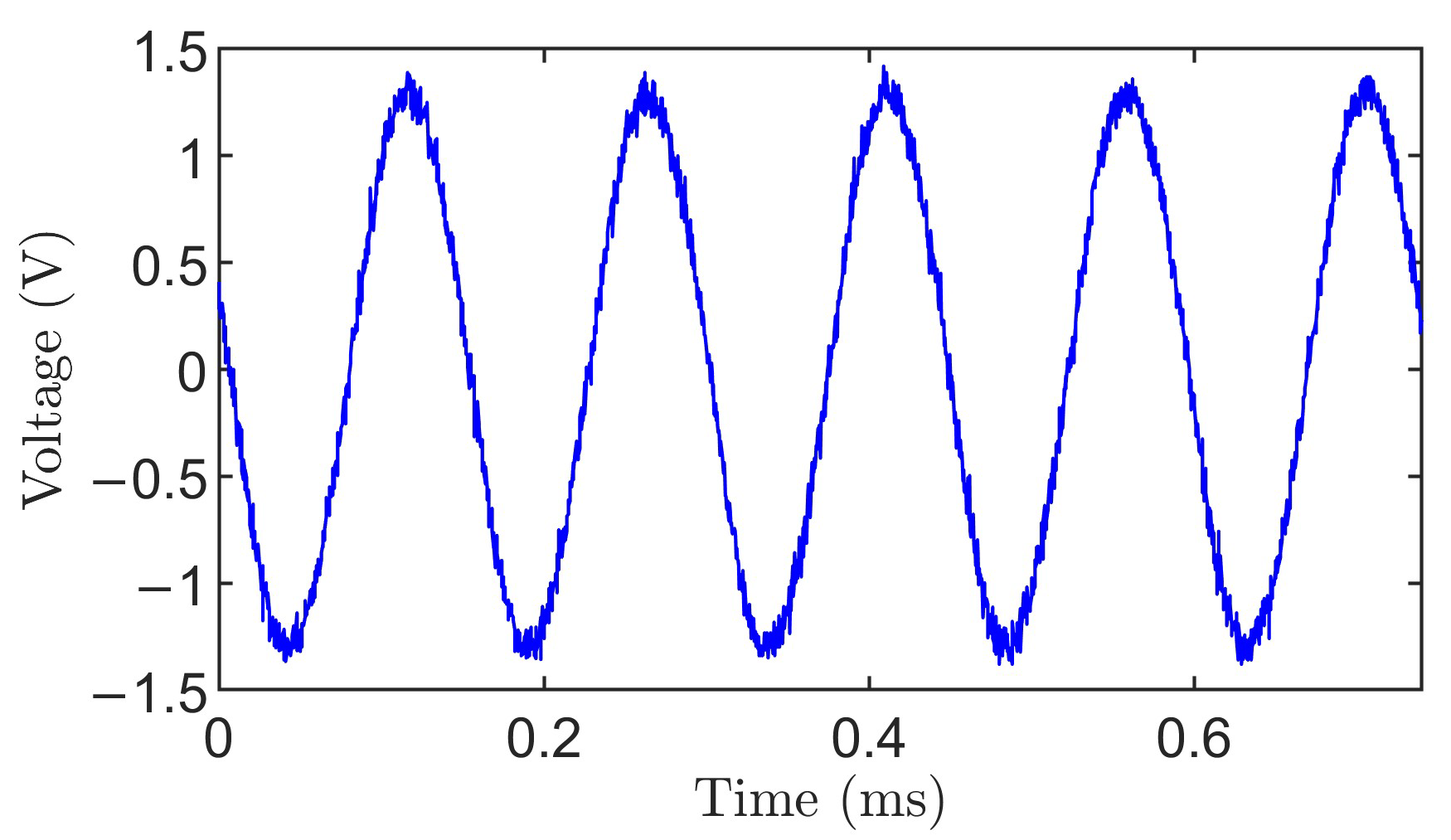

3.2. Experiment Result

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Tierney, J.; Rader, C.; Gold, B. A Digital Frequency Synthesizer. IEEE Trans. Audio Electroacoust. 1971, 19, 48–57. [Google Scholar] [CrossRef]

- Asfour, A.; Raoof, K.; Yonnet, J.P. Software Defined Radio (SDR) and Direct Digital Synthesizer (DDS) for NMR/MRI Instruments at Low-Field. Sensors 2013, 13, 16245–16262. [Google Scholar] [CrossRef] [PubMed]

- Villalba, J.; Zapata, E.; Antelo, E.; Bruguera, J. Radix-4 Vectoring CORDIC Algorithm and Architectures. J. Signal Process. Syst. 1998, 19, 127–147. [Google Scholar] [CrossRef]

- Meher, P.K.; Park, S.Y. Design of Cascaded CORDIC Based on Precise Analysis of Critical Path. Electronics 2019, 8, 382. [Google Scholar] [CrossRef]

- Jeng, S.S.; Lin, H.C.; Lin, C.H. A Novel ROM Compression Architecture for DDFS Utilizing the Parabolic Approximation of Equi-Section Division. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2012, 59, 2603–2612. [Google Scholar] [CrossRef] [PubMed]

- Catunda, S.Y.C.; Saavedra, O.R. Constraints definition and evaluation of piecewise polynomial approximation functions for embedded systems. In Proceedings of the IEEE Instrumentation and Measurement Technology Conference, Anchorage, AK, USA, 7 August 2002; Volume 2, pp. 1103–1108. [Google Scholar]

- Nochetto, R.H.; Otárola, E.; Salgado, A.J. Piecewise polynomial interpolation in Muckenhoupt weighted Sobolev spaces and applications. Numer. Math. 2016, 132, 85–130. [Google Scholar] [CrossRef]

- Changela, A.; Kumar, Y. A Modified Radix-16 CORDIC Algorithm-Based Direct Digital Frequency Synthesizer. In Proceedings of the 2022 5th International Conference on Contemporary Computing and Informatics (IC3I), Uttar Pradesh, India, 14–16 December 2022; pp. 1–6. [Google Scholar]

- Palomäki, K.I.; Nurmi, J. Taylor Series Interpolation-Based Direct Digital Frequency Synthesizer with High Memory Compression Ratio. Sensors 2025, 25, 2403. [Google Scholar] [CrossRef] [PubMed]

- Lan, J.; Gui, L.; She, W.; Hu, J.; Lang, L.; Huang, Q. Spurious Suppression and Frequency Accuracy Enhancement in Direct Digital Frequency Synthesis: Analysis, Simulation, and Experiment. IEEE Trans. Instrum. Meas. 2025, 74, 6504012. [Google Scholar] [CrossRef]

- Wang, C.C.; Sulistiyanto, N.; Shih, H.Y.; Lin, Y.C.; Wang, W. Power-Effective ROM-Less DDFS Design Approach with High SFDR Performance. J. Signal Process. Syst. 2020, 92, 213–224. [Google Scholar] [CrossRef]

- Lu, Z.; Zhang, B.; Peng, X.; Liu, H.; Li, X.; Peng, Y.; Xiao, Y.; Zhang, W.; Tang, H. A New Artificial Neural Network-Based Calibration Mechanism for ADCs: A Time-Interleaved ADC Case Study. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2024, 32, 1184–1195. [Google Scholar] [CrossRef]

- Pomponio, M.; Hati, A.; Nelson, C. Ultra-Low Phase Noise Frequency Division With Array of Direct Digital Synthesizers. IEEE Trans. Instrum. Meas. 2024, 73, 5501310. [Google Scholar] [CrossRef] [PubMed]

- Xing, X.; Wang, W. A New Recursive Trigonometric Technique for FPGA-Design Implementation. Sensors 2023, 23, 3683. [Google Scholar] [CrossRef] [PubMed]

- Xing, X.; Melek, W.; Wang, W. A Recursive Trigonometric Technique for Direct Digital Frequency Synthesizer Implementation. Electronics 2024, 13, 4762. [Google Scholar] [CrossRef]

- Yu, F.; He, S.; Yao, W.; Cai, S.; Xu, Q. Bursting Firings in Memristive Hopfield Neural Network with Image Encryption and Hardware Implementation. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2025, 1, 1. [Google Scholar] [CrossRef]

- Vankka, J. Methods of Mapping from Phase to Sine Amplitude in Direct Digital Synthesis. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 1997, 44, 526–534. [Google Scholar] [CrossRef] [PubMed]

- Korn, G.A.; Korn, T.M. Functions and Limits. Differential and Integral Calculus. In Mathematical Handbook for Scientists and Engineers, 2nd ed.; Dover Publications: New York, NY, USA, 2000; Chapter 4; pp. 132–134. [Google Scholar]

- Stegun, I.; Abramowitz, M. Handbook of Mathematical Functions with Formulas, Graphs, and Mathematical Tables; National Bureau of Standards, Applied Mathematics Series 55; Abramowitz, M., Stegun, I.A., Eds.; Dover Publications: New York, NY, USA, 1972. [Google Scholar]

- Huang, Z.; Zhang, S.; Wang, W. An Efficient Method of Parallel Multiplication on a Single DSP Slice for Embedded FPGAs. IEEE Access 2019, 7, 99947–99956. [Google Scholar] [CrossRef]

- Alink, M.S.O.; Kokkelcor, A.B.J.; Klumperink, E.A.M.; Rovers, K.C.; Smit, G.J.M.; Nauta, B. Spurious-Free Dynamic Range of a Uniform Quantizer. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1006–1010. [Google Scholar]

- Guo, X.; Wu, D.; Zhou, L.; Liu, H.; Wu, J.; Liu, X. High speed high resolution direct digital frequency synthesizer with non-linear DAC coarse quantization and ROM-based piecewise linear interpolation. Analog Integr. Circ. Sig. Process. 2017, 90, 263–272. [Google Scholar] [CrossRef]

- Maxim Integrated. 14-/16-Bit, Low-Power, Buffered Output, Rail-to-Rail DACs with SPI Interface. MAX5216 Datasheet, September 2010; Revised June 2013. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/MAX5214-MAX5216.pdf (accessed on 26 July 2025).

- Man, P.; Ding, C.; Ren, W.; Xu, G. A Nonlinear Fingerprint-Level Radar Simulation Modeling Method for Specific Emitter Identification. Electronics 2021, 10, 1030. [Google Scholar] [CrossRef]

- Zhou, K.; Xu, Q.; Zhang, T. Optimized Design of Direct Digital Frequency Synthesizer Based on Hermite Interpolation. Sensors 2024, 24, 6285. [Google Scholar] [CrossRef]

| Algorithm | 16-Bit Cosine SFDR (dBc) |

|---|---|

| CORDIC | −42.45 |

| Piecewise | −53.02 |

| 2nd Taylor | −82.02 |

| RT | −52.31 |

| HRT | −86.09 |

| Algorithm | SFDR (dBc) | SNR (dB) |

|---|---|---|

| CORDIC | −51.27 | 46.02 |

| Piecewise | −52.18 | 46.98 |

| 2nd Taylor | −57.73 | 51.03 |

| RT | −52.71 | 47.13 |

| HRT | −58.86 | 52.74 |

| Frequency (kHz) | Iterations | SFDR (dBc) | SNR (dB) |

|---|---|---|---|

| 13.46 | 32 | −53.92 | 50.02 |

| 6.73 | 64 | −58.86 | 52.72 |

| 3.37 | 128 | −58.51 | 53.91 |

| 1.68 | 256 | −57.80 | 55.07 |

| Algorithm | LUTs | Flip Flops | ROMs |

|---|---|---|---|

| CORDIC | 907 | 555 | 0 |

| Piecewise | 131 | 73 | 1 |

| 2nd Taylor | 620 | 72 | 0 |

| RT | 764 | 204 | 0 |

| HRT | 827 | 82 | 0 |

| Algorithm | LUTs | Flip Flops | Aritect. Blocks |

|---|---|---|---|

| CORDIC [8] | 1176 | N/A | 135 |

| Piecewise [22] | 131 | 73 | 27 |

| Hermite [25] | 1392 | N/A | 46 multipliers |

| Taylor seg [9] | 328 | 224 | 3 DSPs |

| RT [15] | 1009 | 1142 | 1 multiplier |

| Proposed | 827 | 82 | 2 multipliers |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xing, X.; Melek, W.; Wang, W. A Hybrid Recursive Trigonometric Technique for Direct Digital Frequency Synthesizer. Electronics 2025, 14, 3027. https://doi.org/10.3390/electronics14153027

Xing X, Melek W, Wang W. A Hybrid Recursive Trigonometric Technique for Direct Digital Frequency Synthesizer. Electronics. 2025; 14(15):3027. https://doi.org/10.3390/electronics14153027

Chicago/Turabian StyleXing, Xing, William Melek, and Wilson Wang. 2025. "A Hybrid Recursive Trigonometric Technique for Direct Digital Frequency Synthesizer" Electronics 14, no. 15: 3027. https://doi.org/10.3390/electronics14153027

APA StyleXing, X., Melek, W., & Wang, W. (2025). A Hybrid Recursive Trigonometric Technique for Direct Digital Frequency Synthesizer. Electronics, 14(15), 3027. https://doi.org/10.3390/electronics14153027