Optimizing FPGA Resource Allocation in SDR Remote Laboratories via Partial Reconfiguration

Abstract

1. Introduction

2. Background

2.1. SDR Remote Laboratories

2.2. Partial Reconfiguration

2.2.1. Multitasking in Remote Laboratory

2.2.2. Reconfiguration Time in SDRs

2.2.3. Resource Utilization and Power Consumption in SDRs

3. Materials and Methods

3.1. Knowledge Gap and Significance of the Research

3.2. Design Flow

- Designing the FPGA Program—The program is developed either by writing scripts in a Hardware Description Language (HDL) or by utilizing Intellectual Property (IP) blocks, which are interconnected within a block design. Running the program on a physical FPGA requires both source files, which define the logic and circuitry, and constraint files, which specify pin assignments and other essential details needed for synthesis and implementation.

- Synthesis—The project is synthesized to detect syntax errors and generate a “netlist,” which describes the necessary circuit components and their connections.

- Implementation—The synthesized design is mapped onto the selected FPGA device according to the specified constraints.

- Bitstream Generation—The implemented design is converted into a .bit file, which serves as the final FPGA configuration file.

- Programming—The generated bitstream is loaded onto the FPGA, configuring the device to execute the intended design.

3.3. Feasibility Assessment of Partial Reconfiguration on Zynq-Based Development Board

- Dynamic PR Configuration: A single reconfigurable partition (RP) housing one arithmetic module at a time, swapped via Vivado’s Hardware Manager.

- Static Configuration: All four modules implemented concurrently, with operation selection via switch inputs.

- PR-Enabled Design: A single partial reconfigurable region (PRR) housed either a low-pass or high-pass FIR filter, dynamically swapped via PR.

- Static Design: Both filters implemented concurrently, with mode switching controlled by register writes to emulate SDR-style software reconfiguration.

- Reduced PR Module Count: Only two filter modules (vs. four arithmetic units) limited resource-sharing opportunities.

- Homogeneous Resource Demands: Both filters required similar LUT/FF counts, diminishing PR’s advantage over static multiplexing.

3.4. Selecting an SDR

- Zynq-7000 SoC Compatibility: Zynq-7010/7020 devices to align with academic SDR affordability while ensuring sufficient logic resources.

- Cost and Accessibility: Sub-$750 pricing with broad adoption for technical support scalability.

- Open-Source Ecosystem: Community-driven documentation and firmware to enable customization.

- Remote-Ready Connectivity: Ethernet for configuration and microSD for firmware recovery.

3.5. Integration of the Red Pitaya SDR into the RHL-RELIA SDR Remote Laboratory Framework

- Centralized Server: Hosts a web-based remote laboratory interface for user interaction, a scheduler for fair hardware access, and a data exchanger that processes configuration files (e.g., bitstreams, filter coefficients) and streams processed signals back to users.

- Edge Devices: Raspberry Pi units deployed as reconfigurable intermediaries, tasked with programming SDRs and retrieving I/O data via low-latency GPIO interfaces.

- Physical Layer: SDR platforms (e.g., Red Pitaya, ADALM-PLUTO) housed in Faraday cages to minimize RF interference, colocated at the University of Washington’s RHL facility.

3.5.1. Enclosure Design for Multi-SDR RF Isolation

- 4 Raspberry Pi units for device control;

- 4 SDRs across 2 partitioned Faraday cages;

- Centralized power management;

- Ceiling-mounted cameras with a view through the cages’ semi-transparent mesh tops.

3.5.2. PR Architecture Design for Zynq-Based SDRs

3.6. Feasibility Assessment of Partial Reconfiguration on SDRs

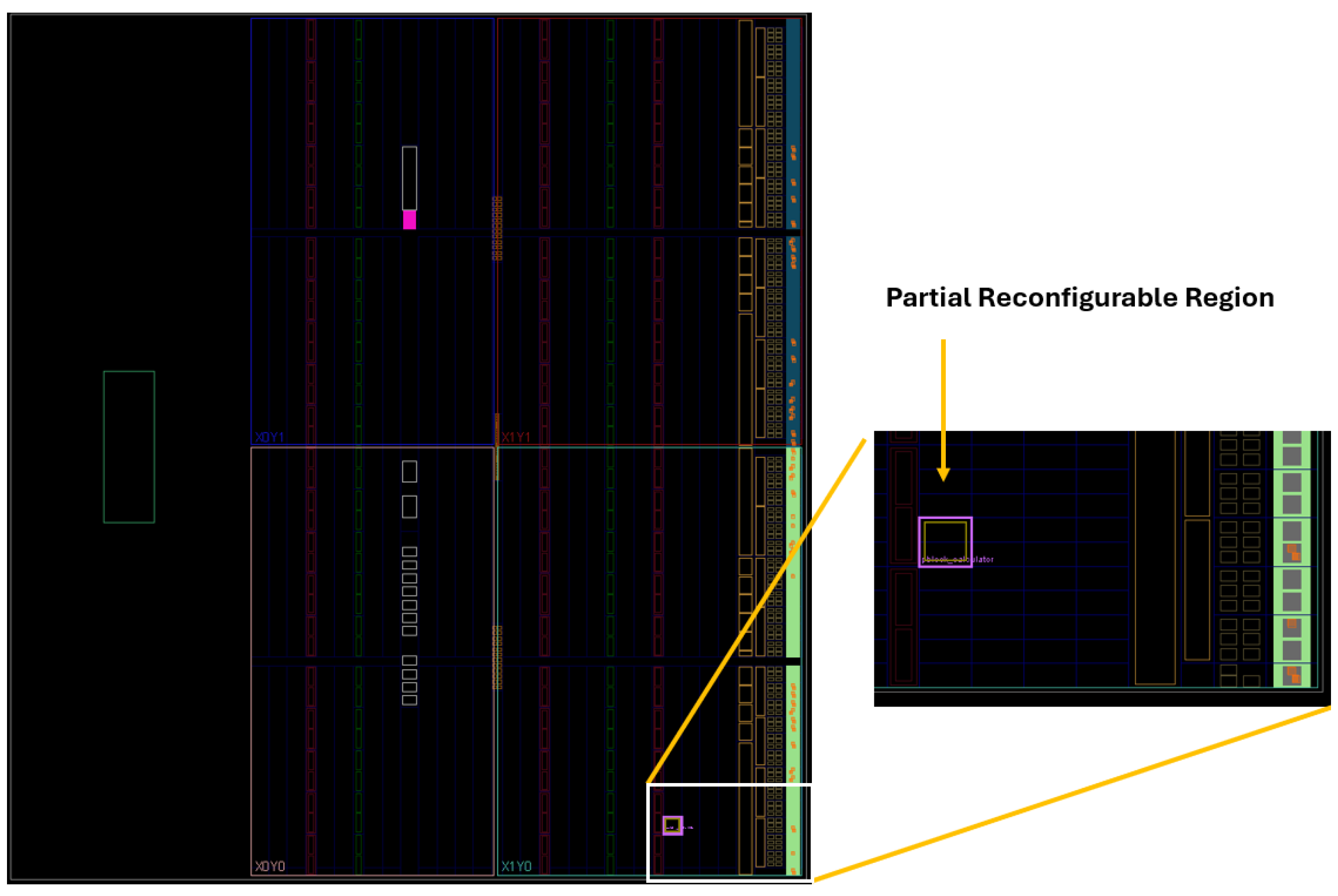

3.6.1. Case Study 1: GPIO-Driven Calculator with Partial Reconfiguration

3.6.2. Case Study 2: 1-PRR Scaling Program with Partial Reconfiguration

3.6.3. Case Study 3: 2-PRR Scaling and Filtering Program with Partial Reconfiguration

4. Results

4.1. Case Study 1: GPIO-Driven Calculator with Partial Reconfiguration Result

4.2. Case Study 2: 1-PRR Scaling Program with Partial Reconfiguration Result

4.3. Case Study 3: 2-PRR Scaling and Filtering Program with Partial Reconfiguration Result

5. Discussion

5.1. Interpretation in Context of SDR Education

5.2. Broader Implications for Industry and Research

5.3. Limitations

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Blossom, E. GNU Radio: Tools for Exploring the Radio Frequency Spectrum. Linux J. 2004, 122, 4. [Google Scholar]

- Tato, A. Software Defined Radio: A Brief Introduction. Proceedings 2018, 2, 1196. [Google Scholar] [CrossRef]

- Pini, A. Learn the Fundamentals of Software-Defined Radio. 2020. Available online: https://www.digikey.com/en/articles/learn-the-fundamentals-of-software-defined-radio (accessed on 28 March 2024).

- Collins, T.; Getz, R.; Pu, D.; Wyglinski, A. Software-Defined Radio for Engineers. 2018. Available online: https://www.analog.com/en/resources/technical-books/software-defined-radio-for-engineers.html (accessed on 16 July 2025).

- Hussein, R.; Guo, M.; Amarante, P.; Rodriguez Gil, L.; Orduña, P. Digital Twinning and Remote Engineering for Immersive Embedded Systems Education. In Proceedings of the Frontiers in Education (FIE) Conference, College Station, TX, USA, 18–21 October 2023; IEEE: Piscataway, NJ, USA, 2023. [Google Scholar]

- Grout, I. Supporting access to STEM subjects in higher education for students with disabilities using remote laboratories. In Proceedings of the 2015 12th International Conference on Remote Engineering and Virtual Instrumentation (REV), Bangkok, Thailand, 25–27 February 2015; pp. 7–13. [Google Scholar] [CrossRef]

- Love, T. Addressing Safety and Liability in STEM Education: A Review of Important Legal Issues and Case Law 1. Technol. Stud. 2013, 39, 28–41. [Google Scholar] [CrossRef]

- Wei, C. Research on university laboratory management and maintenance framework based on computer aided technology. Microprocess. Microsyst. 2020, 103617. [Google Scholar] [CrossRef]

- Gomes, L.; Bogosyan, S. Current Trends in Remote Laboratories. Ind. Electron. IEEE Trans. 2010, 56, 4744–4756. [Google Scholar] [CrossRef]

- Hussein, R.; Maloney, R.C.; Rodriguez-Gil, L.; Beroz, J.A.; Orduna, P. RHL-BEADLE: Bringing Equitable Access to Digital Logic Design in Engineering Education. In Proceedings of the 2023 ASEE Annual Conference & Exposition, Baltimore, MD, USA, 25–28 June 2023. [Google Scholar]

- May, D.; Morkos, B.; Jackson, A.; Hunsu, N.J.; Ingalls, A.; Beyette, F. Rapid transition of traditionally hands-on labs to online instruction in engineering courses. Eur. J. Eng. Educ. 2023, 48, 842–860. [Google Scholar] [CrossRef]

- Guidote, A.; Bareo, R.; Enriquez, E.; Duldulao, D.J.; Chua, M.; Lea, C.; Botona, M.; Moli, M.; Vilela, J.D. Redesigning an organic laboratory course for remote learning: Incorporating Lab@Home Kits and other techniques for teaching Organic Chemistry online. KIMIKA 2023, 34, 21–35. [Google Scholar] [CrossRef]

- Castaño, F.; López, E.; Jaramillo, J.; Navarro, V.; Osorio, J. Deploying an IoT-based remote physics lab platform to enhance experimental physics education in remote regions. Phys. Educ. 2024, 59, 065017. [Google Scholar] [CrossRef]

- Laouina, Z.; Ouchaouka, L.; Mordane, S.; Moussetad, M.; Radid, M. Development of a Remote Experiment for Practical Work in Physics at the University: The Case of Elastic Pendulum; Springer: Cham, Switzerland, 2024; pp. 749–758. [Google Scholar] [CrossRef]

- Schnieder, M.; Williams, S.; Ghosh, S. Comparison of In-Person and Virtual Labs/Tutorials for Engineering Students Using Blended Learning Principles. Educ. Sci. 2022, 12, 153. [Google Scholar] [CrossRef]

- Schnieder, M.; Ghosh, S.; Williams, S. Using Gamification and Flipped Classroom for Remote/Virtual Labs for Engineering Students. 2021. Available online: https://figshare.com/articles/conference_contribution/Using_gamification_and_flipped_classroom_for_remote_virtual_labs_for_engineering_students/19188251?file=34091900 (accessed on 16 July 2025).

- Hussein, R.; Wilson, D. Remote Versus In-hand Hardware Laboratory in Digital Circuits Courses. In Proceedings of the 2021 ASEE Virtual Annual Conference Content Access, Virtual Conference, 26–29 July 2021; Available online: https://peer.asee.org/37662 (accessed on 14 March 2024).

- Product Advantages. Available online: https://www.xilinx.com/products/silicon-devices/soc/zynq7000.html (accessed on 2 April 2024).

- AMD Zynq 7000 SoCs Product Table. Available online: https://www.amd.com/en/products/adaptive-socs-and-fpgas/soc/zynq-7000.html#product-table (accessed on 25 March 2024).

- Partial Reconfiguration in the ISE Design Suite. Available online: https://www.xilinx.com/products/design-tools/partial-reconfiguration.html (accessed on 27 March 2024).

- Liu, S.; Pittman, R.N.; Forin, A.; Gaudiot, J.L. On energy efficiency of reconfigurable systems with run-time partial reconfiguration. In Proceedings of the ASAP 2010–21st IEEE International Conference on Application-Specific Systems, Architectures and Processors, Rennes, France, 7–9 July 2010; pp. 265–272. [Google Scholar] [CrossRef]

- Xu, Z.; Hei, X.; Qu, D. Process Data Acquirement and Analysis for the Online Experiment in Principles of Communications. In Proceedings of the 2022 IEEE International Conference on Teaching, Assessment and Learning for Engineering (TALE), Hung Hom, Hong Kong, 4–7 December 2022; pp. 657–660. [Google Scholar] [CrossRef]

- Xu, Z.; Chen, W.; Hei, X.; Wang, X. Design and Evaluation of SDR-based Labs for Learning Principles of Communications. In Proceedings of the 2018 IEEE International Conference on Teaching, Assessment, and Learning for Engineering (TALE), Wollongong, NSW, Australia, 4–7 December 2018; pp. 1049–1052. [Google Scholar] [CrossRef]

- Șorecău, M.; Șorecău, E.; Sârbu, A.; Bechet, P. Real-Time Statistical Measurement of Wideband Signals Based on Software Defined Radio Technology. Electronics 2023, 12, 2920. [Google Scholar] [CrossRef]

- Nguyen, M.; Tamburo, R.; Narasimhan, S.; Hoe, J. Quantifying the Benefits of Dynamic Partial Reconfiguration for Embedded Vision Applications. In Proceedings of the 2019 29th International Conference on Field Programmable Logic and Applications (FPL), Barcelona, Spain, 8–12 September 2019; Volume 9, pp. 129–135. [Google Scholar] [CrossRef]

- Yamakura, M.; Hironaka, K.; Azegami, K.; Musha, K.; Amano, H. The Evaluation of Partial Reconfiguration for a Multi-board FPGA System FiCSW. In Proceedings of the HEART 2019: The 10th International Symposium on Highly-Efficient Accelerators and Reconfigurable Technologies, Nagasaki, Japan, 6–7 June 2019; Volume 6, pp. 1–4. [Google Scholar] [CrossRef]

- Sadek, A.; Nassar, A.; Ismail, Y. Towards the Implementation of Multiband Multistandard Software Defined Radio using Dynamic Partial Reconfiguration. Int. J. Commun. Syst. 2017, 30, e3342. [Google Scholar] [CrossRef]

- Hassan, A.; Ahmed, R.; Fahmy, H.; Hussien, A. Performance evaluation of dynamic partial reconfiguration techniques for software defined radio implementation on FPGA. In Proceedings of the 2015 IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Cairo, Egypt, 6–9 December 2015; Volume 12, pp. 183–186. [Google Scholar] [CrossRef]

- Kamaleldin, A.; Mohamed Mahmoud, A.; Nagy, A.; Gamal, Y.; Shalash, A.; Ismail, Y. Design guidelines for the high-speed dynamic partial reconfiguration based software defined radio implementations on Xilinx Zynq FPGA. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; Volume 5, pp. 1–4. [Google Scholar] [CrossRef]

- Kumar, K. FPGA implementation of PSK modems using partial re-configuration for SDR and CR applications. In Proceedings of the 2012 Annual IEEE India Conference (INDICON), Kochi, India, 7–9 December 2012; pp. 205–209. [Google Scholar] [CrossRef]

- Machidon, O.; Machidon, A.; Cotfas, P.; Cotfas, D. Leveraging Web Services and FPGA Dynamic Partial Reconfiguration in a Virtual Hardware Design Lab. Int. J. Eng. Educ. 2017, 33, 865–876. [Google Scholar]

- Grassi, S.; Convers, A.; Dassatti, A. FPGA Partial Reconfiguration in Software Defined Radio Devices. In Proceedings of the GNU Radio Conference, Virtual Event, 14–18 September 2020; Volume 5. [Google Scholar]

- Hosny, S.; Elnader, E.; Gamal, M.; Hussien, A.; Khalil, A. A Software Defined Radio Transceiver Based on Dynamic Partial Reconfiguration. In Proceedings of the 2018 New Generation of CAS (NGCAS), Valletta, Malta, 20–23 November 2018; pp. 158–161. [Google Scholar] [CrossRef]

- Vivado Overview. Available online: https://www.xilinx.com/products/design-tools/vivado.html (accessed on 2 April 2024).

- Kizheppatt, V.; Fahmy, S. FPGA Dynamic and Partial Reconfiguration: A Survey of Architectures, Methods, and Applications. ACM Comput. Surv. 2018, 51, 1–39. [Google Scholar] [CrossRef]

- Bin Tariq, O.; Shan, J.; Floros, G.; Sotiriou, C.; Casu, M.; Lazarescu, M.; Lavagno, L. High-Level Annotation of Routing Congestion for Xilinx Vivado HLS Designs. IEEE Access 2021, 9, 54286–54297. [Google Scholar] [CrossRef]

- Blackboard. Available online: https://www.realdigital.org/hardware/blackboard (accessed on 26 February 2025).

- Remote Hub Lab. Available online: https://rhlab.ece.uw.edu (accessed on 26 February 2025).

- LabsLand. Available online: https://labsland.com (accessed on 26 February 2025).

- ADALM-PLUTO. Available online: https://www.analog.com/en/resources/evaluation-hardware-and-software/evaluation-boards-kits/adalm-pluto.html (accessed on 26 February 2025).

- Inonan, M.; Hussein, R. MELODY: A Platform-Agnostic Model for Building and Evaluating Remote Labs of Software-Defined Radio Technology. IEEE Access 2023, 11, 127550–127566. [Google Scholar] [CrossRef]

- USRP N210. Available online: https://www.ettus.com/all-products/un210-kit/ (accessed on 26 February 2025).

- Red Pitaya—Swiss Army Knife For Engineers. Available online: https://redpitaya.com/ (accessed on 26 February 2025).

- STEMlab 125-14. Available online: https://redpitaya.com/stemlab-125-14/ (accessed on 26 February 2025).

- SDRlab 122-16. Available online: https://redpitaya.com/sdrlab-122-16/ (accessed on 26 February 2025).

- Inonan, M.; Zhang, Z.; Amarante, P.; Orduña, P.; Hussein, R.; Arabshahi, P. RHLab Interoperable Software-Defined Radio (SDR) Remote Laboratory; Springer: Cham, Swizerland, 2024; pp. 145–156. [Google Scholar] [CrossRef]

- Padmanabha, A.; Nalli, P. Design of Software Defined Radio (Sdr) Waveforms For Portability and Interoperability. J. Aerosp. Sci. Technol. 2023, 200–206. [Google Scholar] [CrossRef]

- Zhang, Z.; Inoñan, M.; Orduña, P.; Hussein, R. RHLab: Towards Implementing a Partial Reconfigurable SDR Remote Lab. In Proceedings of the Smart Technologies for a Sustainable Future, Porto, Portugal, 3–4 October 2024; Auer, M.E., Langmann, R., May, D., Roos, K., Eds.; Springer: Cham, Swizerland, 2024; pp. 180–192. [Google Scholar]

- FPGA Lessons. Available online: https://redpitaya-knowledgebase.readthedocs.io/en/latest/learn_fpga/4_lessons/top.html (accessed on 12 March 2024).

| SDR Remote Lab | Huazhong University of Science and Technology | Technical University of Cluj-Napoca | RHL-RELIA |

|---|---|---|---|

| Number of SDR Models | 2 | 1 | 3 |

| Software Tool | MATLAB | GNU Radio | GNU Radio or HDL |

| Access Method | Web Browser | Virtual Machine | Web Brower |

| Partial Reconfiguration | No | No | Planned |

| STEMlab 125-14 | SDRlab 122-16 | |

|---|---|---|

| SoC | Z-7010 | Z-7020 |

| Connectivity | USB 2.0, 1 Gb Ethernet | |

| Number of RF Input Channels | 2 | |

| Number of RF Output Channels | 2 | |

| RF Input Bandwidth | DC—60 MHz | 300 kHz–550 MHz |

| RF Output Bandwidth | DC—60 MHz | 300 kHz–60 MHz |

| Input Sampling Rate (MS/s) | 125 | 122.88 |

| Output Sampling Rate (MS/s) | 125 | 122.88 |

| Input Resolution (bit) | 14 | 16 |

| Output Resolution (bit) | 14 | |

| Program | 8-Bit Calculator | 1-PRR Scaling | 2-PRR Scaling and Filtering |

|---|---|---|---|

| LUT | 6.9% | 3.8% | 4% |

| FF | 13.6% | 1.4% | 2% |

| DSP | Not Applicable | 14.3% | 14.3% |

| Total Power | 0.2% | 2.7% | 0% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Z.; Hussein, R. Optimizing FPGA Resource Allocation in SDR Remote Laboratories via Partial Reconfiguration. Electronics 2025, 14, 2908. https://doi.org/10.3390/electronics14142908

Zhang Z, Hussein R. Optimizing FPGA Resource Allocation in SDR Remote Laboratories via Partial Reconfiguration. Electronics. 2025; 14(14):2908. https://doi.org/10.3390/electronics14142908

Chicago/Turabian StyleZhang, Zhiyun, and Rania Hussein. 2025. "Optimizing FPGA Resource Allocation in SDR Remote Laboratories via Partial Reconfiguration" Electronics 14, no. 14: 2908. https://doi.org/10.3390/electronics14142908

APA StyleZhang, Z., & Hussein, R. (2025). Optimizing FPGA Resource Allocation in SDR Remote Laboratories via Partial Reconfiguration. Electronics, 14(14), 2908. https://doi.org/10.3390/electronics14142908