Short Circuit Withstand Time Screening of 1.2 kV Commercial SiC MOSFETs: A Non-Destructive Approach †

Abstract

1. Introduction

2. SCWT Variation

2.1. Device Under Test (DUT)

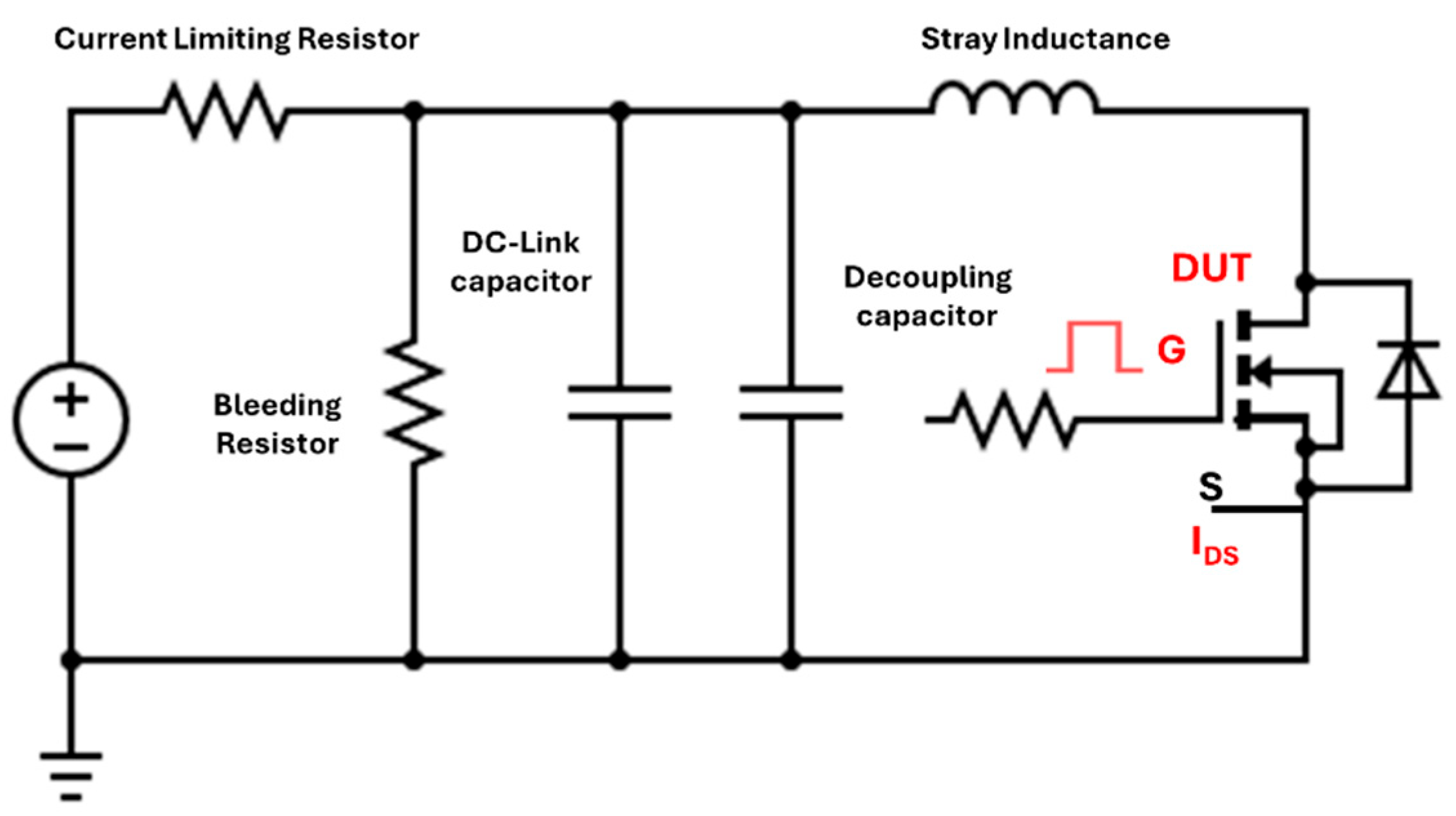

2.2. Short Circuit Test Evaluation

2.3. SCWT Variation in Commercial 1.2 kV SiC MOSFETs

3. SC Screening Methodology

3.1. Simulation Study of Planar-Gate 1.2 kV SiC MOSFETs

3.2. Proposed SC Screening Method

3.2.1. Determining Screening Pulse Width

3.2.2. Determining Screening Parameter and SCWT Correlation

3.2.3. Effect of Screening Process

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| MOSFET | metal oxide semiconductor field-effect transistor |

| DUT | device under test |

| SC | short circuit |

| SCWT | short circuit withstand time |

| DIBL | drain induced barrier lowering |

| CLM | channel length modulation |

References

- Liu, G.; Tuttle, B.R.; Dhar, S. Silicon carbide: A unique platform for metal-oxide-semiconductor physics. Appl. Phys. Rev. 2015, 2, 021307. [Google Scholar] [CrossRef]

- Wu, L.; Liang, J.; Zhang, M.; Liu, M.; Zhang, T.; Yang, G.; Song, X. An approach for extracting the SiC/SiO2 SiC MOSFET interface trap distribution and study during short circuit. Mater. Sci. Semicond. Process. 2023, 163, 107581. [Google Scholar] [CrossRef]

- Xing, D.; Hu, B.; Kang, M.; Zhang, Y.; Nayak, S.; Wang, J.; Agarwal, A.K. 1200-V SiC MOSFET Short-Circuit Ruggedness Evaluation and Methods to Improve Withstand Time. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 5059–5069. [Google Scholar] [CrossRef]

- Kimoto, T.; Cooper, J.A. In Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; John Wiley & Sons Singapore Pvt. Ltd.: Hoboken, NJ, USA, 2014. [Google Scholar]

- Hofstetter, P.; Maier, R.W.; Bakran, M.M. Influence of the Threshold Voltage Hysteresis and the Drain Induced Barrier Lowering on the Dynamic Transfer Characteristic of SiC Power MOSFETs. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 944–950. [Google Scholar]

- Tachiki, K.; Ono, T.; Kobayashi, T.; Kimoto, T. Short-Channel Effects in SiC MOSFETs Based on Analyses of Saturation Drain Current. IEEE Trans. Electron Devices 2021, 68, 1382–1384. [Google Scholar] [CrossRef]

- Sun, J.; Xu, H.; Wu, X.; Sheng, K. Comparison and analysis of short circuit capability of 1200V single-chip SiC MOSFET and Si IGBT. In Proceedings of the 2016 13th China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China (SSLChina: IFWS), Beijing, China, 15–18 November 2016; pp. 42–45. [Google Scholar]

- Castellazzi, A.; Funaki, T.; Kimoto, T.; Hikihara, T. Short-circuit tests on SiC power MOSFETs. In Proceedings of the 2013 IEEE 10th International Conference on Power Electronics and Drive Systems (PEDS), Kitakyushu, Japan, 22–25 April 2013. [Google Scholar]

- Wang, Z.; Shi, X.; Tolbert, L.M.; Wang, F.; Liang, Z.; Costinett, D.; Blalock, B.J. Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs. IEEE Trans. Power Electron. 2016, 31, 1555–1566. [Google Scholar] [CrossRef]

- Namai, M.; An, J.; Yano, H.; Iwamuro, N. Investigation of short-circuit failure mechanisms of SiC MOSFETs by varying DC bus voltage. Jpn. J. Appl. Phys. 2018, 57, 074102. [Google Scholar] [CrossRef]

- Wang, J.; Jiang, X. Review and analysis of SiC MOSFETs’ ruggedness and reliability. IET Power Electron. 2020, 13, 445–455. [Google Scholar] [CrossRef]

- Cui, R.; Xin, Z.; Liu, Q.; Kang, J.; Luo, H.; Zhang, L.; Loh, P.C. Review of Methodologies for Evaluating Short-Circuit Robustness and Reliability of SiC Power MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 4665–4679. [Google Scholar] [CrossRef]

- Yu, R.; Jahdi, S.; Alatise, O.; Ortiz-Gonzalez, J.; Munagala, S.P.; Simpson, N.; Mellor, P. Measurements and Review of Failure Mechanisms and Reliability Constraints of 4H-SiC Power MOSFETs Under Short Circuit Events. IEEE Trans. Device Mater. Reliab. 2023, 23, 544–563. [Google Scholar] [CrossRef]

- Yao, K.; Yano, H.; Tadano, H.; Iwamuro, N. Investigations of SiC MOSFET Short-Circuit Failure Mechanisms Using Electrical, Thermal, and Mechanical Stress Analyses. IEEE Trans. Electron Devices 2020, 67, 4328–4334. [Google Scholar] [CrossRef]

- Hain, S.; Meiler, M.; Denk, M. Evaluation of 800V Traction Inverter with SiC-MOSFET versus Si-IGBT Power Semiconductor Technology. In Proceedings of the PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 7–9 May 2019; pp. 1–6. [Google Scholar]

- Han, K.; Kanale, A.; Baliga, B.J.; Bhattacharya, S. Static, Dynamic, and Short-Circuit Performance of 1.2 kV 4H-SiC MOSFETs with Various Channel Lengths. In Proceedings of the 2019 IEEE 7th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Raleigh, NC, USA, 29–31 October 2019; pp. 47–52. [Google Scholar]

- Nayak, S.; Yu, S.; Maddi, H.L.R.; Jin, M.; Shi, L.; Ganguly, S.; Agarwal, A.K. Non-isothermal simulation of SiC DMOSFET short circuit capability. Jpn. J. Appl. Phys. 2022, 61, 061007. [Google Scholar] [CrossRef]

- Yu, H.; Bhattacharya, M.; Jin, M.; Shi, L.; Houshmand, S.; Shimbori, A.; White, M.H.; Agarwal, A.K. Artificial Neural Network-Based Screening Method for Short-Circuit Withstand Time in Packaged SiC MOSFETs to Enhance Device Consistency. IEEE Electron Device Lett. 2025, 46, 1179–1182. [Google Scholar] [CrossRef]

- Nguyen, T.-T.; Ahmed, A.; Thang, T.V.; Park, J.-H. Gate Oxide Reliability Issues of SiC MOSFETs Under Short-Circuit Operation. IEEE Trans. Power Electron. 2015, 30, 2445–2455. [Google Scholar] [CrossRef]

- Hatta, H.; Tominaga, T.; Hino, S.; Miura, N.; Tomohisa, S.; Yamakawa, S. Suppression of Short-Circuit Current with Embedded Source Resistance in SiC-MOSFET. Mater. Sci. Forum 2018, 924, 727–730. [Google Scholar] [CrossRef]

- Kanale, A.; Baliga, B.J. A New User-Configurable Method to Improve Short-Circuit Ruggedness of 1.2-kV SiC Power MOSFETs. IEEE Trans. Power Electron. 2021, 36, 2059–2067. [Google Scholar] [CrossRef]

- Wang, J.; Shen, Z.; Burgos, R.; Boroyevich, D. Design of a high-bandwidth Rogowski current sensor for gate-drive shortcircuit protection of 1.7 kV SiC MOSFET power modules. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 104–107. [Google Scholar]

- Baliga, B.J.; Kanale, A. Introduction. In The BaSIC Topology: A Revolutionary Power Device Control Strategy; Baliga, B.J., Kanale, A., Eds.; Springer Nature: Cham, Switzerland, 2025; pp. 1–5. [Google Scholar]

- Kim, D.; Sung, W. Improved Short-Circuit Ruggedness for 1.2kV 4H-SiC MOSFET Using a Deep P-Well Implemented by Channeling Implantation. IEEE Electron Device Lett. 2021, 42, 1822–1825. [Google Scholar] [CrossRef]

- Diaz Reigosa, P.; Schulz, N.; Minamisawa, R. Short-circuit robustness of retrograde channel doping 1.2 kV SiC MOSFETs. Microelectron. Reliab. 2021, 120, 114117. [Google Scholar] [CrossRef]

- Kono, H.; Asaba, S.; Ohashi, T.; Ogata, T.; Furukawa, M.; Sano, K.; Yamaguchi, M.; Suzuki, H. Improving the specific on-resistance and short-circuit ruggedness tradeoff of 1.2-kV-class SBD-embedded SiC MOSFETs through cell pitch reduction and internal resistance optimization. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 227–230. [Google Scholar]

- Zhang, M.; Li, H.; Yang, Z.; Zhao, S.; Wang, X.; Ding, L. Short Circuit Protection of Silicon Carbide MOSFETs: Challenges, Methods, and Prospects. IEEE Trans. Power Electron. 2024, 39, 13081–13095. [Google Scholar] [CrossRef]

- Jouha, W.; Oualkadi, A.E.; Dherbécourt, P.; Joubert, E.; Masmoudi, M. A new extraction method of SiC power MOSFET threshold voltage using a physical approach. In Proceedings of the 2017 International Conference on Electrical and Information Technologies (ICEIT), Rabat, Morocco, 15–18 November 2017; pp. 1–6. [Google Scholar]

- Bhattacharya, M.; Jin, M.; Qian, J.; Shi, L.; Houshmand, S.; Yu, H.; White, M.H.; Agarwal, A.K.; Shimbori, A.; Aman, A.; et al. A Non-destructive Short Circuit Withstand Time Screening Methodology for Commercially Available SiC Power MOSFET. In Proceedings of the 2024 IEEE 11th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Dayton, OH, USA, 4–6 November 2024; pp. 1–5. [Google Scholar]

- Synopsys, Inc. Sentaurus Device User Manual; Synopsys, Inc.: Sunnyvale, CA, USA, 2022. [Google Scholar]

- Ionita, C.; Nawaz, M.; Ilves, K.; Iannuzzo, F. Short-circuit ruggedness assessment of a 1.2 kV/180 A SiC MOSFET power module. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017. [Google Scholar]

- Nguyen, T.A.; Lefebvre, S.; Azzopardi, S.; Chaplier, G. Investigation on the junction temperature of planar power 4H-SiC MOSFET under short circuit operation. Microelectron. Reliab. 2022, 138, 114694. [Google Scholar] [CrossRef]

- Romano, G.; Riccio, M.; Maresca, L.; Breglio, G.; Irace, A.; Fayyaz, A.; Castellazzi, A. Influence of design parameters on the short-circuit ruggedness of SiC power MOSFETs. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 47–50. [Google Scholar]

- Kakarla, B. Short Circuit Behavior of SiC MOSFETs; ETH Zurich: Zurich, Switzerland, 2021. [Google Scholar]

- Meng, J.; Sun, P.; Cai, Y.; Zhang, H.; Zhao, Z.; Xin, Z. Influence of Short-Circuit Time on Short-Circuit Failure Modes of Planar Silicon Carbide MOSFETs. IEEE Trans. Device Mater. Reliab. 2024, 1. [Google Scholar] [CrossRef]

- Yu, S.; White, M.H.; Agarwal, A.K. Experimental determination of interface trap density and fixed positive oxide charge in commercial 4H-SiC power MOSFETs. IEEE Access 2021, 9, 149118–149124. [Google Scholar] [CrossRef]

| Vendor | Vendor D | Vendor F |

|---|---|---|

| Device type | Planar | Planar |

| Rated Voltage (kV) | 1.2 | 1.2 |

| Rated Current (A) | 20 | 7.6 |

| Typical Threshold Voltage (V) | 3.5 | 2.5 |

| Typical On Resistance (mΩ) | 189 | 350 |

| Number of Devices Tested | 30 | 23 |

| Parameter | Value | Unit |

|---|---|---|

| Tdrift | 10 | µm |

| NN−drift | 8 × 1015 | cm−3 |

| NP+ | 1 × 1019 | cm−3 |

| NP-well | 1 × 1018 | cm−3 |

| NN+ | 1 × 1019 | cm−3 |

| Nchannel | 2 × 1017 | cm−3 |

| NJFET | 1 × 1016 | cm−3 |

| NN+substrate | 2 × 1018 | cm−3 |

| Lch (avg.) | 0.5 | µm |

| ½ WJFET | 1.0 | µm |

| tox | 50 | nm |

| ½ Wcell | 4.5 | µm |

| Model | Parameter | Value | Unit |

|---|---|---|---|

| Lattice Heat Capacity | cv | 10 | J/(K-cm3) |

| cv_b | 1.75 × 10−3 | J/(K2-cm3) | |

| cv_c | 1 × 10−9 | J/(K3-cm3) | |

| cv_d | −6.6 × 10−4 | J/(K3-cm3) | |

| Thermal Conductivity | 1/kappa | 1 | K-cm/W |

| 1/kappa_b | 4.9662 × 10−4 | cm/W | |

| 1/kappa_c | 0.35 × 10−6 | cm/(W-K) |

| Vendor | Threshold Voltage (V) | On-Resistance (mΩ) | Gate Leakage Current (nA) | |||

|---|---|---|---|---|---|---|

| Pretest | Post- Screening | Pretest | Post- Screening | Pretest | Post- Screening | |

| D | 7.2 | 7.2 | 116.25 | 116.25 | 0.081 | 0.051 |

| F | 6.11 | 6.12 | 318.2 | 321.1 | 27.5 | 27.1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bhattacharya, M.; Yu, H.; Jin, M.; Houshmand, S.; Qian, J.; Shi, L.; White, M.H.; Shimbori, A.; Agarwal, A.K. Short Circuit Withstand Time Screening of 1.2 kV Commercial SiC MOSFETs: A Non-Destructive Approach. Electronics 2025, 14, 2786. https://doi.org/10.3390/electronics14142786

Bhattacharya M, Yu H, Jin M, Houshmand S, Qian J, Shi L, White MH, Shimbori A, Agarwal AK. Short Circuit Withstand Time Screening of 1.2 kV Commercial SiC MOSFETs: A Non-Destructive Approach. Electronics. 2025; 14(14):2786. https://doi.org/10.3390/electronics14142786

Chicago/Turabian StyleBhattacharya, Monikuntala, Hengyu Yu, Michael Jin, Shiva Houshmand, Jiashu Qian, Limeng Shi, Marvin H. White, Atsushi Shimbori, and Anant K. Agarwal. 2025. "Short Circuit Withstand Time Screening of 1.2 kV Commercial SiC MOSFETs: A Non-Destructive Approach" Electronics 14, no. 14: 2786. https://doi.org/10.3390/electronics14142786

APA StyleBhattacharya, M., Yu, H., Jin, M., Houshmand, S., Qian, J., Shi, L., White, M. H., Shimbori, A., & Agarwal, A. K. (2025). Short Circuit Withstand Time Screening of 1.2 kV Commercial SiC MOSFETs: A Non-Destructive Approach. Electronics, 14(14), 2786. https://doi.org/10.3390/electronics14142786