A Reflection-Based Ultra-Fast Measurement Method for the Continuous Characterization of Self-Heating for Advanced MOSFETs

Abstract

1. Introduction

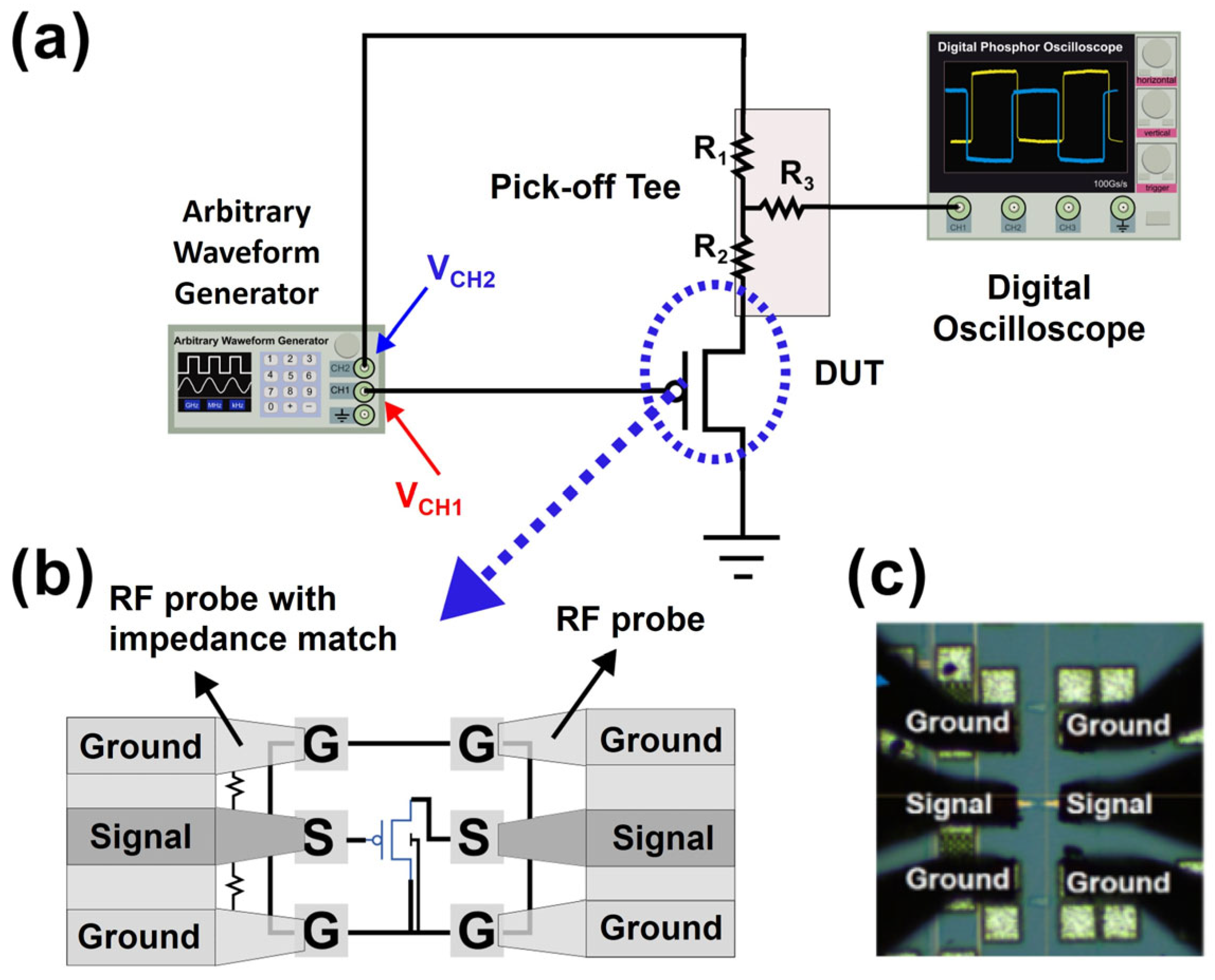

2. Experimental Setup

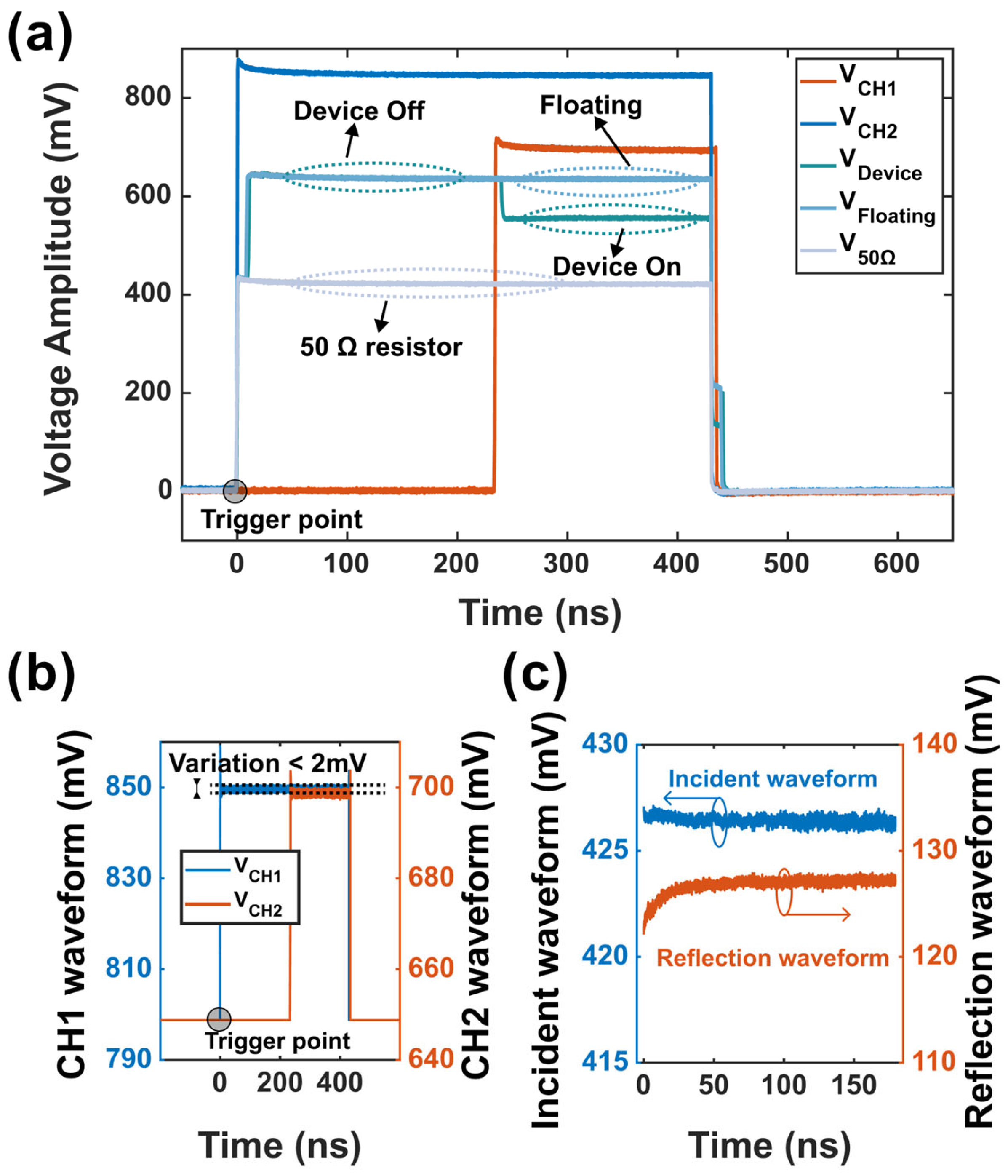

3. Reflection-Based Characterization Methodology

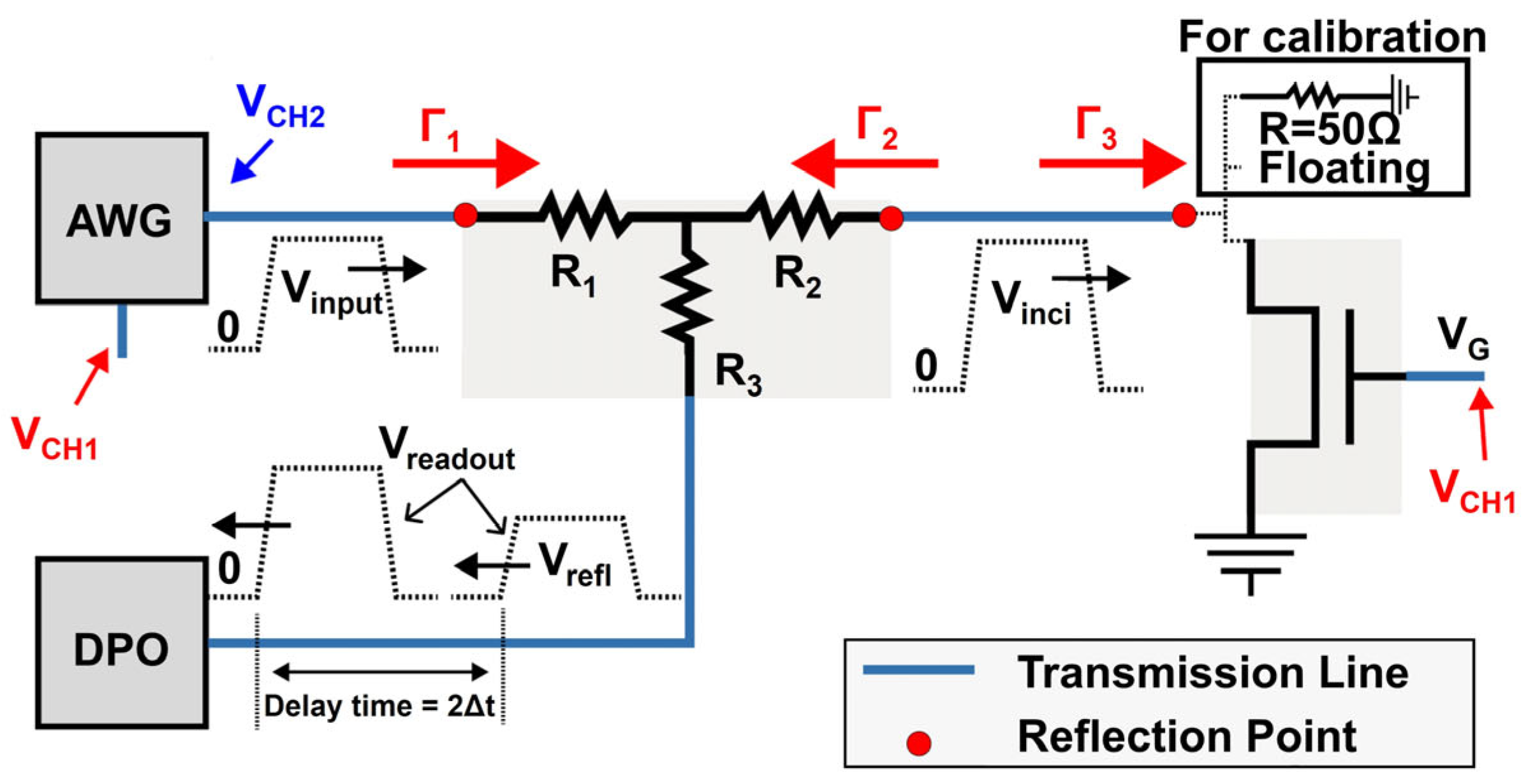

3.1. Reflection in the System

- Vinci: The incident voltage reaching the drain side of the DUT (unit: V).

- Vrefl: The reflected voltage due to impedance mismatch at the DUT (unit: V).

- Γ1, Γ2, Γ3: The reflection coefficients at different impedance discontinuities, with dimensionless ratios defined as , where Z is the local impedance and Z0 = 50 Ω is the characteristic impedance.

- RC: The channel resistance of the DUT, extracted from the waveform superposition (unit: Ω).

- VD: The instantaneous drain voltage at the device terminal (unit: V).

- ID: The drain current calculated using Ohm’s law (unit: A).

- R1, R2, R3: The resistors in the pick-off tee, each 16.7 Ω.

- RP1, RP2: Parallel equivalent resistances of the resistive divider branches (unit: Ω).

- Z0: The characteristic impedance of the transmission line, fixed to 50 Ω.

3.2. The Calibration of the Measurement System

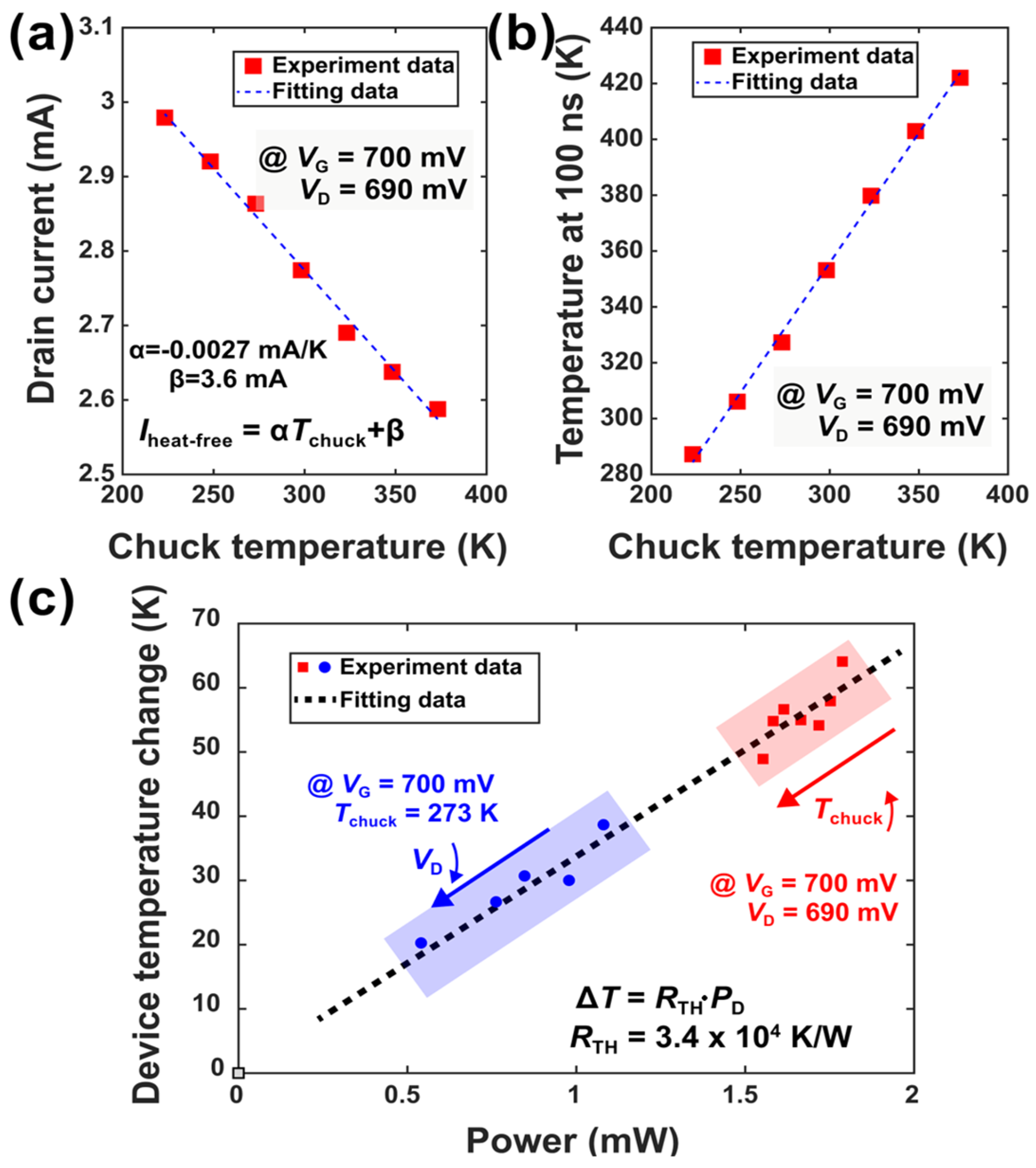

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Negro, V.; Pannone, L. Self-Heating and Gate Leakage Current in a Guarded MOSFET. Proc. IEEE 1972, 60, 342–343. [Google Scholar] [CrossRef]

- Lidback, C.A.C. Scanning infrared microscopy techniques for semiconductor thermal analysis. In Proceedings of the 17th International Reliability Physics Symposium (IRPS), San Diego, CA, USA, 24–26 April 1979; pp. 183–189. [Google Scholar] [CrossRef]

- Mautry, P.; Trager, J. Self-heating and temperature measurement in sub-mm-MOSFETs. In Proceedings of the 19th European Solid State Device Research Conference (ESSDERC ’89), Berlin, Germany, 11–14 September 1989; pp. 675–678. [Google Scholar] [CrossRef]

- Prasad, C. A review of self-heating effects in advanced CMOS technologies. IEEE Trans. Electron Devices 2019, 66, 4546–4555. [Google Scholar] [CrossRef]

- Qu, Y.; Lin, X.; Li, J.; Cheng, R.; Yu, X.; Zheng, Z.; Lu, J.; Chen, B.; Zhao, Y. Ultra-fast (<1 ns) electrical characterization of self-heating effect and its impact on hot carrier injection in 14 nm FinFETs. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 39.2.1–39.2.4. [Google Scholar] [CrossRef]

- Choudhury, N.; Sharma, U.; Zhou, H.; Southwick, R.G.; Wang, M.; Mahapatra, S. Analysis of BTI, SHE induced BTI and HCD under full VG/VD space in GAA nano-sheet N and P FETs. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April 2020–30 May 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Federspiel, X.; Torrente, G.; Arfaoui, W.; Cacho, F.; Huard, V. Temperature sense effect in HCI self-heating deconvolution: Application to 28 nm FDSOI. In Proceedings of the 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016; p. XT–09-1–XT-09-4. [Google Scholar] [CrossRef]

- Arfaoui, W.; Bossu, G.; Muhlhoff, A.; Lipp, D.; Manuwald, R.; Chen, T.; Nigam, T.; Siddabathula, M. A novel HCI reliability model for RF/mmWave applications in FDSOI technology. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April 2020–30 May 2020. [Google Scholar] [CrossRef]

- Zhao, Y.; Qu, Y. Impact of self-heating effect on transistor characterization and reliability issues in sub-10 nm technology nodes. IEEE J. Electron Devices Soc. 2019, 7, 829–836. [Google Scholar] [CrossRef]

- Jin, W.; Fung, S.; Liu, W.; Chan, P.; Hu, C. Self-heating characterization for SOI MOSFET based on AC output conductance. In Proceedings of the International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–8 December 1999; pp. 175–178. [Google Scholar] [CrossRef]

- Baylis, C.; Dunleavy, L.; Daniel, J. Direct measurement of thermal circuit parameters using pulsed IV and the normalized difference unit. In Proceedings of the 2004 IEEE MTT-S International Microwave Symposium Digest, Fort Worth, TX, USA, 6–11 June 2004; Volume 2, pp. 1233–1236. [Google Scholar] [CrossRef]

- Tyaginov, S.; Jech, M.; Franco, J.; Sharma, P.; Kaczer, B.; Grasser, T. Understanding and modeling the temperature behavior of hot-carrier degradation in SiON nMOSFETs. IEEE Electron Device Lett. 2016, 37, 84–87. [Google Scholar] [CrossRef]

- Alam, M.A.; Mahapatra, S. A comprehensive model of PMOS NBTI degradation. Microelectron. Reliab. 2005, 45, 71–81. [Google Scholar] [CrossRef]

- Wang, D.; Zhou, L.; Xue, Y.; Ren, P.; Sun, Z.; Wang, Z.; Wang, J.; Wu, B.; Ji, Z.; Wang, R.; et al. On the understanding of defects in short-term negative bias temperature instability (NBTI) for sub-20-nm DRAM technology. IEEE Electron Device Lett. 2023, 44, 1. [Google Scholar] [CrossRef]

- Jiang, H.; Liu, X.; Xu, N.; He, Y.; Du, G.; Zhang, X. Investigation of Self-Heating Effect on Hot Carrier Degradation in Multiple-Fin SOI FinFETs. IEEE Electron Device Lett. 2015, 36, 1258–1260. [Google Scholar] [CrossRef]

- Son, D.; Hong, K.; Shim, H.; Pae, S.; Shin, H. New insight into negative bias temperature instability degradation during self-heating in nanoscale bulk FinFETs. IEEE Electron Device Lett. 2019, 40, 1354–1357. [Google Scholar] [CrossRef]

- Liu, S.E.; Wang, J.S.; Lu, Y.R.; Huang, D.S.; Huang, C.F.; Hsieh, W.H.; Lee, J.H.; Tsai, Y.S.; Shih, J.R.; Lee, Y.H.; et al. Self-heating effect in FinFETs and its impact on devices reliability characterization. In Proceedings of the 2014 IEEE International Reliability Physics Symposium (IRPS), Waikoloa, HI, USA, 1–5 June 2014; pp. 4A.4.1–4A.4.4. [Google Scholar] [CrossRef]

- Prakash, O.; Dabhi, C.K.; Chauhan, Y.S.; Amrouch, H. Transistor self-heating: The rising challenge for semiconductor testing. In Proceedings of the 2021 IEEE 39th VLSI Test Symposium (VTS), San Diego, CA, USA, 25–28 April 2021; pp. 1–7. [Google Scholar] [CrossRef]

- Polonsky, S.; Jenkins, K. Time-resolved measurements of self-heating in SOI and strained-silicon MOSFETs using photon emission microscopy. IEEE Electron Device Lett. 2004, 25, 208–210. [Google Scholar] [CrossRef]

- Gotsmann, B.; Menges, F.; Karg, S.; Troncale, V.; Lantz, M.; Mensch, P.; Schmid, H.; Das Kanungo, P.; Drechsler, U.; Schmidt, V.; et al. Heat dissipation and thermometry in nanosystems: When interfaces dominate. In Proceedings of the 71st Device Research Conference (DRC), Notre Dame, IN, USA, 23–26 June 2013; pp. 231–232. [Google Scholar] [CrossRef]

- Sarua, A.; Ji, H.; Kuball, M.; Uren, M.; Martin, T.; Hilton, K.; Balmer, R. Integrated micro-Raman/infrared thermography probe for monitoring of self-heating in AlGaN/GaN transistor structures. IEEE Trans. Electron Devices 2006, 53, 2438–2447. [Google Scholar] [CrossRef]

- Paliwoda, P.; Chbili, Z.; Kerber, A.; Gondal, A.; Misra, D. Self-heating measurement methodologies and their assessment on bulk FinFET devices. In Proceedings of the 2017 IEEE International Integrated Reliability Workshop (IIRW), South Lake Tahoe, CA, USA, 8–12 October 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Jenkins, K.; Rim, K. Measurement of the effect of self-heating in strained-silicon MOSFETs. IEEE Electron Device Lett. 2002, 23, 360–362. [Google Scholar] [CrossRef]

- Makovejev, S.; Olsen, S.; Raskin, J.P. RF extraction of self-heating effects in FinFETs. IEEE Trans. Electron Devices 2011, 58, 3335–3341. [Google Scholar] [CrossRef]

- Scholten, A.; Smit, G.; Pijper, R.; Tiemeijer, L.; Tuinhout, H.; van der Steen, J.L.; Mercha, A.; Braccioli, M.; Klaassen, D. Experimental assessment of self-heating in SOI FinFETs. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Liu, W.; Ding, Y.; Zhao, L.; Zhao, Y. Nanosecond-scale and self-heating free characterization of advanced CMOS transistors utilizing wave reflection. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Makovejev, S.; Olsen, S.; Raskin, J.P. Time and frequency domain characterization of transistor self-heating. IEEE Trans. Electron Devices 2013, 60, 1844–1851. [Google Scholar] [CrossRef]

- Niu, S.; Yu, H.; Niu, S.; Jian, L. Power loss analysis and thermal assessment on wireless electric vehicle charging technology: The over-temperature risk of ground assembly needs attention. Appl. Energy 2020, 275, 115344. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, W.; Huang, G.; Ding, Y.; Yan, C.; Yu, X.; Zhao, L.; Zhao, Y. A Reflection-Based Ultra-Fast Measurement Method for the Continuous Characterization of Self-Heating for Advanced MOSFETs. Electronics 2025, 14, 2634. https://doi.org/10.3390/electronics14132634

Liu W, Huang G, Ding Y, Yan C, Yu X, Zhao L, Zhao Y. A Reflection-Based Ultra-Fast Measurement Method for the Continuous Characterization of Self-Heating for Advanced MOSFETs. Electronics. 2025; 14(13):2634. https://doi.org/10.3390/electronics14132634

Chicago/Turabian StyleLiu, Wei, Guoqixin Huang, Yaru Ding, Chu Yan, Xinwei Yu, Liang Zhao, and Yi Zhao. 2025. "A Reflection-Based Ultra-Fast Measurement Method for the Continuous Characterization of Self-Heating for Advanced MOSFETs" Electronics 14, no. 13: 2634. https://doi.org/10.3390/electronics14132634

APA StyleLiu, W., Huang, G., Ding, Y., Yan, C., Yu, X., Zhao, L., & Zhao, Y. (2025). A Reflection-Based Ultra-Fast Measurement Method for the Continuous Characterization of Self-Heating for Advanced MOSFETs. Electronics, 14(13), 2634. https://doi.org/10.3390/electronics14132634