Novel Series-Parallel Phase-Shifted Full-Bridge Converters with Auxiliary LC Networks to Achieve Wide Lagging-Leg ZVS Range

Abstract

1. Introduction

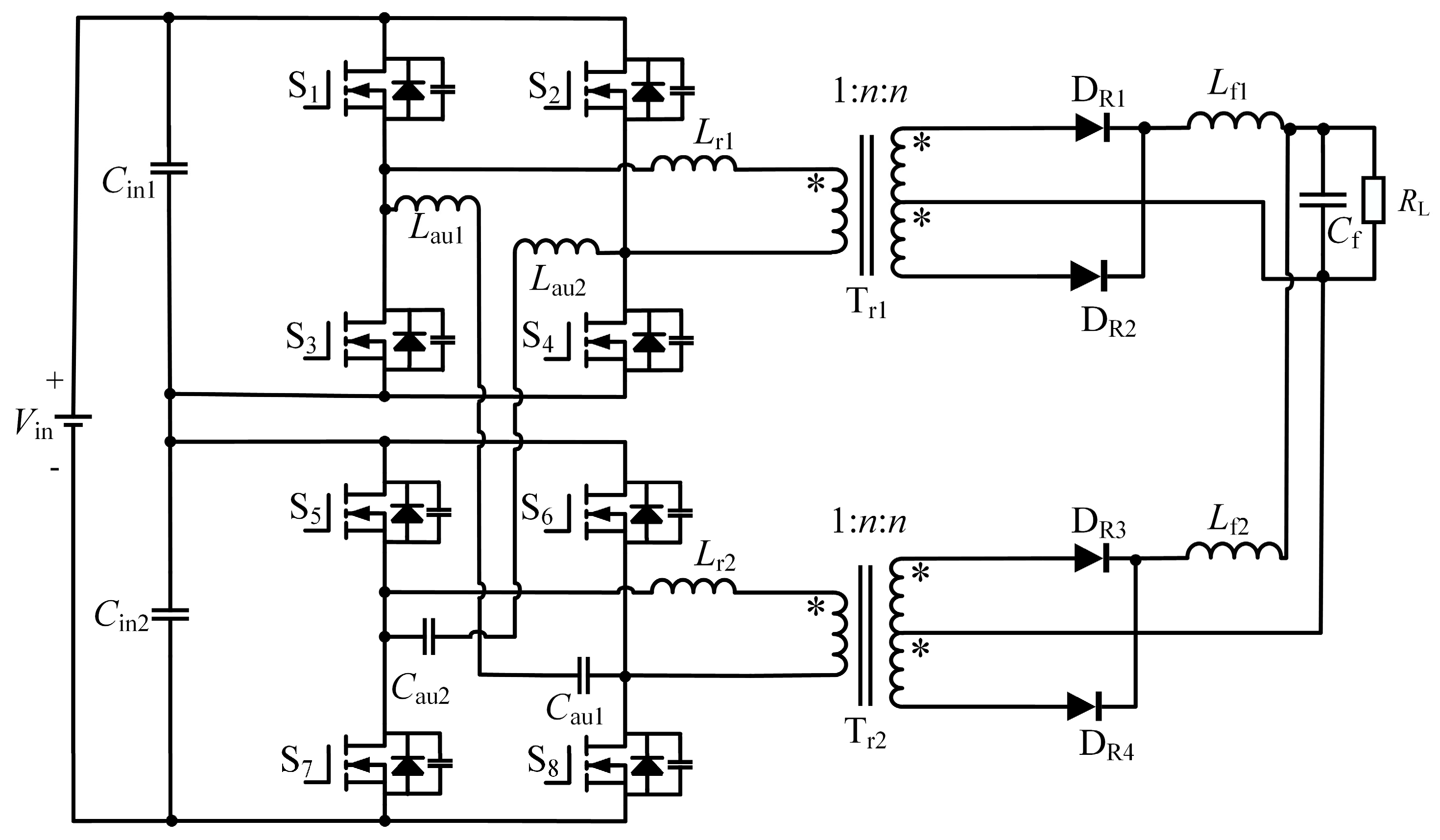

2. Working Principle of ZVS Series-Parallel PSFB Converter

- The module works in a steady state;

- Switching tubes S1-S8 and diodes DR1-DR8 are ideal devices;

- Switch tubes S1-S8 parasitic capacitance C1 = C2 = --- = C8 = Cr;

- Transformer Tr1, Tr2, inductors Lr1, Lr2, Lf1, Lf2, Lau and capacitors Cin, Cf1, Cf2, Cau are ideal devices, and Lr1 = Lr2, Lf1 = Lf2, and Cf1 = Cf2.

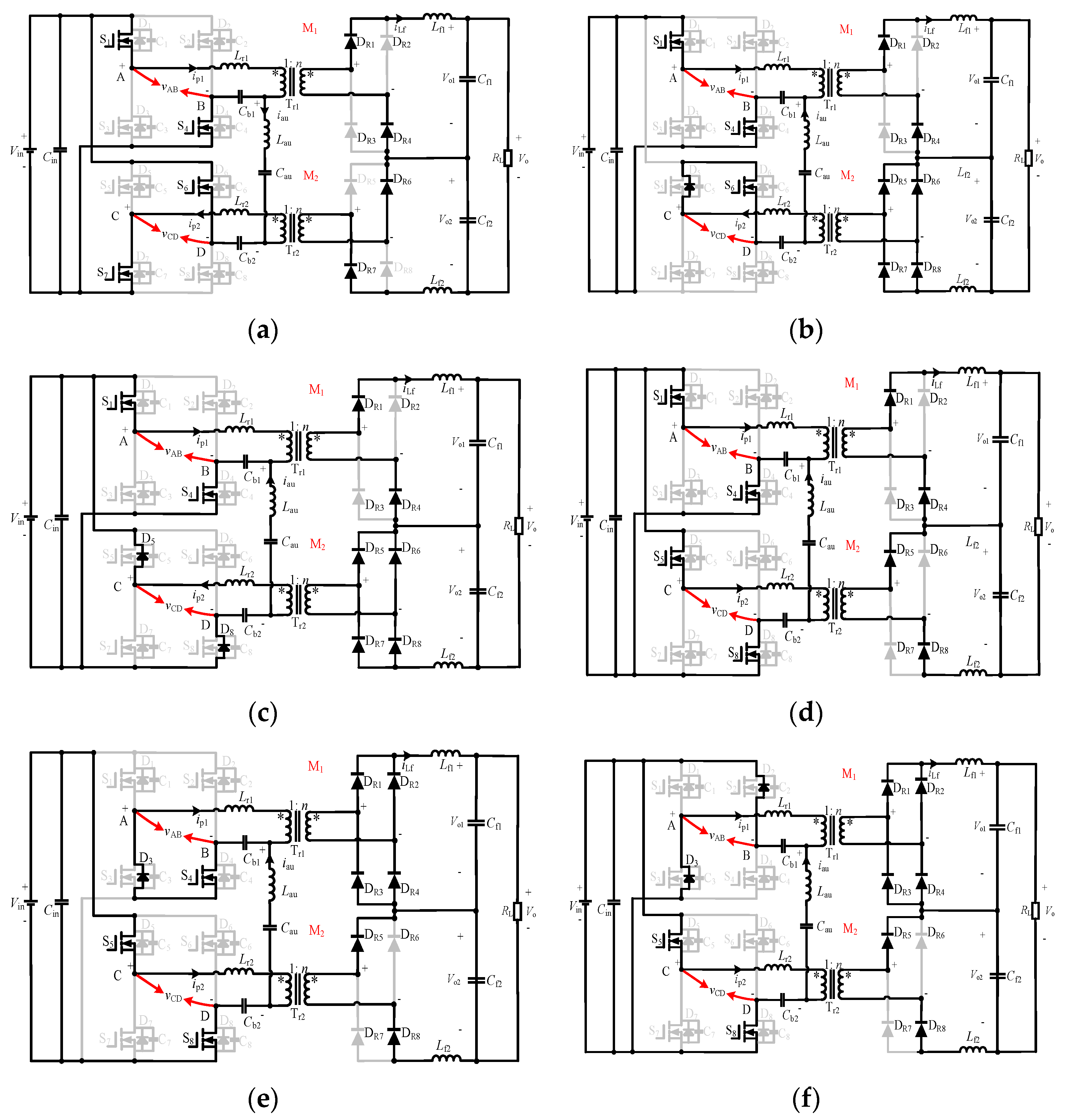

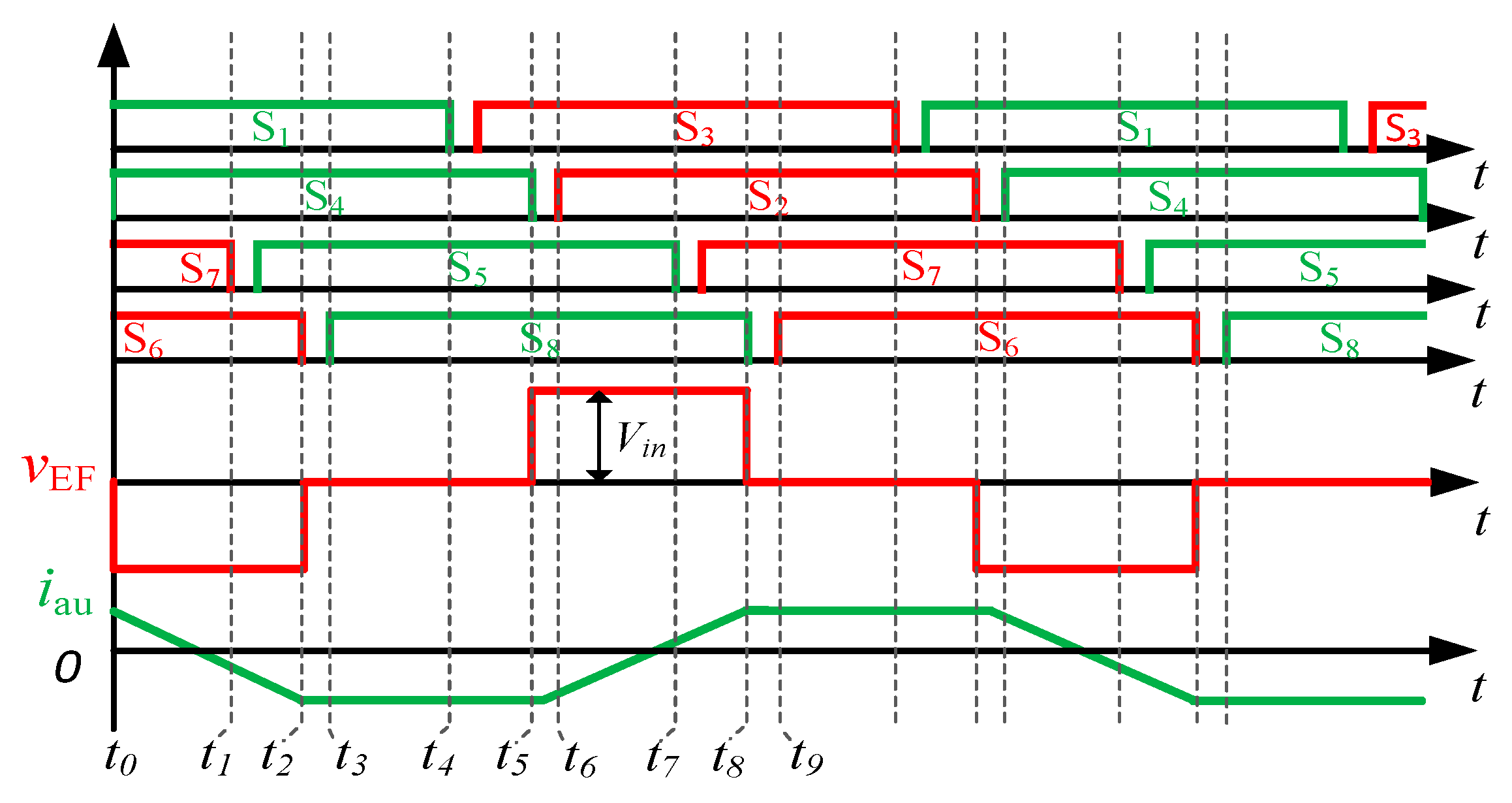

- a.

- Mode 0 [t0-t1]:

- b.

- Mode 1 [t1-t2]:

- c.

- Mode 2 [t2-t3]:

- d.

- Mode 3 [t3-t4]:

- e.

- Mode 4 [t4-t5]:

- f.

- Mode 5 [t5-t6]:

3. Series-Parallel PSFB Converter ZVS Condition and N-Bridge Extension

3.1. Series-Parallel PSFB Converter ZVS Condition

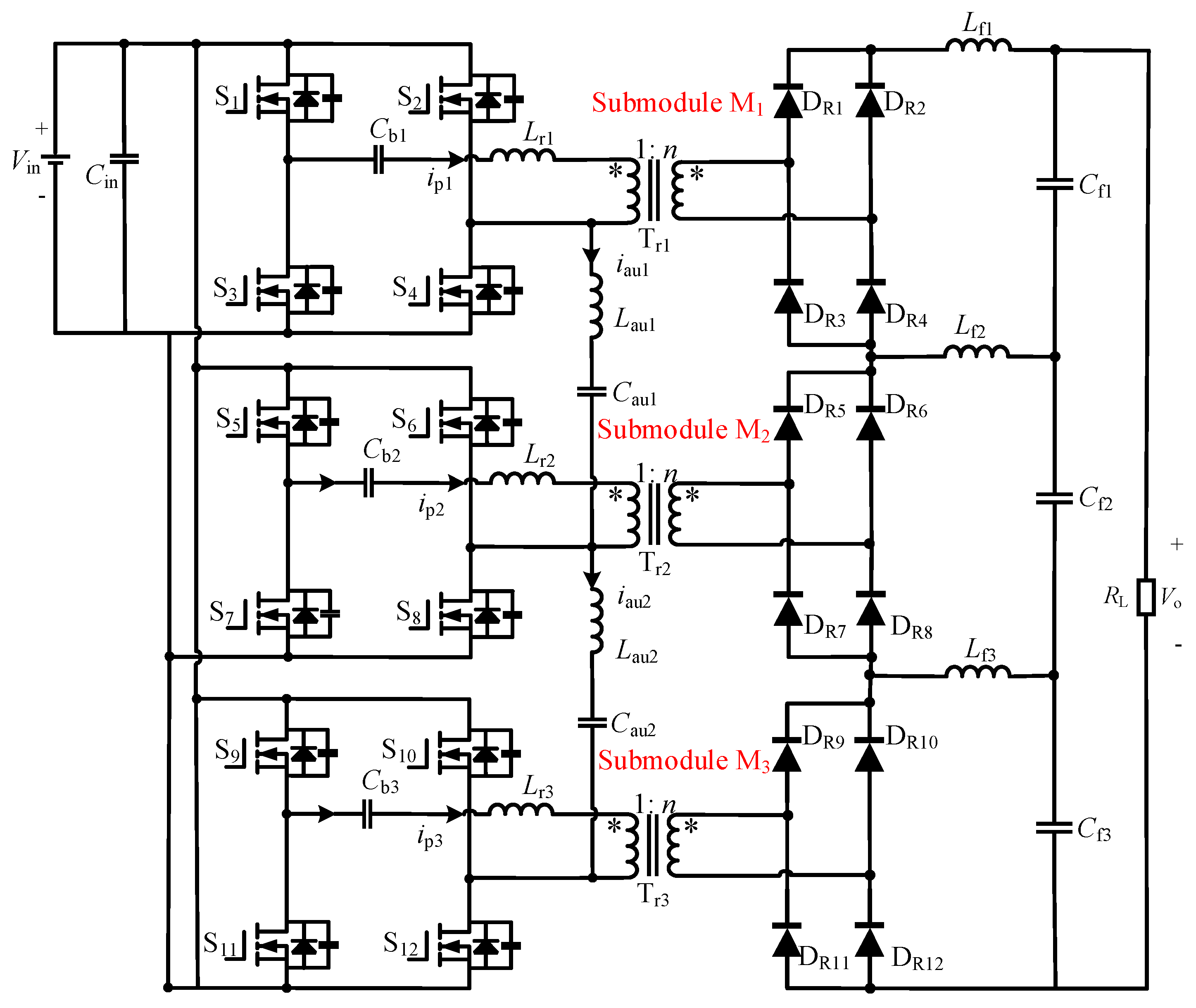

3.2. Implementation of Lagging-Leg ZVS for N-Bridge ZVS Series-Parallel PSFB Converter

4. Simulation Results and Discussion

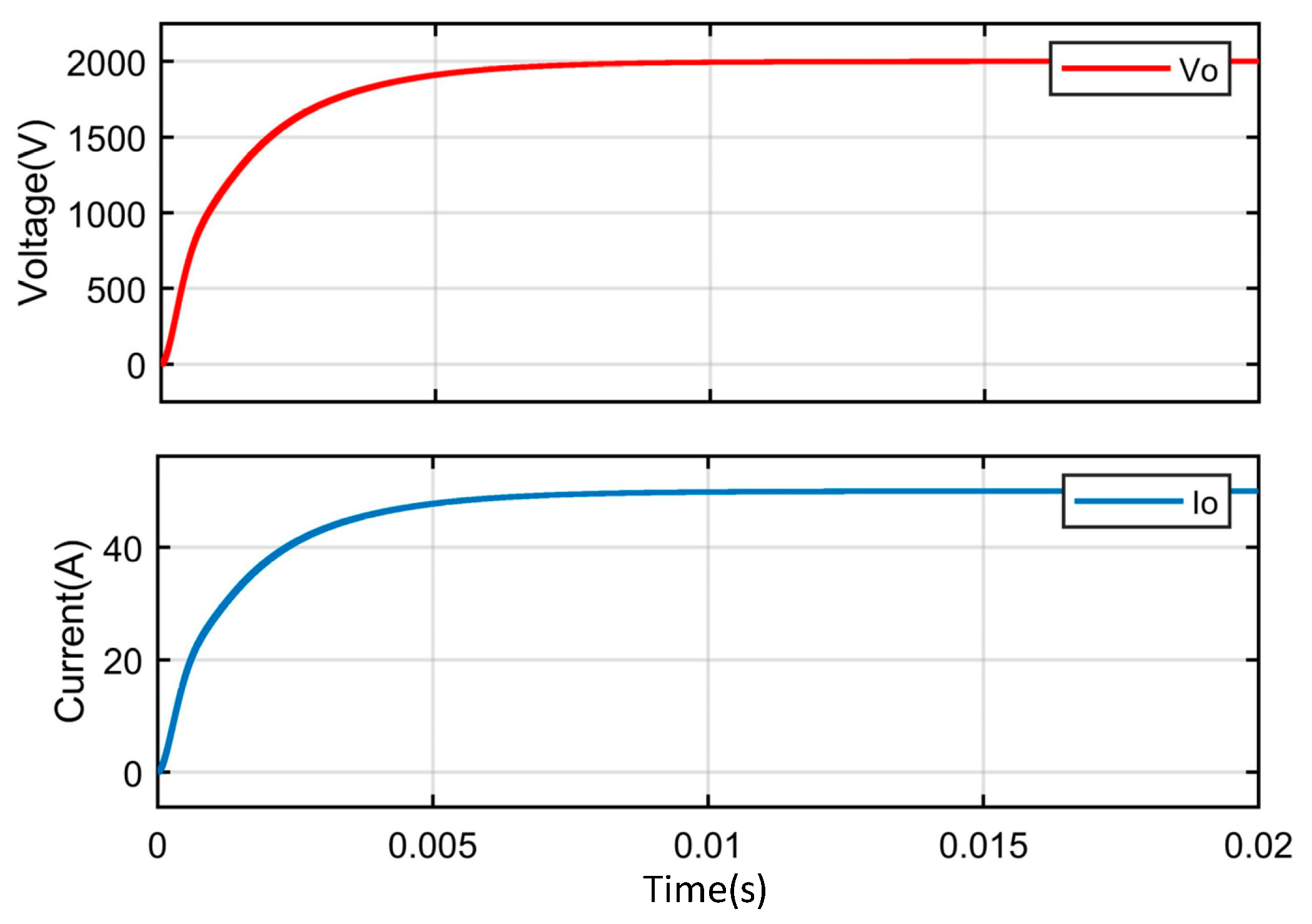

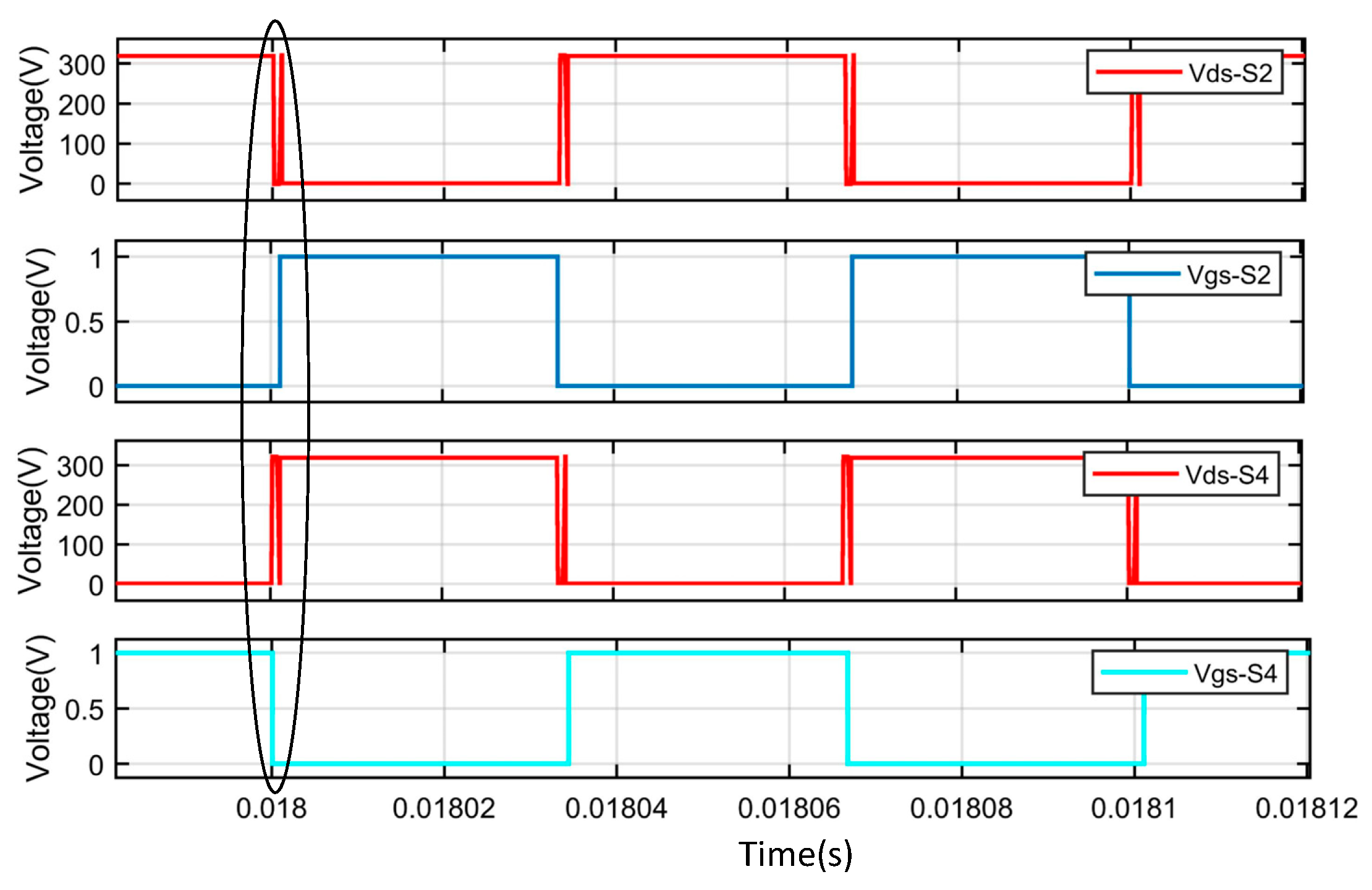

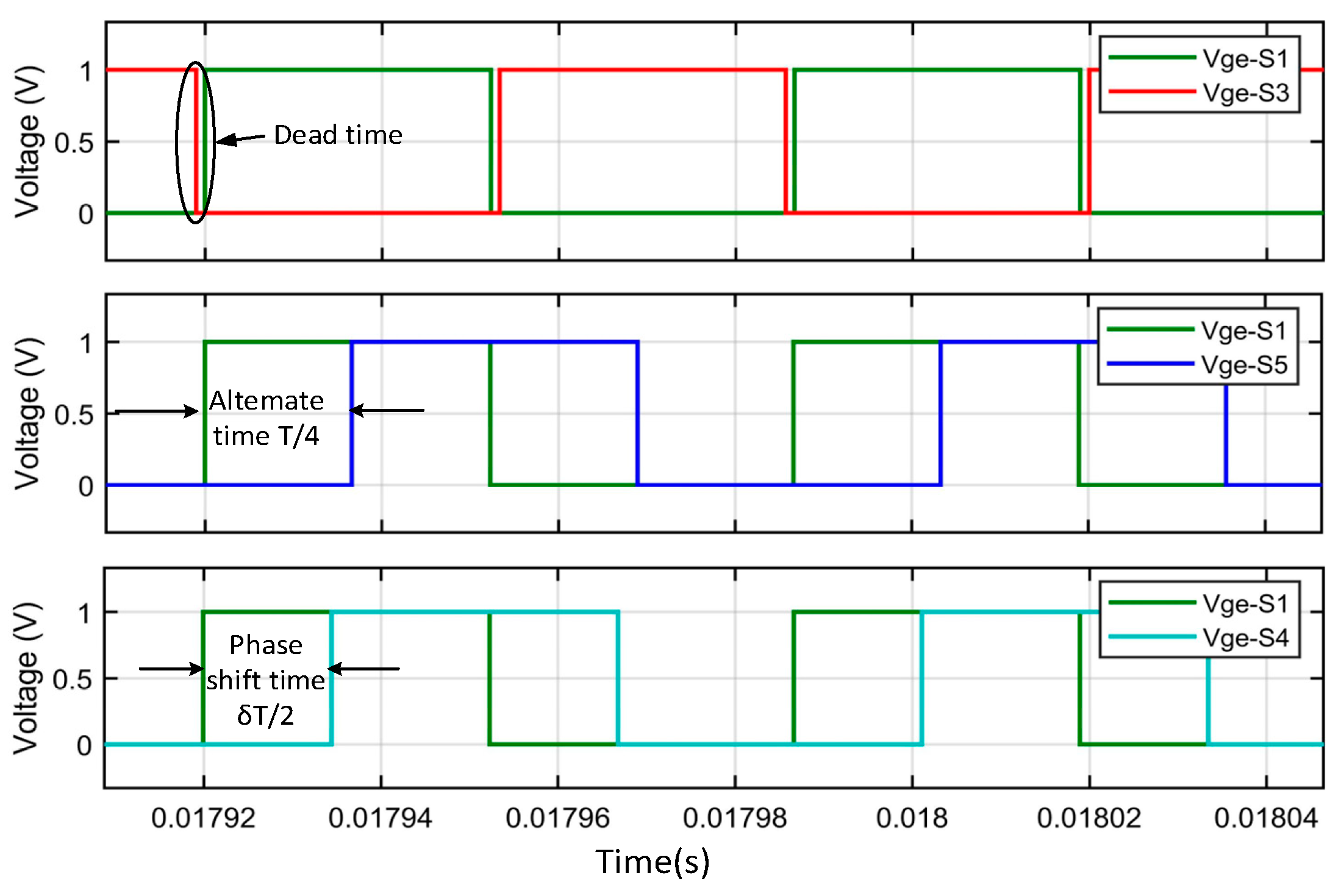

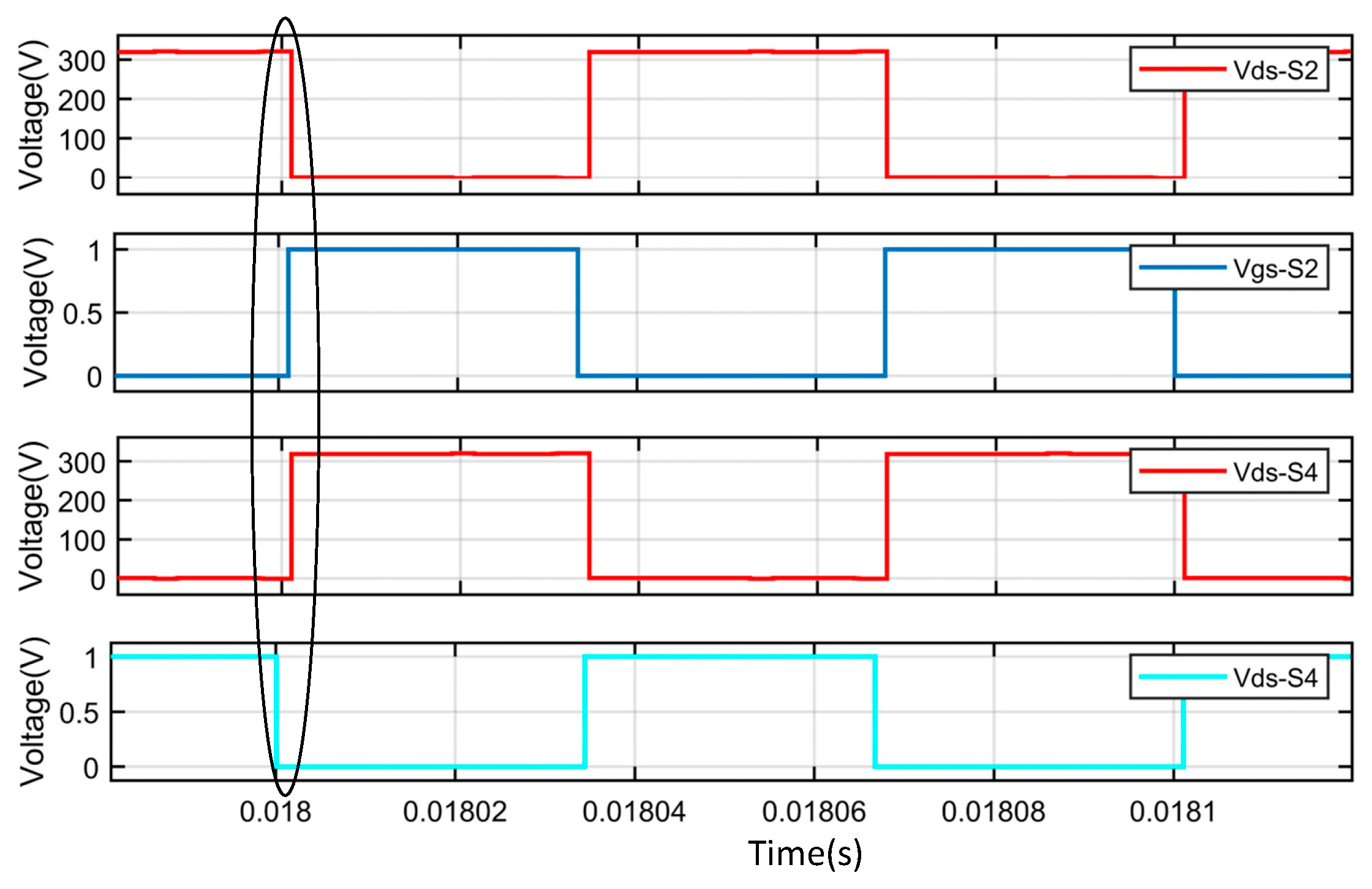

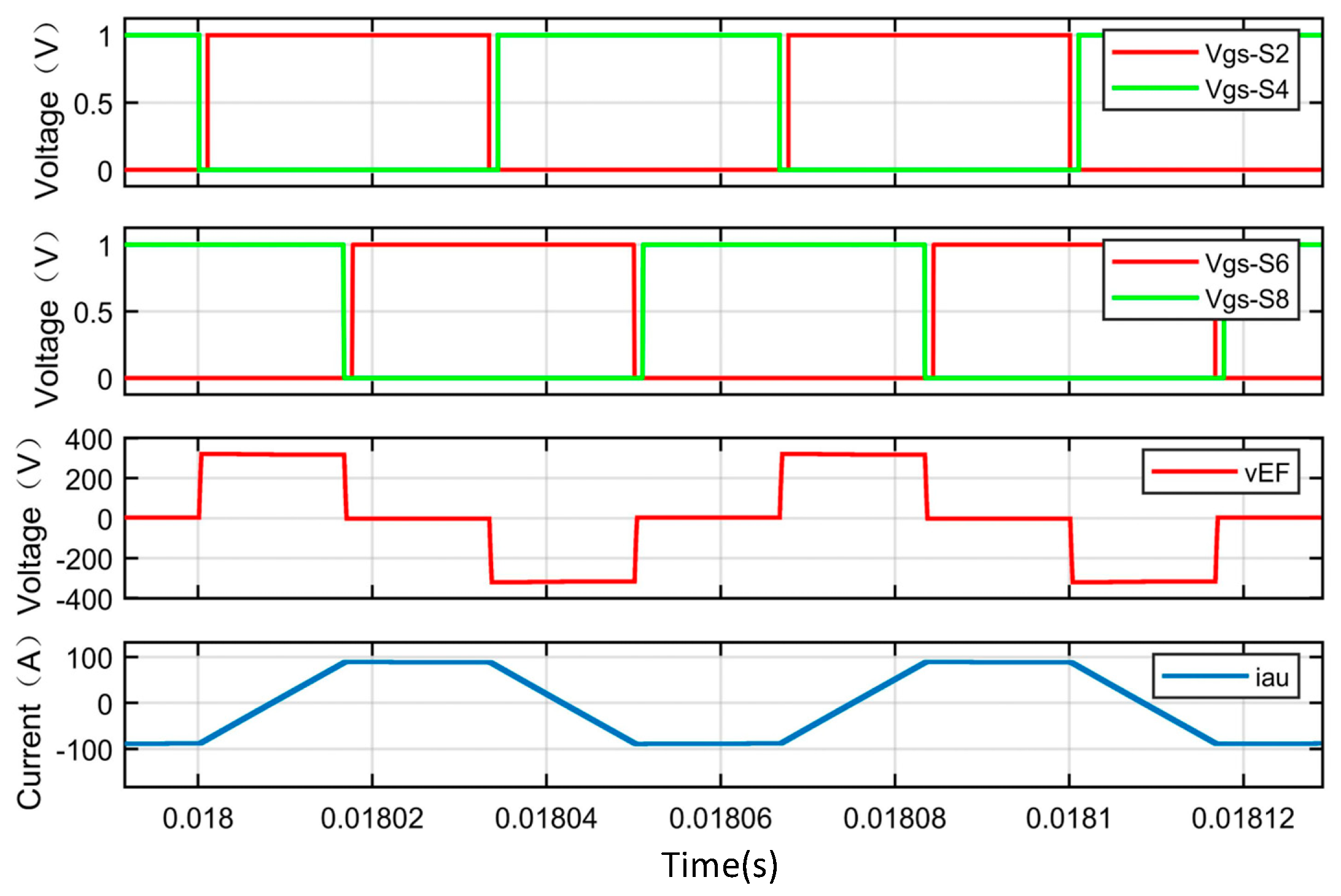

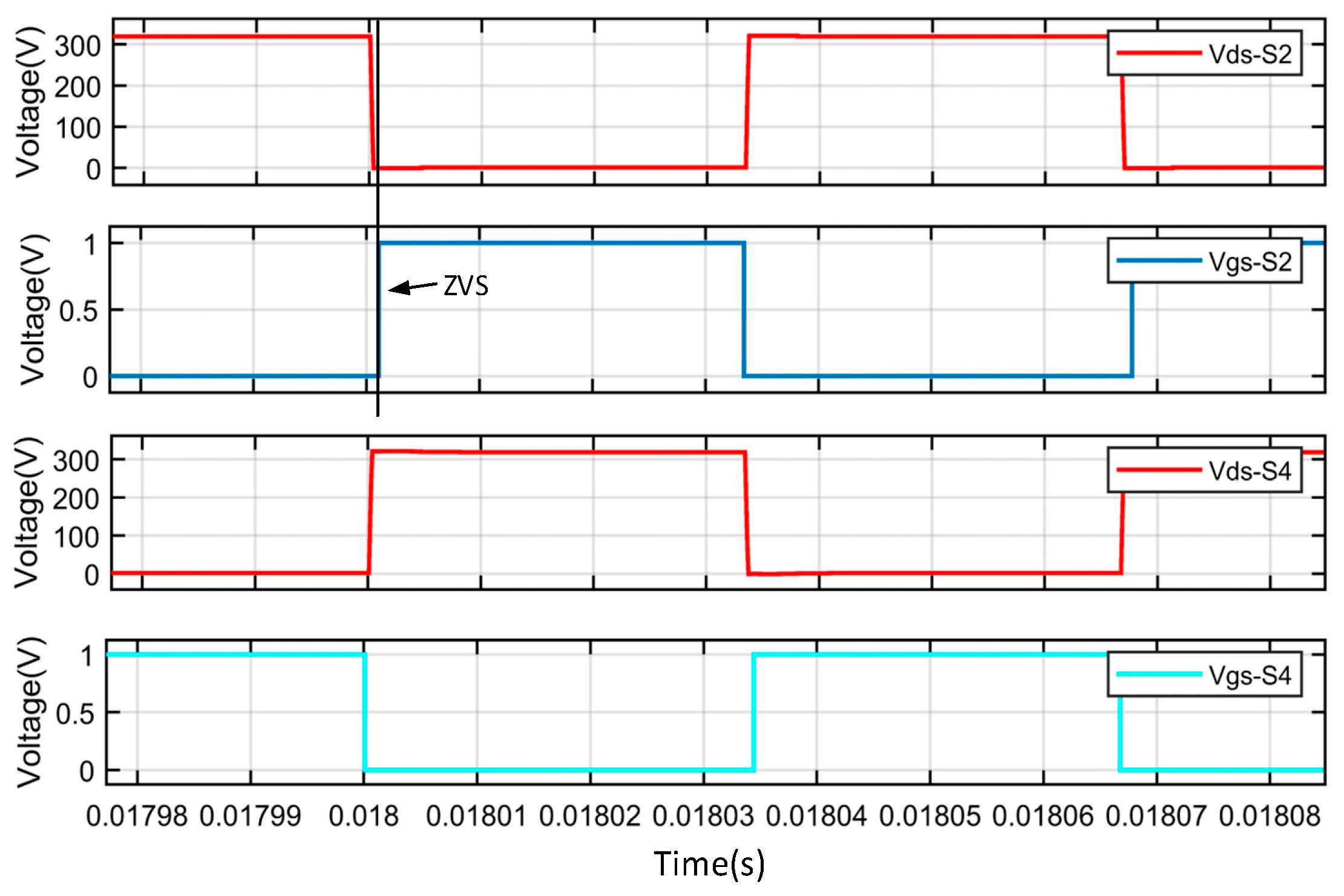

4.1. Simulation Results under Rated Load for an Input Voltage of 320 V

4.2. Simulation Results under Light Load for an Input Voltage of 320 V

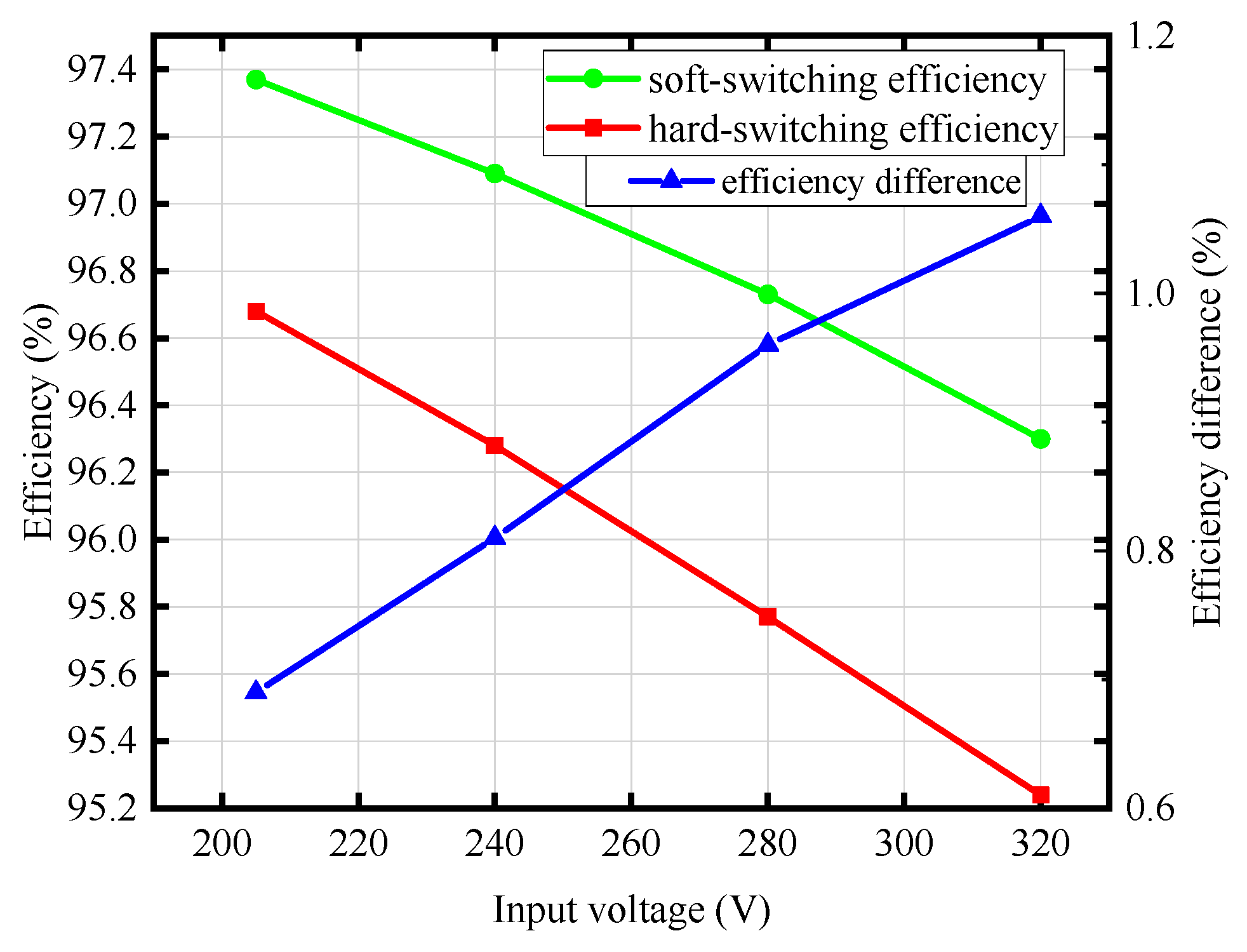

4.3. Comparative Study

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kasper, M.; Bortis, D.; Kolar, J.W. Classification and comparative evaluation of PV panel-integrated DC–DC converter concepts. IEEE Trans. Power Electron. 2014, 29, 2511–2526. [Google Scholar] [CrossRef]

- Lu, Y.; Sun, K.; Wu, H.; Dong, X.; Xing, Y. A three-port converter based distributed DC grid connected PV system with autonomous output voltage sharing control. IEEE Trans. Power Electron. 2019, 34, 325–339. [Google Scholar] [CrossRef]

- Chen, J.; Liu, C.; Liu, H.; Li, G. Zero-voltage switching full-bridge converter with reduced filter requirement and wide ZVS range for variable output application. IEEE Trans. Ind. Electron. 2022, 69, 6805–6816. [Google Scholar] [CrossRef]

- Shi, Y.; Feng, L.; Li, Q.; Kang, J. High power ZVZCS phase shift full bridge DC–DC converter with high current reset ability and no extra electrical stress. IEEE Trans. Ind. Electron. 2022, 69, 12688–12697. [Google Scholar] [CrossRef]

- Kanamarlapudi, V.R.K.; Wang, B.; Kandasamy, N.K.; So, P.L. A New ZVS Full-Bridge DC–DC Converter for Battery Charging With Reduced Losses Over Full-Load Range. IEEE Trans. Ind. Appl. 2018, 54, 571–579. [Google Scholar] [CrossRef]

- Liu, G.; Wang, B.; Liu, F.; Wang, X.; Guan, Y.; Wang, W.; Wang, Y.; Xu, D. An improved zero-voltage and zero-current- switching phase-shift full-bridge PWM converter with low output current ripple. IEEE Trans. Power Electron. 2023, 38, 3419–3432. [Google Scholar] [CrossRef]

- Yen, W.-W.; Chao, P.C.P. A ZVS Phase-Shift Full-Bridge Converter With Input Current Steering to Reduce EMI Noise. IEEE Trans. Power Electron. 2022, 37, 11937–11950. [Google Scholar] [CrossRef]

- Elezab, A.; Zayed, O.; Abuelnaga, A.; Narimani, M. High Efficiency LLC Resonant Converter With Wide Output Range of 200–1000 V for DC-Connected EVs Ultra-Fast Charging Stations. IEEE Access 2023, 11, 33037–33048. [Google Scholar] [CrossRef]

- Li, Y. High-Gain High-Efficiency IPOS LLC Converter With Coupled Transformer and Current Sharing Capability. CPSS Trans. Power Electron. Appl. 2020, 5, 63–73. [Google Scholar] [CrossRef]

- Vu, H.-N.; Choi, W. A Novel Dual Full-Bridge LLC Resonant Converter for CC and CV Charges of Batteries for Electric Vehicles. IEEE Trans. Ind. Electron. 2018, 65, 2212–2225. [Google Scholar] [CrossRef]

- Gu, B.; Lai, J.-S.; Kees, N.; Zheng, C. Hybrid-Switching Full-Bridge DC–DC Converter With Minimal Voltage Stress of Bridge Rectifier, Reduced Circulating Losses, and Filter Requirement for Electric Vehicle Battery Chargers. IEEE Trans. Power Electron. 2013, 28, 1132–1144. [Google Scholar] [CrossRef]

- Liang, Y.; Liu, X. Soft-switching and low-conduction loss full-bridge converter with auxiliary circuit for battery charging applications. J. Power Electron. 2023, 23, 1051–1062. [Google Scholar] [CrossRef]

- Lyu, D.; Soeiro, T.B.; Bauer, P. Design and Implementation of a Reconfigurable Phase Shift Full-Bridge Converter for Wide Voltage Range EV Charging Application. IEEE Trans. Transp. Electrif. 2023, 9, 1200–1214. [Google Scholar] [CrossRef]

- Sun, F.; Chen, J.; Lin, X.; Liao, D. Analysis and Suppression of Rectifier Diode Voltage Oscillation Mechanism in IPOS High-Power PSFB Converters. Electronics 2023, 12, 2871. [Google Scholar] [CrossRef]

- Le, T.-T.; Lee, D.; Kim, J.; Kieu, H.-P.; Choi, S. Modular Bidirectional Differential Converter With Series Parallel Connected Output for Ultra-Wide-Voltage Applications: Control, Module Shedding, and Fail-Safe Operation. IEEE Trans. Power Electron. 2022, 37, 617–628. [Google Scholar] [CrossRef]

- Li, T.; Parsa, L. Design, Control, and Analysis of a Fault-Tolerant Soft-Switching DC–DC Converter for High-Power High-Voltage Applications. IEEE Trans. Power Electron. 2018, 33, 1094–1104. [Google Scholar] [CrossRef]

- Chen, W.; Ruan, X.; Yan, H.; Tse, C.K. DC/DC conversion systems consisting of multiple converter modules: Stability, control, and experimental verifications. IEEE Trans. Power Electron. 2009, 24, 1463–1474. [Google Scholar] [CrossRef]

- You, J.; Cheng, L.; Fu, B.; Deng, M. Analysis and control of input-parallel output-series based combined DC/DC converter with modified connection in output filter circuit. IEEE Access 2019, 7, 58264–58276. [Google Scholar] [CrossRef]

- Luo, J.; Guo, Z.; Zhan, W.; Chen, S. Efficient Hybrid Dual Full-Bridge DC–DC Converters for Pulsed Output Current Applications. IEEE Trans. Ind. Electron. 2023, 70, 12254–12266. [Google Scholar] [CrossRef]

- Mohammadpour, A.; Parsa, L.; Todorovic, M.H.; Lai, R.; Datta, R.; Garces, L. Series-Input Parallel-Output Modular-Phase DC–DC Converter With Soft-Switching and High-Frequency Isolation. IEEE Trans. Power Electron. 2016, 31, 111–119. [Google Scholar] [CrossRef]

- Zhuang, Y.; Liu, F.; Huang, W.; Wang, S.; Jiang, J.; Pan, S.; Zha, X. A peak current reducing method for input-independent and output-series modular converters with LC-branch-based power balancing unit. IEEE Trans. Ind. Electron. 2023, 70, 418–429. [Google Scholar] [CrossRef]

- Liu, F.; Zhu, C.; Liu, Z.; Yang, J.; Wei, Y.; Zhang, Y.; Li, X. Effect of Hydrogen Molecule Release On NBTI By Low-Temperature Pre-Treatment in P-Channel Power VDMOS Transistors. IEEE Trans. Device Mater. Reliab. 2024. early Access. [Google Scholar] [CrossRef]

- Tahi, H.; Tahanout, C.; Boubaaya, M.; Djezzar, B.; Merah, S.M.; Nadji, B.; Saoula, N. Experimental Investigation of NBTI Degradation in Power VDMOS Transistors Under Low Magnetic Field. IEEE Trans. Device Mater. Reliab. 2017, 17, 99–105. [Google Scholar] [CrossRef]

- Huang, L.; Zhou, Y.; Huang, J.; Zeng, J.; Chen, G. Analysis and Design of ZVZCS Full-Bridge Converter With Reduced Components for Input-Series-Output-Parallel Application. IEEE Trans. Ind. Electron. 2021, 68, 6806–6817. [Google Scholar] [CrossRef]

- Guo, Z.; Sha, D.; Liao, X.; Luo, J. Input-Series-Output-Parallel Phase-Shift Full-Bridge Derived DC–DC Converters With Auxiliary LC Networks to Achieve Wide Zero-Voltage Switching Range. IEEE Trans. Power Electron. 2014, 29, 5081–5086. [Google Scholar] [CrossRef]

- Shi, K.; Zhang, D.; Zhou, Z.; Zhang, M.; Gu, Y. A Novel Phase-Shift Dual Full-Bridge Converter With Full Soft-Switching Range and Wide Conversion Range. IEEE Trans. Power Electron. 2016, 31, 7747–7760. [Google Scholar] [CrossRef]

- Gao, Y.; Tang, Y.; Yao, F.; Ge, L.; Guo, Y.; Sun, H. Paralleled Variable Inductor Phase-Shifted Full-Bridge Converter With Full-Load Range ZVS and Low Duty Cycle Loss. IEEE Trans. Ind. Electron. 2024, 71, 4673–4684. [Google Scholar] [CrossRef]

- Yu, C.; Yong, K. A fully regulated dual-output DC–DC converter with special-connected two transformers (SCTTs) cell and complementary pulsewidth modulation–PFM (CPWM-PFM). IEEE Trans. Power Electron. 2010, 25, 1296–1309. [Google Scholar] [CrossRef]

| Input Voltage (V) | 205 | 240 | 280 | 320 | |

|---|---|---|---|---|---|

| Loss Type (W) | |||||

| Switch tube on-state loss | 427.63 | 359.64 | 311.62 | 342.06 | |

| Switch tube opening loss | 697.00 | 816.00 | 952.00 | 1088.00 | |

| Switch tube turn-off loss | 1312.00 | 1536.00 | 1792.00 | 2048.00 | |

| Transformer iron loss | 276.00 | 299.16 | 328.00 | 351.12 | |

| Transformer copper loss | 98.74 | 96.36 | 92.10 | 87.70 | |

| Rectifier diode on-state loss | 396.48 | 408.00 | 418.40 | 426.00 | |

| Rectifier diode turn-off loss | 19.20 | 23.84 | 32.26 | 38.00 | |

| Filter inductance copper loss | 24.25 | 24.25 | 24.25 | 24.25 | |

| Filter inductance iron loss | 5.00 | 5.00 | 5.00 | 5.00 | |

| Parameters | Value |

|---|---|

| Input voltage Vin | 205 V–320 V |

| Output voltage Vo | 2000 V |

| Transformer ratio 1:n | 1:6 |

| Resonant inductance Lr | 1 μH |

| Junction capacitance Cj | 680 pF |

| Filter inductance Lf | 1 mH |

| Filter capacitor Cf | 40 μF |

| Switching frequency fs | 15 kHz |

| Isolation capacitor Cb | 0.416 mF |

| Dead time td | 1.2 μs |

| Auxiliary inductor Lau | 30 μH |

| Auxiliary capacitor Cau | 100 μF |

| Rated power Pn | 100 kW |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Y.; Sun, F.; Chen, J.; Cai, H.; Gao, S. Novel Series-Parallel Phase-Shifted Full-Bridge Converters with Auxiliary LC Networks to Achieve Wide Lagging-Leg ZVS Range. Electronics 2024, 13, 1311. https://doi.org/10.3390/electronics13071311

Wang Y, Sun F, Chen J, Cai H, Gao S. Novel Series-Parallel Phase-Shifted Full-Bridge Converters with Auxiliary LC Networks to Achieve Wide Lagging-Leg ZVS Range. Electronics. 2024; 13(7):1311. https://doi.org/10.3390/electronics13071311

Chicago/Turabian StyleWang, Yunzhi, Fei Sun, Jun Chen, Huafeng Cai, and Shen Gao. 2024. "Novel Series-Parallel Phase-Shifted Full-Bridge Converters with Auxiliary LC Networks to Achieve Wide Lagging-Leg ZVS Range" Electronics 13, no. 7: 1311. https://doi.org/10.3390/electronics13071311

APA StyleWang, Y., Sun, F., Chen, J., Cai, H., & Gao, S. (2024). Novel Series-Parallel Phase-Shifted Full-Bridge Converters with Auxiliary LC Networks to Achieve Wide Lagging-Leg ZVS Range. Electronics, 13(7), 1311. https://doi.org/10.3390/electronics13071311