A Central Array Method to Locate Chips in AOI Systems in Semiconductor Manufacturing

Abstract

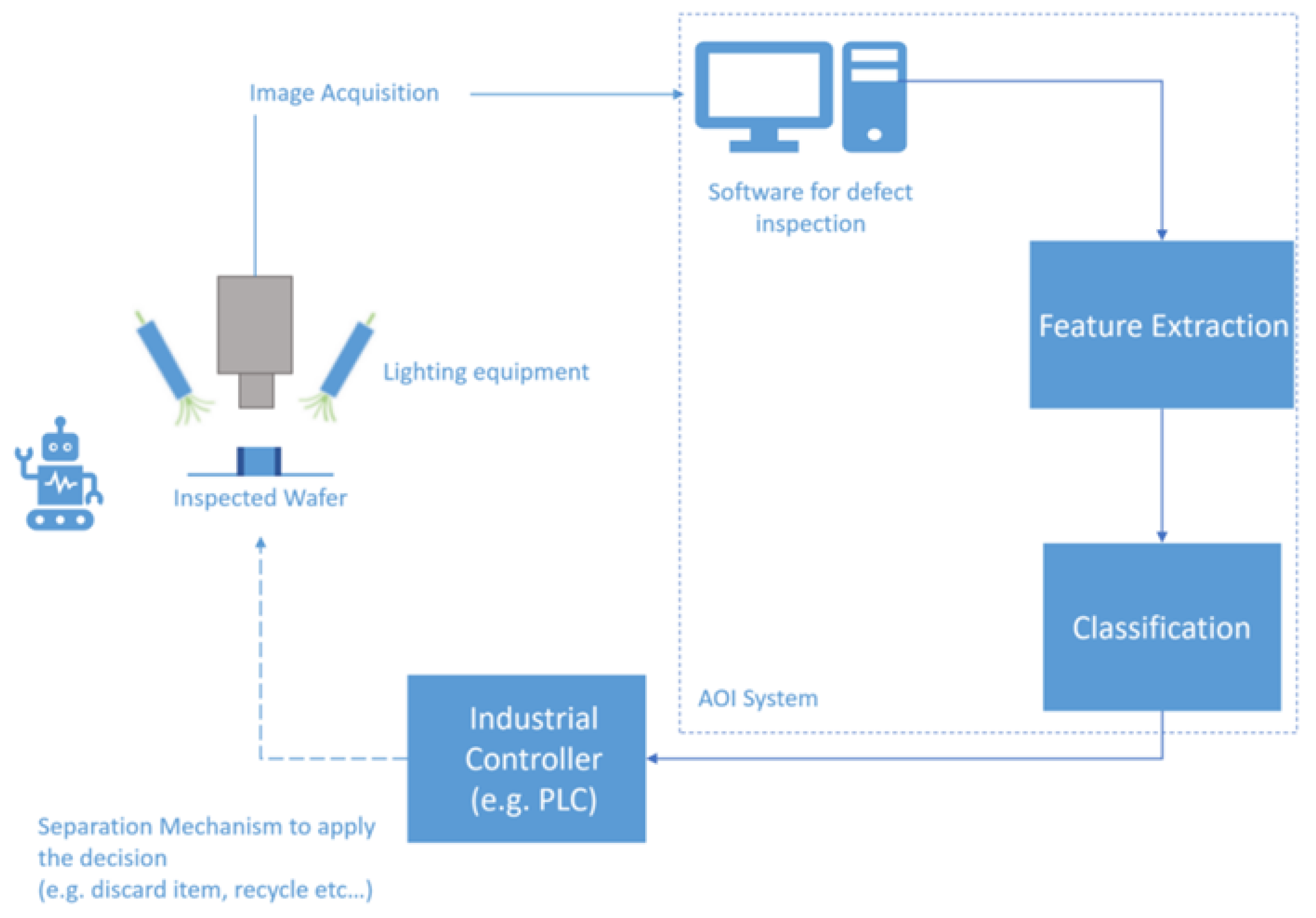

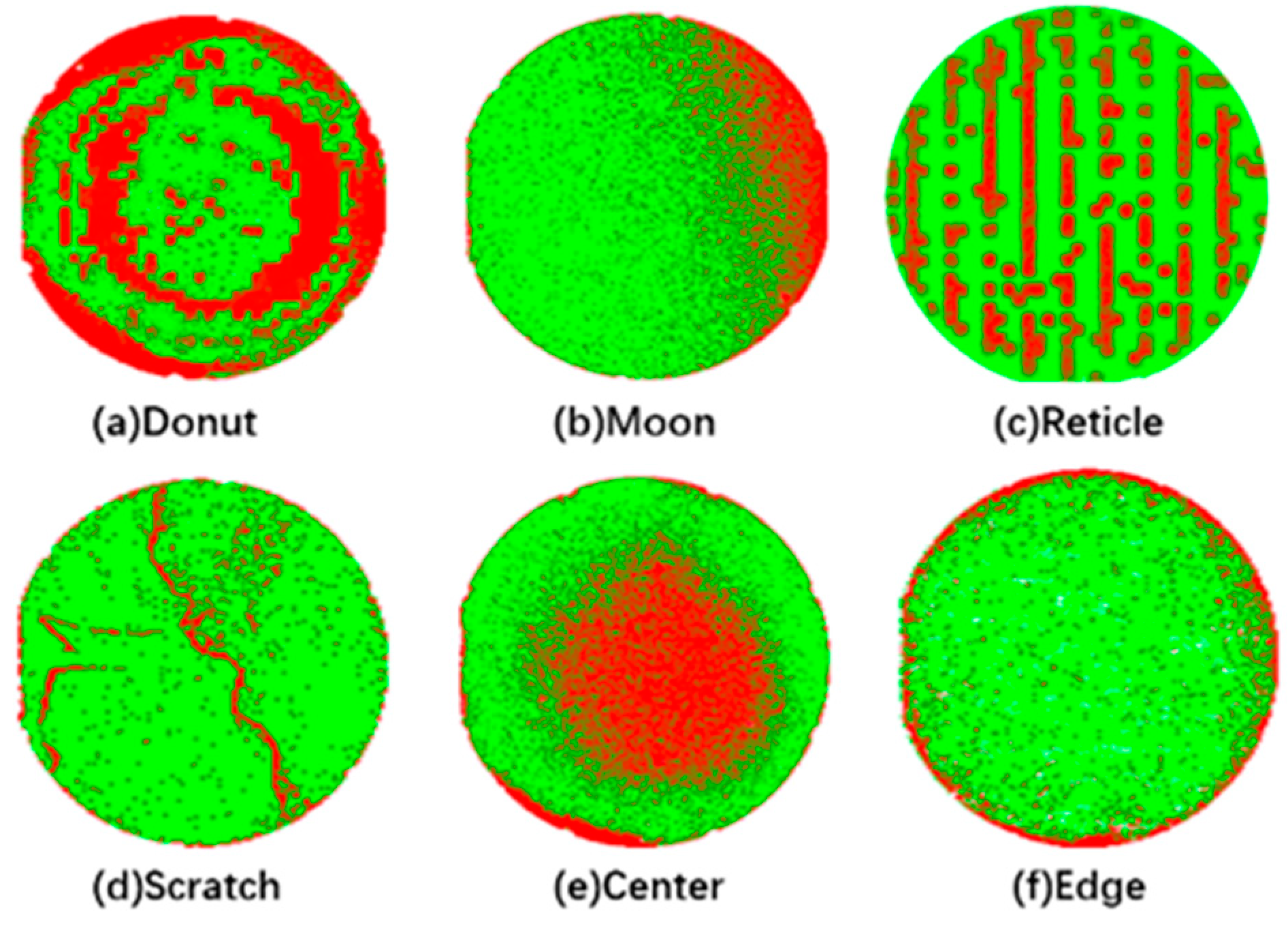

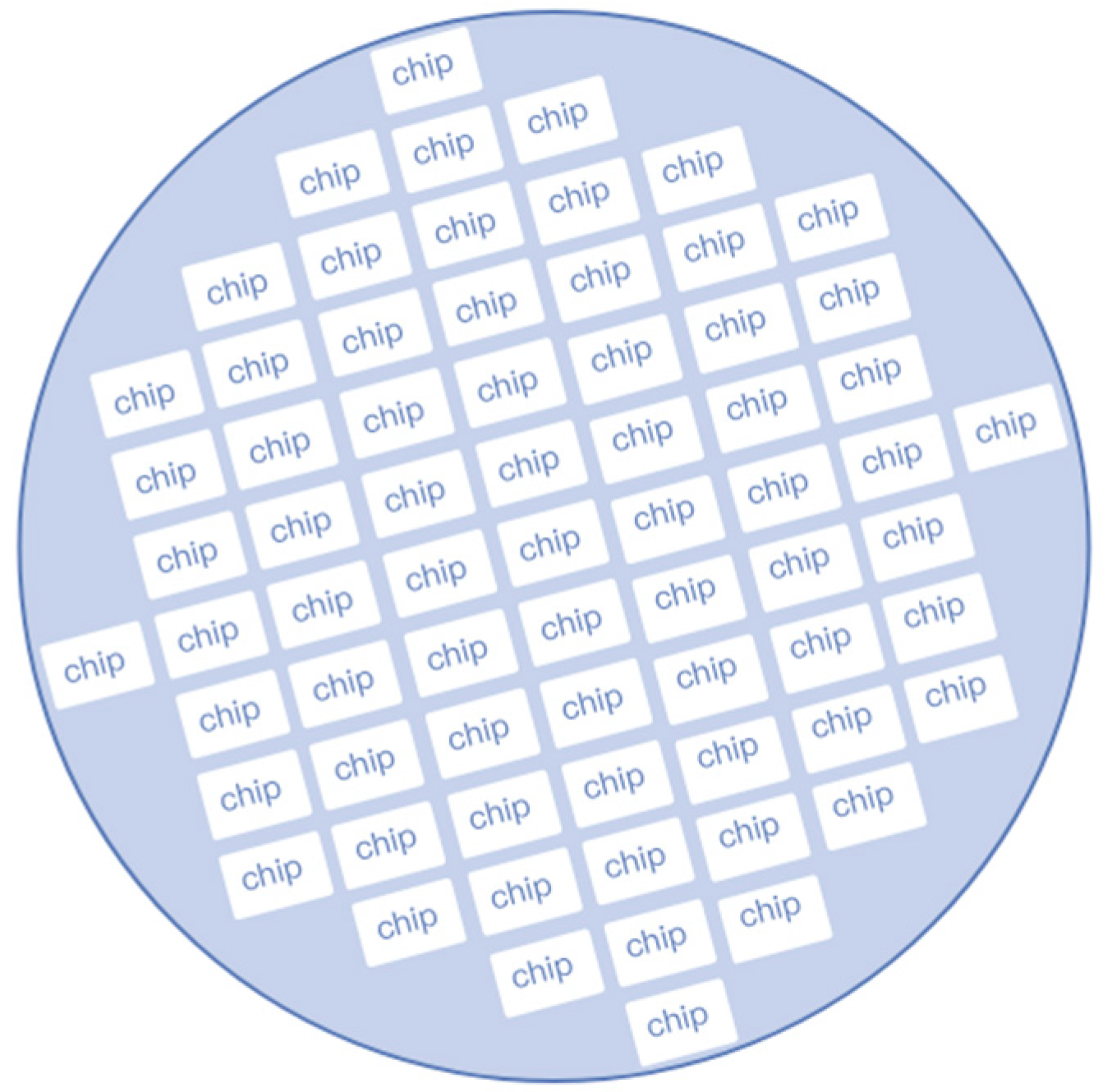

1. Introduction

2. Literature Review

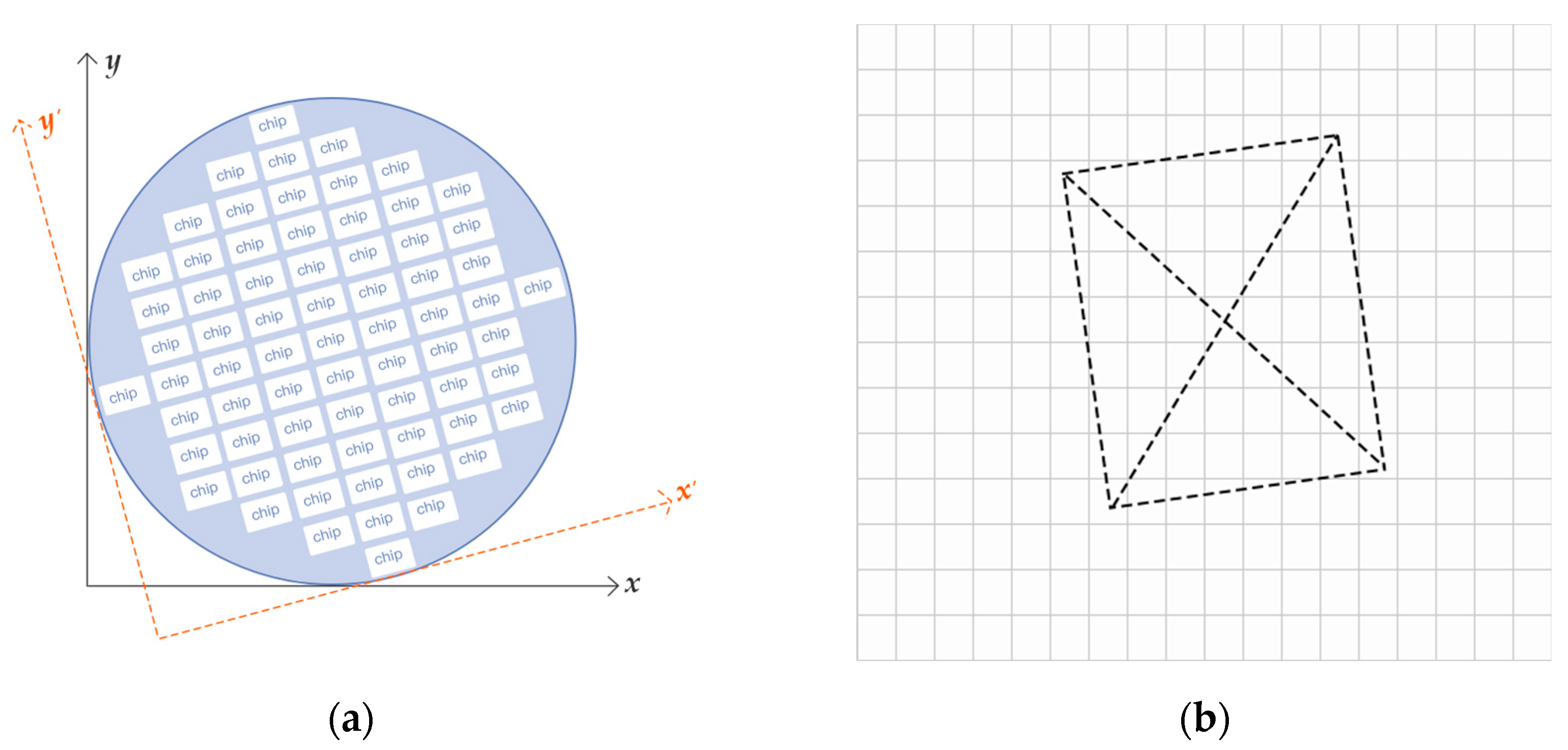

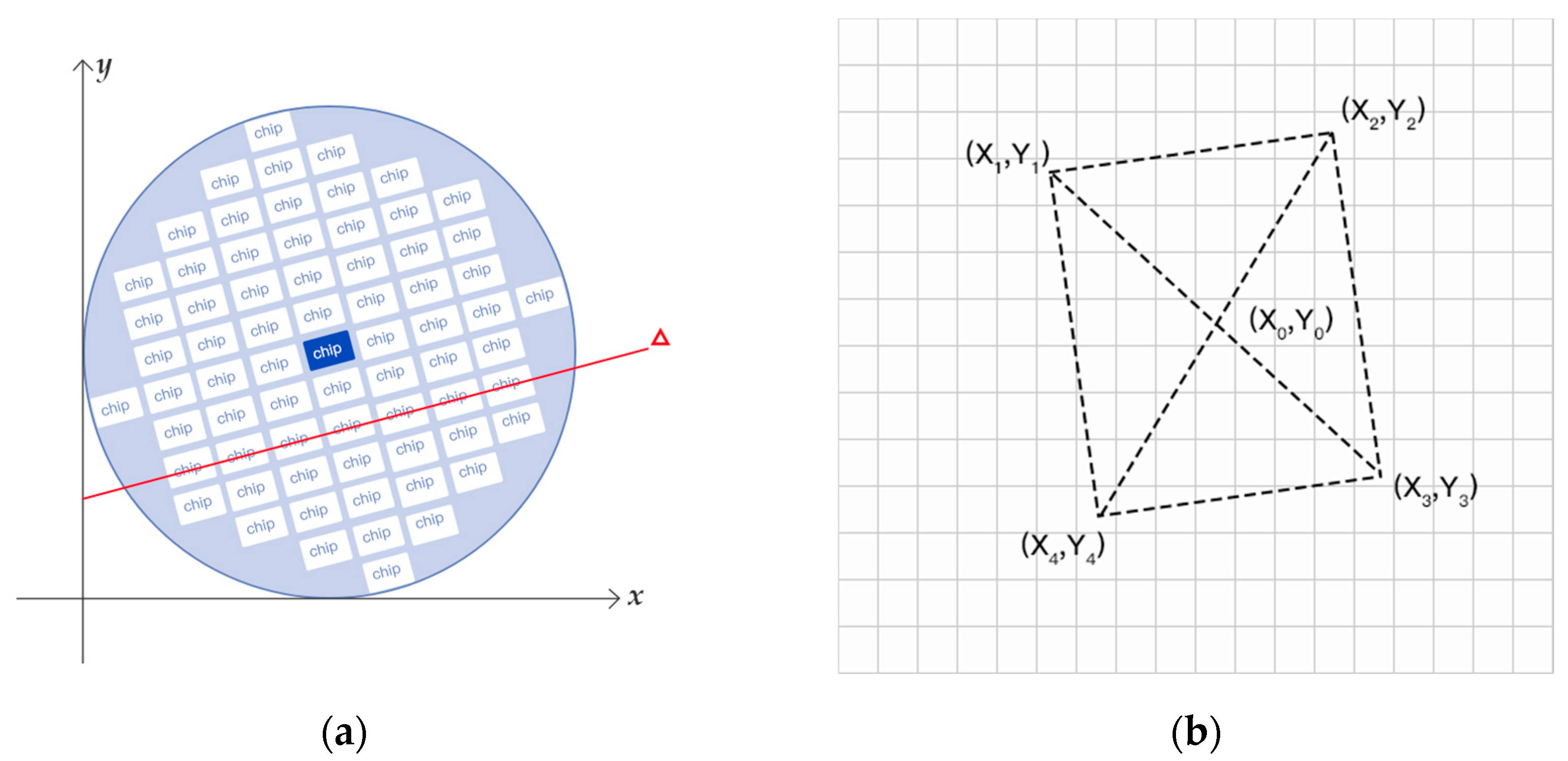

3. A Central Array Method

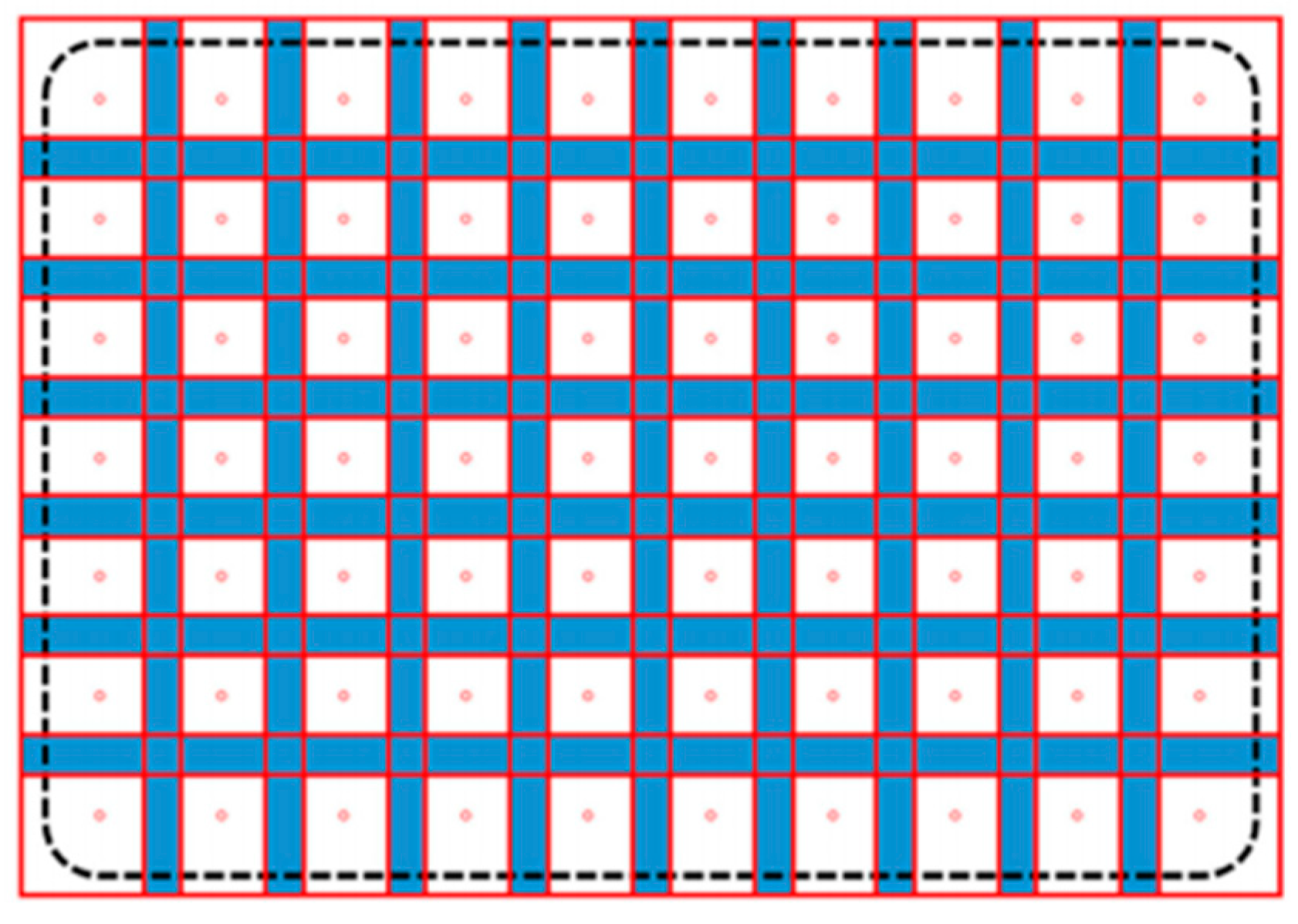

3.1. Merging of Chip Maps

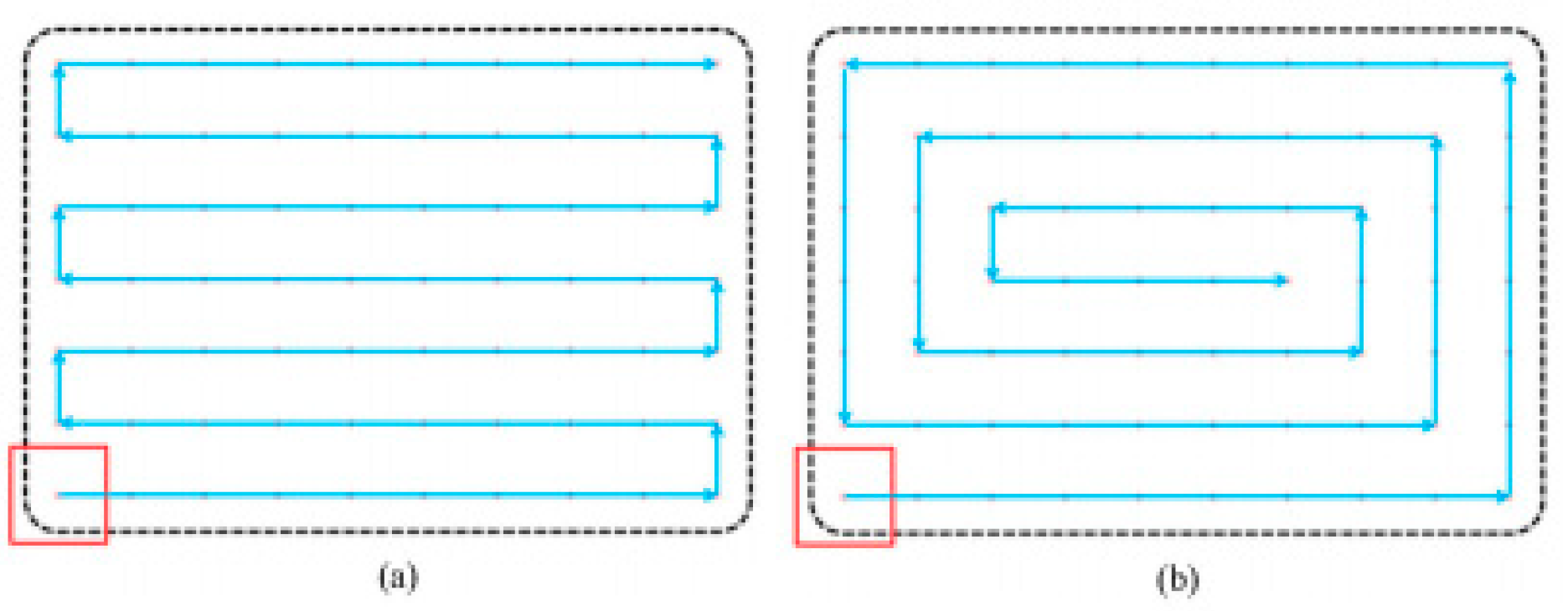

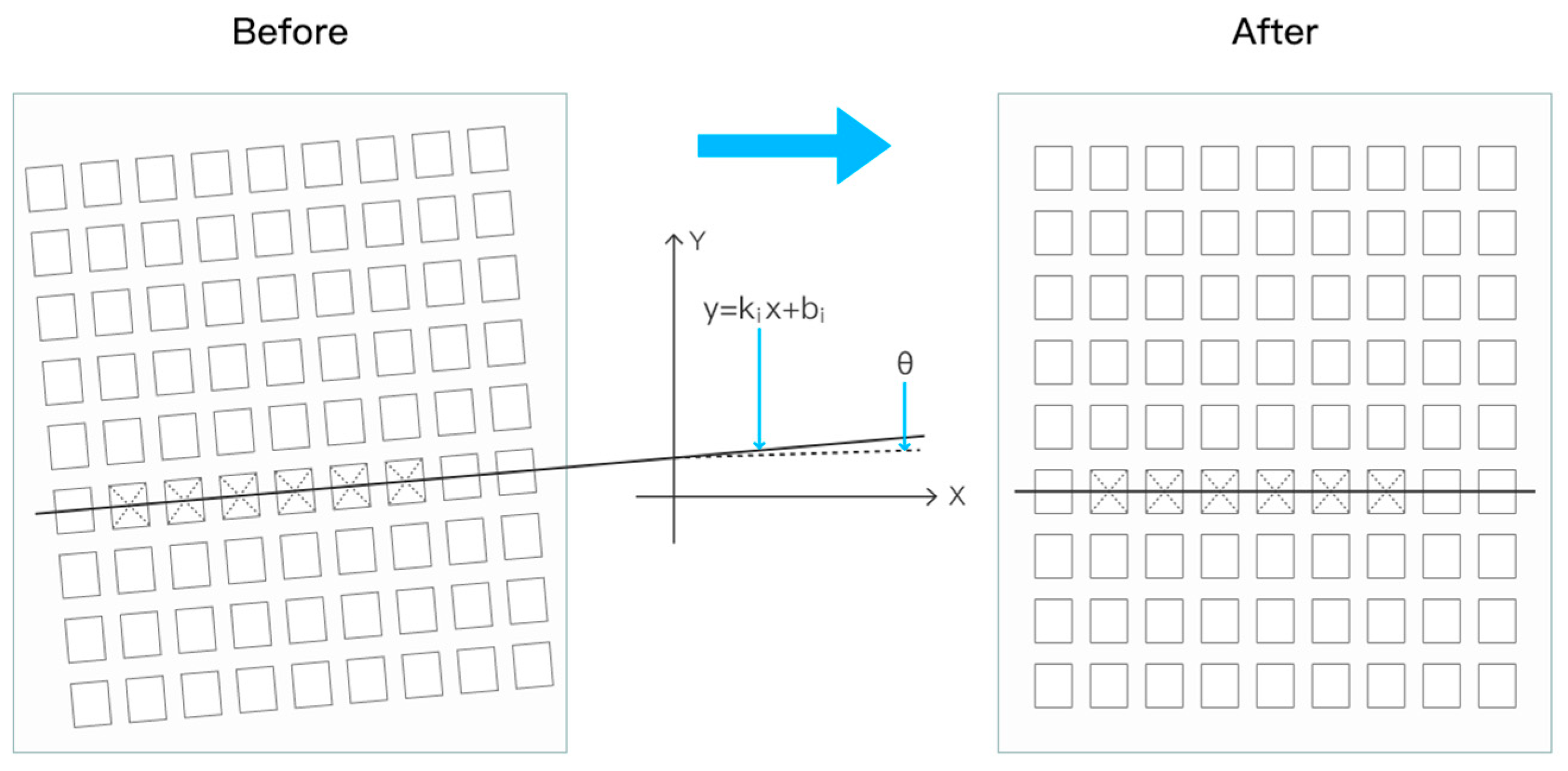

3.2. The Central Array Method

3.3. Implementation of Deep Learning in the AOI System

4. Experiments

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kim, J.; Lee, Y.; Kim, H. Detection and clustering of mixed-type defect patterns in wafer bin maps. IISE Trans. 2018, 50, 99–111. [Google Scholar] [CrossRef]

- Jin, C.; Na, H.; Piao, M.; Pok, G.; Ryu, K. A novel DBSCAN-based defect pattern detection and classification framework for wafer bin map. IEEE Trans. Semicond. Manuf. 2019, 32, 286–292. [Google Scholar]

- Qiao, Y.; Wu, N.; Zhou, M. Real-time scheduling of single-arm cluster tools subject to residency time constraints and bounded activity time variation. IEEE Trans. Autom. Sci. Eng. 2012, 9, 564–577. [Google Scholar] [CrossRef]

- Qiao, Y.; Wu, N.; Zhou, M. A Petri net–based novel scheduling approach and its cycle time analysis for dual-arm cluster tools with wafer revisiting. IEEE Trans. Semicond. Manuf. 2013, 26, 100–110. [Google Scholar] [CrossRef]

- Song, T.; Qiao, Y.; He, Y.; Wu, N.; Li, Z.; Liu, B. Dual-arm cluster tool scheduling for reentrant wafer flows. Electronics 2023, 12, 2411. [Google Scholar] [CrossRef]

- Zhu, Q.; Qiao, Y.; Wu, N.; Hou, Y. Post-processing time-aware optimal scheduling of single robotic cluster tools. IEEE CAA J. Autom. Sin. 2020, 7, 597–605. [Google Scholar] [CrossRef]

- Adly, F.; Yoo, P.; Muhaidat, S.; Al-Hammadi, Y.; Lee, U.; Ismail, M. Randomized general regression network for identification of defect patterns in semiconductor wafer maps. IEEE Trans. Semicond. Manuf. 2015, 28, 145–152. [Google Scholar] [CrossRef]

- Yu, J.; Lu, X. Wafer map defect detection and recognition using joint local and nonlocal linear discriminant analysis. IEEE Trans. Semicond. Manuf. 2016, 29, 33–43. [Google Scholar] [CrossRef]

- Tong, L.-I.; Wang, C.-H.; Huang, C.-L. Monitoring defects in IC fabrication using a hotelling T2 control chart. IEEE Trans. Semicond. Manuf. 2005, 18, 140–147. [Google Scholar] [CrossRef]

- Kim, B.; Jeong, Y.-S.; Tong, S.; Chang, I.-K.; Jeong, M.-K. Step-down spatial randomness test for detecting abnormalities in DRAM wafers with multiple spatial maps. IEEE Trans. Semicond. Manuf. 2016, 29, 57–65. [Google Scholar] [CrossRef]

- Wang, C.-H.; Kuo, W.; Bensmail, H. Detection and classification of defect patterns on semiconductor wafers. IIE Trans. 2006, 38, 1059–1068. [Google Scholar] [CrossRef]

- Hwang, J.; Kuo, W. Model-based clustering for integrated circuit yield enhancement. Eur. J. Oper. Res. 2005, 178, 143–153. [Google Scholar] [CrossRef]

- Chien, C.-F.; Hsu, S.-C.; Chen, Y.-J. A system for online detection and classification of wafer bin map defect patterns for manufacturing intelligence. Int. J. Prod. Res. 2013, 51, 2324–2338. [Google Scholar] [CrossRef]

- Lee, J.; Yu, S.; Park, S. Design of intelligent data sampling methodology based on data mining. IEEE Trans. Robot. Autom. 2001, 17, 637–649. [Google Scholar] [CrossRef]

- Wang, C.-H.; Wang, S.-J.; Lee, W.-D. Automatic identification of spatial defect patterns for semiconductor manufacturing. Int. J. Prod. Res. 2006, 44, 5169–5185. [Google Scholar] [CrossRef]

- Chien, C.-F.; Wang, W.-C.; Cheng, J.-C. Data mining for yield enhancement in semiconductor manufacturing and an empirical study. Expert Syst. Appl. 2007, 33, 192–198. [Google Scholar] [CrossRef]

- Wu, M.-J.; Jang, J.-S.; Chen, J.-L. Wafer map failure pattern recognition and similarity ranking for large-scale data sets. IEEE Trans. Semicond. Manuf. 2015, 28, 1–12. [Google Scholar]

- Kim, B.; Jeong, Y.-S.; Tong, S.H.; Chang, I.-K.; Jeongyoung, M.-K. A regularized singular value decomposition-based approach for failure pattern classification on fail bit map in a DRAM wafer. IEEE Trans. Semicond. Manuf. 2015, 28, 41–49. [Google Scholar]

- Kyeong, K.; Kim, H. Classification of mixed-type defect patterns in wafer bin maps using convolutional neural networks. IEEE Trans. Semicond. Manuf. 2018, 31, 395–402. [Google Scholar] [CrossRef]

- Lowe, D. Distinctive image features from scale-invariant key-points. Int. J. Comput. Vis. 2004, 60, 91–110. [Google Scholar] [CrossRef]

- Cheon, M.-K.; Lee, W.-J.; Hyun, C.-H.; Park, M. Rotation invariant histogram of oriented gradients. Int. J. Fuzzy Log. Intell. Syst. 2011, 11, 293–298. [Google Scholar] [CrossRef][Green Version]

- Khotanzad, A.; Hong, Y. Invariant image recognition by Zernike moments. IEEE Trans. Pattern Anal. Mach. Intell. 1990, 12, 489–497. [Google Scholar] [CrossRef]

- Bay, H.; Ess, A.; Tuytelaars, T.; Van Gool, L. Speeded-up robust features (SURF). Comput. Vis. Image Underst. 2008, 110, 346–359. [Google Scholar] [CrossRef]

| System Type | Wafer Recipe | Average Detection Time |

|---|---|---|

| AI-based AOI system | S-B-K | 0:04:03 |

| S-G-K | 0:04:20 | |

| S-B-M | 0:03:39 | |

| S-G-M | 0:03:56 | |

| Current AOI system | S-B-K | 0:04:46 |

| S-G-K | 0:05:06 | |

| S-B-M | 0:04:17 | |

| S-G-M | 0:04:39 |

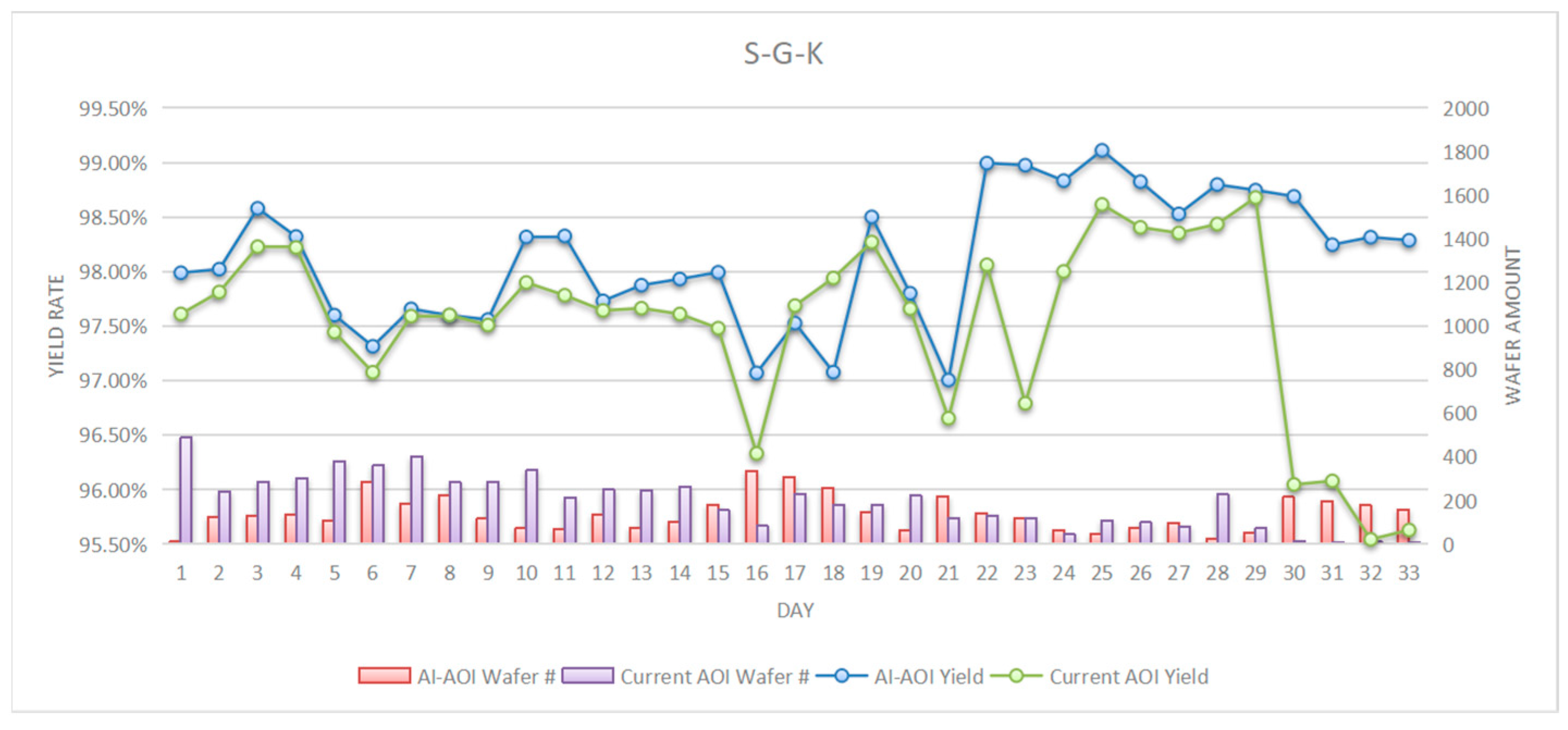

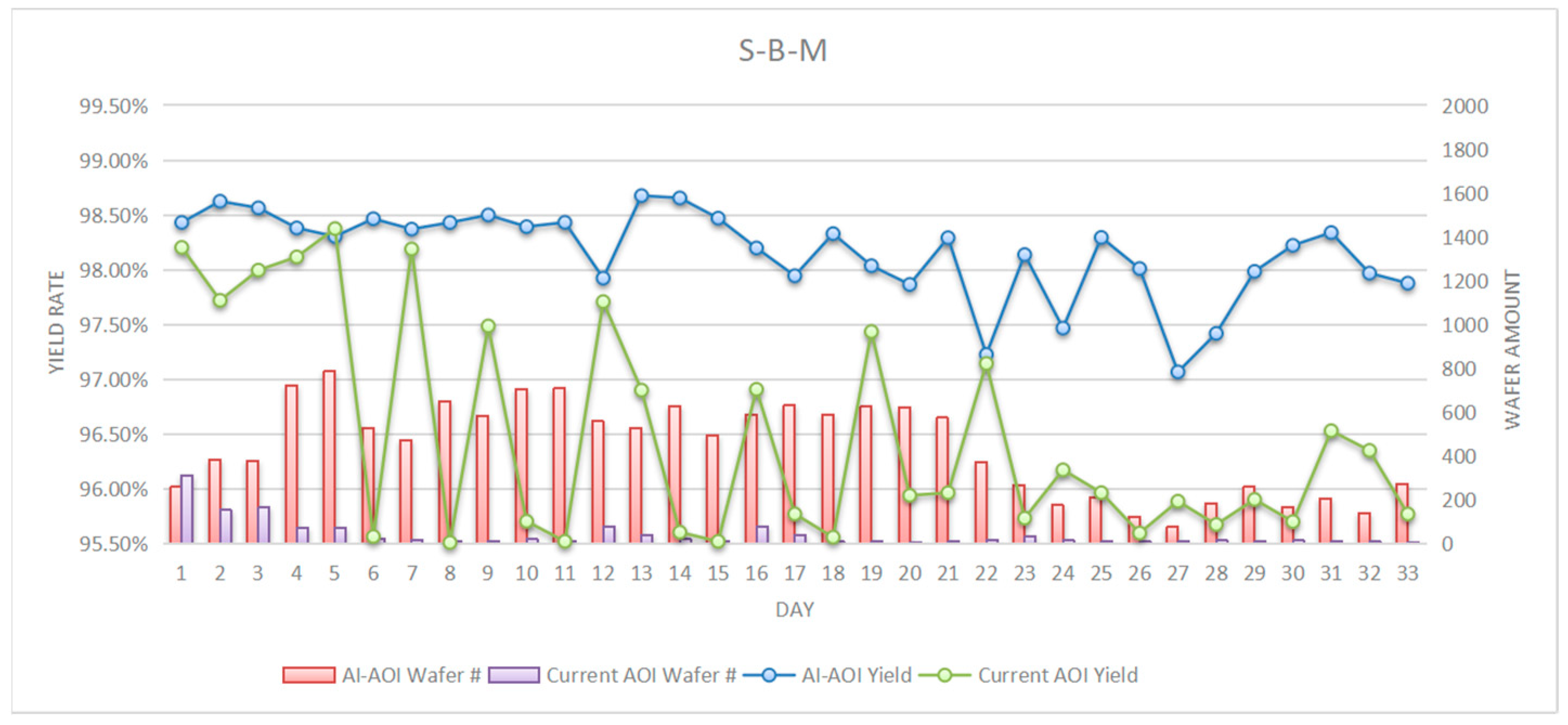

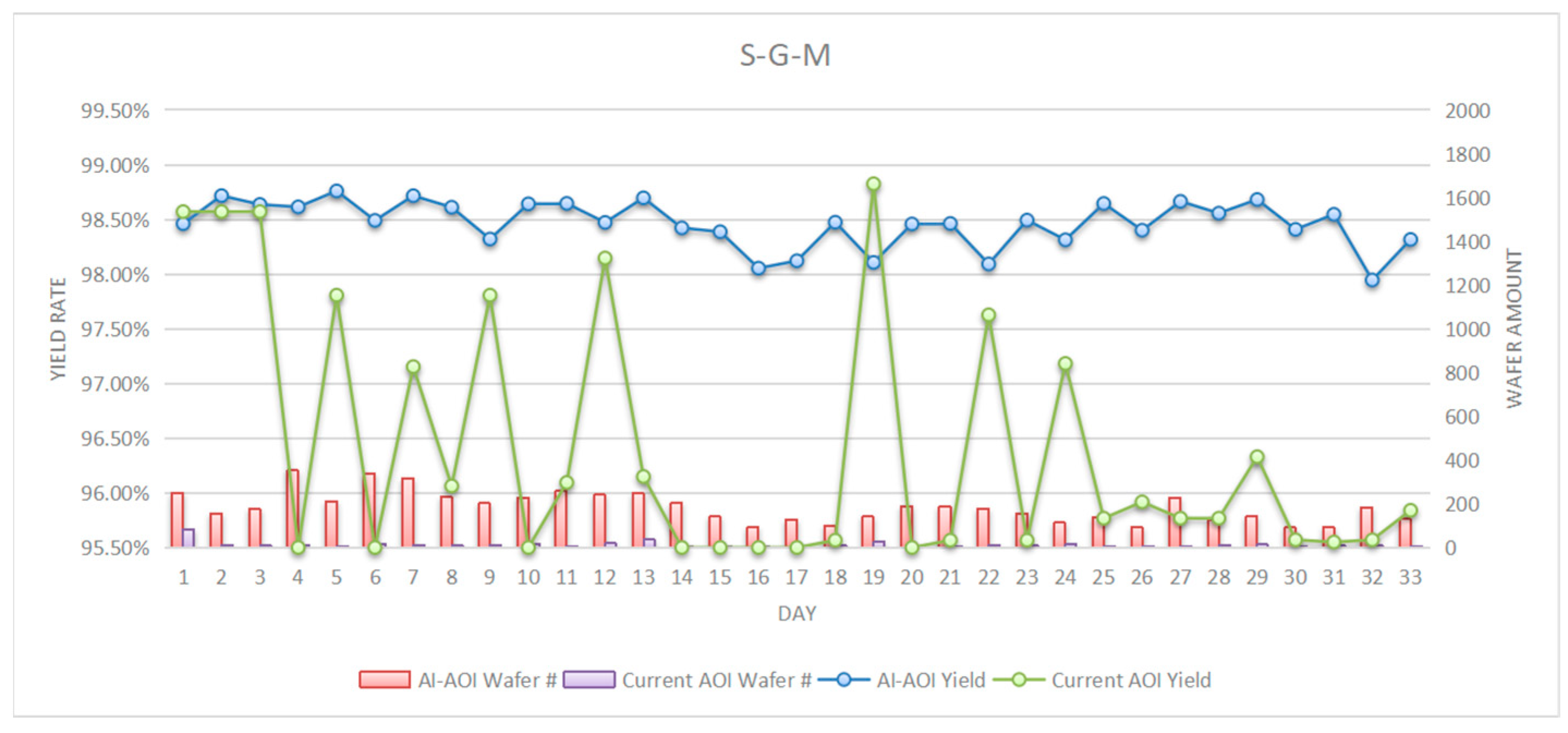

| System Type | Wafer Recipe | Minimum YR | Maximum YR | Overall YR |

|---|---|---|---|---|

| AI-based AOI system | S-B-K | 98.01% | 99.06% | 98.54% |

| S-G-K | 97.01% | 99.11% | 98.06% | |

| S-B-M | 97.07% | 98.68% | 97.87% | |

| S-G-M | 97.95% | 98.76% | 98.35% | |

| Current AOI system | S-B-K | 97.62% | 98.76% | 98.19% |

| S-G-K | 95.54% | 98.68% | 97.11% | |

| S-B-M | 95.51% | 98.37% | 96.94% | |

| S-G-M | 95.50% | 98.83% | 97.16% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fu, H.; Lai, Y.; Pan, C.; Zhang, S.; Bai, L.; Li, J. A Central Array Method to Locate Chips in AOI Systems in Semiconductor Manufacturing. Electronics 2024, 13, 1070. https://doi.org/10.3390/electronics13061070

Fu H, Lai Y, Pan C, Zhang S, Bai L, Li J. A Central Array Method to Locate Chips in AOI Systems in Semiconductor Manufacturing. Electronics. 2024; 13(6):1070. https://doi.org/10.3390/electronics13061070

Chicago/Turabian StyleFu, Huichu, Yiming Lai, Chunrong Pan, Siwei Zhang, Liping Bai, and Jie Li. 2024. "A Central Array Method to Locate Chips in AOI Systems in Semiconductor Manufacturing" Electronics 13, no. 6: 1070. https://doi.org/10.3390/electronics13061070

APA StyleFu, H., Lai, Y., Pan, C., Zhang, S., Bai, L., & Li, J. (2024). A Central Array Method to Locate Chips in AOI Systems in Semiconductor Manufacturing. Electronics, 13(6), 1070. https://doi.org/10.3390/electronics13061070