In this section, we address the flying capacitor voltage dynamics under PSPWM, deriving a newly conceived state space dynamic model. The main purpose of the model is to provide some insight about the origin, the effects, and the dynamic characteristics of the oscillation phenomena that take place in FCML boost converters.

2.1. Phase-Shifted PWM

In this study, we want to explore the intrinsic circuit dynamic properties and, specifically, how the flying capacitors interact with each other and with the rest of the circuit, in particular, with the input inductor. Therefore, at this stage, we do not need to consider any specific control organization. The circuit will be treated as a simple boost-type FCML DC-DC converter, operating in

open-loop conditions, i.e., considering only the modulator layer of the whole control hierarchy. While this approach somewhat narrows the scope of the discussion, as no specific control design is considered, it allows to study the intrinsic converter performance before feedback is applied and complicates the observable dynamics. Furthermore, many papers have already discussed the closed-loop control of FCML converters, e.g., [

2,

11,

12], providing all the basic information needed to design digital voltage and current regulators as needed by specific applications.

Ever since the first published papers on FCML DC-DC converter topologies [

3,

5], the preferred modulation strategy has been indicated as PSPWM, the same normally employed in controlling, for example, interleaved converter topologies. Some fundamental properties of PSPWM in FCML circuits motivate this choice:

The voltage conversion ratio of the converter, under PSPWM, is exactly the same as a standard, two-level, DC-DC converter, operating in continuous conduction mode (CCM).

PSPWM induces a specific voltage scaling across the flying capacitors, namely, such that in the general, N-level, boost converter case,

which, in turn, generates a ripple frequency multiplication effect on the inductor current.

PSPWM is said to allow the self-balancing of the flying capacitor voltages, at least in ideal conditions.

For ideal conditions, we mean that the driving signals present no asymmetry or phase errors, glitches, or jitter whatsoever, and that the power circuit itself is ideal, i.e., no parasitic components and no mismatch among nominally equal components can be observed.

In the general case with

N levels, the number of converter switching cells is equal to

. Each one is controlled by a phase of the modulator, exactly as in a simple half bridge configuration, i.e., with complementary, not overlapping (i.e., with suitable dead-times inserted), gate driving signals for the low-side and high-side devices. In addition,

N − 2

critical duty cycles can be defined as in

that mark the borderline among adjacent converter operating regions (whose number is

, as are the modulator phases).

In the particular case of a four-level circuit, like the one in

Figure 1, we are dealing with three cells and, accordingly, with a three-phase PSPWM organization, where the time displacement between two consecutive phase carriers is equal to

. Three different operating regions are possible, depending on the specific duty cycle

D at which the modulator operates in the steady state. These can be defined as

where

are the two critical duty cycles for this topology. The modulation patterns for each operating region are shown in

Figure 2.

As can be seen, each modulation pattern defines a different sequence of circuit states, with specific flying capacitor current profiles as shown on the right column of

Figure 2. This determines a different dynamic behavior in each operating region as will be discussed in the following

Section 2.3.

The procedure to derive the circuit configuration and dynamic model in each operating region can be automated and more easily extended to a larger number of levels considering a systematic approach, whose first step is the construction of the

switching state matrices for each operating region. For the four-level topology considered here, such matrices are given by

where

indicates the circuit operating region and each element represents the state of

switches (one for each row in ascending order) in each modulation period sub-interval

k (ordered from left to right), indicating with one the state of a closed switch and with zero the state of an open switch. The explicit expressions are presented in

Appendix A. As it is easy to verify, they can be immediately matched to the plots of

Figure 2. In the general case, an

N-level converter will be fully described by

N − 1 switching state matrices, each one having

rows (as the number of switching cells) and

columns (as the number of sub-intervals in the modulation period).

As is performed in [

11], from the switching state matrices, the

capacitor connection matrices can be built. The capacitor connection matrices have the same dimensions as the switching state matrices and can be automatically built as

The explicit values of

are, once again, shown in

Appendix A. Their interpretation is straightforward: during each sub-interval

k of the switching period, capacitor

is either connected in series with the inductor or connected in anti-series with the inductor, or else altogether disconnected from the current path, which makes the matrix element value

respectively equal to +1, −1, or 0.

Additional insight on the circuit operation can be achieved if one considers the sub-interval duration vectors, which, in the example case, are given by

where

,

is the modulator switching period and

Vectors (

7) can be used to weight the capacitor connection matrices on the sub-interval durations, which is simply performed by multiplying each row of (

6) and the corresponding duration vector. This procedure yields the

time weighted capacitor connection matrices that are defined as

where

indicates the element-wise multiplication. As will be explained in

Section 2.3, (

6) and, most importantly, (

9) allow to automate the construction of the system model state matrices.

2.2. PSPWM Properties

The analysis of (

9) allows to see why the fundamental properties of the PSPWM modulator mentioned in

Section 2.1 hold for any FCML circuit. As can be easily verified, irrespective of the considered operating region, the sum of the elements appearing on each row corresponding to flying capacitors, e.g., rows 1 and 2 in (

9), always equals zero. Consequently, assuming steady-state operation and negligible ripple over currents and voltages, it is possible to write the

balance of

L over a modulation period in the following generalized form

that, observing the last equality, yields the voltage conversion ratio of a boost converter. Clearly, the result is the same for any operating region

. Because the properties of matrices (

9) are not changing with the number of levels, the methodology followed to derive (

10) represents a proof of the first property of PSPWM in FCML converters for any number of levels

N.

Furthermore, if one imposes the

balance of

L to be zero also

over each sub-interval, as it is necessary to have the same average inductor current and obtain ripple frequency multiplication, it is possible to write a system of equations like, as an example,

that applies to region

. The above system can be immediately solved using (

8), yielding

thus proving the second fundamental property. Of course, if region

or

is considered instead of

, the result is exactly the same. Once again, the procedure to derive the system of Equation (

11) can be automated, just manipulating matrices (

9), thus allowing the property to be proven for any number of levels

N. In agreement with (

12), any time the flying capacitor voltages satisfy (

1), the circuit of

Figure 1 experiences a frequency multiplication effect such that the current ripple on

L, in the steady state, will be at

,

being the converter modulation frequency.

The PSPWM modulator, furthermore, naturally tends to maintain a balanced operating condition, with some degree of robustness. If one considers again (

9), it is clearly visible that the inductor current flows through each flying capacitor for identical times in opposite directions. Neglecting the ripple, if the average inductor current is slowly (here, we mean that the variation must be so slow to be almost undetectable in a single modulation period; in other words, the decoupling capability of the modulator is effective only for perturbations falling inside a bandwidth whose upper limit is much lower than the converter switching frequency, and in this frequency range, power dissipation mechanisms are more effective in driving the circuit back to a balanced operating condition) changing over time, then there will be no visible effect on the flying capacitor voltages, as the variation will affect both the charging and discharging practically by the same amount, leaving the average charge stored in the flying capacitor unchanged. Similarly, because the contribution of each flying capacitor voltage to the inductor

balance is always zero, a slow variation in such a voltage is not able to induce significant effects on the average inductor current. Something similar can be said in relation to the converter output voltage. Slow output voltage variations are tracked by the average flying capacitor voltages because (

11) is in any case satisfied whenever

is not changing significantly in a modulation period. Therefore, slow variations in the output voltage do not induce unbalances in the average flying capacitor voltages with respect to their expected values (

12). In a sense, the flying capacitor structure is transparent to the low-frequency dynamics of both the inductor current and the output voltage.

This is the third inherent feature of the PSPWM modulator: it indeed allows to decouple the inductor from the flying capacitors so that, at least in a limited bandwidth, disturbances cannot freely propagate from one to the others and the other way around. Unfortunately, wider bandwidth disturbances, such as those induced, for example, by duty cycle, load or input voltage steps, modulator jitter or other asymmetries in the power circuit, have the capability of unbalancing the flying capacitors, perturbing the frequency multiplication effect and propagating through all system state variables, a complex phenomenon that we will analyze in the following sections.

2.3. Converter Dynamic Model Derivation

As discussed in

Section 2.1, the FCML boost converter, driven by PSPWM, undergoes a sequence of

topological configurations in each modulation period, resulting from the different switch states. The variations in the converter structure make it impossible to treat it as a linear system, even in open-loop operating conditions.

A typical way to circumvent the problem and to linearize the system is to adopt the state space averaging approach, where equivalent system state matrices are obtained as the weighted time average of the ones describing the circuit in each sub-interval of the modulation period. The resulting model is then linearized considering small signal perturbations around a specific operating point. By construction, it describes the system dynamics only on time scales longer than that modulation period, but, because the phenomena that take place in a switching circuit typically have time constants much longer than that, the model is normally adequate to accurately predict the circuit’s response to small signal perturbations.

Referring to the circuit of

Figure 1, we can start deriving the average model by defining a system state vector, made of four components, each one representing the deviation of the variable from its steady-state value, that is

Being that the converter is operated in an open loop, voltage

represents the only system input, as the control input, i.e., the duty cycle, is considered constant. This makes the individual subsystems corresponding to each circuit configuration intrinsically linear, and allows us to neglect, for now, the usual small signal linearization step. The sets of linear differential equations describing the dynamic relations among the above state vector components and the input in every sub-interval of the modulation period and in every operating region, can be written in the general form

where the subscripts

r and

s indicate, respectively, the operating region and the sub-interval of the modulation period where matrices

and

are applicable. Referring to the example case with

, 18 different state matrices need to be calculated to derive a set of three average state space models, each one applicable to a specific converter operating region. In each operating region, we can then determine the average state matrix as

and the average input matrix as

If we now recall the definition of (

6) and (

9), we notice that (

15) is bound to yield

a null sub-matrix . This is due to the fact that, in any sub-interval, a flying capacitor current is always written as in

or

or else

, and the inductor current

is assumed not to change during the modulation period. This makes the conventional state space averaging approach structurally unable to catch the inner dynamics of the converter [

9,

11,

14].

Differently from other studies, our conclusion is not that the flying capacitors are dynamically decoupled from the rest of the circuit. On the contrary, we want to overcome this limitation of the standard model by following a different approach. Indeed, in FCML converters, the system state variables interact among each other

within the modulation period, and their average value actually changes along the way. Some recent papers, like [

19,

20], although referring to buck-type converters, tackled the same problem by means of state transition modeling, which proved to be able to predict the oscillatory behavior of the circuit. Additionally, Ref. [

20] also provided an automatic matrix derivation procedure similar to, and possibly more general than, the one presented in

Appendix A. However, they did not provide explicit expressions for the circuit resonant frequency and gave only limited insight on the underlying physical process. Both limitations can be overcome by the modeling technique described in the following.

2.4. Circuit Dynamics Within the Modulation Period

We can illustrate the rationale of the modeling approach we are about to follow referring to

Figure 3 that describes the inner dynamics of a four-level boost converter, assumed to be operating in region

, i.e., with

. Let us suppose all flying capacitors to have the same value

and that we can somehow perturb the system ideal steady-state condition by moving, at instant

, a small amount of charge from

to

, thereby making

and

. Because duty cycle D is constant and the circuit is ideal, the only effect is a deviation of the inductor current trajectory, which, at the end of sub-interval 1, brings the peak value

higher than is nominal.

In the following sub-interval, capacitors and are both disconnected from the circuit and, therefore, the current follows a trajectory with the same slope it would have had in the ideal case. In the third sub-interval, capacitor is connected to the inductor with opposite polarity with respect to the first sub-interval, which means that its effect on the current trajectory is compensated for and, if there were not an unbalance for as well, the original current trajectory would be restored (this is visualized by a red line in the picture). Please note that this reasoning holds as long as we can assume that the current deviation during sub-interval 1 does not change the average voltage on C1 because only if that happens will the compensation taking place in the third sub-interval be exact. If this is not the case, the compensation will be incomplete, and a small amount of charge will be further removed from or added to capacitor , depending on the initial perturbation sign, determining an incremental variation in its average voltage. A totally symmetrical process, indicated by a green line in the picture, involves during sub-intervals 3 and 5. In conclusion, at the end of the modulation period, the current is apparently back onto its original trajectory. But, even if that were the case, the initial unbalance of flying capacitor voltages would not be reduced or compensated for in any way. Therefore, the same non-ideal current trajectory will be observed in all the following modulation periods.

At this point, we can conclude that, if the flying capacitor voltages are somehow even minimally perturbed, the current ripple frequency multiplication effect is lost, and a current oscillation is activated that, in the absence of other, unaccounted for phenomena (e.g., some form of power dissipation) seems to repeat itself period after period. But then, if that were the case, we would no longer be able to neglect the effects of the tiny voltage variations over each flying capacitor that take place at each iteration of the process. Indeed, even if they were almost invisible in a single modulation period, they would accumulate over time and, eventually, determine a visible deviation from the steady-state value.

In conclusion, the careful analysis of

Figure 3 suggests that, if a perturbation is applied to the ideal flying capacitor charge distribution, a relatively slow transient is started that will develop over many modulation periods and can only be extinguished by the circuit lossy components, in the absence of which it is potentially capable of going on forever. The inner mechanism sustaining the process can only be described as a resonance between the inductor and the flying capacitors because both the inductor current and the capacitor voltages are involved and affected simultaneously. For the reasons explained above, this type of process cannot be described by a standard average circuit model; a different approach needs to be devised in order to properly analyze it.

2.5. A More Accurate Dynamic Model

The purpose of the model we are now going to discuss is exactly to account for the resonance process sketched in the discussion of

Figure 3 and to allow us to make some quantitative assessment of its characteristics.

We start by calculating, for each converter operating region, the time average in the modulation period of flying capacitors currents and , now explicitly considering their dependency on flying capacitor voltages. To keep the illustration simple, we can just consider a reduced-order state vector, defined as .

The dynamic equations describing the

small signal perturbations of the flying capacitor currents around the steady state can then be found, as usual, eliminating all the constant terms from the average current expression, using the a priori information about the converter steady-state operating point. The state equation system is finally found, that is,

where the

elements have to be determined for each circuit operation region, as usual indicated by subscript

. The procedure requires, in any case, lengthy calculations, even if the order of the circuit is just four. Therefore, after explaining it in one case, we present an automated model derivation procedure, applicable to higher-order circuits.

2.5.1. Analysis of the Circuit in Region

The average current on flying capacitor

,

, can be determined considering (

9), specifically matrix

, that indicates how

is connected in the circuit and for how long in any modulation period. From that, it is possible to write the following relation:

where the last equality is obtained by simplifying all the constant terms related to the steady-state operating point. The above result shows that

is not going to be zero in the presence of perturbations on the average values of the flying capacitor voltages because, as we have explained, these impact the capacitor charging and discharging phases, generating either charge accumulation or depletion. From (

18), we can conclude that the first row of matrix

is equal to

Similarly, by analyzing

, we can write the time average of

, which is given by the following relation:

The above equation proves that

which means that we can now re-write (

17) as

Without any real loss of generality, we can assume

, thus making

Based on (

22) and (

23), we can now see that, even in the above defined idealized conditions, the flying capacitor cells of the circuit in

Figure 1 tend to behave like an

ideal oscillator at frequency

. This result allows us to conclude that any small perturbation in the flying capacitor voltages generates a form of persistent oscillation, exactly as we deduced from

Figure 3. The persistence of the oscillation is infinite because the idealized converter model has zero damping, i.e., no power dissipation occurs.

In order to verify this finding, the circuit of

Figure 1 is simulated in the Matlab-Simulink

© v. 23.2 environment, using the PLECS

© v. 4.8.3 toolbox and considering, wherever applicable, the circuit parameters reported in

Table 1.

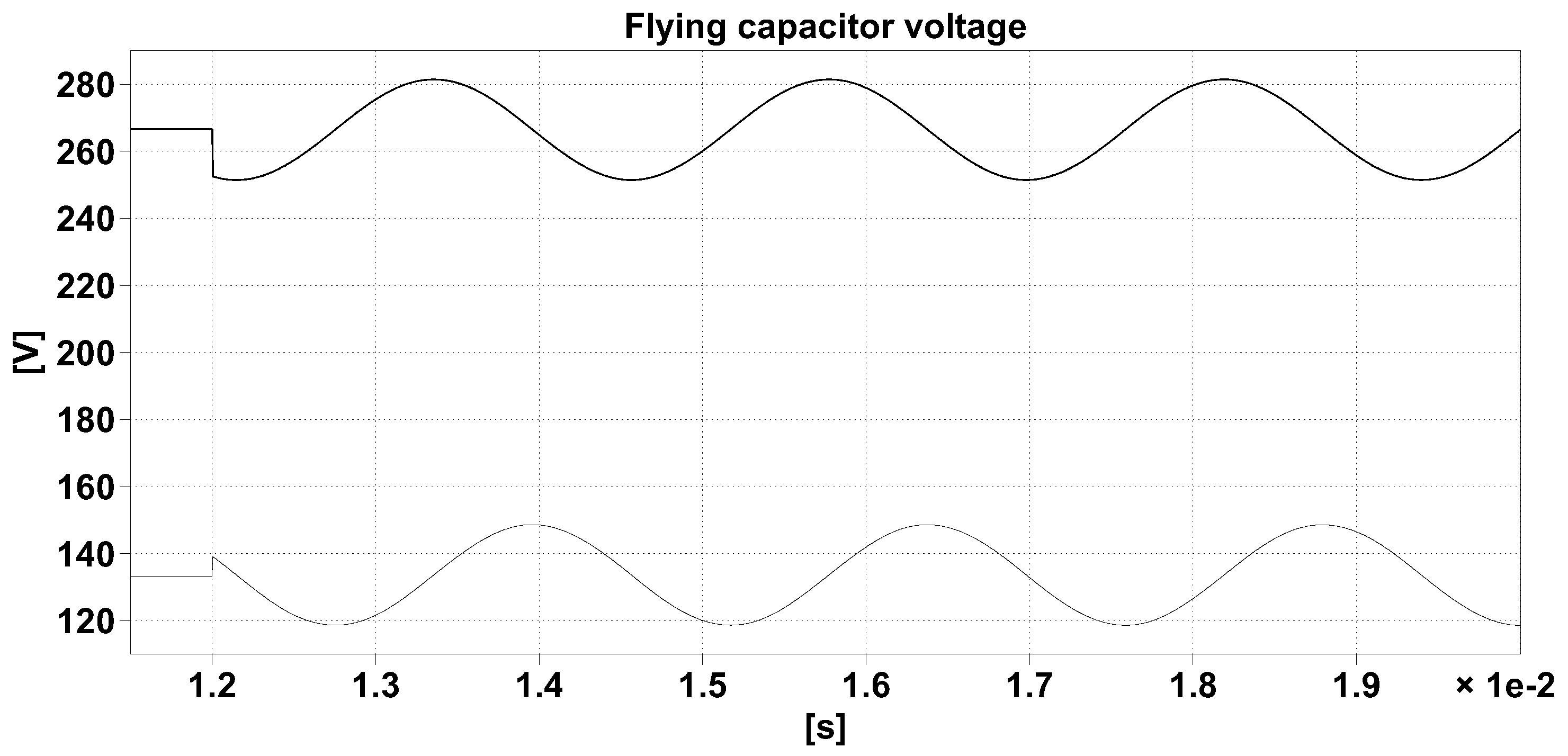

The simulation results are shown in

Figure 4, considering

and perturbation values of

on

and

on

, applied at

, when the circuit is operating in the steady state. For better readability, the switching ripple is removed from the traces using a moving average filter.

If we use (

23) to calculate the frequency of the oscillation when

as in

Figure 4, we find

, a value that is very close to the one resulting from the simulation plot of

Figure 4, that is

. It is also interesting to notice how the oscillating voltage waveforms correspond to sine and cosine terms as implied by the presence of purely imaginary, complex conjugate eigenvalues. Finally, it is important to point out that the average modeling approach is well posed and reliable, as the oscillation period of the dynamic phenomena under investigation is much longer than the averaging period. Now, we need to verify if the same conclusions can be drawn for region

and

.

2.5.2. Analysis of the Circuit in Region and

The procedure to derive the dynamic model of the flying capacitor cells in region

and

is basically the same as that followed for

. The only difference is that now we need to use matrices

and

, respectively, to identify the integration intervals and the polarity of the capacitor insertions. The system of differential Equation (

22) turns out to be identical to the previous one, except for the eigenvalue expression, which, for region

is found to be

while for region

it is equal to

again under the simplifying assumption of having identical flying capacitors values. It is interesting to observe that the three

functions, with

, once composed in the interval

, correspond to a function that is not only continuous but continuously differentiable as well.

In conclusion, the system exhibits essentially the same dynamic behavior of region

in

and

as well, only with different resonance frequencies.

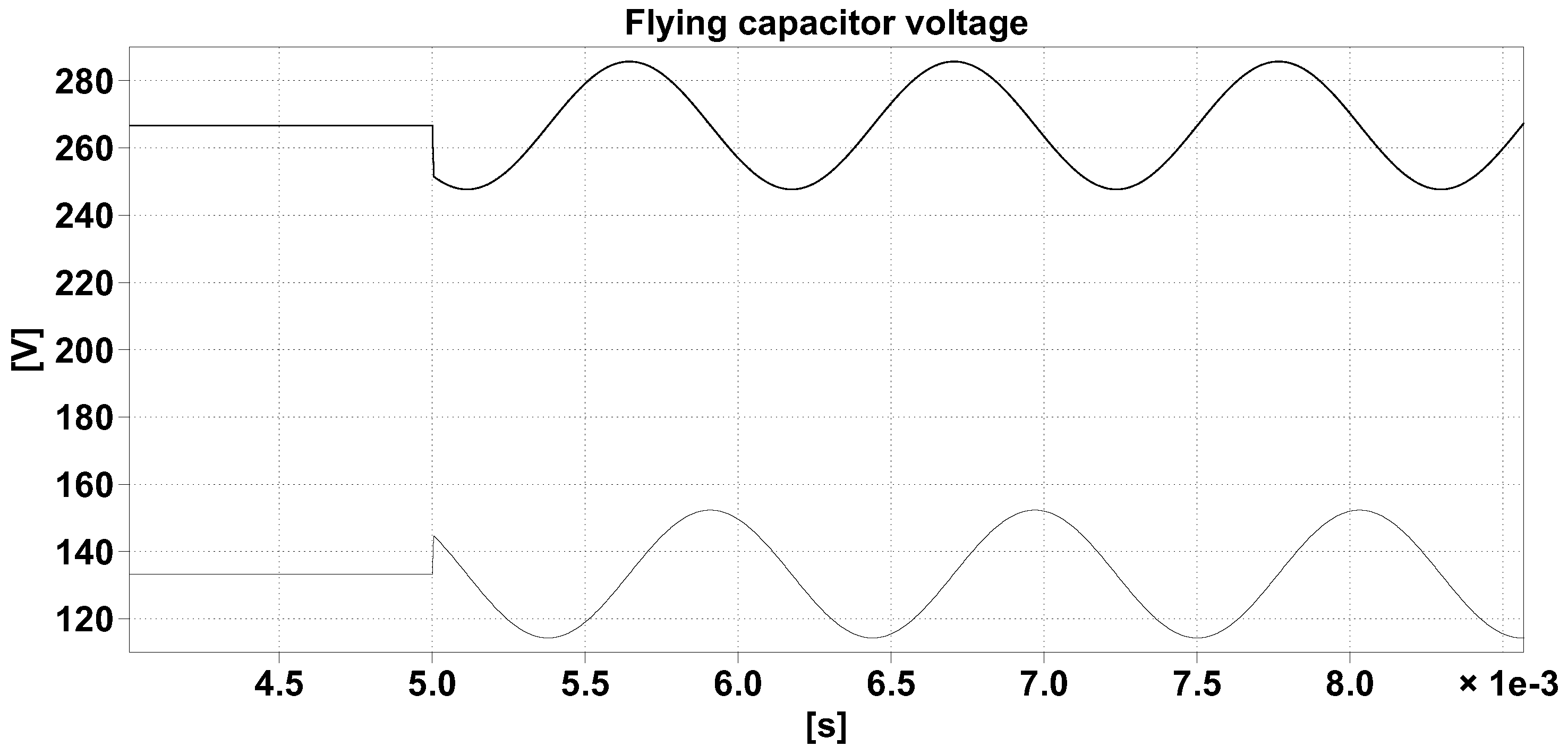

Figure 5 displays the results of test simulations with

and perturbation values of

on

and

on

, applied at

. The oscillation frequency predicted as

is equal to

, while the one found simulating the circuit is

. Finally,

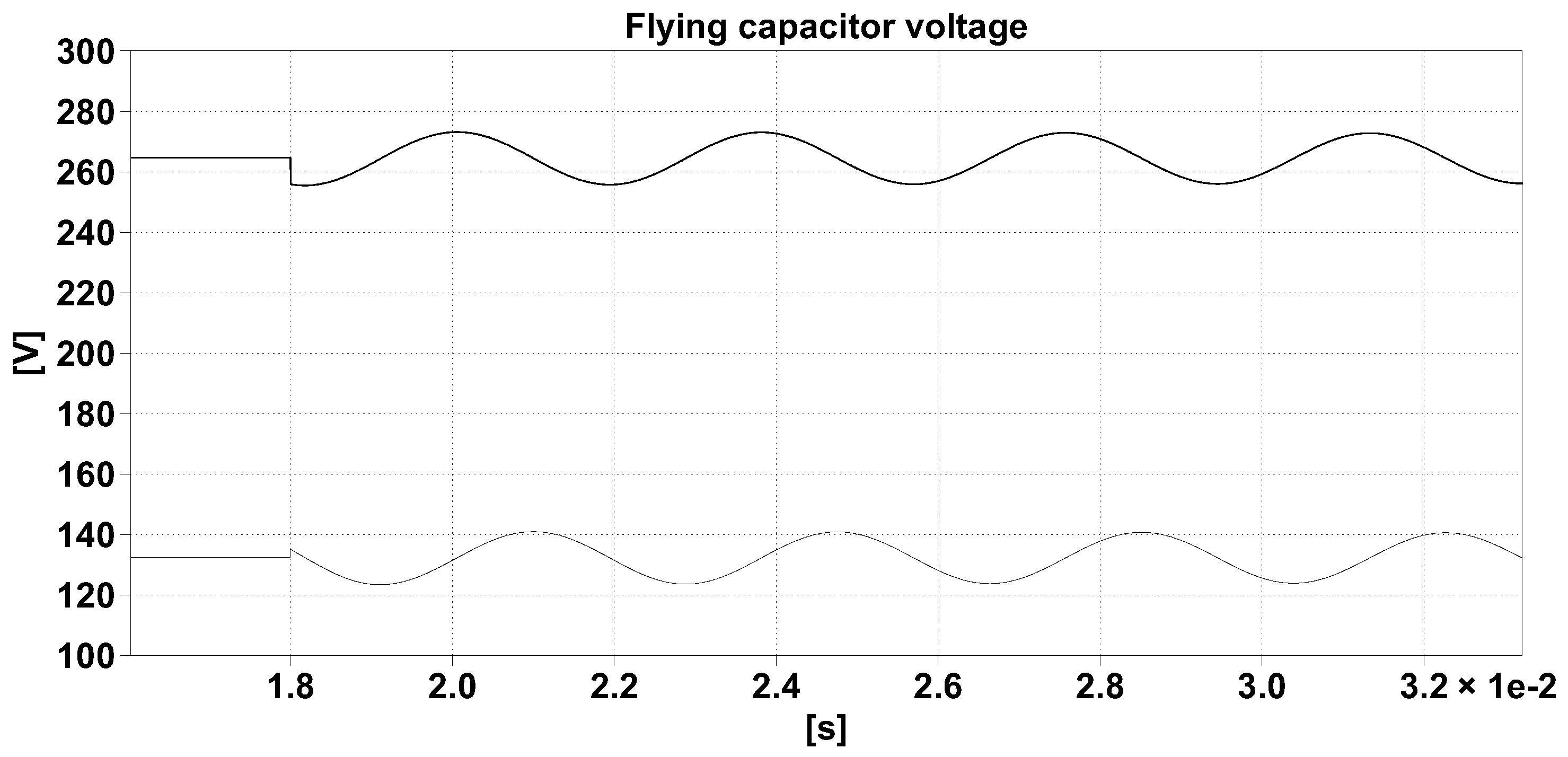

Figure 6 displays the results of the test simulations with

and perturbation values of

on

and

on

, applied at

. The oscillation frequency predicted as

is equal to

, while the one found simulating the circuit is

. The oscillation frequencies observed in the simulation only depend on the parameters appearing in (

23)–(

25); they are practically invariant for a different input voltage, average inductor current or perturbation sign, and amplitude.

2.6. Generalization of the Flying Capacitor Cell Dynamic Model

The above modeling approach can be likewise applied to higher-order converters. The main limitation is that the required pencil and paper calculations become more and more involved; in order to prevent errors, a Matlab

© script is implemented to automate the derivation of the system state matrix

in all converter operating regions and, in principle, for any value of

N. The key step is the automatic construction of the inductor current integrals in each sub-interval. Indeed, as can be seen in (

18) and (

20), the average flying capacitor current is obtained exactly by summing the inductor current integrals over each sub-interval, which, assuming the current to be piecewise linear, correspond to a trapezoidal integration process. The integration routine can therefore be built from (

9) as a sequence of repeated summations followed by multiplication between the resulting integration matrix and the time weighted capacitor connection matrix (

9). The adopted algorithm is reported in

Appendix A for better clarity. It is tested on values of

N ranging from 4 to 9, yielding consistent results.

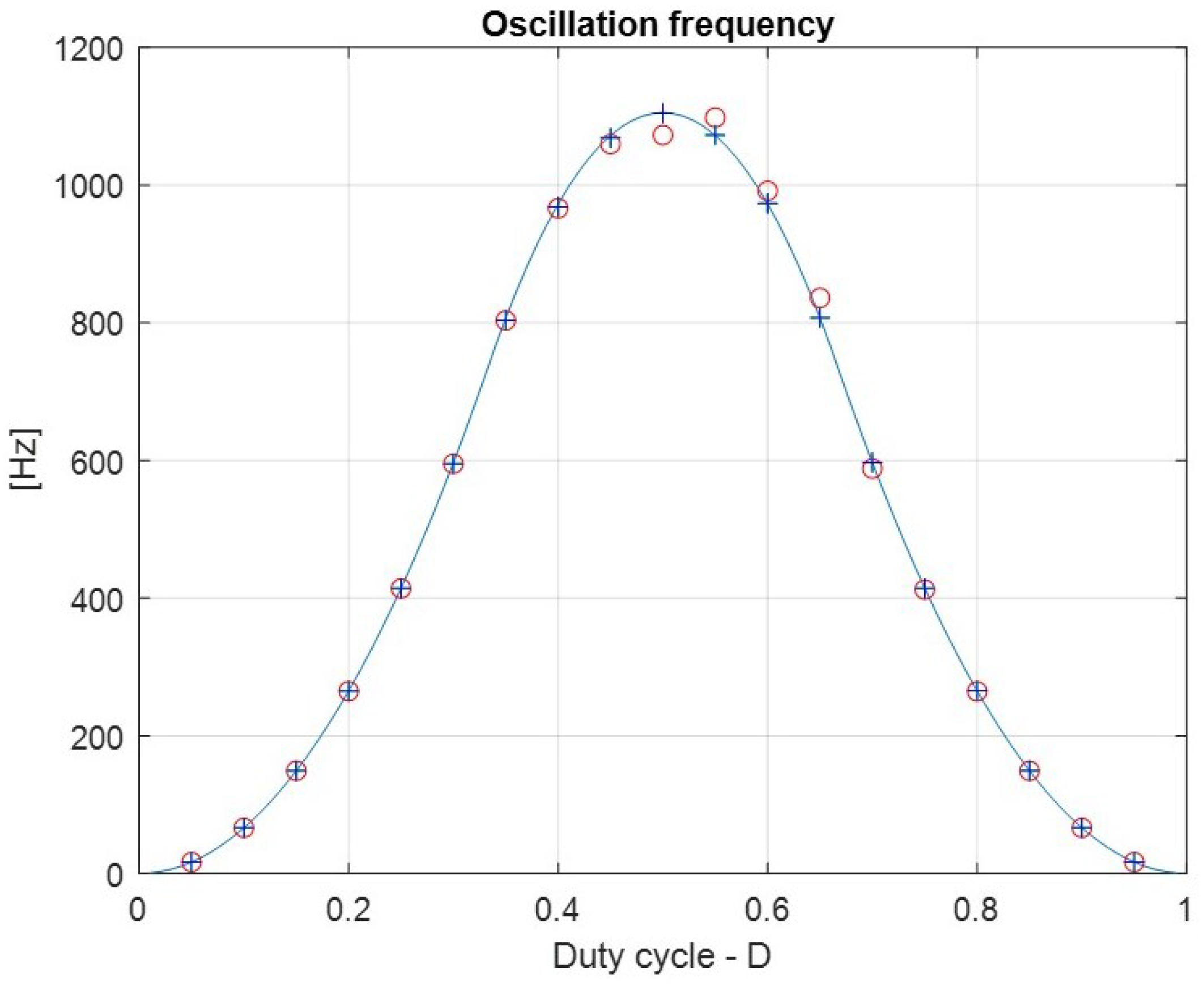

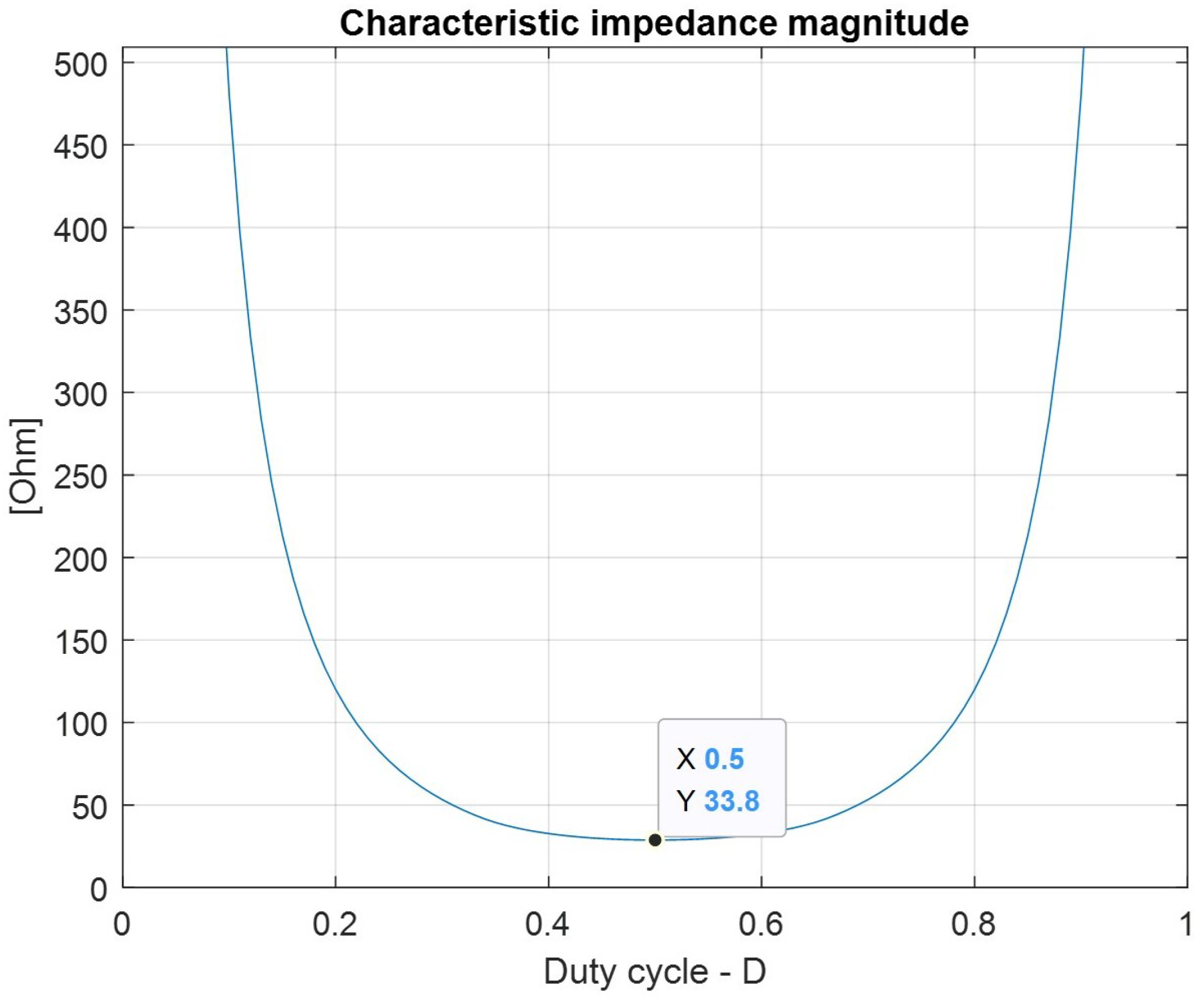

Thanks to this procedure, it is then possible to derive the expressions of the system eigenvalues in each operating region and to calculate, among other things, the magnitude plot shown in

Figure 7 also for higher values of

N. The figure is obtained comparing the analytically calculated eigenvalue magnitude with the oscillation frequency automatically extracted from simulation plots like those in

Figure 4,

Figure 5 and

Figure 6. This step is facilitated by the insertion of losses in the circuit, especially at duty cycles around 0.5, where strong beating occurs, complicating the automatic extraction of the oscillation frequency.

From the automated modeling, it is also possible to determine the magnitude of the characteristic impedance associated with the resonant poles in the circuit. This can be directly extrapolated from (

23)–(

25), and it is found to be given by

where

with

is the specific dependency from the duty cycle

D of expressions (

23)–(

25). The plot of

over the whole duty-cycle range is shown in

Figure 8.

As can be seen, a minimum value of about is found for . The plot confirms the observed tendency of the circuit to oscillate more widely and with longer transients when the duty cycle is around . It also allows to estimate the value of a possible damping resistor.

Considering the values of (

26), we see that placing in parallel to each flying capacitor an

AC coupled damping resistor of about

should be sufficient to visibly shorten the transient duration over the entire operating range. Given the observed typical amplitude of the oscillations, a small amount of additional losses is going to be generated, estimated at around

per cell (only during transients, of course).