TCAD Simulation of an E-Mode Heterojunction Bipolar p-FET with Imax > 240 mA/mm

Abstract

1. Introduction

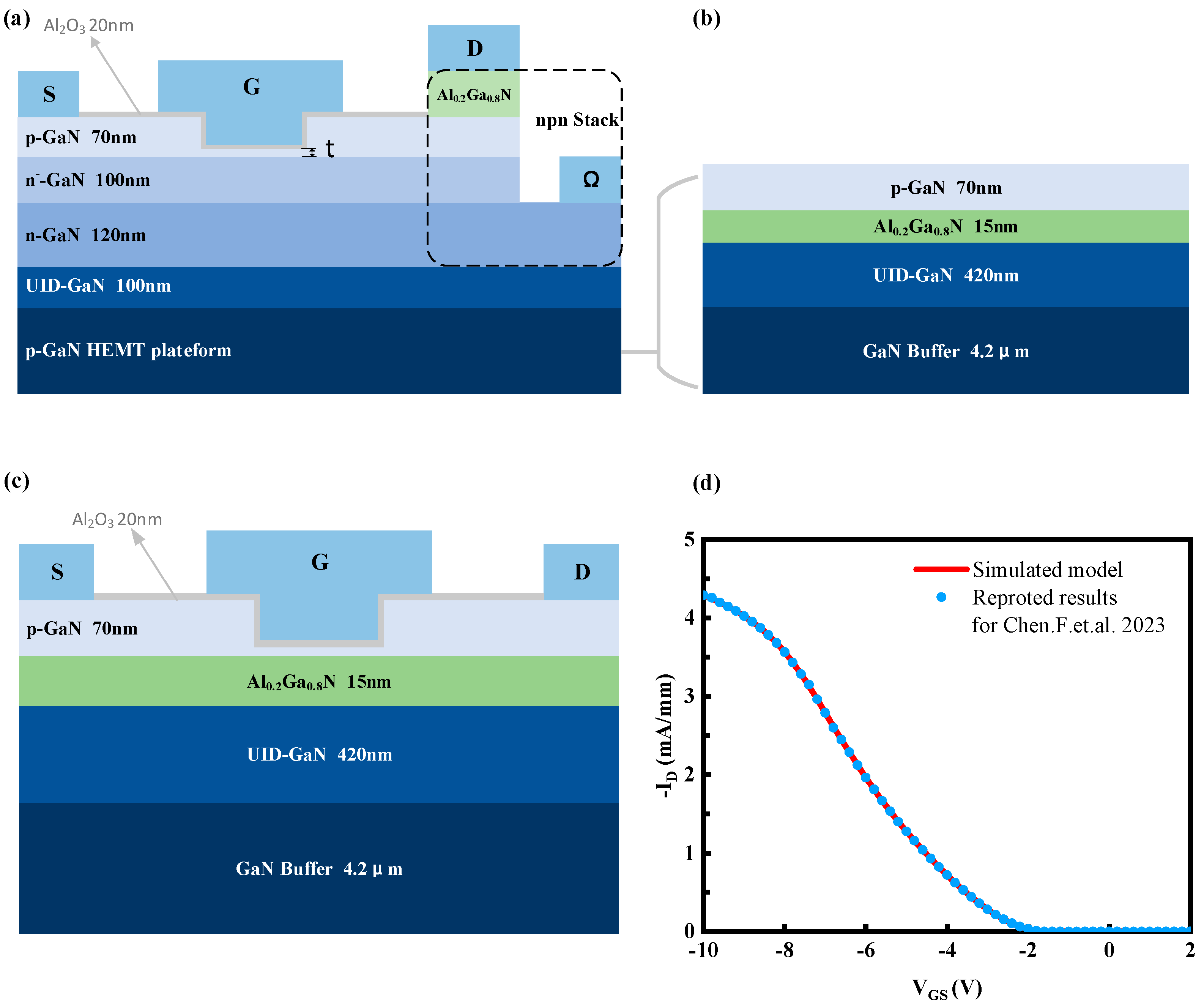

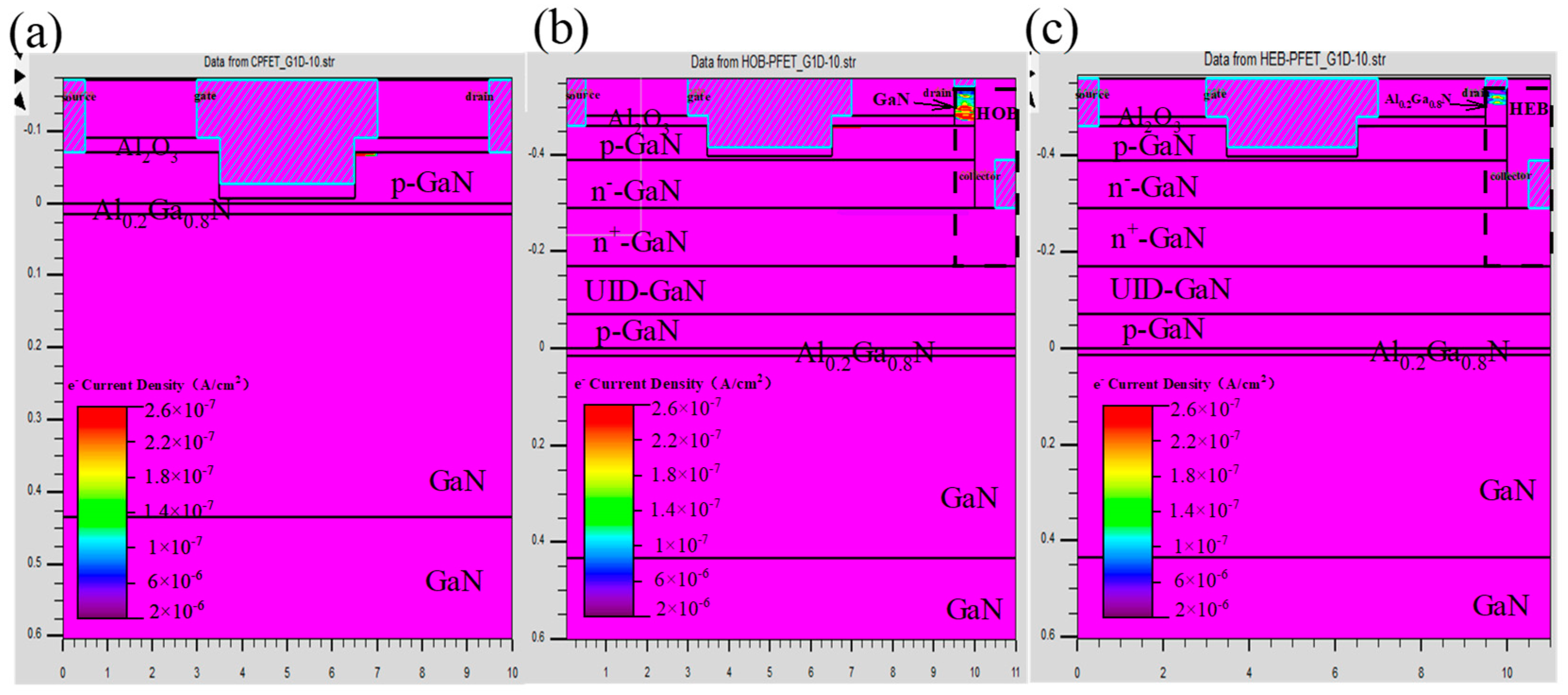

2. Device Structure and Simulation Models

3. Results and Discussion

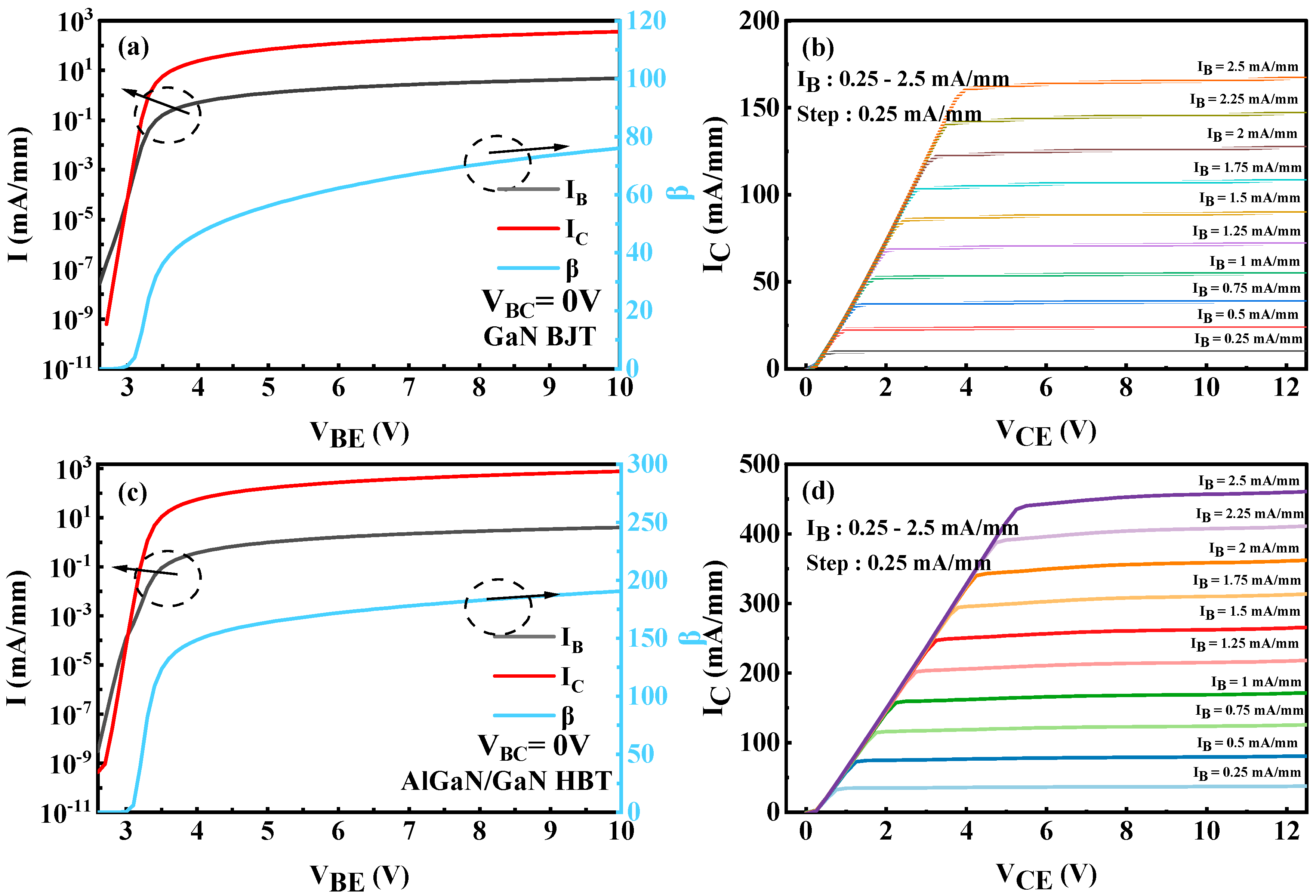

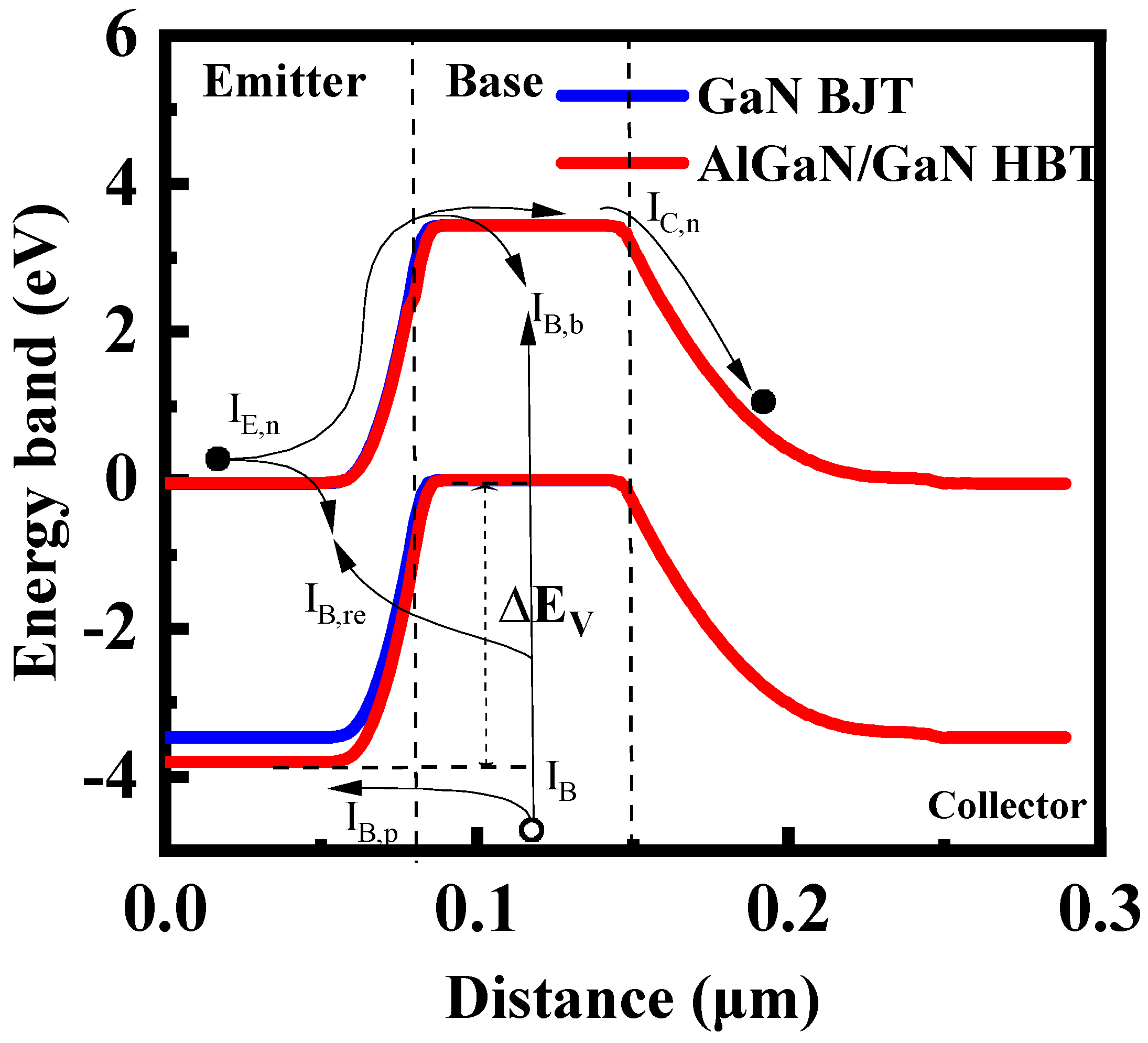

3.1. I–V Characteristics of GaN BJT and AlGaN/GaN HBT

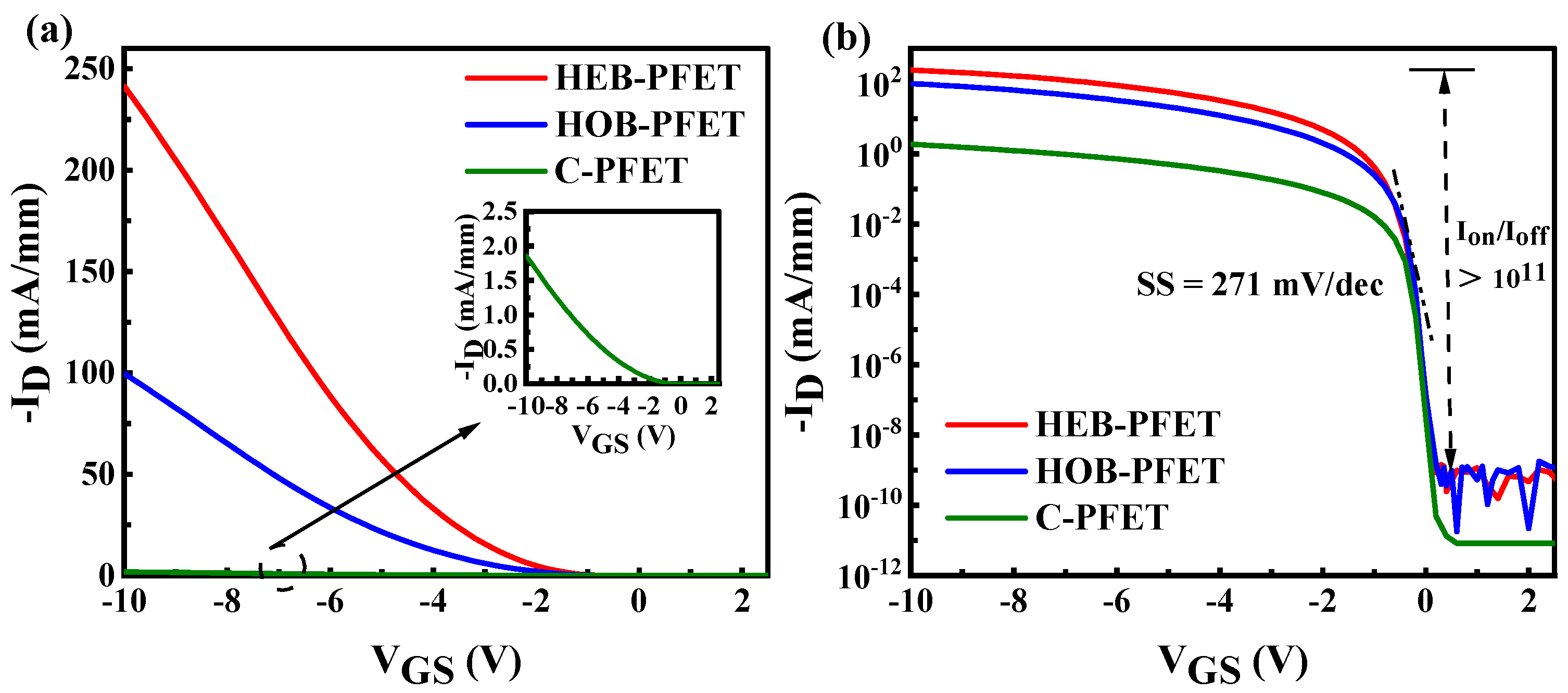

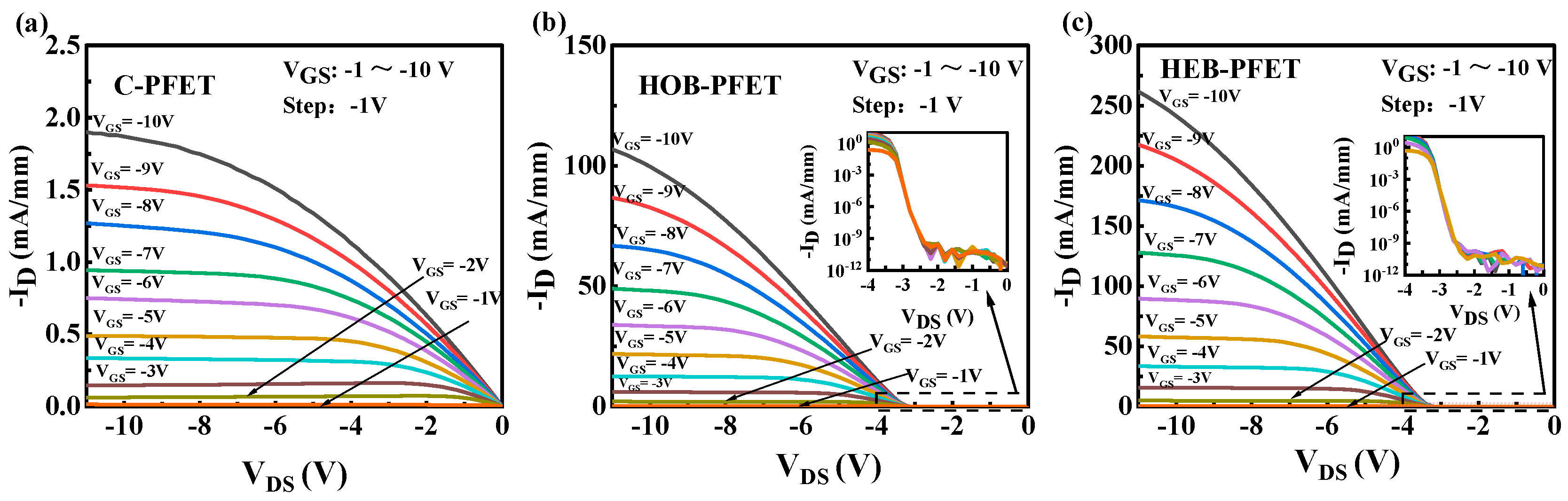

3.2. I–V Characteristics of the C-PFET, HOB-PFET and HEB-PFET

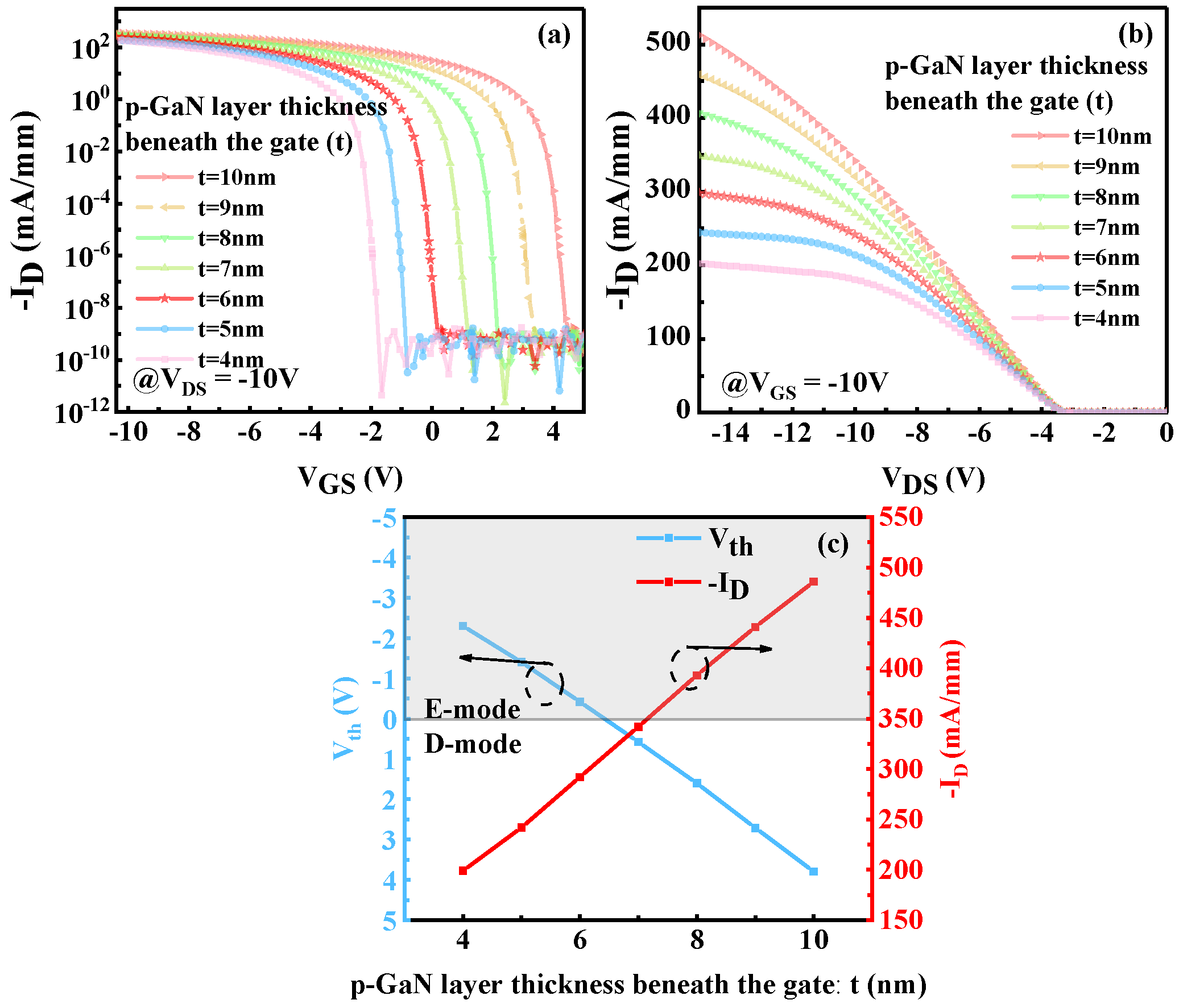

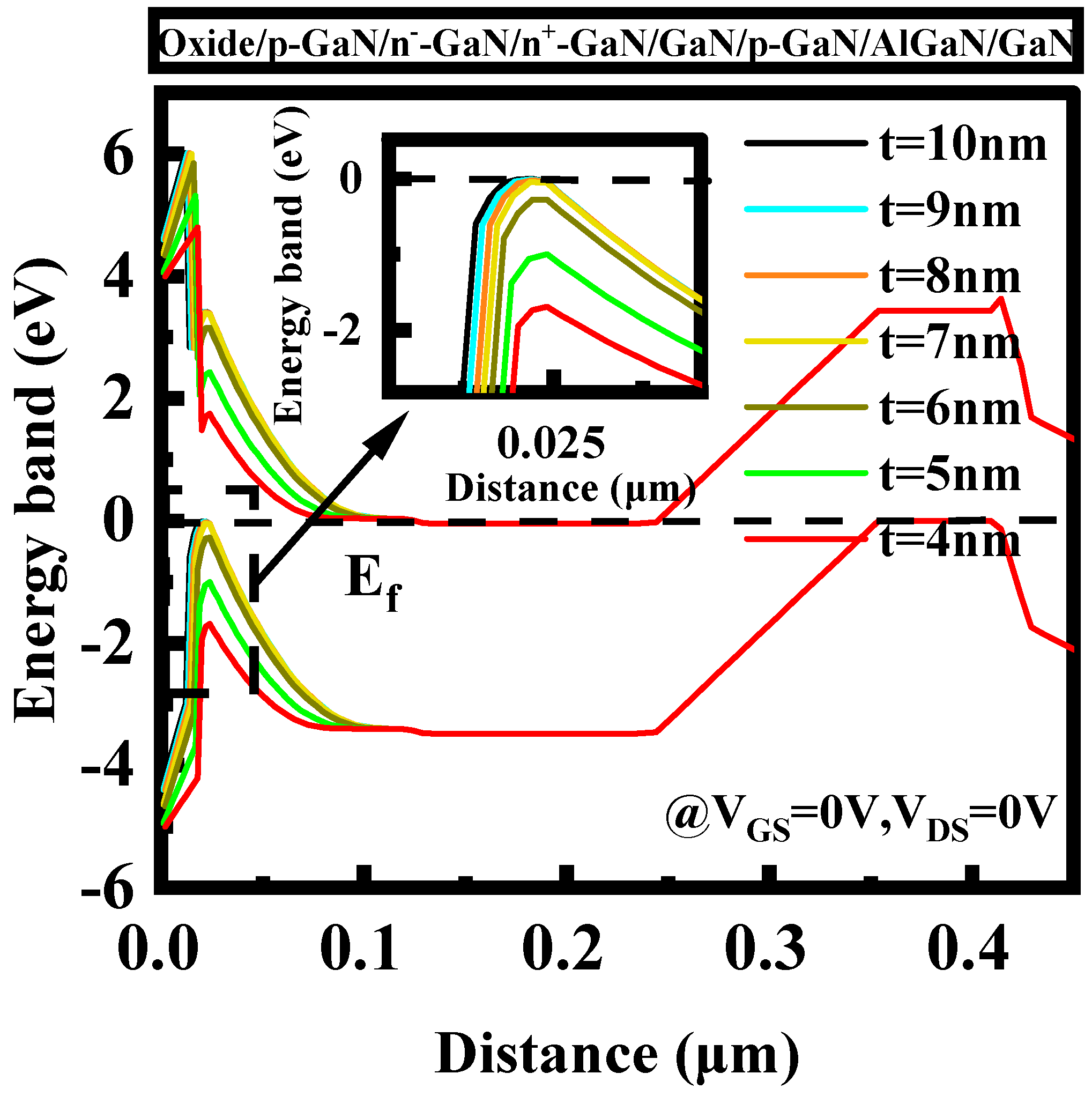

3.3. Optimization of the HEB-PFET

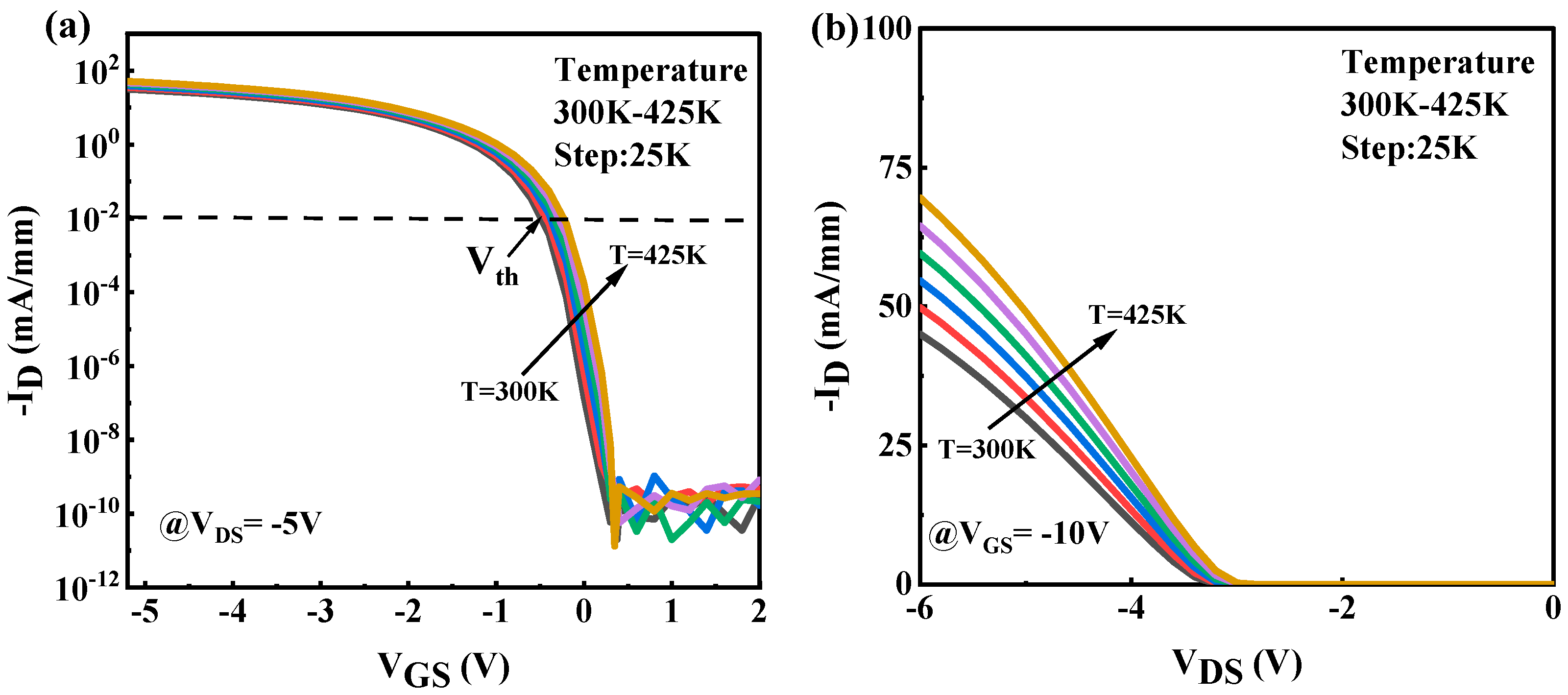

3.4. Temperature-Dependent Characteristics on the HEB-PFET

3.5. A Semi-Empirical Compact Model for ID of HEB-PFET

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si power technology: Devices and applications. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Zheng, Z.; Song, E.; Zhang, L.; Yang, S.; Xu, H.; Wong, R.K.-Y.; Wei, J.; Chen, K.J. Enhancement-Mode GaN p-Channel MOSFETs for Power Integration. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020. [Google Scholar]

- Chen, K.; Su, Y.; Ruan, J.; Cai, Y.; Zhu, L.; Zhang, B.; Zhou, Q. A novel E-mode GaN p-MOSFET featuring charge storage layer with high current density. J. Phys. D Appl. Phys. 2022, 55, 444007. [Google Scholar] [CrossRef]

- Chen, J.; Liu, Z.; Wang, H.; He, Y.; Zhu, X.; Ning, J.; Zhang, J.; Hao, Y. A GaN Complementary FET Inverter With Excellent Noise Margins Monolithically Integrated With Power Gate-Injection HEMTs. IEEE Trans. Electron Devices 2022, 69, 51–56. [Google Scholar] [CrossRef]

- Chen, F.; Qin, G.; Li, L.; Zhai, J.; Chen, Y. Simulation of E-mode p-channel GaN/AlGaN HFETs with hybrid AlGaN barrier layer. In Proceedings of the 2023 Cross Strait Radio Science and Wireless Technology Conference (CSRSWTC), Guilin, China, 10–13 November 2023. [Google Scholar]

- Nakajima, A.; Liu, P.; Ogura, M.; Makino, T.; Kakushima, K.; Nishizawa, S.-I.; Ohashi, H.; Yamasaki, S.; Iwai, H. Generation and transportation mechanisms for two-dimensional hole gases in GaN/AlGaN/GaN double heterostructures. J. Appl. Phys. 2014, 115, 153707. [Google Scholar] [CrossRef]

- Chowdhury, N.; Lemettinen, J.; Xie, Q.; Zhang, Y.; Rajput, N.S.; Xiang, P.; Cheng, K.; Suihkonen, S.; Then, H.W.; Palacios, T. p-Channel GaN Transistor Based on p-GaN/AlGaN/GaN on Si. IEEE Trans. Electron Devices 2019, 40, 1036–1039. [Google Scholar] [CrossRef]

- Bader, S.J.; Chaudhuri, R.; Nomoto, K.; Hickman, A.; Chen, Z.; Then, H.W.; Muller, D.A.; Xing, H.G.; Jena, D. Gate-recessed E-mode p-channel HFET with high on-current based on GaN/AlN 2D hole gas. IEEE Electron Device Lett. 2018, 39, 1848–1851. [Google Scholar] [CrossRef]

- Nomoto, K.; Chaudhuri, R.; Bader, S.J.; Li, L.; Hickman, A.; Huang, S.; Lee, H.; Maeda, T.; Then, H.W.; Radosavljevic, M.; et al. GaN/AlN p-channel HFETs with Imax > 420 mA/mm and ~20 GHz fT/fMAX. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020. [Google Scholar]

- Zimmermann, T.; Neuburger, M.; Kunze, M.; Daumiller, I.; Denisenko, A.; Dadgar, A.; Krost, A.; Kohn, E. P-channel InGaN-HFET structure based on polarization doping. IEEE Electron Device Lett. 2004, 25, 450–452. [Google Scholar] [CrossRef]

- Reuters, B.; Hahn, H.; Pooth, A.; Holländer, B.; Breuer, U.; Heuken, M.; Kalisch, H.; Vescan, A. Fabrication of p-channel heterostructure field effect transistors with polarization-induced two-dimensional hole gases at metal–polar GaN/AlInGaN interfaces. J. Phys. D Appl. Phys. 2014, 47, 175103. [Google Scholar] [CrossRef]

- Hahn, H.; Reuters, B.; Pooth, A.; Hollander, B.; Heuken, M.; Kalisch, H.; Vescan, A. p-Channel Enhancement and Depletion Mode GaN-Based HFETs With Quaternary Backbarriers. IEEE Trans. Electron Devices 2013, 60, 3005–3011. [Google Scholar] [CrossRef]

- Su, H.; Zhang, T.; Xu, S.; Tao, H.; Gao, Y.; Liu, X.; Xie, L.; Xiang, P.; Cheng, K.; Hao, Y.; et al. An energy-band modulated p-GaN/InGaN/AlN p-channel MESFET with high ION/IOFF ratio and steep subthreshold swing. Appl. Phys. Lett. 2024, 124, 162102. [Google Scholar] [CrossRef]

- Xing, Z.; Zhang, H.; Ye, Y.; Liang, F.; Yang, L.; Huang, Z.; Liang, K.; Wang, H.; Zhang, M.; Li, J.; et al. GaN-based E-mode p-FETs with polarization-doped p-type graded AlGaN channels. J. Phys. D Appl. Phys. 2024, 57, 385102. [Google Scholar] [CrossRef]

- Zheng, Z.; Song, W.; Zhang, L.; Yang, S.; Wei, J.; Chen, K.J. High ION and ION/IOFF Ratio Enhancement-Mode Buried p-Channel GaN MOSFETs on p-GaN Gate Power HEMT Platform. IEEE Electron Device Lett. 2020, 41, 26–29. [Google Scholar] [CrossRef]

- Chen, F.; Hao, R.; Yu, G.; Zhang, X.; Song, L.; Wang, J.; Cai, Y.; Zhang, B. Enhancement-mode n-GaN gate p-channel heterostructure field effect transistors based on GaN/AlGaN 2D hole gas. Appl. Phys. Lett. 2019, 115, 112103. [Google Scholar] [CrossRef]

- Kumar, A.; De Souza, M.M. Extending the bounds of performance in E-mode pchannel GaN MOSHFETs. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar]

- Yang, C.; Fu, H.; Peri, P.; Fu, K.; Zhou, J.; Montes, J.; Smith, D.J.; Zhao, Y. Enhancement-mode gate-recess-free gan-based p-channel heterojunction field-effect transistor with ultra-low subthreshold swing. IEEE Electron Device Lett. 2021, 42, 1128–1131. [Google Scholar] [CrossRef]

- Raj, A.; Krishna, A.; Romanczyk, B.; Keller, S.; Mishra, U.K. GaN/AlGaN Superlattice Based E-Mode Hole Channel FinFET With Schottky Gate. IEEE Electron Device Lett. 2023, 44, 9–12. [Google Scholar] [CrossRef]

- Tang, J.; Jiang, Z.; Wang, C.; Chen, J.; Chen, H.; Zhang, Y.; Zheng, Z.; Wang, X.; Ma, J.; Zhao, J.; et al. Bipolar p-FET with Enhanced Conduction Capability on E-mode GaN-on-Si HEMT Platform. In Proceedings of the 2023 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 9–13 December 2023. [Google Scholar]

- Zhou, J.; Do, H.-B.; De Souza, M.M. Impact of an Underlying 2DEG on the Performance of a p-Channel MOSFET in GaN. ACS Appl. Electron. Mater. 2023, 5, 3309–3315. [Google Scholar] [CrossRef]

- ‘Silvaco TCAD Atlas’, Version V3.44.1R. 2017. Available online: https://www.silvaco.com/products/tcad.html (accessed on 24 November 2017).

- Kumar, A.; De Souza, M.M. Modelling the threshold voltage of p-channel enhancement-mode GaN heterostructure field-effect transistors. IET Power Electron. 2018, 11, 675–680. [Google Scholar] [CrossRef]

- Albrecht, J.D.; Wang, R.P.; Ruden, P.P.; Farahmand, M.; Brennant, K.F. Electron transport characteristics of GaN for high temperature device modeling. J. Appl. Phys. 1998, 83, 4777–4781. [Google Scholar] [CrossRef]

- Wang, W.; Shervin, S.; Oh, S.K.; Chen, J.; Huai, Y.; Pouladi, S.; Kim, H.; Lee, S.-N.; Ryou, J.-H. Flexible AlGaInN/GaN Heterostructures for High-Hole-Mobility Transistors. IEEE Electron Device Lett. 2017, 38, 1086–1089. [Google Scholar] [CrossRef]

- Yan, S.; Zhou, Y.; Liu, J.; Zhong, Y.; Sun, X.; Chen, X.; Guo, X.; Li, Q.; Sun, Q.; Yang, H. GaN-Based Double-Heterojunction Bipolar Transistors with a Composition Graded p-InGaN Base. IEEE Trans. Electron Devices 2023, 70, 1613–1621. [Google Scholar] [CrossRef]

- Kumabe, T.; Watanabe, H.; Ando, Y.; Tanaka, A.; Nitta, S.; Honda, Y.; Amano, H. ‘Regrown-free’ fabrication of high-current-gain AlGaN/GaN heterojunctio bipolat transistor with N-p-n configuration. Appl. Phys. Exp. 2022, 15, 046506. [Google Scholar] [CrossRef]

- Zhang, L.; Wang, X.; Zeng, J.; Jia, L.; Cheng, Z.; Ai, Y.; Liu, Z.; Tan, W.; Zhang, Y. AlGaN/GaN Heterojunction Bipolar Transistors with High Current Gain and Low Specific ON-Resistance. IEEE Trans. Electron Devices 2022, 69, 6633–6636. [Google Scholar] [CrossRef]

- Wang, X.; Zhang, L.; He, J.; Cheng, Z.; Liu, Z.; Zhang, Y. Simulation and Comprehensive Analysis of AlGaN/GaN HBT for High Voltage and High Current. Electronics 2023, 12, 3590. [Google Scholar] [CrossRef]

- Van Zeghbroeck, B. Principles of Semiconductor Devices; Colarado University: Boulder, CO, USA, 2011. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, W.; Ge, M.; Li, Y.; Tan, S.; Yu, C.; Chen, D. TCAD Simulation of an E-Mode Heterojunction Bipolar p-FET with Imax > 240 mA/mm. Electronics 2024, 13, 4752. https://doi.org/10.3390/electronics13234752

Zhang W, Ge M, Li Y, Tan S, Yu C, Chen D. TCAD Simulation of an E-Mode Heterojunction Bipolar p-FET with Imax > 240 mA/mm. Electronics. 2024; 13(23):4752. https://doi.org/10.3390/electronics13234752

Chicago/Turabian StyleZhang, Wenqian, Mei Ge, Yi Li, Shuxin Tan, Chenhui Yu, and Dunjun Chen. 2024. "TCAD Simulation of an E-Mode Heterojunction Bipolar p-FET with Imax > 240 mA/mm" Electronics 13, no. 23: 4752. https://doi.org/10.3390/electronics13234752

APA StyleZhang, W., Ge, M., Li, Y., Tan, S., Yu, C., & Chen, D. (2024). TCAD Simulation of an E-Mode Heterojunction Bipolar p-FET with Imax > 240 mA/mm. Electronics, 13(23), 4752. https://doi.org/10.3390/electronics13234752