Considerations on the Development of High-Power Density Inverters for Highly Integrated Motor Drives

Abstract

1. Introduction

2. Materials and Methods

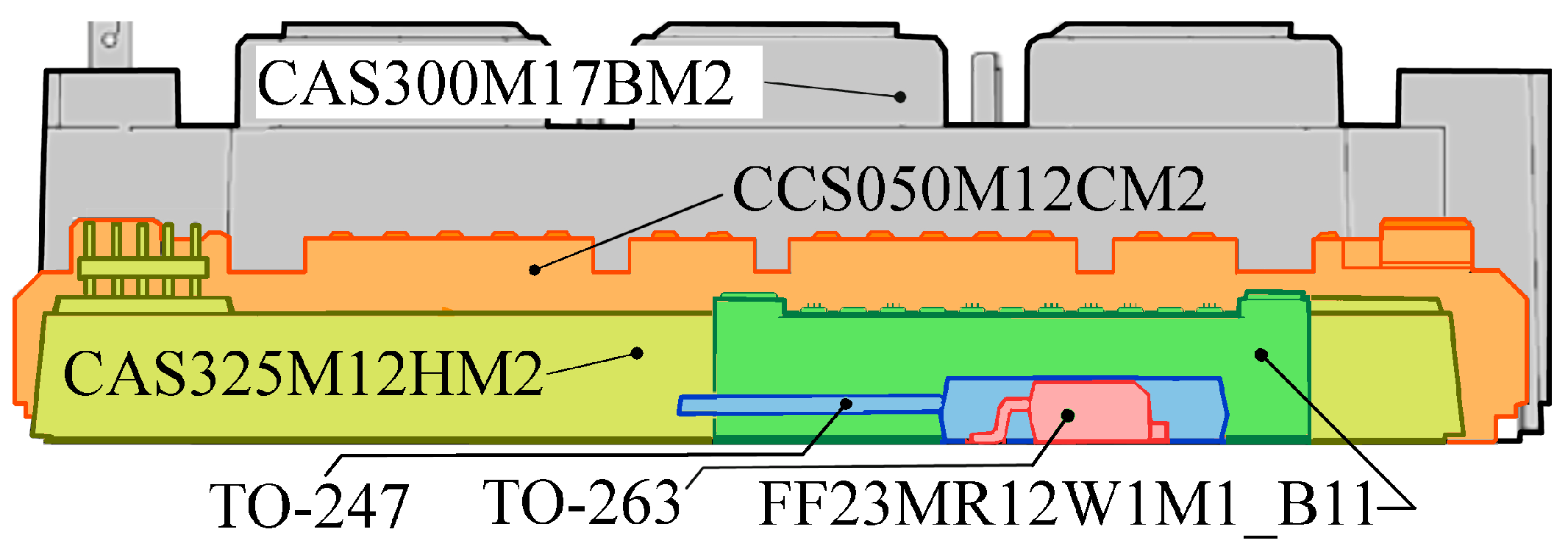

2.1. Power Switches

2.1.1. Discrete SiC MOSFETs

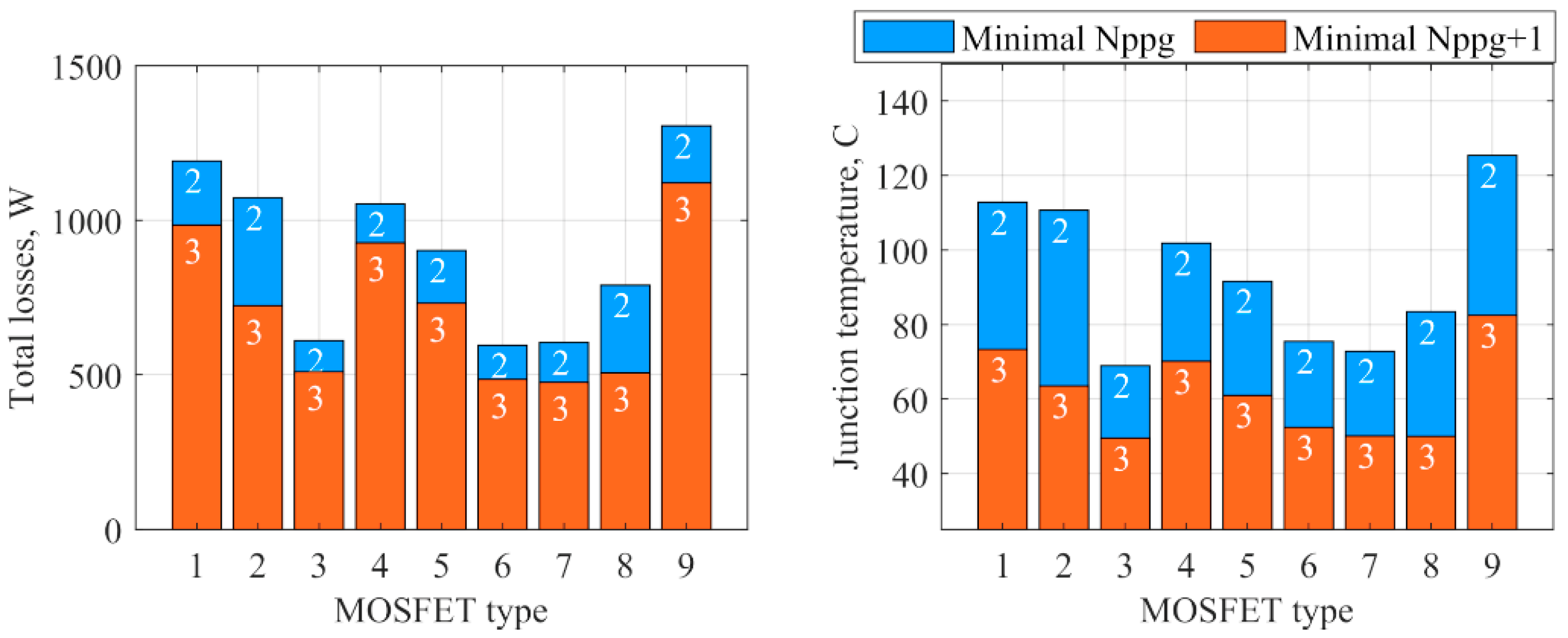

2.1.2. Power Modules

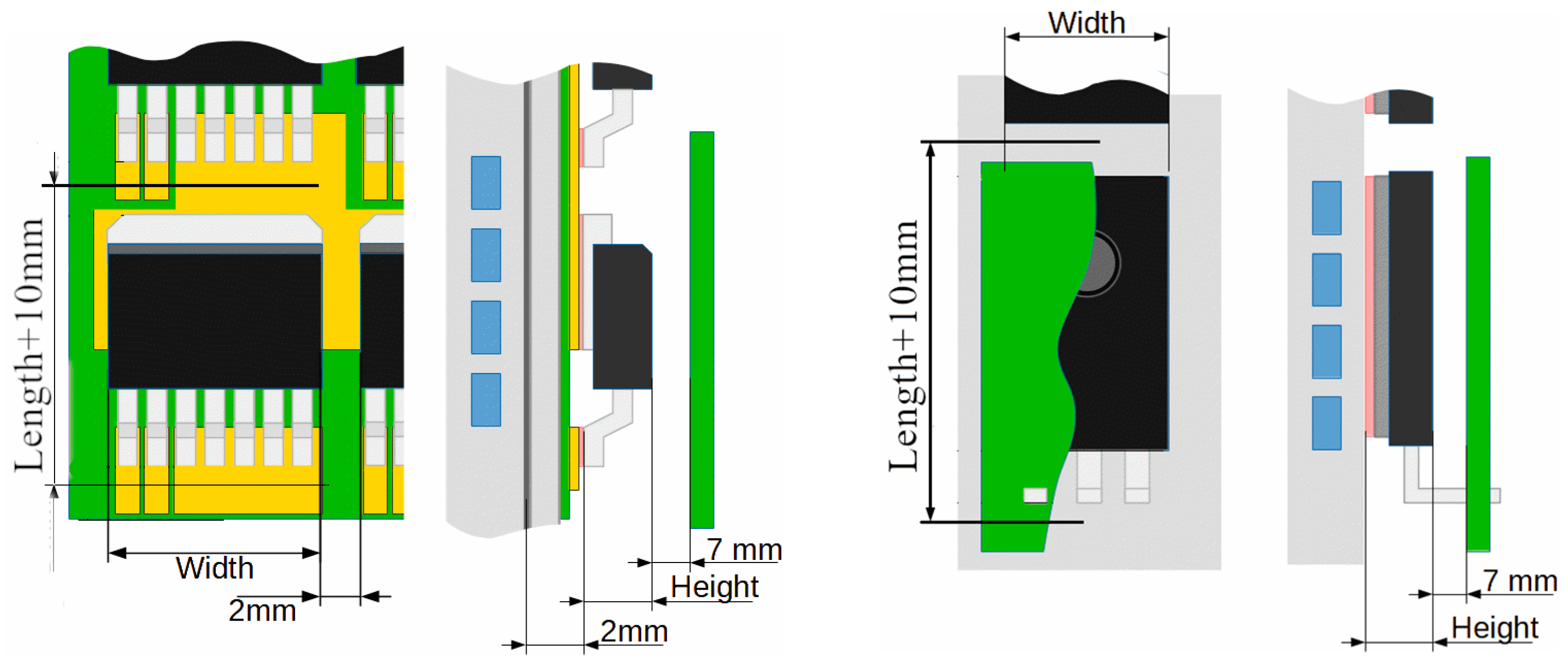

2.2. Losses Calculation and Thermal Model

- All parallel devices share phase drain current in equal parts;

- Dead-time-related losses (difference in conduction losses between diodes and MOSFETs) were not included;

- Diode partial current sharing in 3rd quadrant was not considered in this model; therefore, diode’s conduction losses were not included in calculations.

3. Performance Analysis

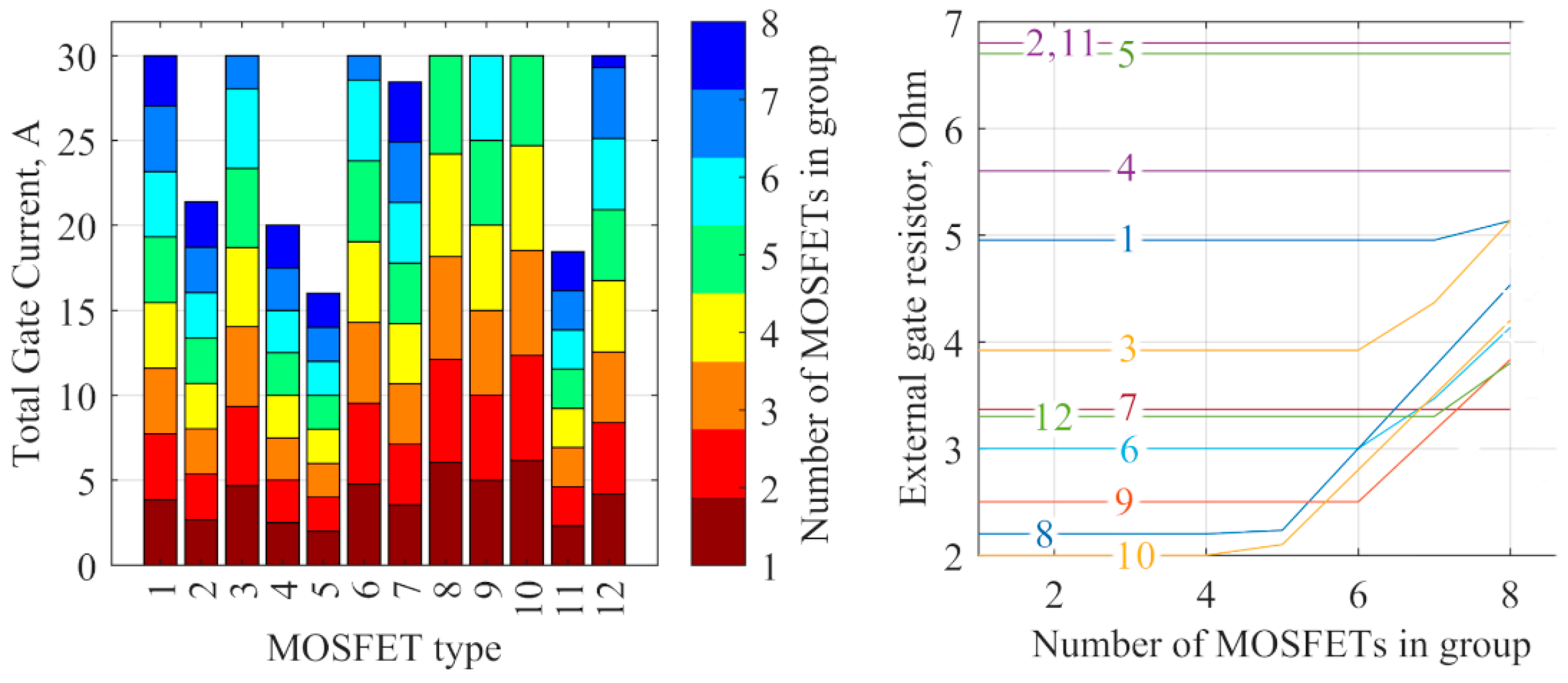

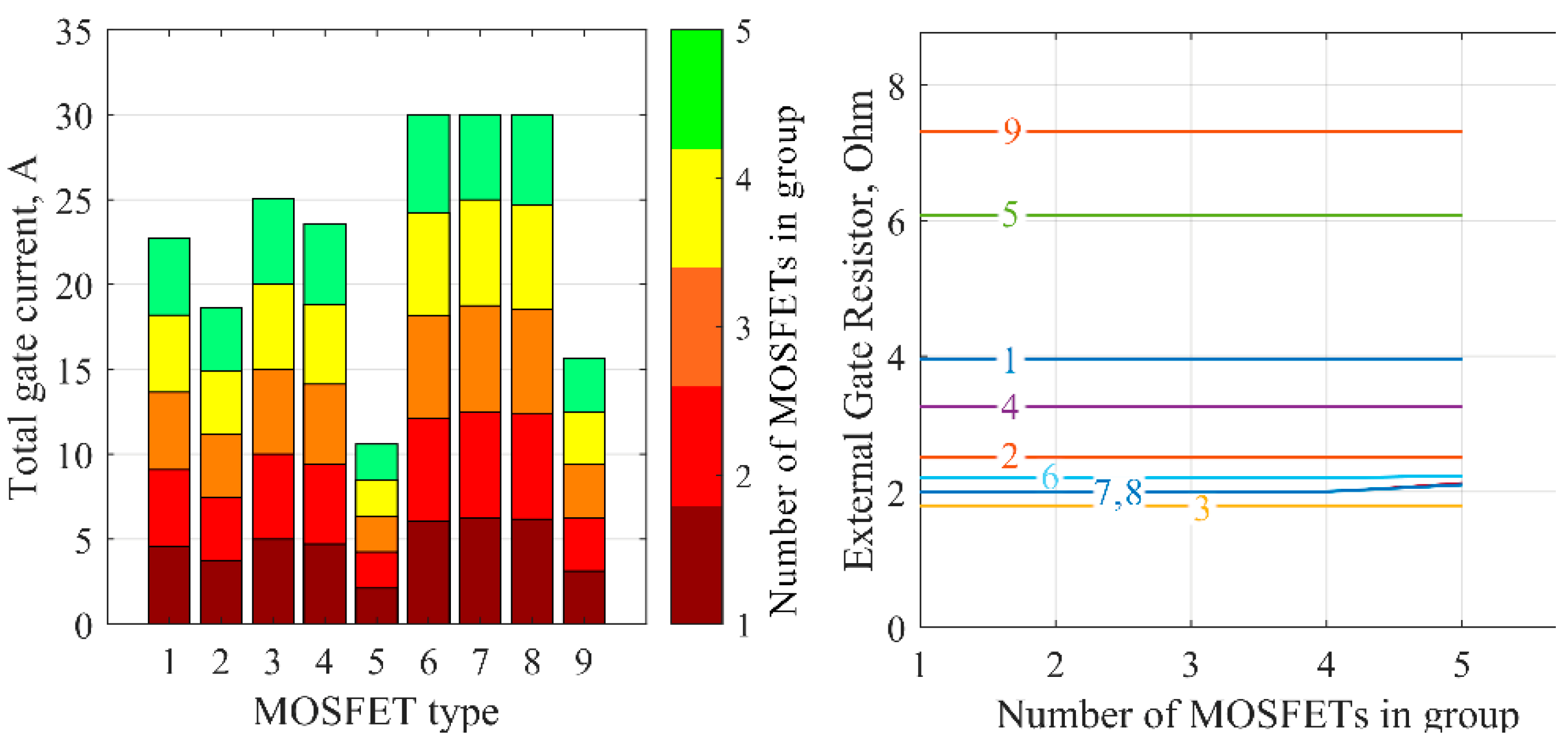

3.1. Effect of Gate Driver Current in Parallel Connection

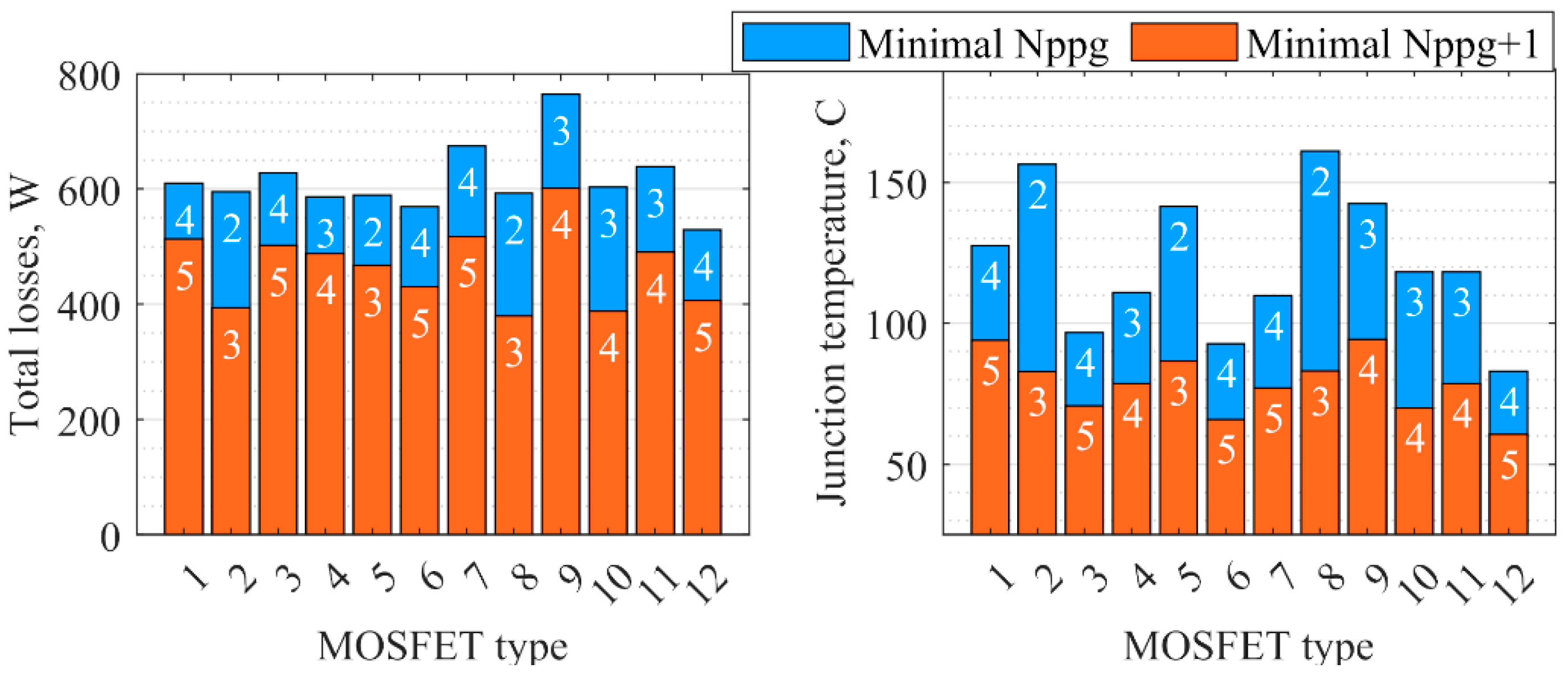

3.2. Case 1—Operation under Normal Ambient Temperature

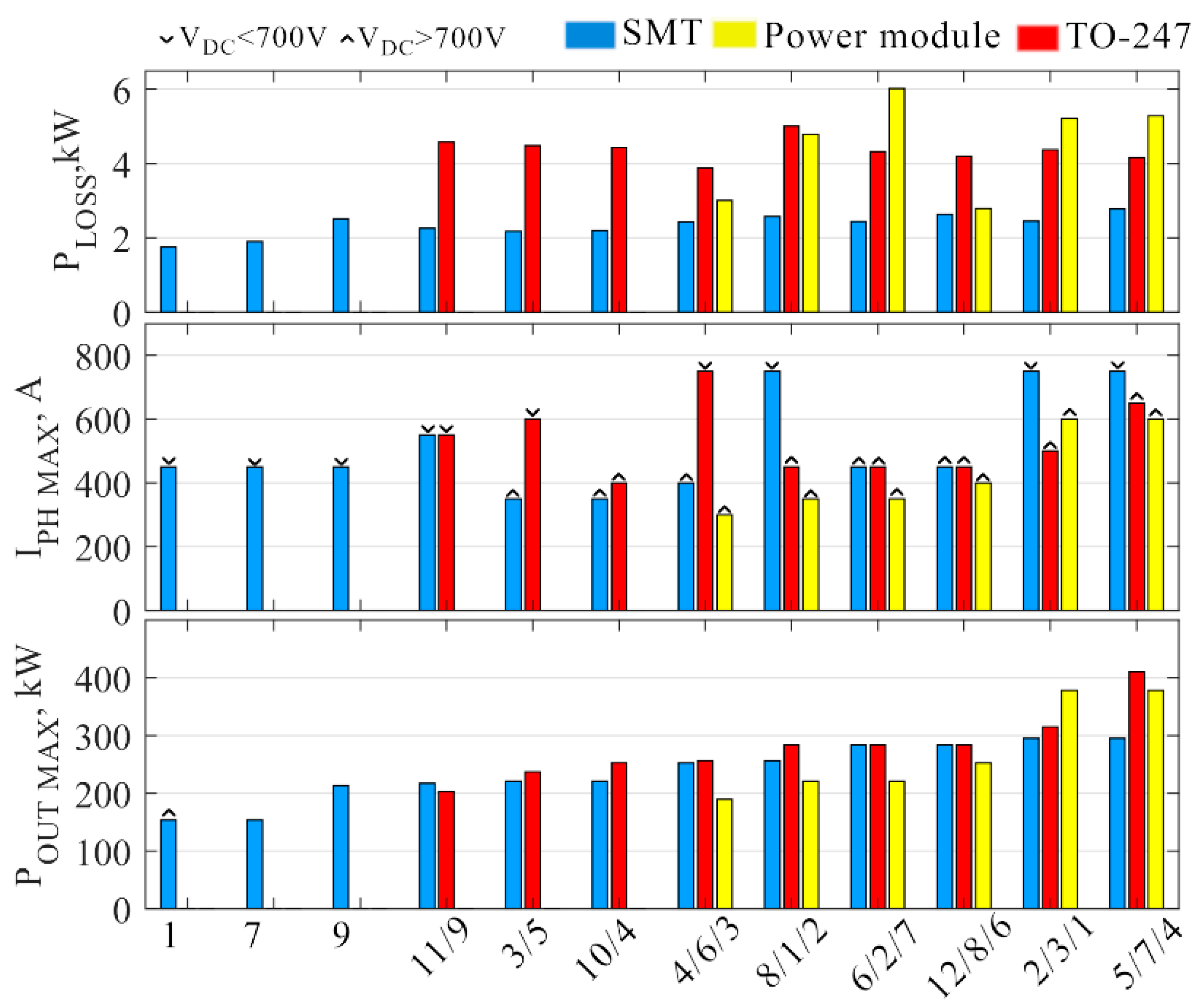

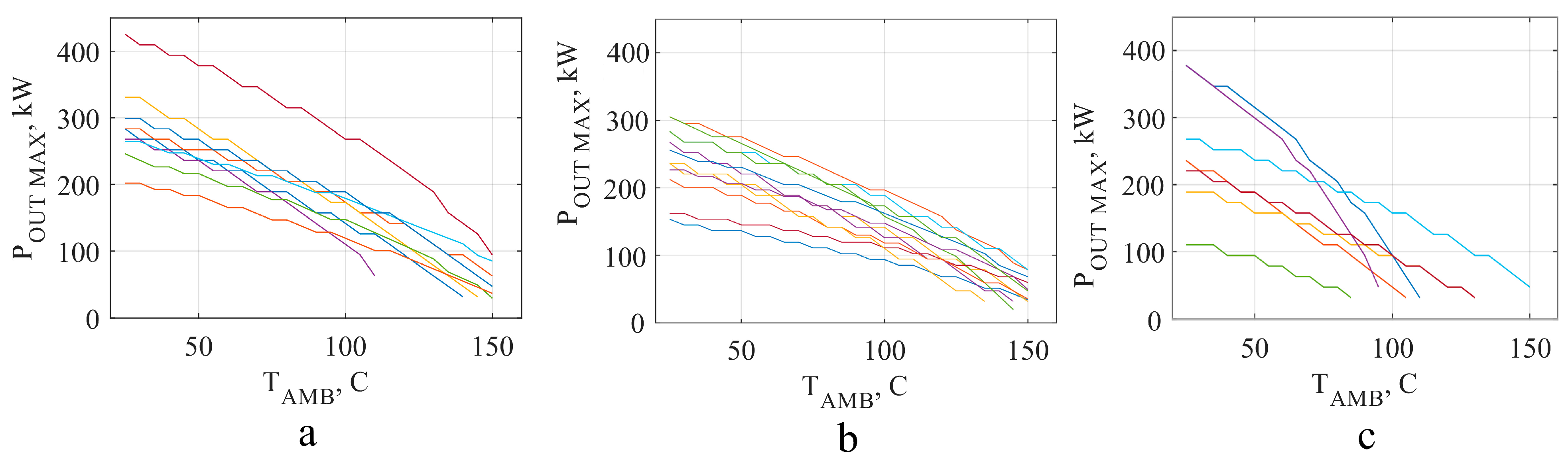

3.3. Case 1—Operation under High Ambient (Coolant) Temperature Tamb = 25–150 °C

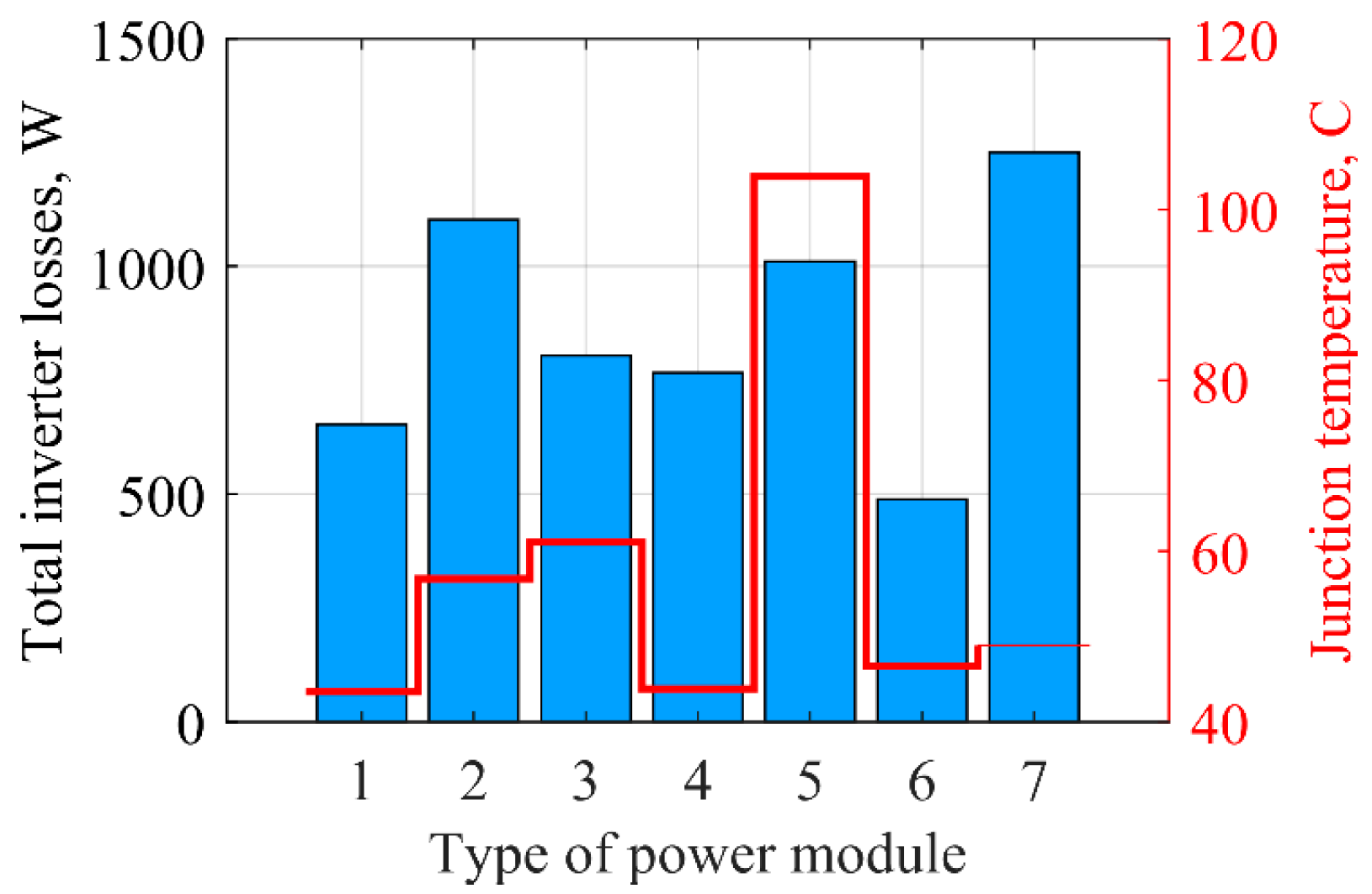

3.4. Maximum Possible Output Power and Individual DC-Link Voltage (Case 2)

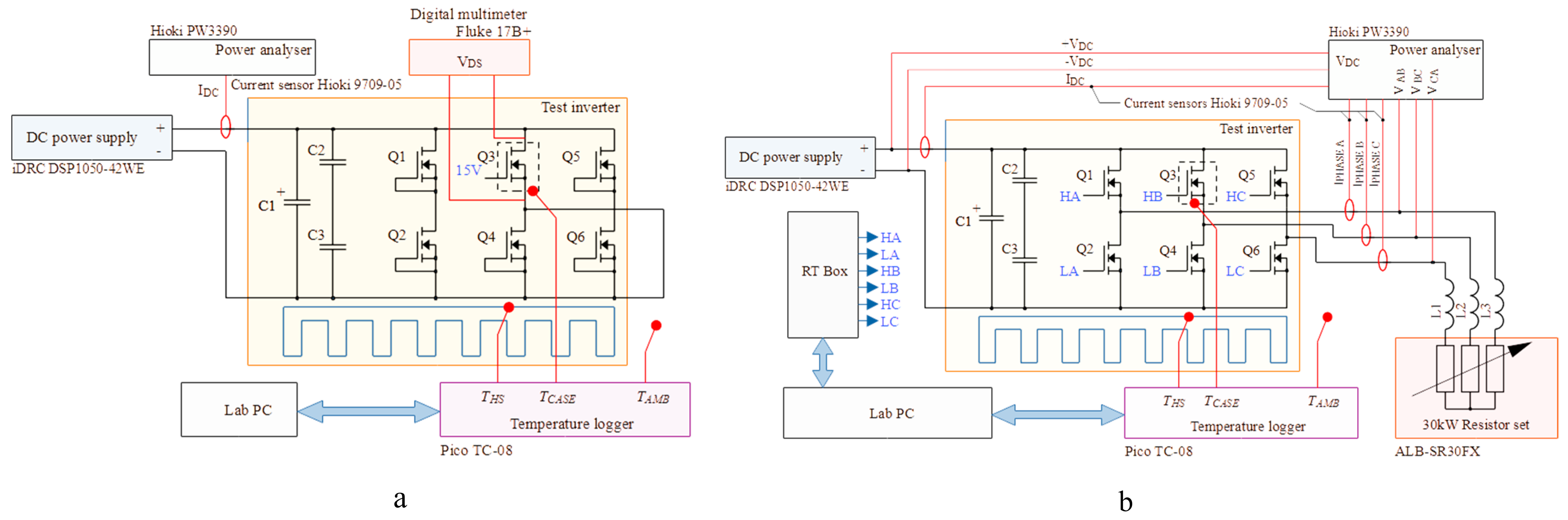

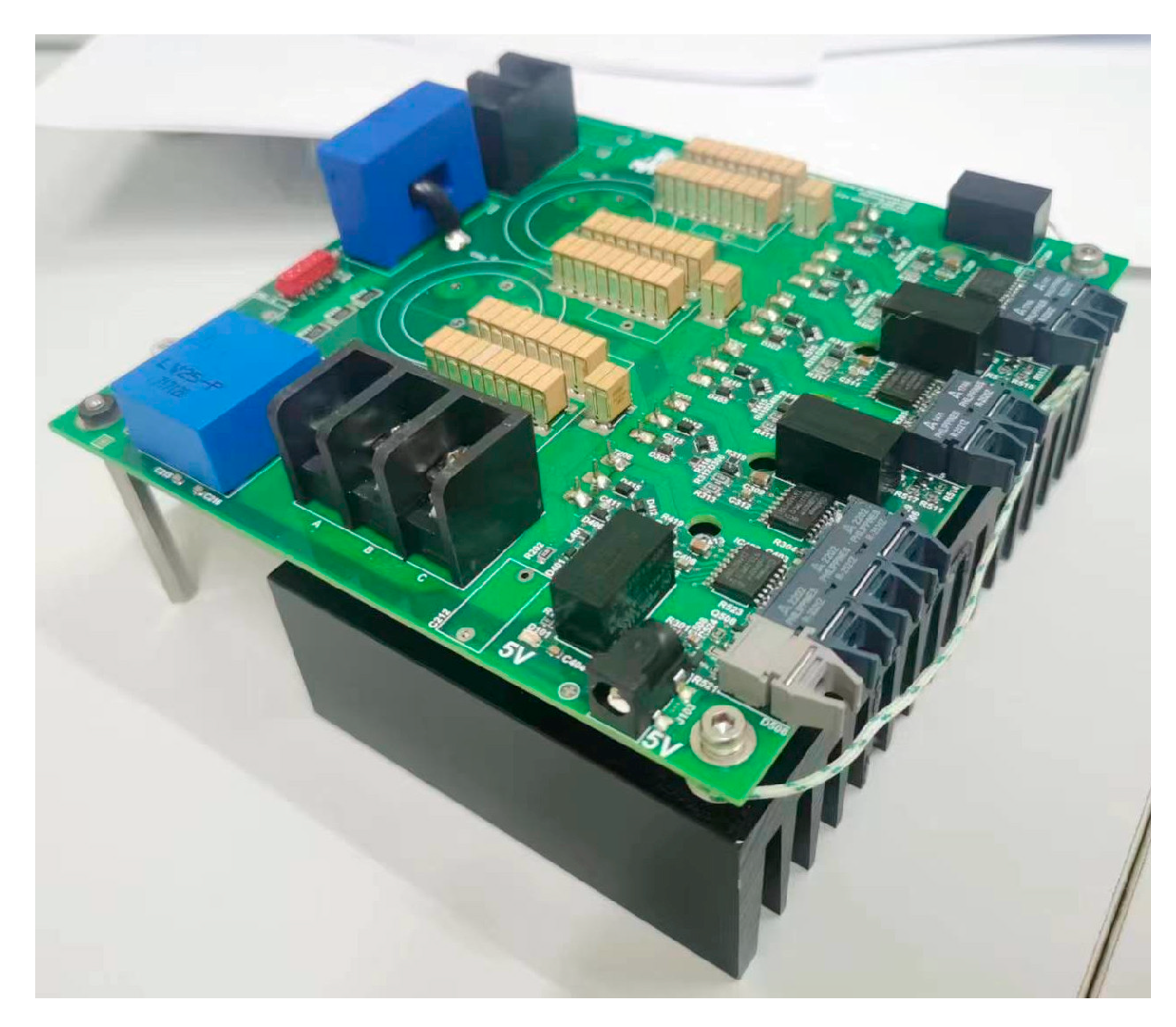

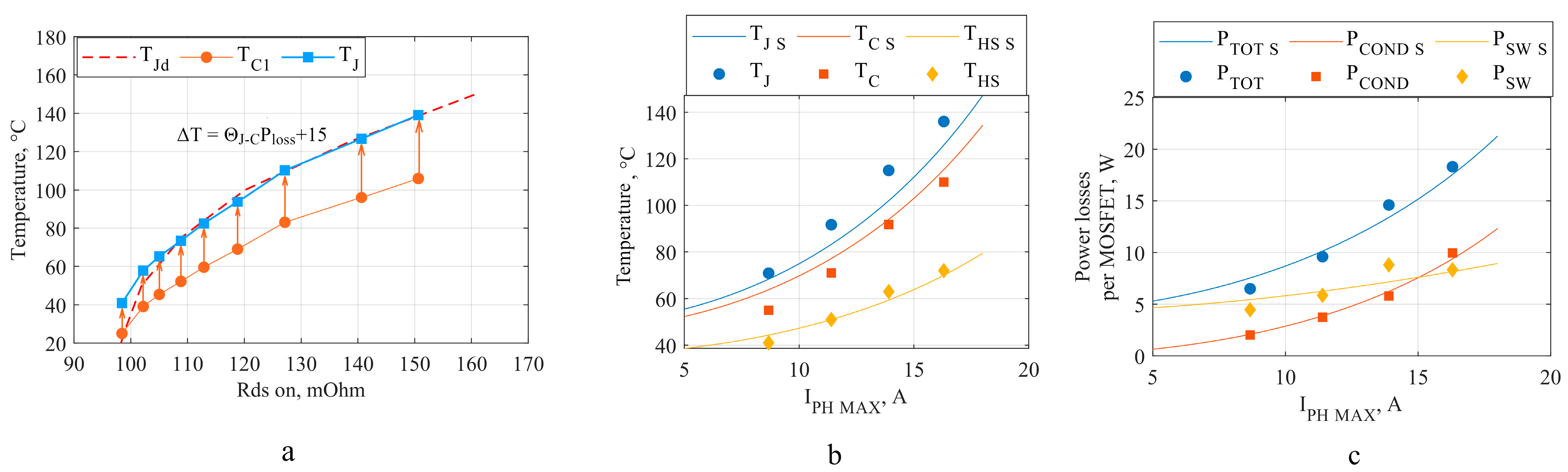

4. Experimental Validation

5. Discussion

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A

| № | Name | Year | , mOhm | , A | , V | , K/W | , nF | , °C | , mm2 | Package | Manufacturer |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | SCTL90N65G2V | 12.2020 | 18 | 40 | 650 | 0.16 | 3.38 | 175 | 31.7 | PowerFLAT 8 × 8 | ST Microelectronics |

| 2 | SCT011H75G3AG | 3.2022 | 11 | 110 | 750 | 0.23 | 3.83 | 175 | 53.3 | H2PAK-7 | |

| 3 | SCTH70N120G2V-7 | 8.2020 | 21 | 90 | 1200 | 0.32 | 3.54 | 175 | 53.3 | H2PAK-7 | |

| 4 | AIMBG120R010M1 | 3.2023 | 8.7 | 205 | 1200 | 0.13 | 5.7 | 175 | 49.3 | PG-TO263-7-HV-ND5.8 | Infineon |

| 5 | UJ4SC075005L8S | 2.2023 | 0.005 | 120 | 750 | 0.1 | 8.37 | 175 | 76.6 | MO-229 | UnitedSiC |

| 6 | G3R30MT12J | 11.2020 | 30 | 85 | 1200 | 0.3 | 3.86 | 175 | 44.6 | TO-263-7 | GeneSiC |

| 7 | NTBL045N065SC1 | 4.2022 | 33 | 73 | 650 | 0.43 | 1.87 | 175 | 55.2 | H−PSOF8L | Onsemi |

| 8 | NVBG015N065SC1 | 2.2021 | 12 | 145 | 650 | 0.3 | 4.69 | 175 | 52.0 | D2PAK−7L | |

| 9 | NVBG020N090SC1 | 8.2019 | 20 | 112 | 650 | 0.31 | 4.42 | 175 | 52.0 | D2PAK−7L | |

| 10 | NTBG014N120M3P | 4.2022 | 16 | 104 | 900 | 0.33 | 6.31 | 175 | 52.0 | D2PAK−7L | |

| 11 | SCT4013DW7 | 3.2023 | 13 | 98 | 750 | 0.43 | 5.48 | 175 | 65.5 | D2PAK-7 | Rohm |

| 12 | SCT4018KW7 | 3.2023 | 18 | 75 | 1200 | 0.43 | 4.53 | 175 | 65.5 | D2PAK-7 |

| № | Name | Manufacturer | Year | , mOhm | , A | , V | , nF | , µC | , K/W | , °C | Package |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | P3M12017K4 | PNJ semi | 6.2021 | 17 | 151 | 1200 | 7.29 | 0.27 | 0.19 | 175 | TO-247-4 |

| 2 | C3M0016120K | Wolfspeed | 4.2019 | 16 | 115 | 1200 | 6 | 0.21 | 0.27 | 175 | TO-247-4 |

| 3 | IMZA120R007M1H | INFINEON | 1.2022 | 7 | 225 | 1200 | 9.17 | 0.22 | 0.15 | 175 | PG-TO247-4-STD-T3.7 |

| 4 | UF3SC120009K4S | UnitedSiC | 12.2019 | 8.6 | 120 | 1200 | 8.5 | 0.23 | 0.15 | 175 | TO 247-4L |

| 5 | UJ4SC075006K4S | 7.2021 | 5.9 | 120 | 750 | 8.31 | 0.16 | 0.16 | 175 | TO 247-4L | |

| 6 | NTH4l015N065SC1-D | onsemi | 4.2021 | 12 | 142 | 650 | 4.79 | 0.28 | 0.3 | 175 | TO 247-4L |

| 7 | G3R20MT12K | GeneSiC | 1.2023 | 12 | 155 | 1200 | 9.34 | 0.28 | 0.26 | 175 | TO 247-4 |

| 8 | NTH4L014N120M3P | onsemi | 1.2023 | 14 | 127 | 1200 | 6.23 | 0.33 | 0.17 | 175 | TO 247-4L |

| 9 | MSC015SMA070B4 | Microsemi | 15 | 140 | 700 | 4.5 | 0.22 | 0.22 | 175 | TO 247-4L | |

| * | C2M0080120D | Wolfspeed | 2013 | 80 | 36 | 1200 | 1.13 | 0.071 | 0.6 | 150 | TO 247 |

| № | Name | Year | , mOhm | , A | , V | , nF | , µC | , K/W | °C | Length, mm | Width, mm | Height, mm | Weight, g |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | CAB760M12HM3 | 2.2022 | 1.33 | 1015 | 1200 | 79.4 | 2.72 | 0.068 | 175 | 110 | 65 | 12.2 | 180 |

| 2 | CAB530M12BM3 | 3.2021 | 2.67 | 719 | 1200 | 39.6 | 1.36 | 0.065 | 175 | 103.5 | 60.4 | 30 | 300 |

| 3 | CAB450M12XM3 | 6.2019 | 2.6 | 450 | 1200 | 38.0 | 1.33 | 0.11 | 175 | 80 | 53 | 15.75 | 175 |

| 4 | MSCSM120AM02CT6LIAG | 1.2020 | 2.1 | 947 | 1200 | 36.2 | 2.78 | 0.04 | 175 | 108 | 62 | 16 | 320 |

| 5 | MSCSM120TAM11CTPAG 1 | 1.2020 | 8.4 | 251 | 1200 | 9 | 0.69 | 0.144 | 175 | 108 | 62 | 11.5 | 250 |

| 6 | GE12047CCA3 | 5.2021 | 3.1 | 475 | 1200 | 29.3 | 1.25 | 0.1 | 175 | 89.3 | 51.2 | 14.8 | 120 |

| 7 | FS03MR12A6MA1B 1,2 | 4.2021 | 2.75 | 400 | 1200 | 42.6 | 1.32 | 0.115 | 150 | 154 | 95 | 19 | 720 |

| Component Function | Component Type | Notes |

|---|---|---|

| Input capacitor | MAL205737101E3 (100 µF 450 V), 2 in parallel B58035U5106M001 (10 µF 500 V), 3 in parallel | C1 C2, C3 |

| Gate drivers | 1ED3320MC12N | |

| Power switches | C2M0080120D | Q1–Q6 |

| DC-link snubber capacitor | B32714H1205K000 (2 µF 1100 V) and B58035U9504M (500n 900 V) in parallel |

References

- Wheeler, P.; Bozhko, S. The More Electric Aircraft: Technology and challenges. IEEE Electrif. Mag. 2014, 2, 6–12. [Google Scholar] [CrossRef]

- Calzo, G.; Vakil, G.; Mecrow, B.C.; Lambert, S.; Cox, T.; Gerada, C.; Johnson, M.; Abebe, R. Integrated Motor Drives: State of the Art and Future Trends. IET Electr. Power Appl. 2016, 10, 757–771. [Google Scholar] [CrossRef]

- Renken, F. High temperature electronics for future hybrid drive systems. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–7. [Google Scholar]

- Lee, W.; Li, S.; Han, D.; Sarlioglu, B.; Minav, T.A.; Pietola, M. Achieving high-performance electrified actuation system with integrated motor drive and wide bandgap power electronics. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.10. [Google Scholar]

- Chen, C.; Chen, Y.; Li, Y.; Huang, Z.; Liu, T.; Kang, Y. An SiC-Based Half-Bridge Module With an Improved Hybrid Packaging Method for High Power Density Applications. IEEE Trans. Ind. Electron. 2017, 64, 8980–8991. [Google Scholar] [CrossRef]

- Wang, R.; Boroyevich, D.; Ning, P.; Wang, Z.; Wang, F.; Mattavelli, P.; Ngo, K.D.T.; Rajashekara, K. A High-Temperature SiC Three-Phase AC–DC Converter Design for > 100/spl deg/C Ambient Temperature. IEEE Trans. Power Electron. 2013, 28, 555–572. [Google Scholar] [CrossRef]

- Ning, P.; Zhang, D.; Lai, R.; Jiang, D.; Wang, F.; Boroyevich, D.; Burgos, R.; Karimi, K.; Immanuel, V.D.; Solodovnik, E.V. High-Temperature Hardware: Development of a 10-kW High-Temperature, High-Power-Density Three-Phase ac-dc-ac SiC Converter. IEEE Ind. Electron. Mag. 2013, 7, 6–17. [Google Scholar] [CrossRef]

- Olejniczak, K.; Flint, T.; Simco, D.; Storkov, S.; McGee, B.; Shaw, R.; Passmore, B.; George, K.; Curbow, A.; McNutt, T. A compact 110 kVA, 140 °C ambient, 105 °C liquid cooled, all-SiC inverter for electric vehicle traction drives. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 735–742. [Google Scholar]

- Zhang, C.; Srdic, S.; Lukic, S.; Sun, K.; Wang, J.; Burgos, R. A SiC-Based Liquid-Cooled Electric Vehicle Traction Inverter Operating at High Ambient Temperature. CPSS Trans. Power Electron. Appl. 2022, 7, 160–175. [Google Scholar] [CrossRef]

- Liu, X.; Wei, M.; Qiu, M.; Hobbs, K.; Yang, S.; Dahneem, A.; Cao, D. FPGA-Based Forced Air-Cooled SiC High-Power-Density Inverter for Electrical Aircraft Applications. In Proceedings of the 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 19–23 March 2023; pp. 3169–3173. [Google Scholar]

- Stella, F.; Vico, E.; Cittanti, D.; Liu, C.; Shen, J.; Bojoi, R. Design and Testing of an Automotive Compliant 800V 550 kVA SiC Traction Inverter with Full-Ceramic DC-Link and EMI Filter. In Proceedings of the 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 9–13 October 2022; pp. 1–8. [Google Scholar]

- Vollmar, N.; Woehrle, D.; Armbruster, C.; Schoener, C. Design of a Fast Switching 200 kVA SiC Drive Inverter for Aviation Application. In Proceedings of the PCIM Europe 2023; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 9–11 May 2023; pp. 1–8. [Google Scholar]

- Mikhaylov, Y. Considerations on the Development of an Integrated Electric Inverter for High Temperature Applications. Ph.D. Thesis, University of Nottingham Ningbo China, Ningbo, China, 2023. [Google Scholar]

- FF2MR12KM1HP. Available online: https://www.infineon.com/cms/en/product/power/mosfet/silicon-carbide/modules/ff2mr12km1hp/ (accessed on 10 November 2023).

- Wolfspeed HM3 High-Performance Half-Bridge Modules. Available online: https://www.mouser.com/new/wolfspeed/wolfspeed-hm3-half-bridge-modules/ (accessed on 10 November 2023).

- MSCSM120AM02CT6LIAG-Module. Available online: https://www.microchip.com/en-us/product/mscsm120am02ct6liag-module (accessed on 10 November 2023).

- Wang, Z.; Luo, B.; Zhan, J.; Zhou, H.; Zhan, X.; Li, T.; Ye, C.; Tian, J. A 200 kW high-efficiency and high-power density xEV motor controller based on discrete SiC MOSFET devices. Int. J. Circuit Theory Appl. 2022, 50, 3053–3070. [Google Scholar] [CrossRef]

- Chen, Z.; Rizi, H.S.; Chen, C.; Liu, P.; Yu, R.; Huang, A.Q. An 800V/300 kW, 44 kW/L Air-Cooled SiC Power Electronics Building Block (PEBB). In Proceedings of the IECON 2021—47th Annual Conference of the IEEE Industrial Electronics Society, Toronto, ON, Canada, 13–16 October 2021; pp. 1–6. [Google Scholar]

- Taha, W.; Juarez-Leon, F.; Hefny, M.; Jinesh, A.; Poulton, M.; Bilgin, B.; Emadi, A. Holistic Design and Development of a 100 kW SiC-Based Six-Phase Traction Inverter for an Electric Vehicle Application. IEEE Trans. Transp. Electrif. 2023. [Google Scholar] [CrossRef]

- Costa, P.; Pinto, S.; Silva, J.F. A Novel Analytical Formulation of SiC-MOSFET Losses to Size High-Efficiency Three-Phase Inverters. Energies 2023, 16, 818. [Google Scholar] [CrossRef]

- Yu, S.; Wang, J.; Zhang, X.; Liu, Y.; Jiang, N.; Wang, W. The Potential Impact of Using Traction Inverters with SiC MOSFETs for Electric Buses. IEEE Access 2021, 9, 51561–51572. [Google Scholar] [CrossRef]

- Cittanti, D.; Guacci, M.; Mirić, S.; Bojoi, R.; Kolar, J.W. Comparative Evaluation of 800V DC-Link Three-Phase Two/Three-Level SiC Inverter Concepts for Next-Generation Variable Speed Drives. In Proceedings of the 2020 23rd International Conference on Electrical Machines and Systems (ICEMS), Hamamatsu, Japan, 24–27 November 2020; pp. 1699–1704. [Google Scholar]

- Yapa, R.; Forsyth, A.J.; Todd, R. Analysis of SiC technology in two-level and three-level converters for aerospace applications. In Proceedings of the 7th IET International Conference on Power Electronics, Machines and Drives (PEMD 2014), Manchester, UK, 8–10 April 2014; pp. 1–6. [Google Scholar]

- Merkert, A.; Krone, T.; Mertens, A. Characterization and Scalable Modeling of Power Semiconductors for Optimized Design of Traction Inverters with Si- and SiC-Devices. IEEE Trans. Power Electron. 2014, 29, 2238–2245. [Google Scholar] [CrossRef]

- Oswald, N.; Anthony, P.; McNeill, N.; Stark, B.H. An Experimental Investigation of the Tradeoff between Switching Losses and EMI Generation with Hard-Switched All-Si, Si-SiC, and All-SiC Device Combinations. IEEE Trans. Power Electron. 2014, 29, 2393–2407. [Google Scholar] [CrossRef]

- Nikouie, M.; Zhang, H.; Wallmark, O.; Nee, H. A highly integrated electric drive system for tomorrow’s EVs and HEVs. In Proceedings of the 2017 IEEE Southern Power Electronics Conference (SPEC), Manchester, UK, 4–7 December 2017; pp. 1–5. [Google Scholar]

- Deng, X.; Lambert, S.; Mecrow, B.; Mohamed, M.A.S. Design Consideration of a High-Speed Integrated Permanent Magnet Machine and its Drive System. In Proceedings of the 2018 XIII International Conference on Electrical Machines (ICEM), Alexandroupoli, Greece, 3–6 September 2018; pp. 1465–1470. [Google Scholar]

- Lee, W.; Li, S.; Han, D.; Sarlioglu, B.; Minav, T.A.; Pietola, M. A Review of Integrated Motor Drive and Wide-Bandgap Power Electronics for High-Performance Electro-Hydrostatic Actuators. IEEE Trans. Transp. Electrif. 2018, 4, 684–693. [Google Scholar] [CrossRef]

| Coefficient Name | Equation’s Parameters’ Default Values | Coefficient Default Value |

|---|---|---|

| Not applicable | ||

| , | 1 | |

| 1.4 | ||

| , | ||

| 0 | ||

| , | 1 |

| Input Parameter | Device Type | Value | Calculated Parameter | Device Type | Value |

|---|---|---|---|---|---|

| Prepreg thickness, mm | SMT | 0.1 | (per MOSFET), K/W | SMT | 2.66–4 |

| Prepreg thermal conductivity, W/m·K | 1 | ||||

| Top copper layer thickness, mm | 0.07 | ||||

| Insulation (mica + grease) thermal resistance per area, K/cm2·K | THT | 0.65 | (per MOSFET), K/W | THT | 0.88–1.05 |

| Heat sink area per a MOSFET (for SMT and THT), mm2 | SMT/THT | (L + 10)·(W + 2) | (per MOSFET), K/W | power modules | 0.148−0.54 |

| Grease thermal conductivity, W/m·K | SMT/THT/Modules | 0.73 | |||

| Heatsink heat transfer coefficient, W/cm2·K | 0.5 |

| Parameter | Value |

|---|---|

| , A | 200 |

| , V | 400 |

| , kHz | 50 |

| , °C | 25 |

| , W/cm2·K | 0.5 |

| Parameter | Area | Weight | Volume |

|---|---|---|---|

| Additional values | 1.5 cm * | 1.5 kg ** | 1.5 L ** |

| , V | , kHz | , kHz | Load (per Phase) | ||

|---|---|---|---|---|---|

| 350 | 50 | 1 | 0.5 mH, 8.6–16.8 Ohm | 0.42 | 2.9–4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mikhaylov, Y.; Aboelhassan, A.; Buticchi, G.; Galea, M. Considerations on the Development of High-Power Density Inverters for Highly Integrated Motor Drives. Electronics 2024, 13, 355. https://doi.org/10.3390/electronics13020355

Mikhaylov Y, Aboelhassan A, Buticchi G, Galea M. Considerations on the Development of High-Power Density Inverters for Highly Integrated Motor Drives. Electronics. 2024; 13(2):355. https://doi.org/10.3390/electronics13020355

Chicago/Turabian StyleMikhaylov, Yury, Ahmed Aboelhassan, Giampaolo Buticchi, and Michael Galea. 2024. "Considerations on the Development of High-Power Density Inverters for Highly Integrated Motor Drives" Electronics 13, no. 2: 355. https://doi.org/10.3390/electronics13020355

APA StyleMikhaylov, Y., Aboelhassan, A., Buticchi, G., & Galea, M. (2024). Considerations on the Development of High-Power Density Inverters for Highly Integrated Motor Drives. Electronics, 13(2), 355. https://doi.org/10.3390/electronics13020355