System Identification–Based Adaptive Real-Time Simulators for Power Electronic Converters—Application to Three-Phase and NPC Inverters

Abstract

1. Introduction

- -

- The possibility to approximate each power switch is based on the voltage/current experimental characteristics. The main interest is to provide a reconfigurable and adaptive eRTS that approximates the actual switch characteristics and, thus, the actual environment where the power converter is deployed.

- -

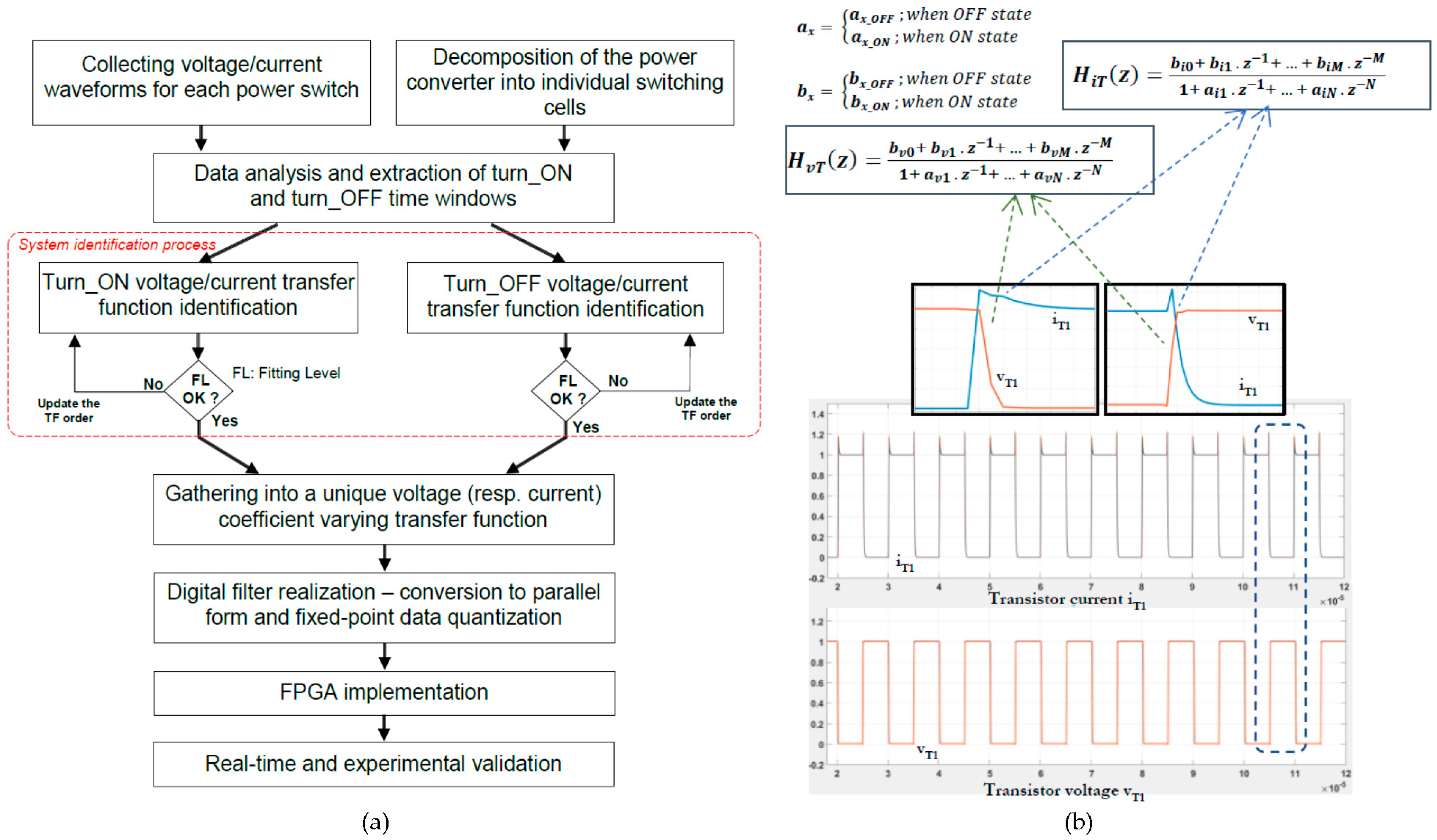

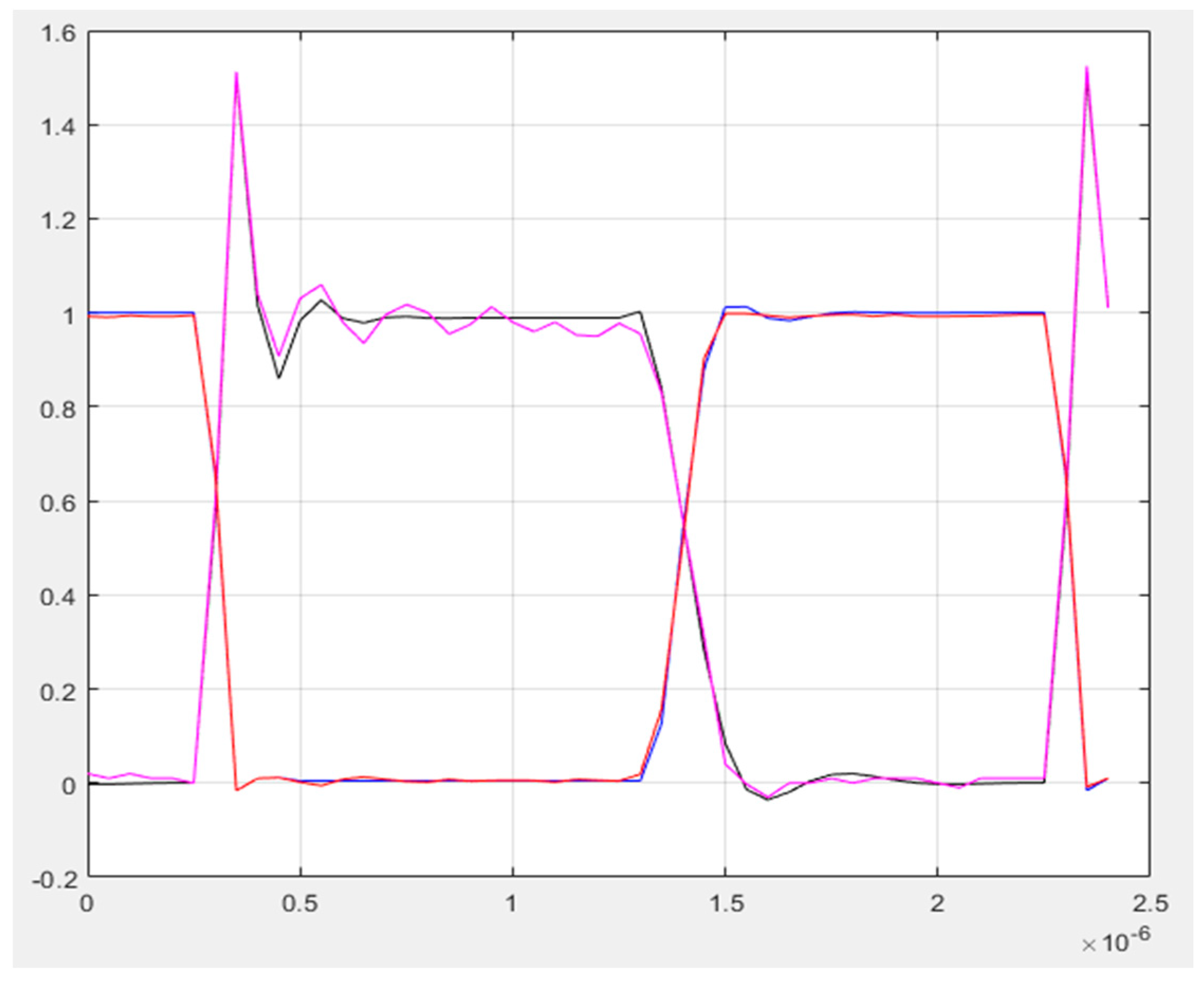

- These experimental data are provided to a system identification process that generates linear transfer functions (TFs). For each power switch, TFs are merged into a unique voltage (resp. current) TF with varying coefficients in order to cover the turn-ON and turn-OFF switch states. These coefficients are not only varying depending on these states, but it is possible to extend them to various electrical/thermal operating conditions of each switch. At the end of the identification process, these coefficients are collected, stored in memory blocks, and adequately read at each simulation time step.

- -

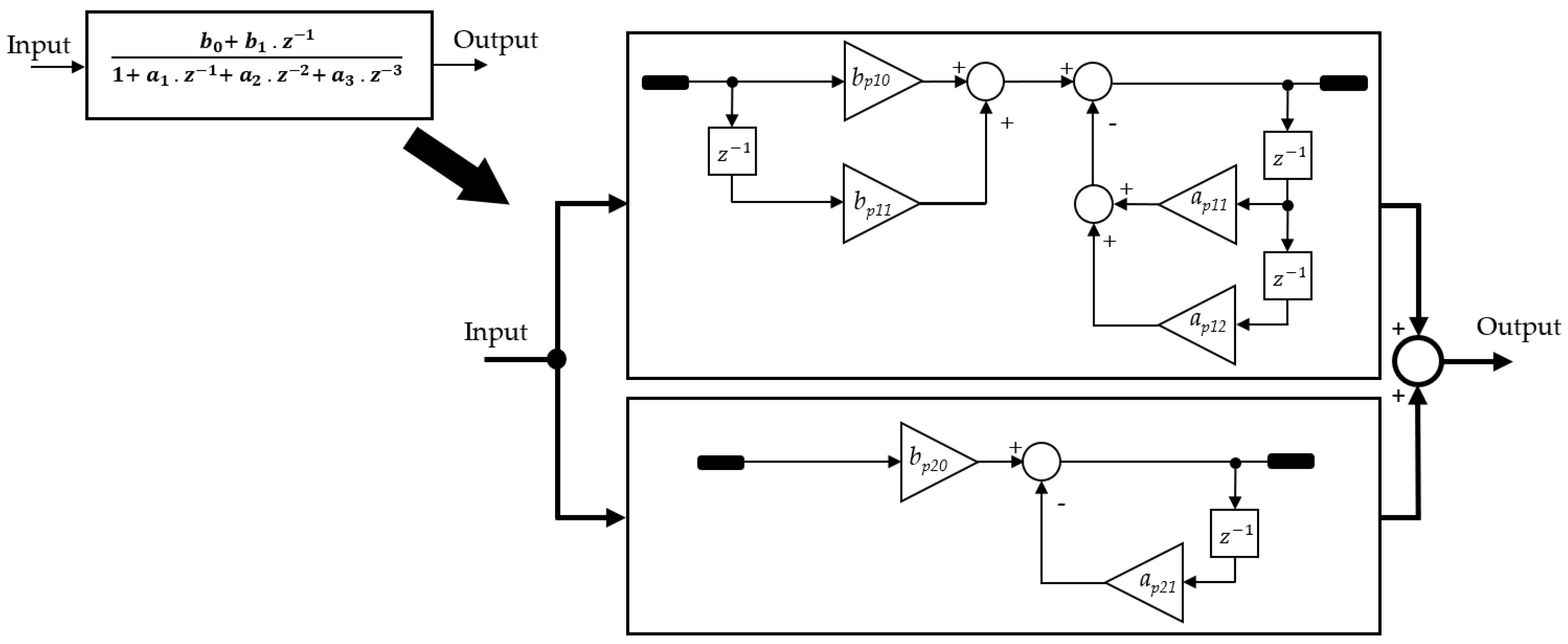

- In terms of digital realization, the eRTS is fully parallelized, and the inherent N-order TFs are designed with a parallel filter form [27], which implies a constant execution time remains regardless of the order (the execution time of a second-order TF). This allows a high fitting level of the experimental data while keeping a short simulation time step. In this context, the use of FPGA is mandatory to preserve this parallelism. However, the price to pay is located at the hardware resources, which have to be rigorously managed, and the data paths carefully synchronized and pipelined.

2. Main Basics of the Adopter Modeling Approach

2.1. System Identification Process

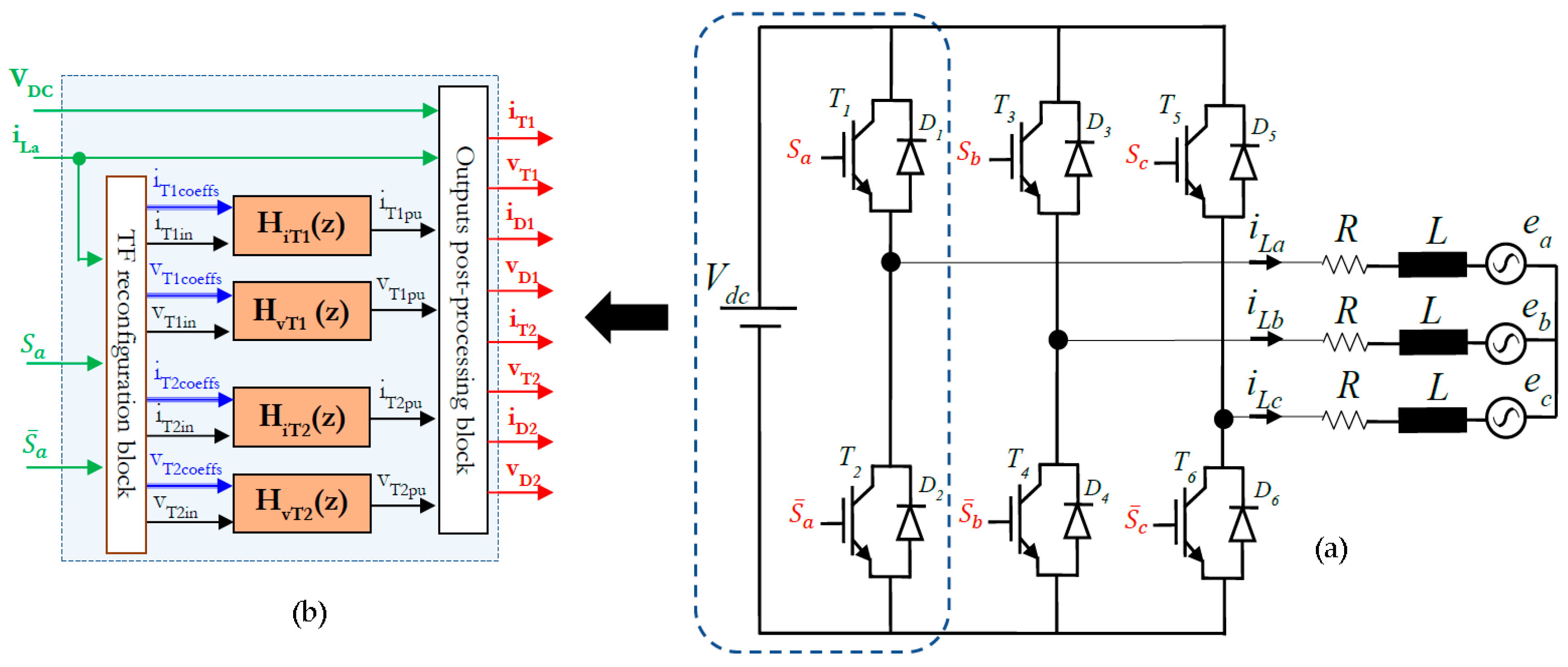

2.2. TF Reconfiguration Block and Output Post-Processing

2.3. Digital Realization and FPGA Implementation

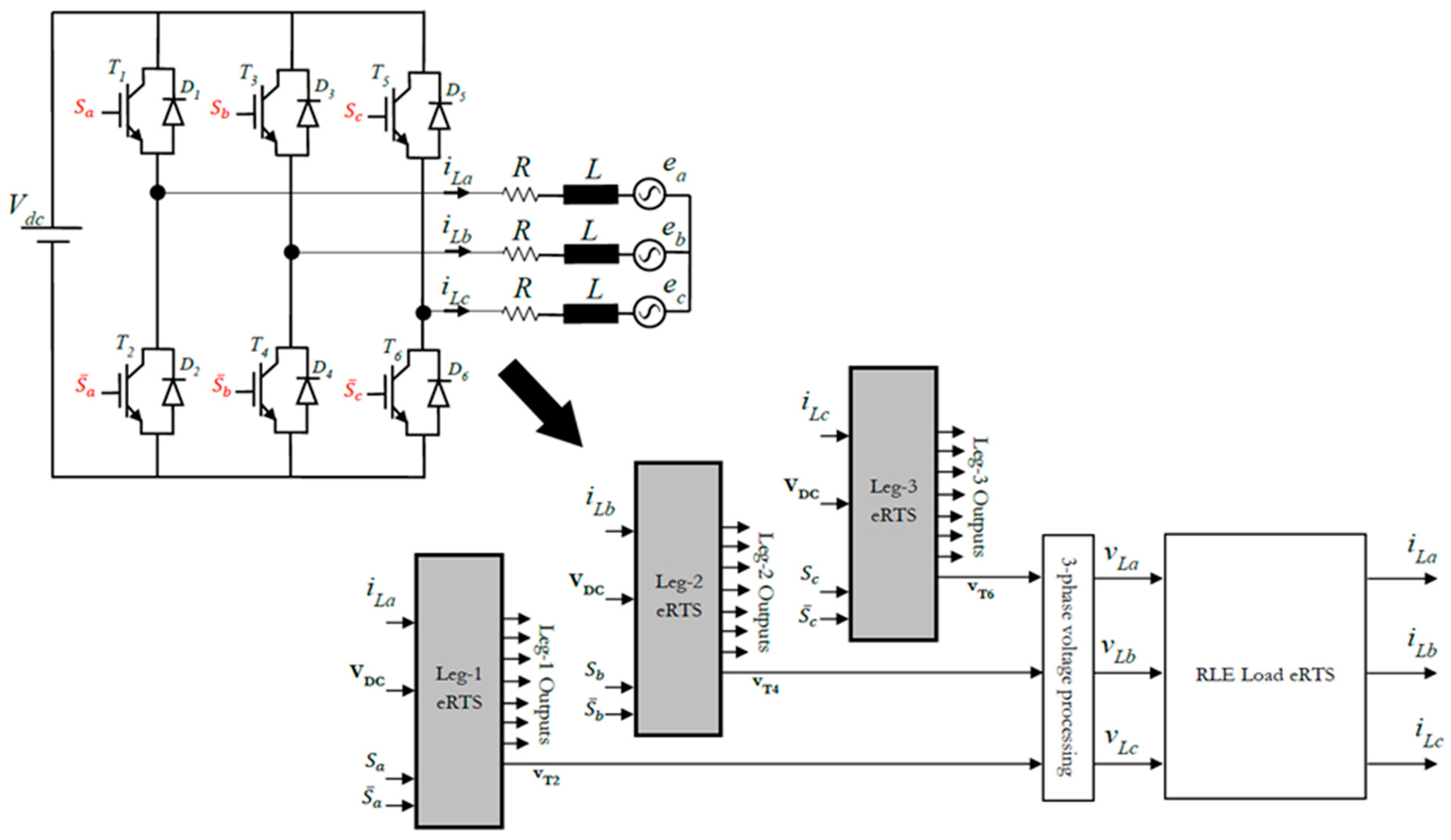

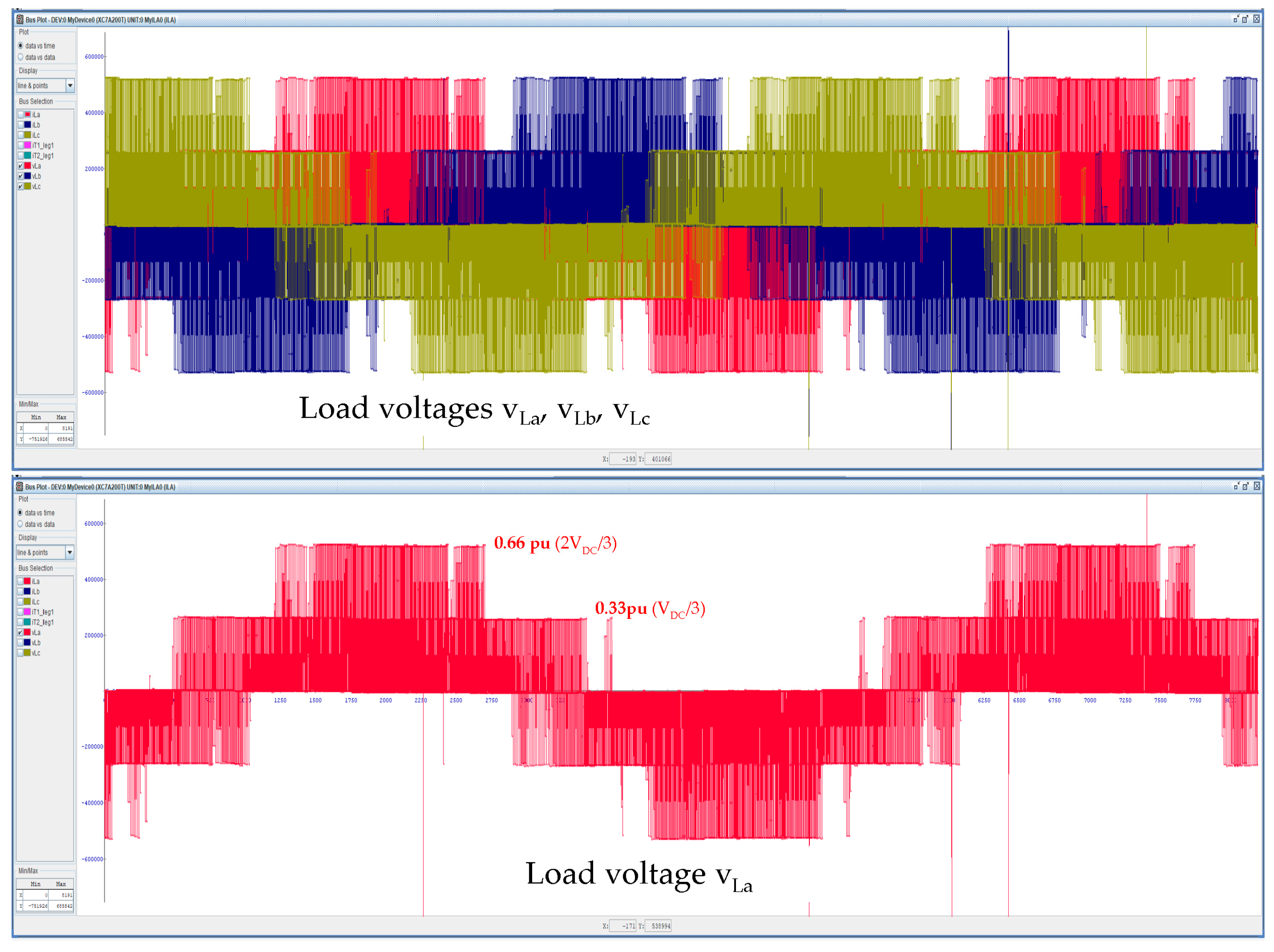

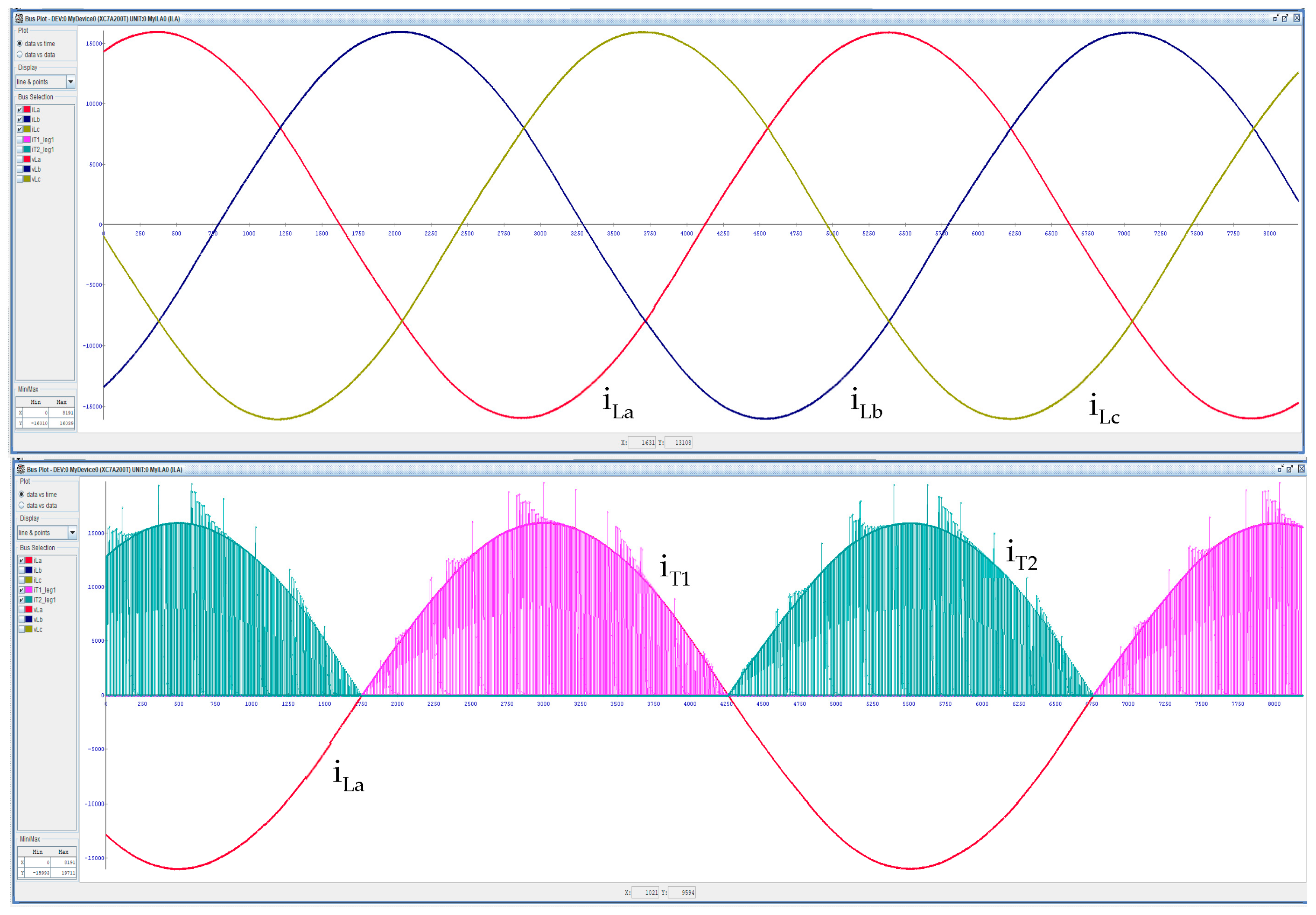

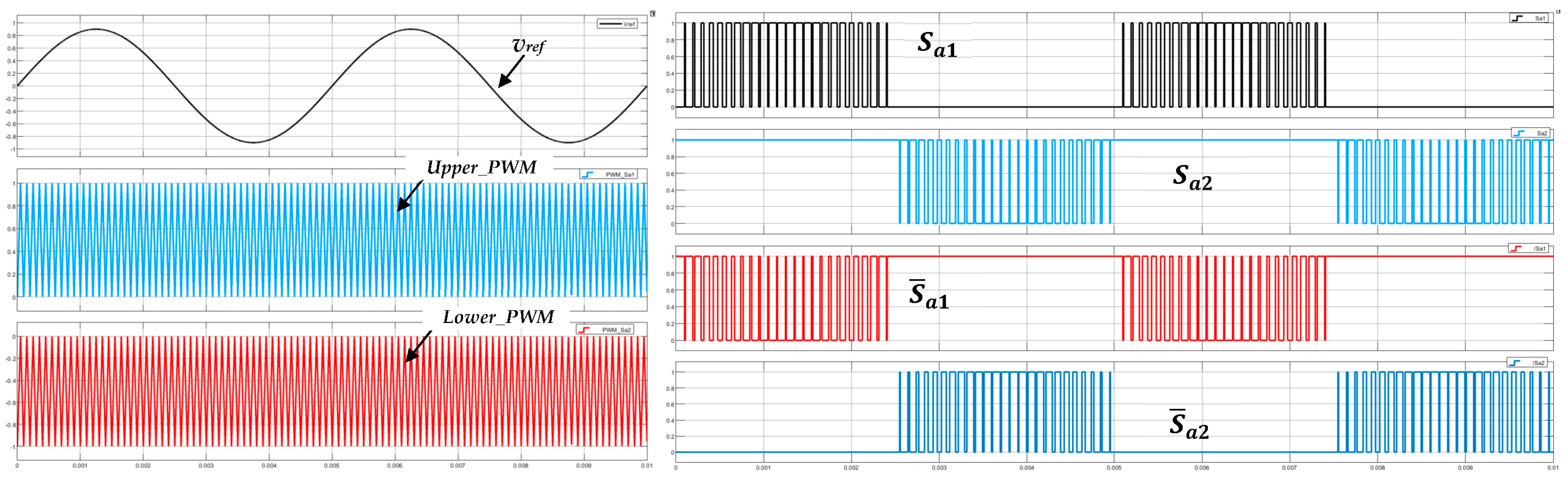

3. Application to a Three-Phase Voltage Source Inverter

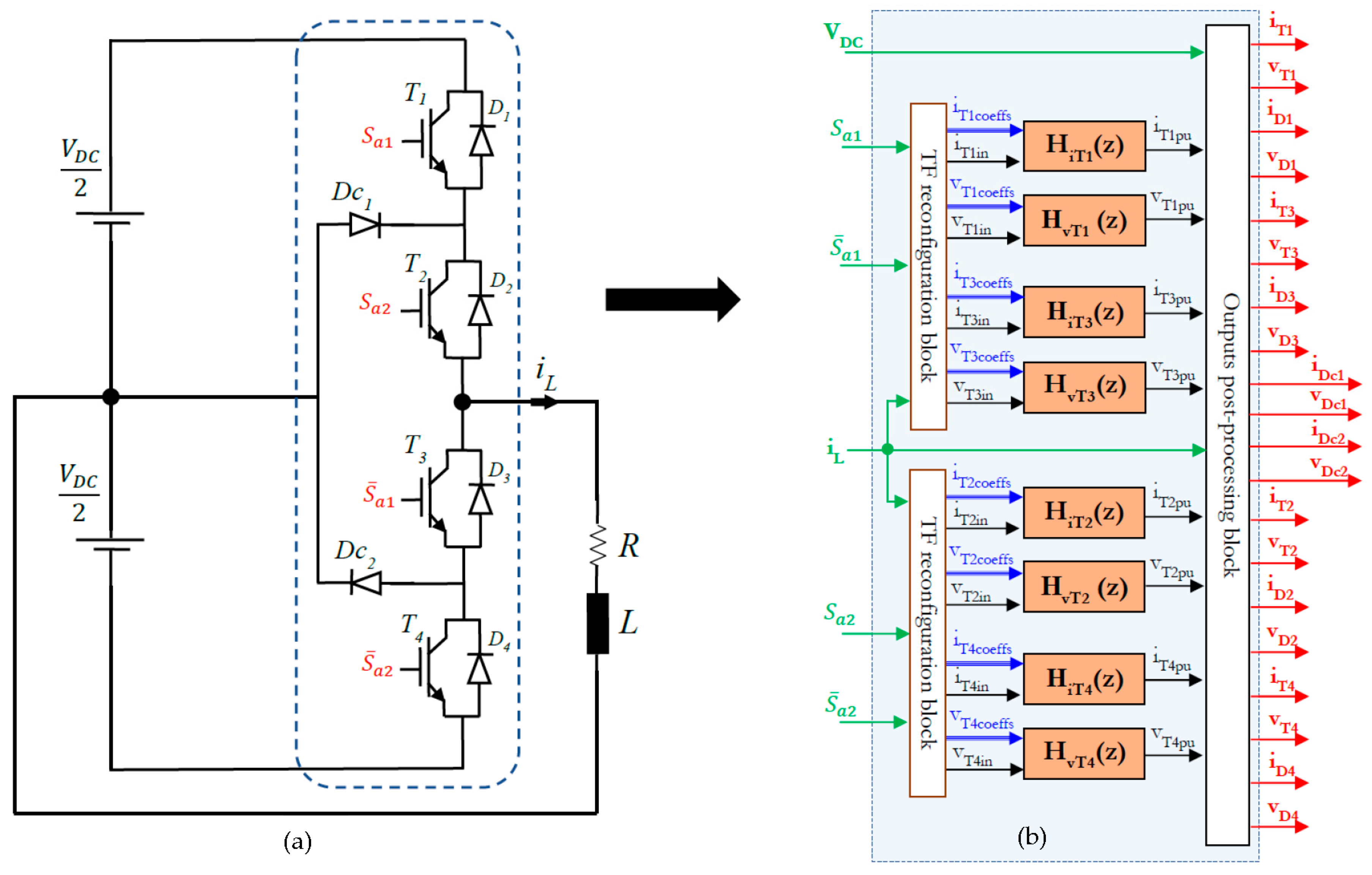

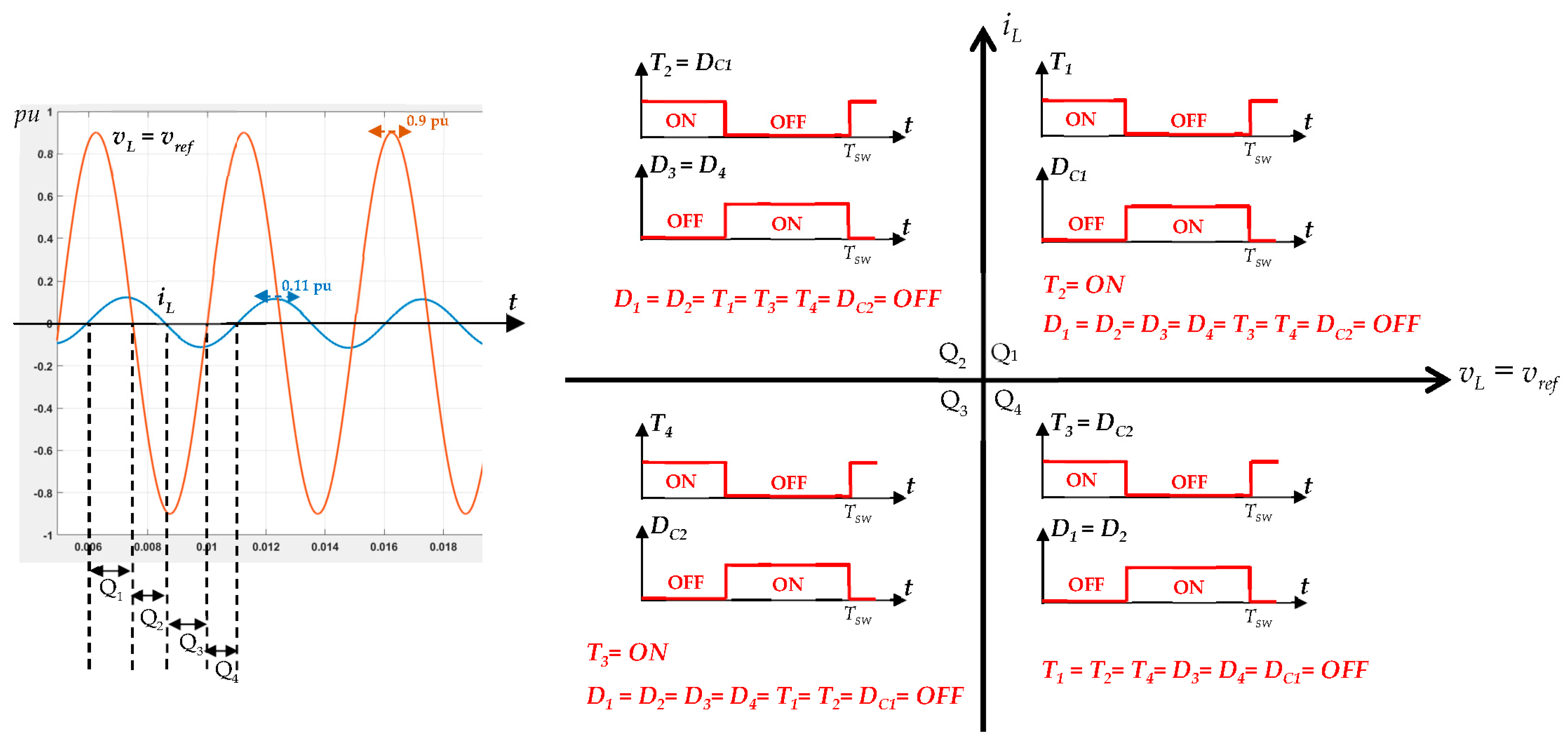

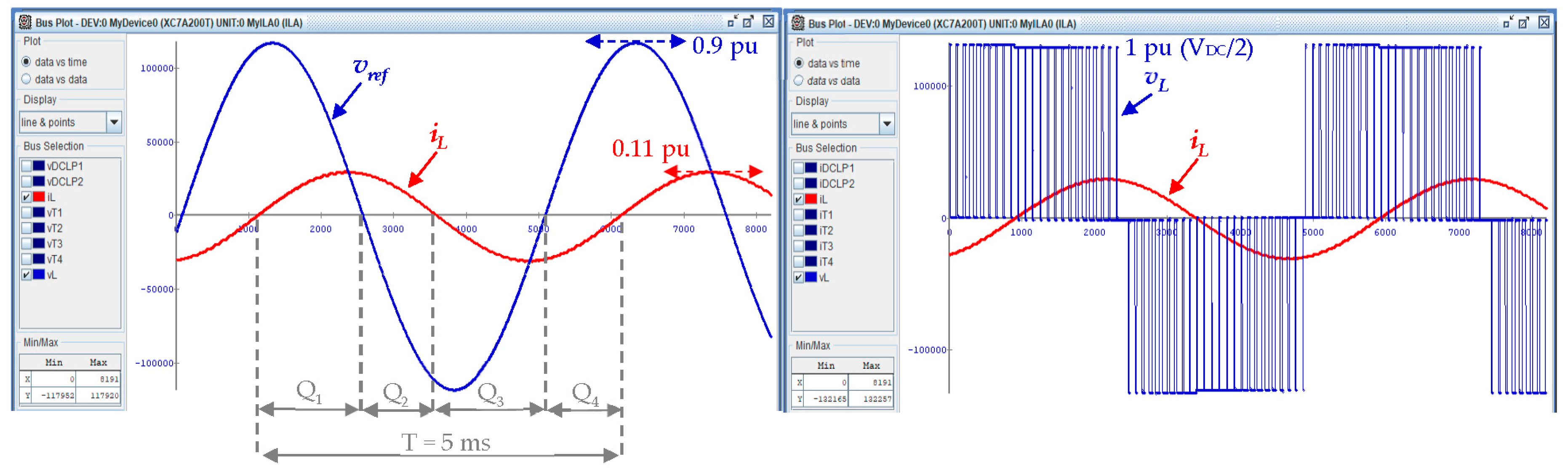

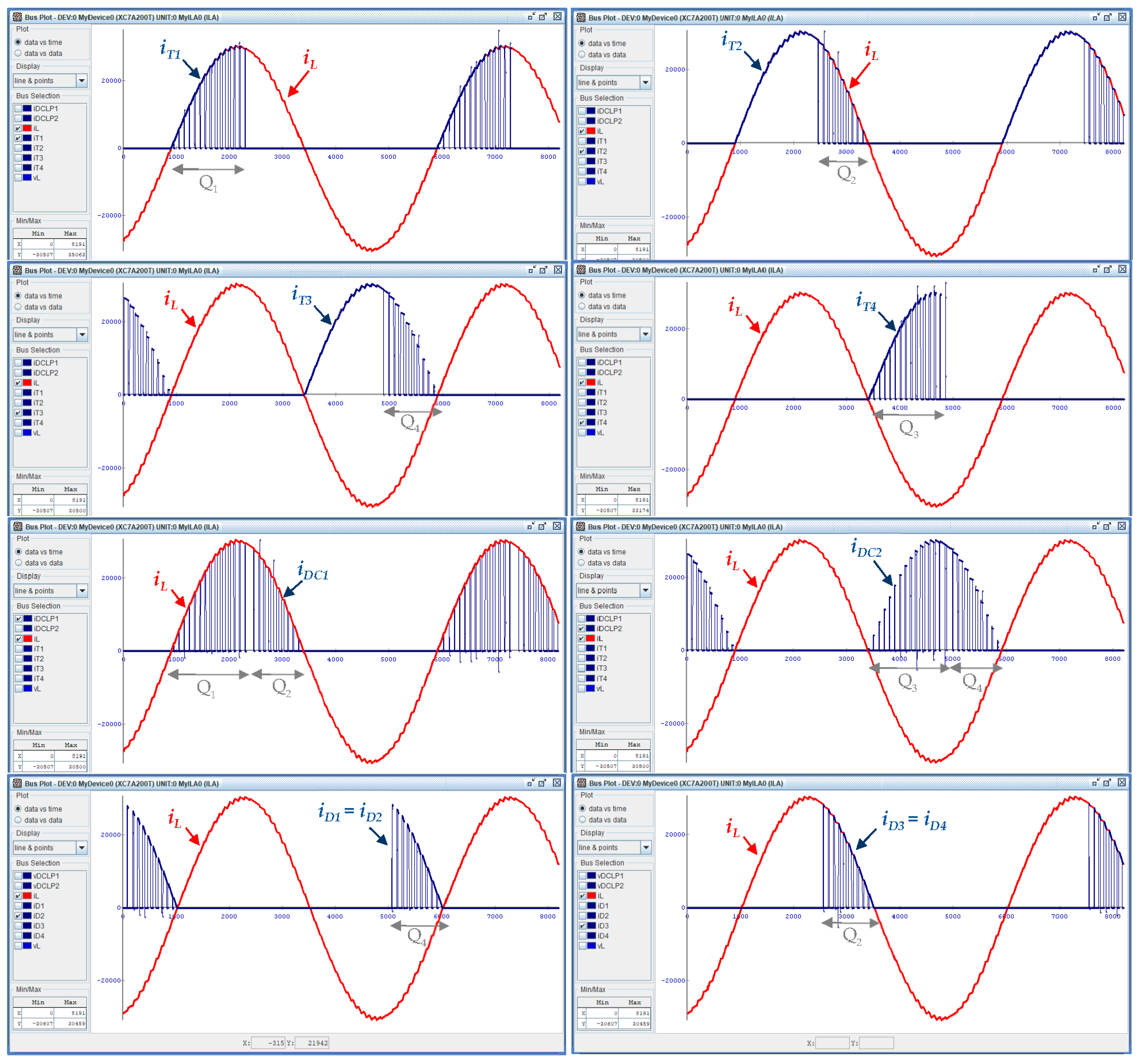

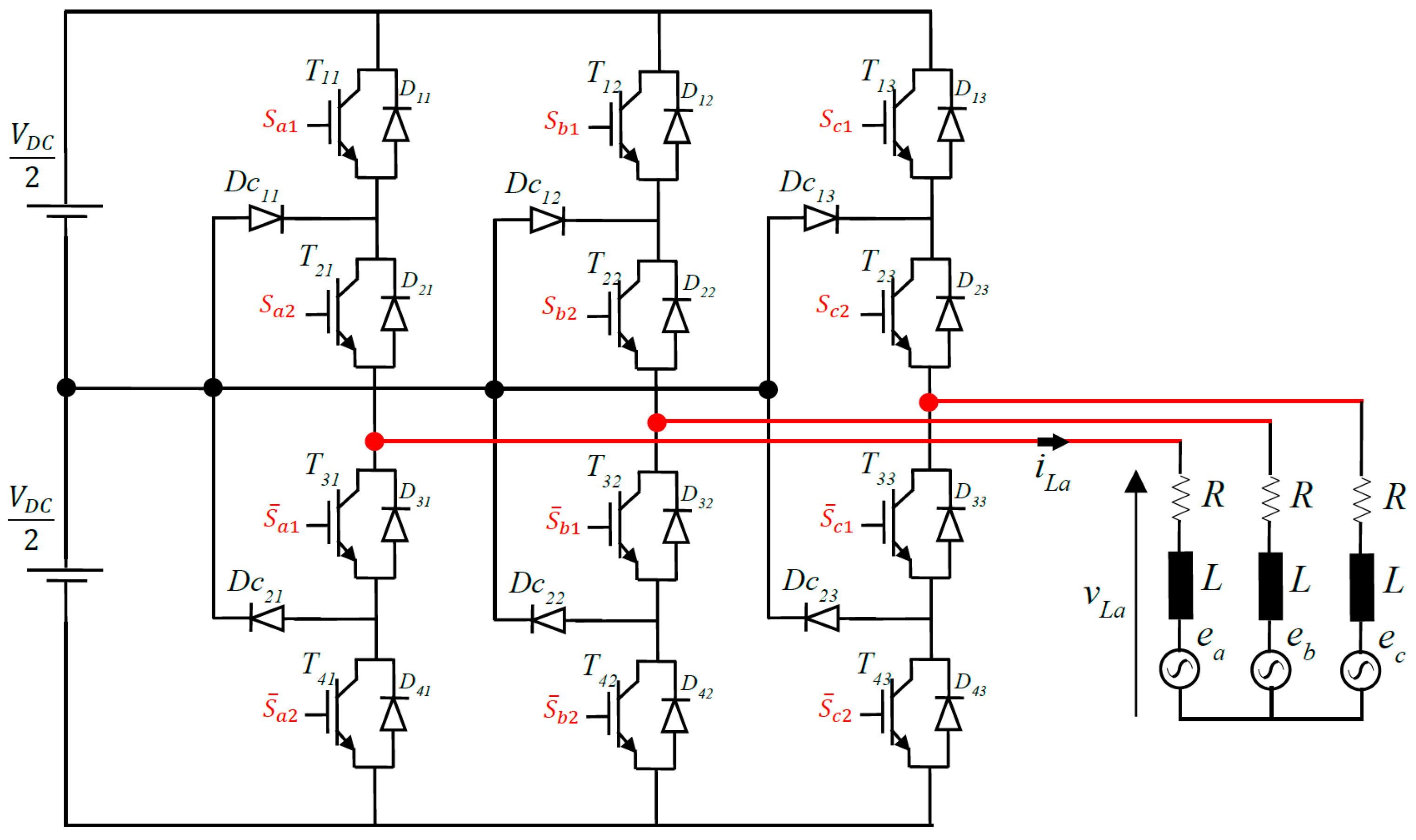

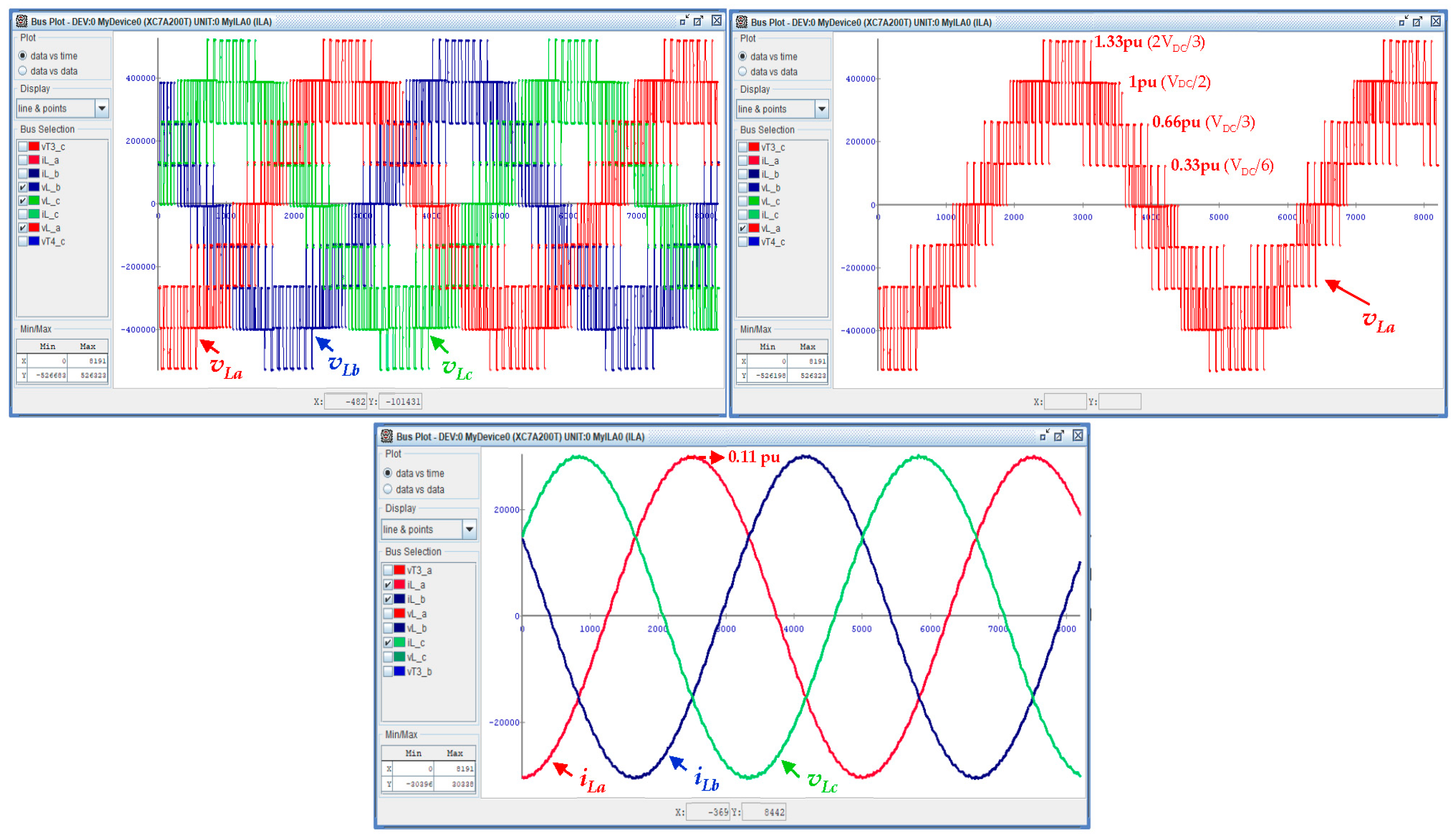

4. Application to a Neutral-Point Clamped Inverter

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Nomenclature

| Transistor, diode | |

| Transistor and diode currents | |

| Transistor and diode voltages | |

| DC-link voltage | |

| Load currents and voltages | |

| Switching signals | |

| Load resistance, inductance, and back-EMF | |

| Transfer function | |

| Transfer function coefficients | |

| NPC inverter operating quadrants |

References

- Mihalič, F.; Truntič, M.; Hren, A. Hardware-in-the-Loop Simulations: A Historical Overview of Engineering Challenges. Electronics 2022, 11, 2462. [Google Scholar] [CrossRef]

- Martínez-García, M.S.; de Castro, A.; Sanchez, A.; Garrido, J. Analysis of Resolution in Feedback Signals for Hardware-in-the-Loop Models of Power Converters. Electronics 2019, 8, 1527. [Google Scholar] [CrossRef]

- Canciello, G.; Cavallo, A.; Schiavo, A.L.; Russo, A. Multi-objective adaptive sliding manifold control for More Electric Aircraft. ISA Trans. 2020, 107, 316–328. [Google Scholar] [CrossRef]

- Fernandez-Alvarez, A.; Portela-Garcia, M.; Garcia-Valderas, M.; Lopez, J.; Sanz, M. HW/SW Co-Simulation System for Enhancing Hardware-in-the-Loop of Power Converter Digital Controllers. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1779–1786. [Google Scholar] [CrossRef]

- Mayet, C.; Id-Khajine, L. Introduction to Hardware-In-the-Loop (HIL) simulations of electrical power systems. In Encyclopedia of Electrical and Electronic Power Engineering; Elsevier: Amsterdam, The Netherlands, 2023; pp. 590–599. [Google Scholar] [CrossRef]

- Lauss, G.; Strunz, K. Accurate and Stable Hardware-in-the-Loop (HIL) Real-Time Simulation of Integrated Power Electronics and Power Systems. IEEE Trans. Power Electron. 2021, 36, 10920–10932. [Google Scholar] [CrossRef]

- Tormo, D.; Vidal-Albalate, R.; Idkhajine, L.; Monmasson, E.; Blasco-Gimenez, R. Embedded Real-Time Simulator for Sensorless Control of Modular Multi-Level Converters. Electronics 2022, 11, 719. [Google Scholar] [CrossRef]

- Tormo, D.; Idkhajine, L.; Monmasson, E.; Vidal-Albalate, R.; Blasco-Gimenez, R. Embedded real-time simulators for electromechanical and power electronic systems using system-on-chip devices. Math. Comput. Simul. 2018, 158, 326–343. [Google Scholar] [CrossRef]

- Peng, Y.; Zhao, S.; Wang, H. A Digital Twin Based Estimation Method for Health Indicators of DC–DC Converters. IEEE Trans. Power Electron. 2020, 36, 2105–2118. [Google Scholar] [CrossRef]

- Milton, M.; De La O, C.A.; Ginn, H.L.; Benigni, A. Controller-Embeddable Probabilistic Real-Time Digital Twins for Power Electronic Converter Diagnostics. IEEE Trans. Power Electron. 2020, 35, 9850–9864. [Google Scholar] [CrossRef]

- Peyghami, S.; Palensky, P.; Blaabjerg, F. An Overview on the Reliability of Modern Power Electronic Based Power Systems. IEEE Open J. Power Electron. 2020, 1, 34–50. [Google Scholar] [CrossRef]

- Gachovska, T.K.; Hudgins, J.L. SiC and GaN Power Semiconductor Devices. In Power Electronics Handbook, 4th ed.; Elsevier Inc.: Amsterdam, The Netherlands, 2018. [Google Scholar] [CrossRef]

- Bai, H.; Liu, C.; Breaz, E.; Al-Haddad, K.; Gao, F. A Review on the Device-Level Real-Time Simulation of Power Electronic Converters: Motivations for Improving Performance. IEEE Ind. Electron. Mag. 2020, 15, 12–27. [Google Scholar] [CrossRef]

- Montaño, F.; Ould-Bachir, T.; David, J. A Latency-Insensitive Design Approach to Programmable FPGA-Based Real-Time Simulators. Electronics 2020, 9, 1838. [Google Scholar] [CrossRef]

- Dagbagi, M.; Hemdani, A.; Idkhajine, L.; Naouar, M.W.; Monmasson, E.; Slama-Belkhodja, I. ADC-Based Embedded Real-Time Simulator of a Power Converter Implemented in a Low-Cost FPGA: Application to a Fault-Tolerant Control of a Grid-Connected Voltage-Source Rectifier. IEEE Trans. Ind. Electron. 2015, 63, 1179–1190. [Google Scholar] [CrossRef]

- Song, Y.; Chen, L.; Chen, Y.; Huang, S. A general parameter configuration algorithm for associate discrete circuit switch model. In Proceedings of the POWERCON 2014—2014 International Conference on Power System Technology: Towards Green, Efficient and Smart Power System, Proceedings, Powercon. Chengdu, China, 22–24 October 2014; pp. 956–961. [Google Scholar] [CrossRef]

- Wang, K.; Xu, J.; Li, G.; Tai, N.; Tong, A.; Hou, J. A Generalized Associated Discrete Circuit Model of Power Converters in Real-Time Simulation. IEEE Trans. Power Electron. 2018, 34, 2220–2233. [Google Scholar] [CrossRef]

- Shen, Z.; Dinavahi, V. Dynamic Variable Time-Stepping Schemes for Real-Time FPGA-Based Nonlinear Electromagnetic Transient Emulation. IEEE Trans. Ind. Electron. 2017, 64, 4006–4016. [Google Scholar] [CrossRef]

- Lin, N.; Dinavahi, V. Detailed Device-Level Electrothermal Modeling of the Proactive Hybrid HVDC Breaker for Real-Time Hardware-in-the-Loop Simulation of DC Grids. IEEE Trans. Power Electron. 2017, 33, 1118–1134. [Google Scholar] [CrossRef]

- Liang, T.; Liu, Q.; Dinavahi, V.R. Real-Time Hardware-in-the-Loop Emulation of High-Speed Rail Power System with SiC-Based Energy Conversion. IEEE Access 2020, 8, 122348–122359. [Google Scholar] [CrossRef]

- Shi, B.; Zhao, Z.; Zhu, Y. Piecewise Analytical Transient Model for Power Switching Device Commutation Unit. IEEE Trans. Power Electron. 2018, 34, 5720–5736. [Google Scholar] [CrossRef]

- Bai, H.; Luo, H.; Liu, C.; Paire, D.; Gao, F. A Device-Level Transient Modeling Approach for the FPGA-Based Real-Time Simulation of Power Converters. IEEE Trans. Power Electron. 2019, 35, 1282–1292. [Google Scholar] [CrossRef]

- Lin, N.; Dinavahi, V. Behavioral Device-Level Modeling of Modular Multilevel Converters in Real Time for Variable-Speed Drive Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1177–1191. [Google Scholar] [CrossRef]

- Myaing, A.; Dinavahi, V. FPGA-Based Real-Time Emulation of Power Electronic Systems with Detailed Representation of Device Characteristics. IEEE Trans. Ind. Electron. 2010, 58, 358–368. [Google Scholar] [CrossRef]

- De Carne, G.; Lauss, G.; Syed, M.H.; Monti, A.; Benigni, A.; Karrari, S.; Kotsampopoulos, P.; Faruque, O. On Modeling Depths of Power Electronic Circuits for Real-Time Simulation—A Comparative Analysis for Power Systems. IEEE Open Access J. Power Energy 2022, 9, 76–87. [Google Scholar] [CrossRef]

- Idkhajine, L.; Monmasson, E. Embedded Fully FPGA-Based Real-Time Simulators for Static Power Converters with Power Switch Characteristics Approximated by Identification. IEEE Trans. Ind. Electron. 2021, 69, 9624–9633. [Google Scholar] [CrossRef]

- Bank, B. Converting Infinite Impulse Response Filters to Parallel Form [Tips & Tricks]. IEEE Signal Process. Mag. 2018, 35, 124–130. [Google Scholar] [CrossRef]

- Monmasson, E.; Idkhajine, L.; Cirstea, M.N.; Bahri, I.; Tisan, A.; Naouar, M.W. FPGAs in Industrial Control Applications. IEEE Trans. Ind. Inform. 2011, 7, 224–243. [Google Scholar] [CrossRef]

- AMD-Xilinx On-Line Documentation. Available online: www.xilinx.com (accessed on 28 January 2023).

| Variable | Commutation | Den. Coeffs | Num. Coeffs | Fitting Level |

|---|---|---|---|---|

| Turn-ON | a1 = 0.3428 a2 = 0.2966 a3 = 0.08111 | b0 = 0.5694 b1 = 1.132 | 91.87% | |

| Turn-OFF | a1 = −1.668 a2 = 1.128 a3 = −0.2927 | b0 = −0.004497 b1 = 0.1712 | 96.18% | |

| Turn-ON | a1 = 0.03343 a2 = 0.009234 a3 = −0.01028 | b0 = 0.3424 b1 = 0.6848 | 98.92% | |

| Turn-OFF | a1 = −1 a2 = 0.556 a3 = −0.1435 | b0 = 0.1219 b1 = 0.2892 | 96.99% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Idkhajine, L.; Aarab, M.; Monmasson, E. System Identification–Based Adaptive Real-Time Simulators for Power Electronic Converters—Application to Three-Phase and NPC Inverters. Electronics 2023, 12, 1094. https://doi.org/10.3390/electronics12051094

Idkhajine L, Aarab M, Monmasson E. System Identification–Based Adaptive Real-Time Simulators for Power Electronic Converters—Application to Three-Phase and NPC Inverters. Electronics. 2023; 12(5):1094. https://doi.org/10.3390/electronics12051094

Chicago/Turabian StyleIdkhajine, Lahoucine, Mohamed Aarab, and Eric Monmasson. 2023. "System Identification–Based Adaptive Real-Time Simulators for Power Electronic Converters—Application to Three-Phase and NPC Inverters" Electronics 12, no. 5: 1094. https://doi.org/10.3390/electronics12051094

APA StyleIdkhajine, L., Aarab, M., & Monmasson, E. (2023). System Identification–Based Adaptive Real-Time Simulators for Power Electronic Converters—Application to Three-Phase and NPC Inverters. Electronics, 12(5), 1094. https://doi.org/10.3390/electronics12051094