Development of Bidirectional Pulsed Power Supply and Its Effect on Copper Plating Effect of Printed Circuit Board Via-Filling

Abstract

:1. Introduction

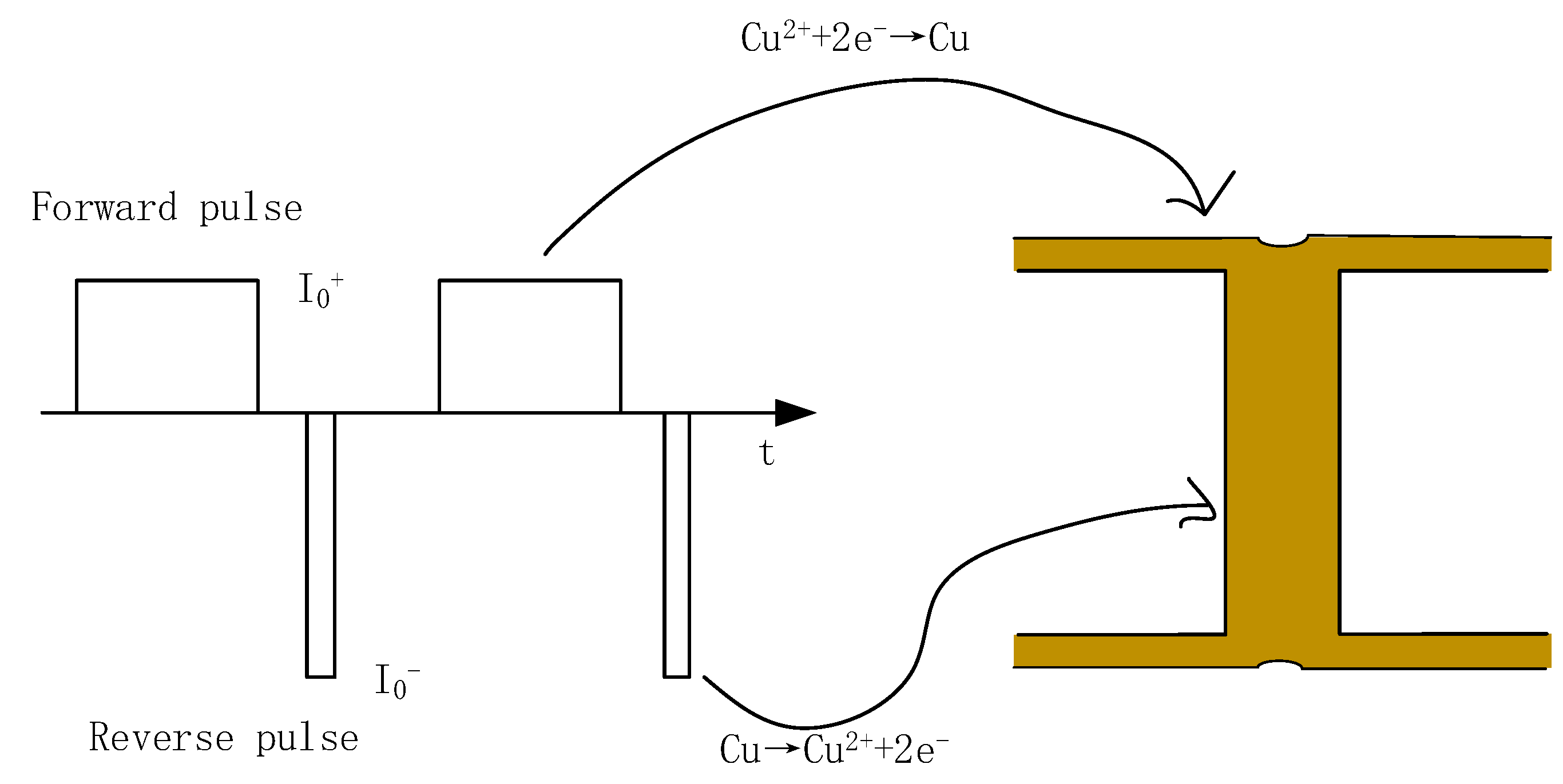

2. Principle of Bidirectional Pulse Plating

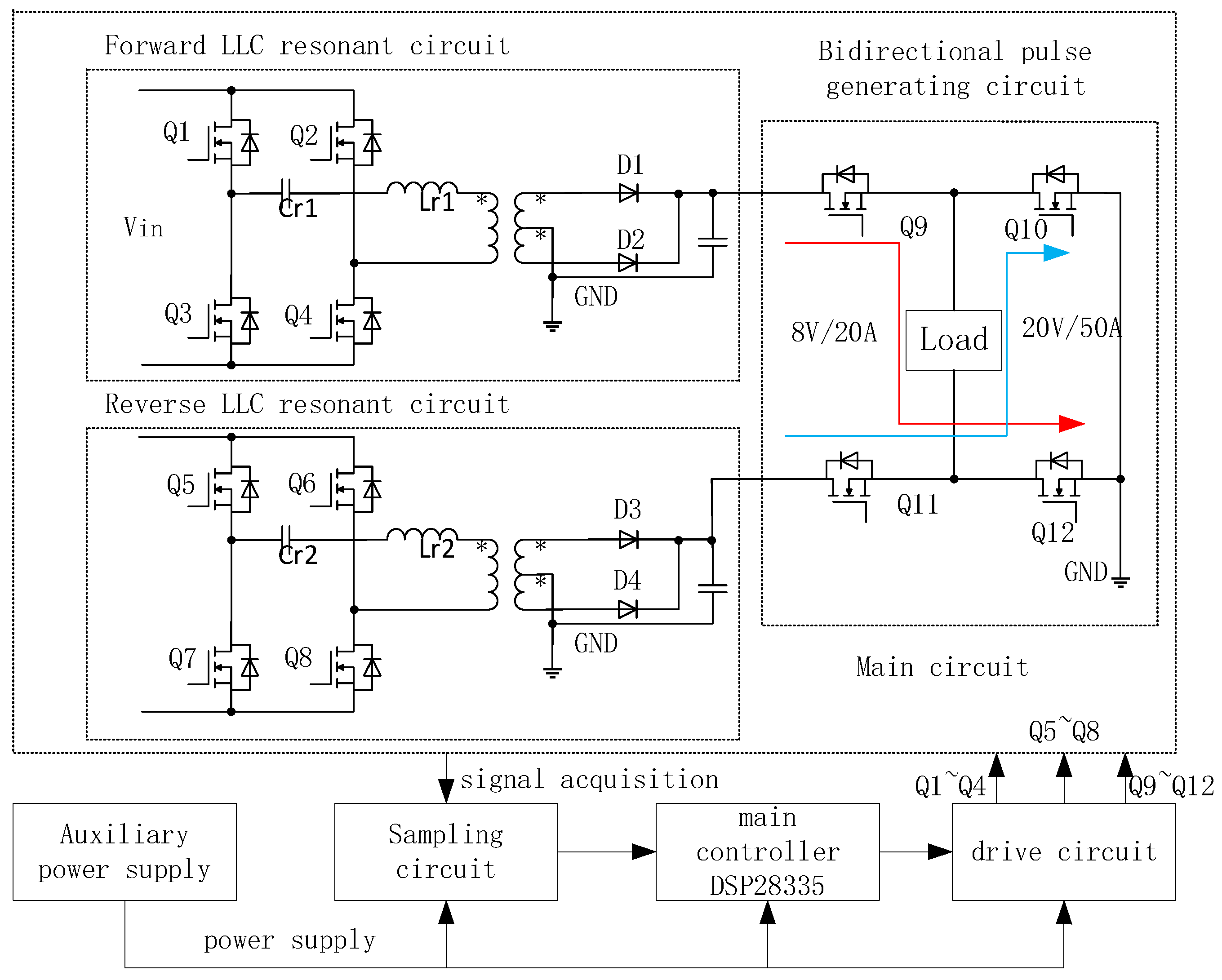

3. Development of Bidirectional Asymmetric Pulse Plating Power Supply

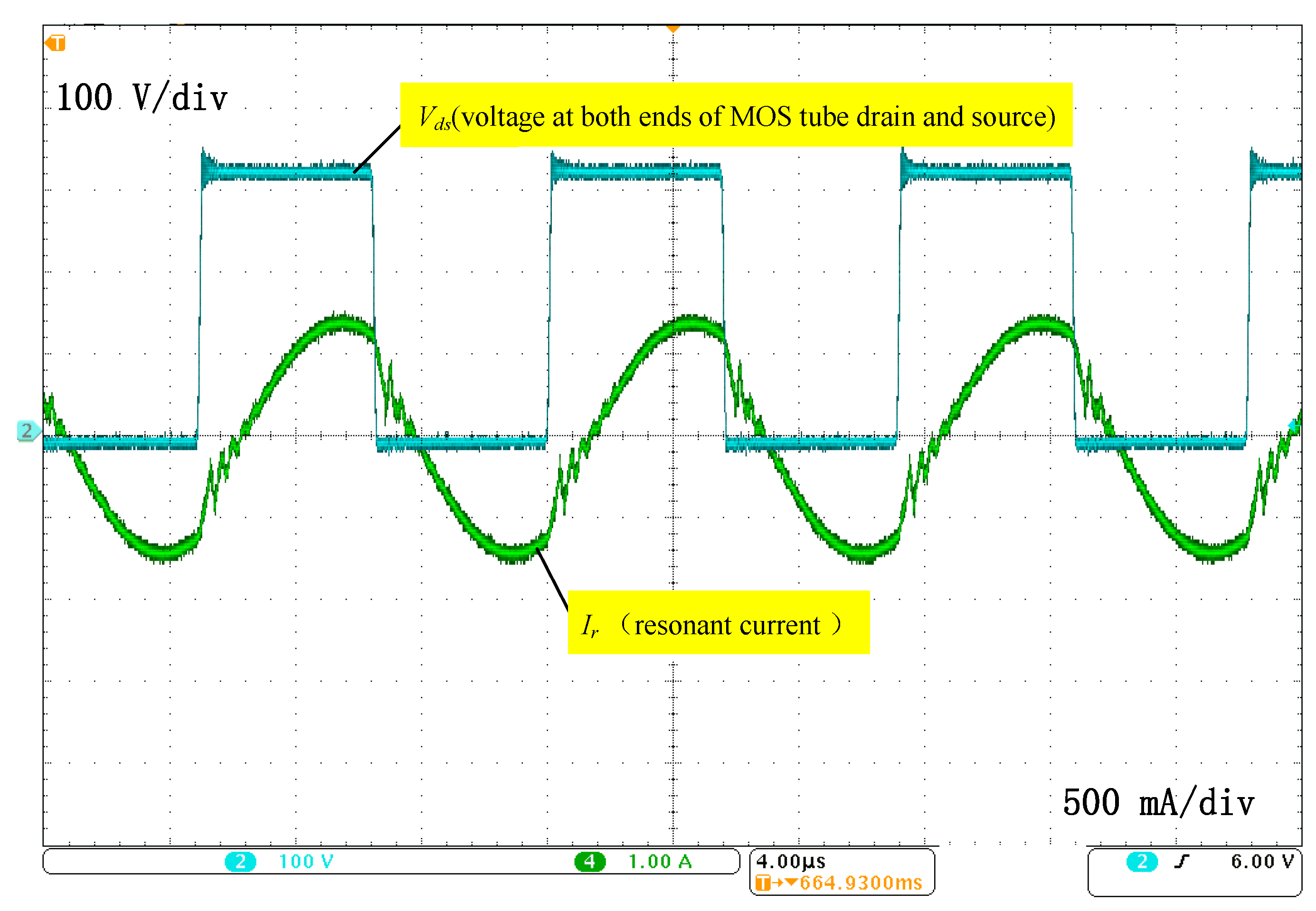

3.1. LLC Resonant Converter Design

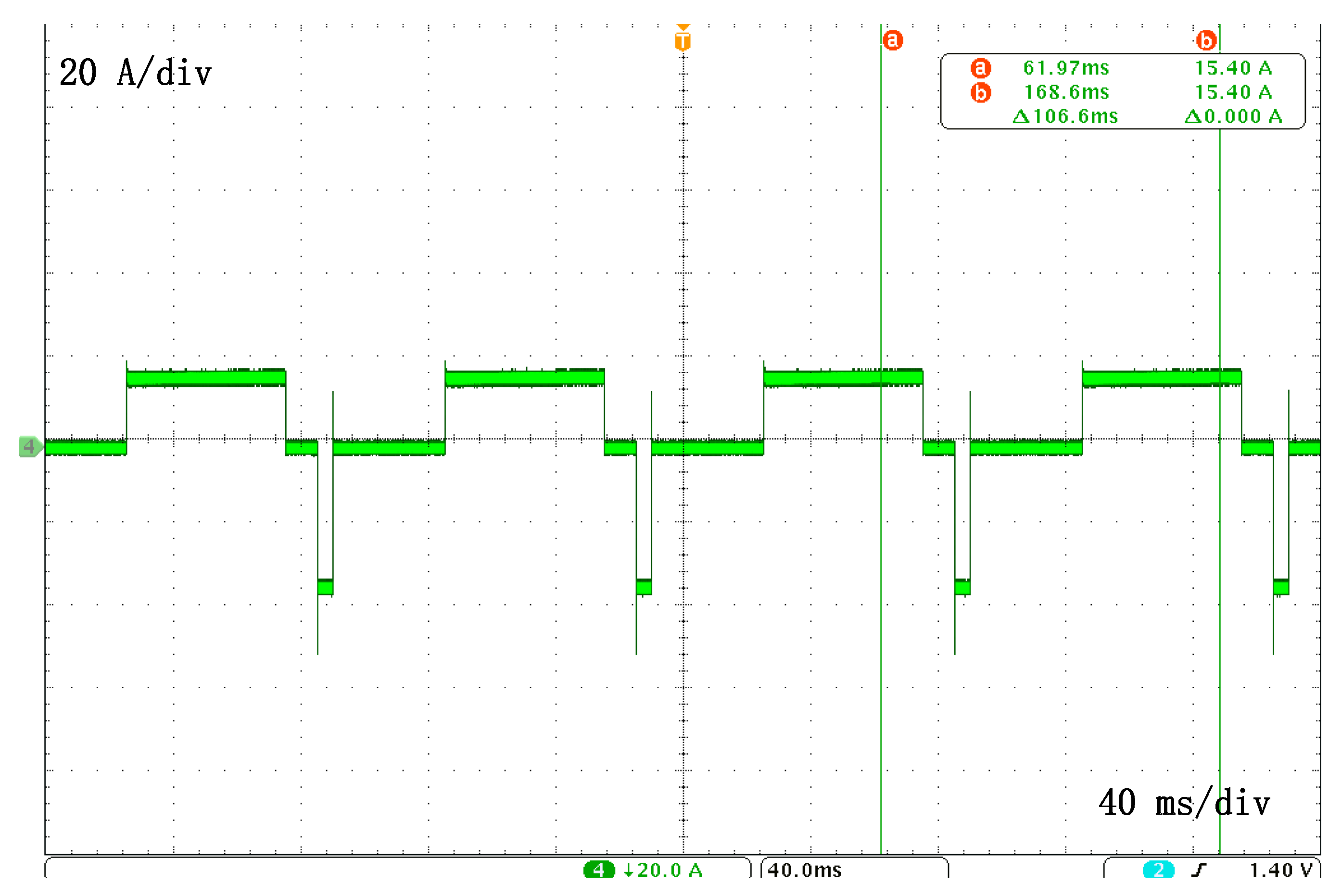

3.2. Bidirectional Pulse Generator Design

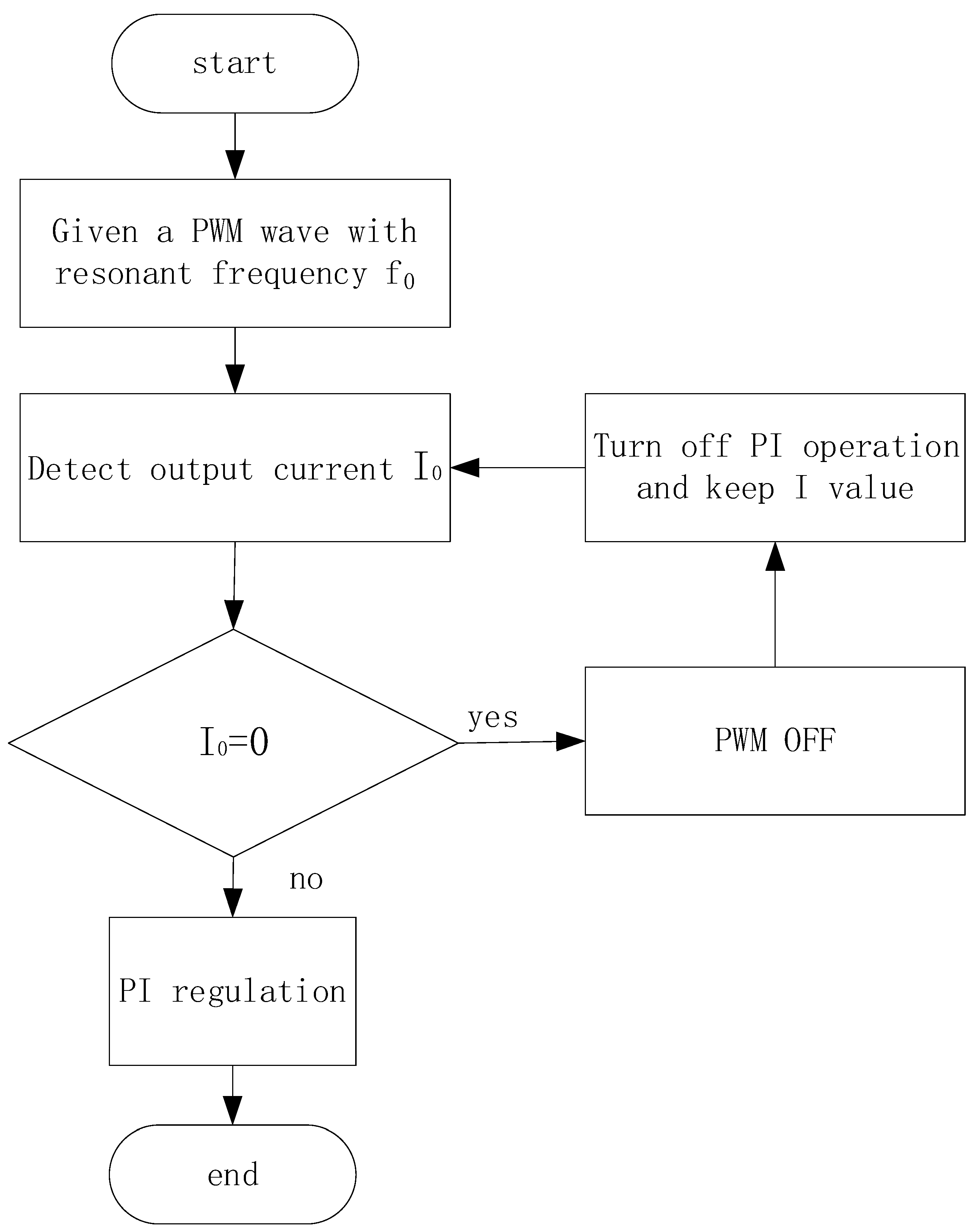

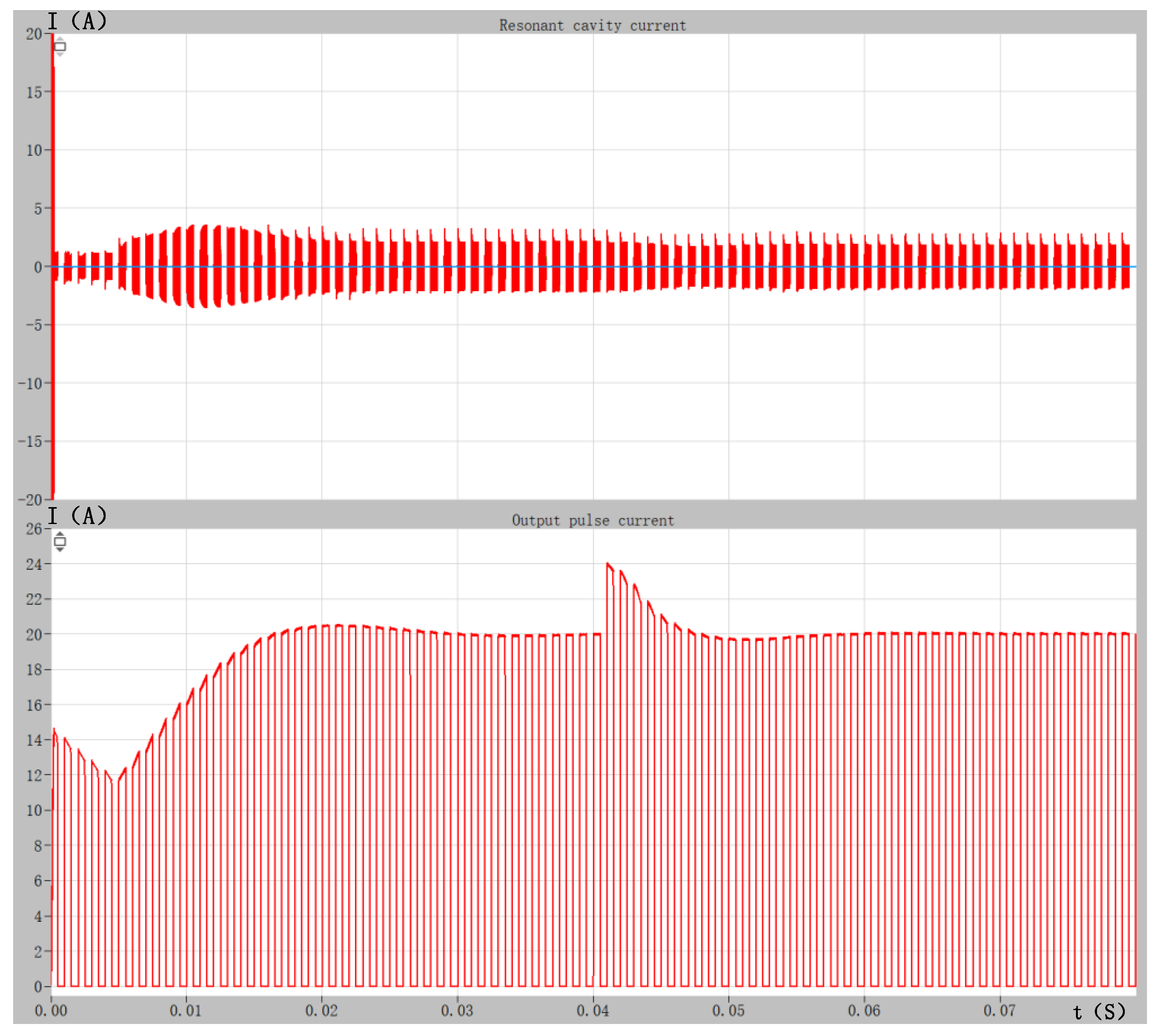

3.3. Pulse Current Closed-Loop Control Strategy

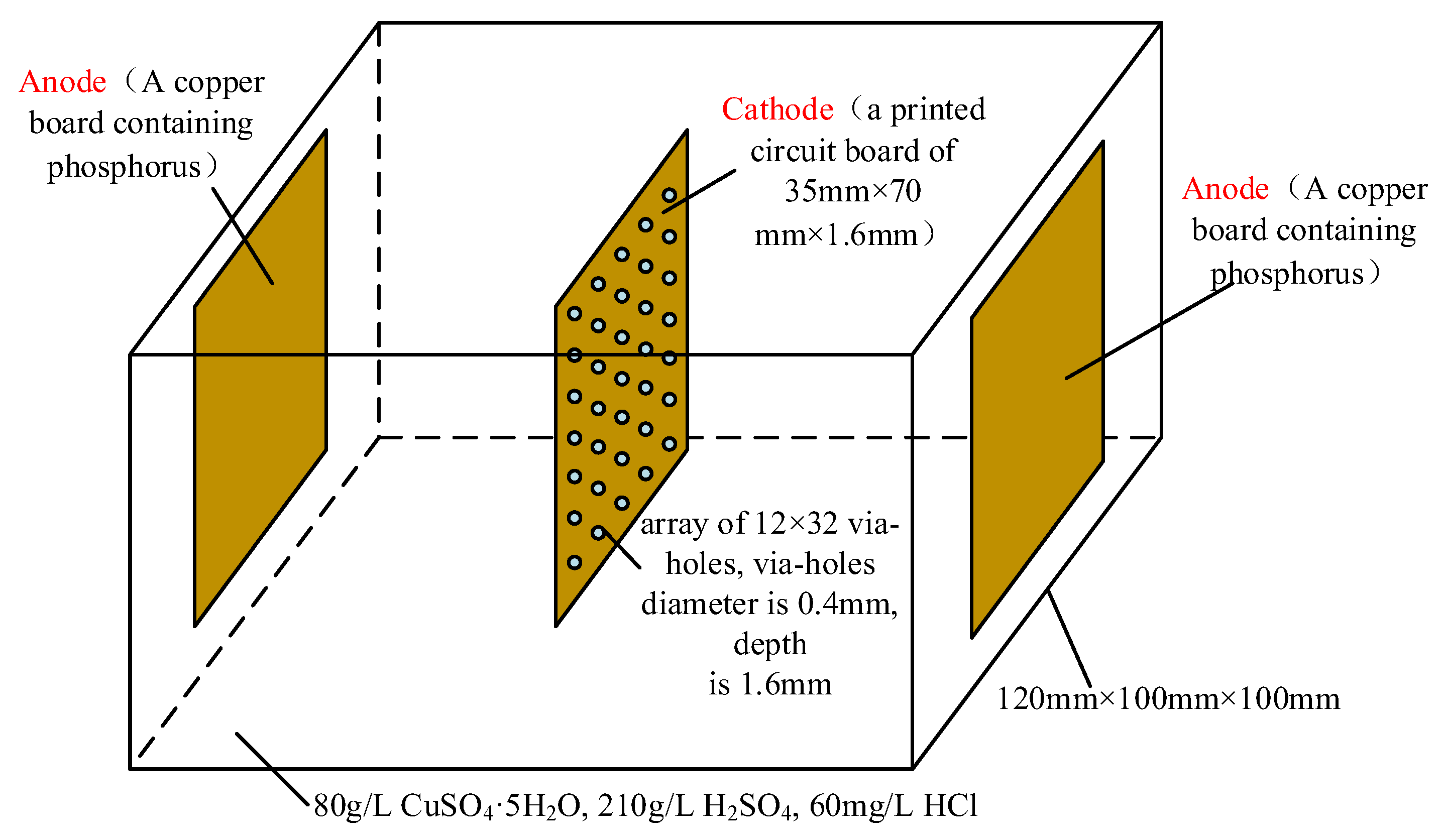

4. Plating Test Experiment

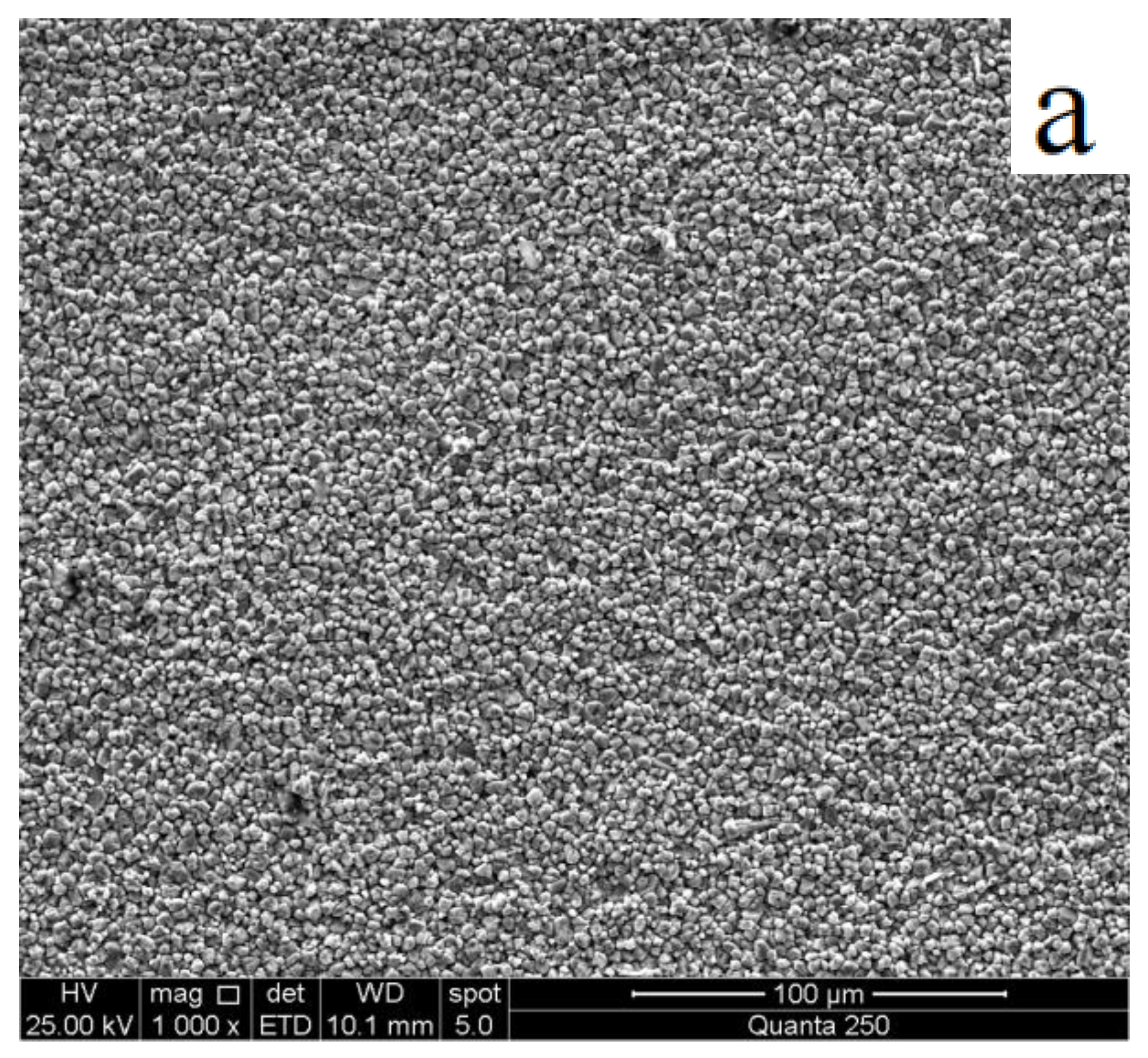

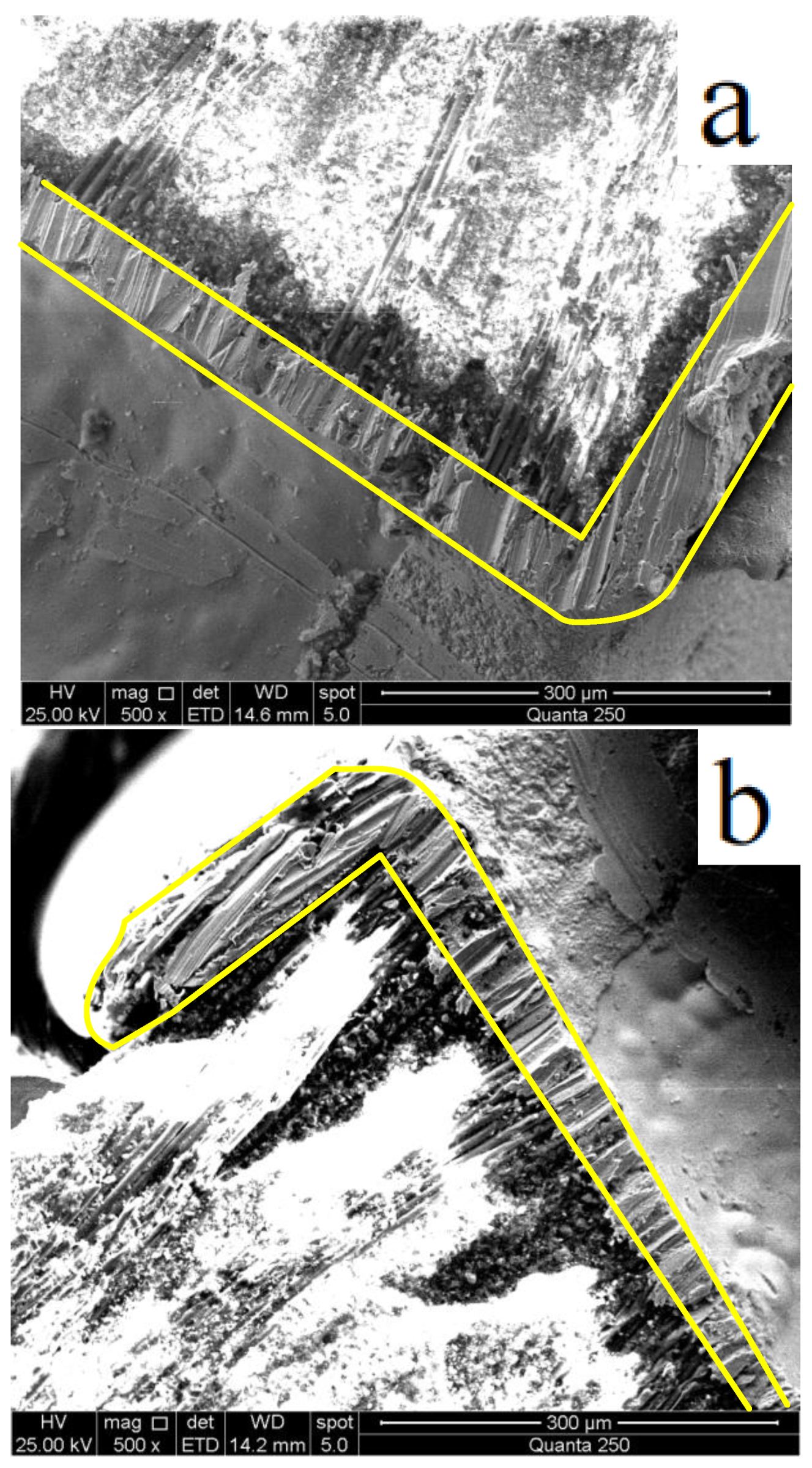

4.1. Comparison of The Effects of Pulse Plating and DC Plating on Via-Filling Copper Plating

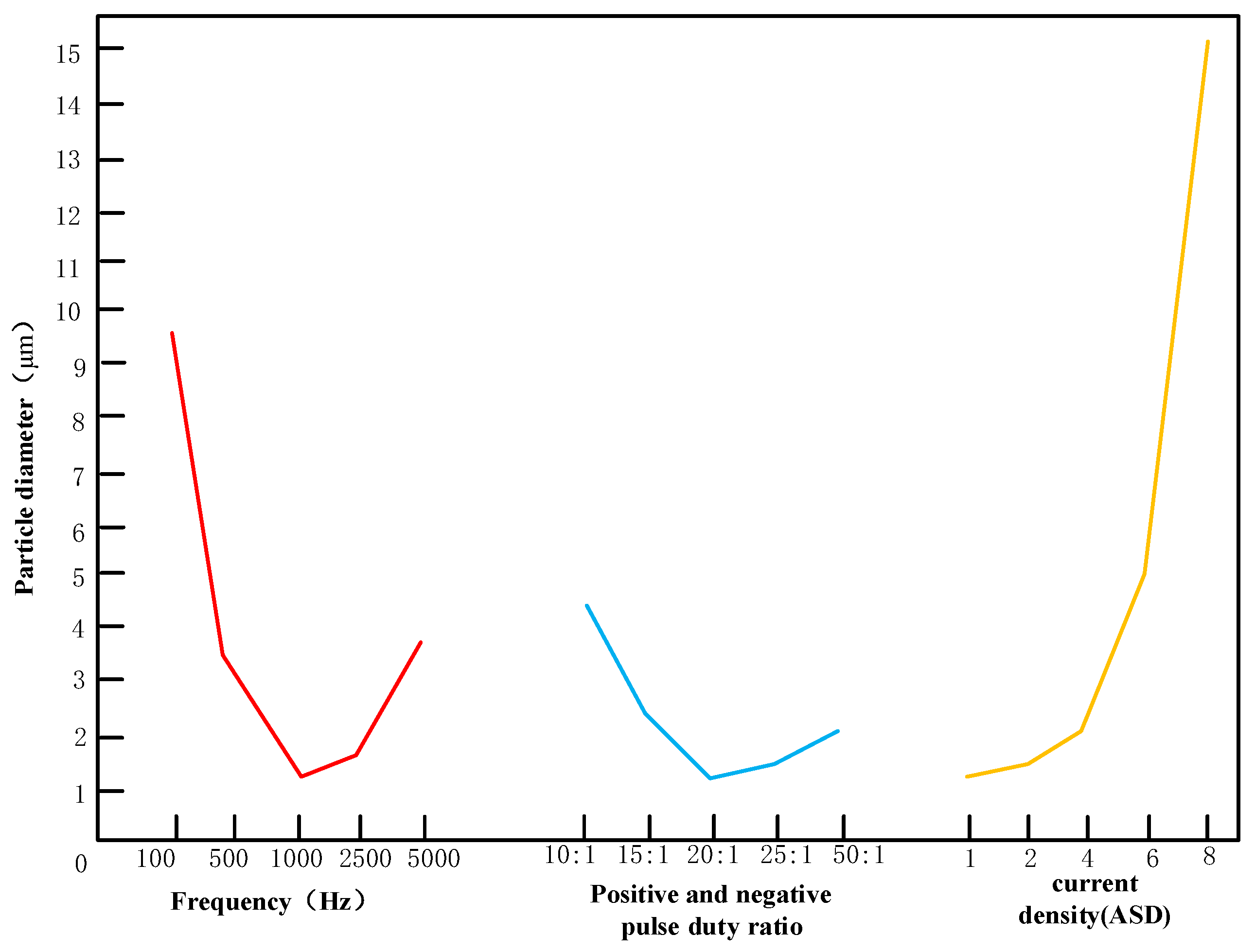

4.2. Effect of Pulse Plating Parameters on Via-Filling Copper Plating

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Jin, H.; Chen, S. Printed Circuit Technology; Chemical Industry Press: Beijing, China, 2003; pp. 1–6. [Google Scholar]

- Li, Y.; Wang, S.; Wang, W. Research Status of Micro-porous Copper Plating on PCB. Plat. Finish. 2007, 29, 32–35. [Google Scholar]

- Ozkok, M.; Lamprecht, S.; Ozkok, A. Filling of Micro-via and Through Holes by Electrolytic Copper Plating-Current Status and Future Outlook. In Proceedings of the 13th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), Taipei, China, 16–18 October 2016; pp. 83–88. [Google Scholar]

- Chen, S.J.; Xu, J.; Luo, X. Factors influencing the effect of blind hole filling by electroplating on printed circuit board. Plat. Finish. 2012, 31, 33–37. [Google Scholar]

- Liu, X.; Luo, Y. Application of Pulse Electroplating in Micro blind Hole Filling. Print. Circuit Inf. 2004, 7, 42–45. [Google Scholar]

- Andricacos, P.; Uzoh, C.; Dukovic, J. Dama-scene copper electroplating for chip interconnections. IBM J. Res. Dev. 1998, 42, 567–574. [Google Scholar] [CrossRef]

- Moffat, T.; Bonevich, J.; Huber, W. Superconducting electrode position of copper in 500–900 nm features. Electrochemical 2000, 147, 4524–4535. [Google Scholar] [CrossRef]

- Moffat, T.; Wheeler, D.; Huber, W. Super-conformal electrode position of copper. Electrochemical 2001, 4, C26–C29. [Google Scholar]

- Soukane, S.; Sen, S.; Cale, T. Feature super-filling in copper electrochemical deposition. Electrochemical 2002, 149, C74–C81. [Google Scholar] [CrossRef]

- Yang, K.; Chen, J.; Chen, S. Optimization of additives and electroplating parameters for high aspect ratio through-hole pulse electroplating. Electrochemistry 2022, 28, 9. [Google Scholar]

- Niu, T.; Li, H.; Cui, K. High aspect ratio TSV hole filling electroplating technology. Electromech. Eng. 2020, 36, 55–59. [Google Scholar]

- Dou, W. Application of filling micron blind holes and through holes with electroplated copper. J. Od Fudan Univ. 2012, 51, 131–138. [Google Scholar]

- Hao, P.; Lu, Q.; Wang, D. New HDI blind hole filling copper electroplating technology. Spec. Equip. Electron. Ind. 2021, 2, 33–36. [Google Scholar]

- Kobayashi, T.; Kawasaki, J.; Mihara, K. Via-filling Using Electroplating for Build-up PCBs. Electrochem. Acta 2001, 47, 85–89. [Google Scholar] [CrossRef]

- Shen, F.; Dow, W.; Liu, A. Periodic Pulse Reverse Cu Plating for Through-Hole Filling. ECS Electrochem. Lett. 2013, 2, D23–D25. [Google Scholar] [CrossRef]

- An, W.; Zeng, F.; Li, J. Application of pulse electroplating in printed circuit board. Electron. Process Technol. 2021, 42, 20–22. [Google Scholar]

- Park, S.; Shin, N.; Lee, C. Au Coated Printed Circuit Board Current Collectors Using a Pulse Electroplating Method for Fuel Cell Applications. Energies 2021, 14, 12–17. [Google Scholar] [CrossRef]

- Liang, P.; Zhang, X.; Wang, K. Development of bidirectional pulse copper plating programmable switching power supply for printed circuit board. Electroplat. Finish. 2019, 41, 31–35. [Google Scholar]

- Lei, T.; Yuan, X.; Wang, C. Effect of Two way Pulse Parameters on the Morphology and Structure of Gold Casting Layer. Rare Met. Mater. Eng. 2016, 45, 1257–1263. [Google Scholar]

- Yu, T. Pulse Electroplating of Ultra-Fine Grained Zinc Coating on 316L Stainless Steel and its Corrosion Behaviors. Int. J. Electrochem. Sci. 2019, 1, 5913–5922. [Google Scholar]

- Wang, S.; Shi, L.; Pen, B. Design and Implementation of A digitally-controlled Phase-shift Full-bridge Converter with Output Synchronous Rectifier and Current Doubles. J. Technol. 2017, 32, 283–297. [Google Scholar]

- Klotzer, S.; Thielke, F.; Warncke, M. Analysis of an LLC Converter with Planar Inverse Coupled Current Doubles Rectifier using Silicon and GaN Devices. In Proceedings of the 21st European Conference on Power Electronics and Applications (EPE ′19 ECCE Europe), Genova, Italy, 3–5 September 2019; pp. 1531–1540. [Google Scholar]

- Sun, L.; He, J.; Pei, Y. Design and Optimization of High Current Intelligent Waveform Power Supply for Electroplating. In Proceedings of the 7th International Power Electronics and Motion Control Conference (IPEMC 2012), Harbin, China, 2–5 June 2012; pp. 1516–1521. [Google Scholar]

- Zeng, W.; Yu, L.; Dong, S.; Ma, J.; Wang, Y.; He, Y.; Wang, X.; Yao, C. A novel high frequency bipolar pulsed power generator for biological applications. IEEE Trans. Power Electron. 2020, 1, 13–17. [Google Scholar] [CrossRef]

- Li, J.; Yuan, X. Hybrid control strategy of full bridge LLC resonant converter. J. Electr. Technol. 2013, 28, 72–79. [Google Scholar]

- Guan, S.; Chen, Q. Working principle and external characteristic analysis of PWM controlled LLC converter. Power Electron. 2012, 46, 55–57. [Google Scholar]

- Hu, H.; Wang, W.; Sun, W. Efficiency optimization design of LLC resonant converter. Chin. J. Electr. Eng. 2013, 19, 12–16. [Google Scholar]

- Kim, J.; Kim, D.; Kim, C. A simple switching control technique for improving light load efficiency in a phase-shifted full-bridge converter with a server power system. IEEE Trans. Power Electron. 2014, 29, 1562–1566. [Google Scholar] [CrossRef]

- Chen, X.; Wang, Y.; He, W. Application of forward and reverse pulse electroplating in communication backplane via interconnection. Print. Circuit Inf. 2021, 29, 7–11. [Google Scholar]

- Han, Y.; Nie, Z.; Zhu, J. Research on low-voltage high current DC converter based on phase shifted full bridge ZVS and synchronous rectification. Electr. Autom. 2016, 38, 7–10. [Google Scholar]

- Teng, S.; Wang, X.; Liu, H. A large current low-voltage power supply with pre charging ”soft start” rectification. Light Ind. Technol. 2021, 7, 75–78. [Google Scholar]

- Wang, X.; Wang, X.; Zou, Y. Double peak pulse electroplating power supply basad on fuzzy PID control. Mob. Power Supply Veh. 2008, 2, 45–47. [Google Scholar]

- Zhou, H.; Tan, C.; Fletcher, J. Lossless bidirectional current sense circuit for low-voltage high-current DC/DC converters. In Proceedings of the 44th Annual conference of the IEEE industrial electronics society, Washington, DC, USA, 21–23 October 2018; pp. 71–73. [Google Scholar]

- Lin, B. Resonant converter for high-input voltage and high-output current applications. IETE J. Res. 2018, 64, 865–872. [Google Scholar] [CrossRef]

- Huang, J.; Ruan, X.; Du, F. A pulsed power supply adopting active capacitor converter for low-voltage and low-frequency pulsed load. IEEE Trans. Power Electron. 2018, 11, 9219–9230. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, W.; Wang, S.; Liu, Z.; Wei, C.; Peng, Y. Development of Bidirectional Pulsed Power Supply and Its Effect on Copper Plating Effect of Printed Circuit Board Via-Filling. Electronics 2023, 12, 631. https://doi.org/10.3390/electronics12030631

Chen W, Wang S, Liu Z, Wei C, Peng Y. Development of Bidirectional Pulsed Power Supply and Its Effect on Copper Plating Effect of Printed Circuit Board Via-Filling. Electronics. 2023; 12(3):631. https://doi.org/10.3390/electronics12030631

Chicago/Turabian StyleChen, Wenguang, Shoutao Wang, Zhijian Liu, Caiyi Wei, and Yuanyuan Peng. 2023. "Development of Bidirectional Pulsed Power Supply and Its Effect on Copper Plating Effect of Printed Circuit Board Via-Filling" Electronics 12, no. 3: 631. https://doi.org/10.3390/electronics12030631

APA StyleChen, W., Wang, S., Liu, Z., Wei, C., & Peng, Y. (2023). Development of Bidirectional Pulsed Power Supply and Its Effect on Copper Plating Effect of Printed Circuit Board Via-Filling. Electronics, 12(3), 631. https://doi.org/10.3390/electronics12030631