Design Methodology and Metrics for Robust and Highly Qualified Security Modules in Trusted Environments

Abstract

:1. Introduction

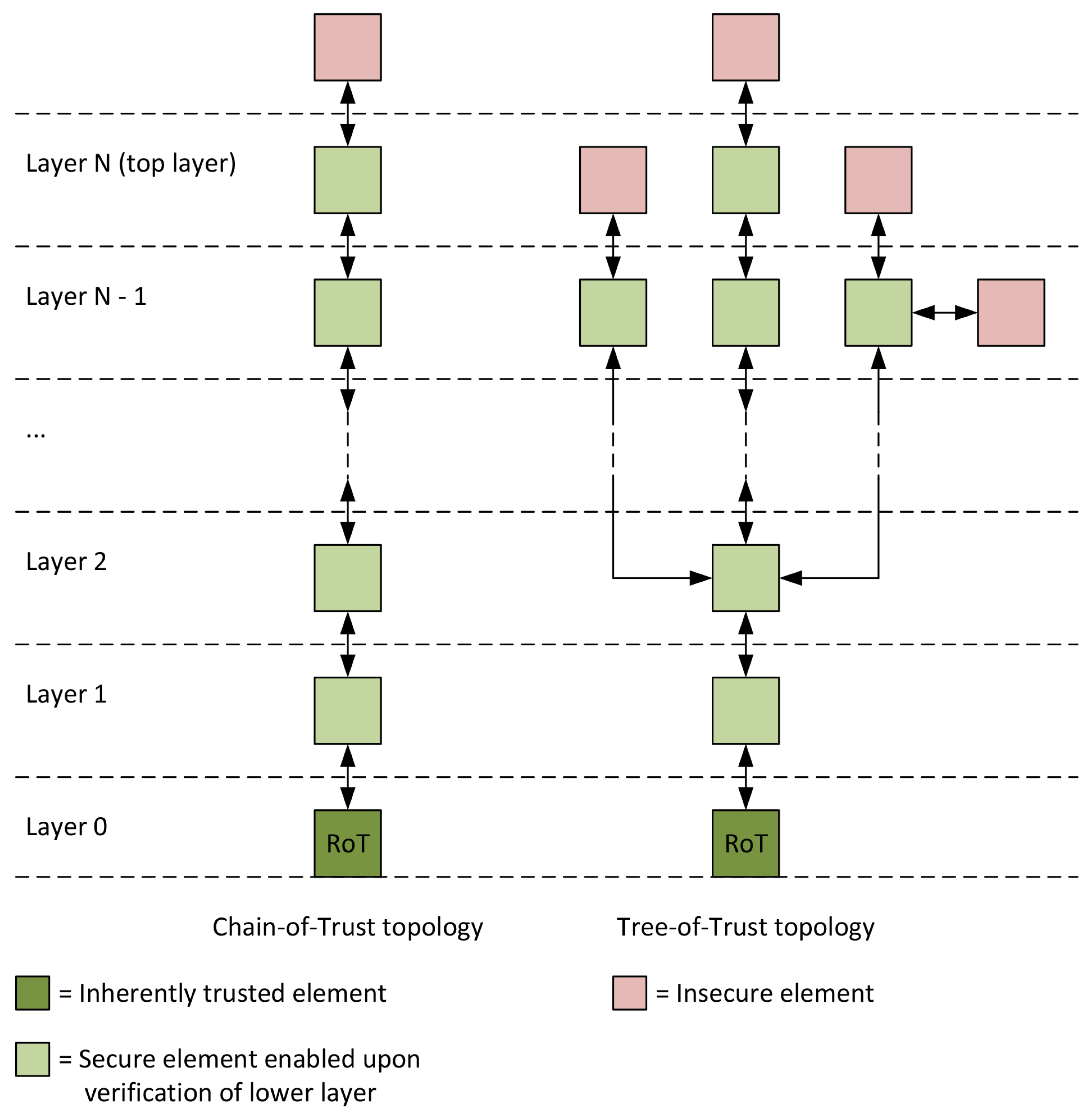

2. Definitions, Principles, and Outline of Roots-of-Trust and Trusted Environments

- Secure Boot and Initialization. The RoT ensures that a computer system starts up securely. It verifies the integrity of the bootloader and firmware during the boot process, ensuring no malicious code has been injected into these critical components. This helps prevent firmware-level attacks and rootkits from compromising the system.

- Code and Data Authentication. The RoT mechanisms can be used to authenticate and verify the integrity of software applications and data. This ensures that only trusted and authorized code and data are executed or accessed on a system.

- Cryptographic Operations. The RoT often includes cryptographic capabilities and can generate and manage cryptographic keys. This is crucial for secure communication, data encryption, and authentication between different system components and devices.

- Secure Storage. Some RoT implementations provide secure storage for sensitive data, such as cryptographic keys or biometric templates, ensuring that this data cannot be easily tampered with or stolen.

- Remote Attestation. The RoT can be used for remote attestation, allowing a system to prove its trustworthiness to remote entities. This is particularly important in scenarios like cloud computing, where a remote server needs assurance that a client device is secure before granting access.

- Hardware-Based Security. Many RoT implementations are designed to be tamper-resistant and are stored in secure hardware modules, making it difficult for attackers to compromise their integrity.

- Trust in Supply Chain. The RoT can establish trust in the supply chain by ensuring that hardware components and software are genuine and have not been tampered with during manufacturing, distribution, or deployment.

- Protecting Against Insider Threats. The RoT can also help protect against insider threats by limiting access to sensitive information and functions based on authentication and authorization policies.

3. State of the Art of RoT-Based Trusted Environments

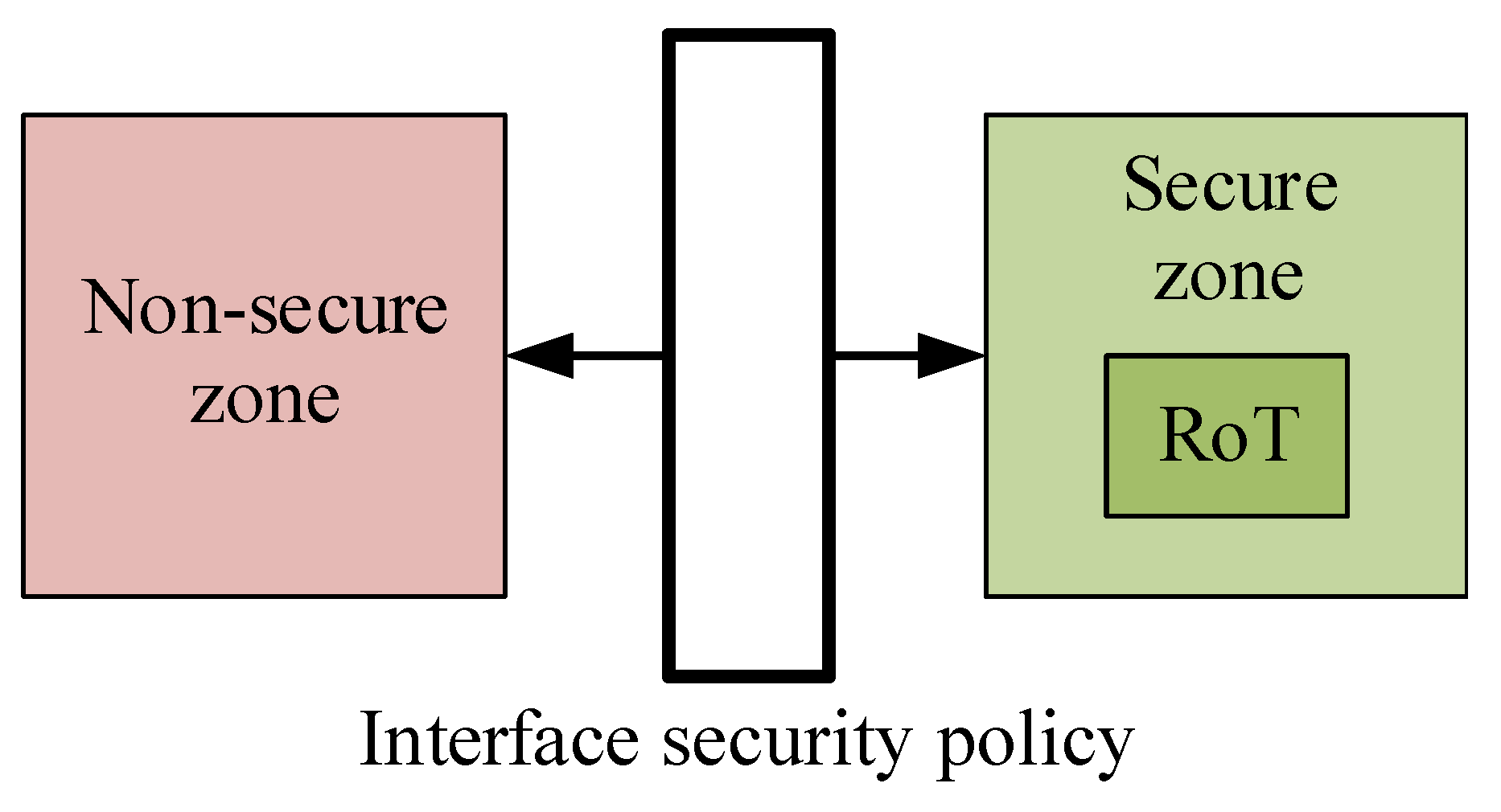

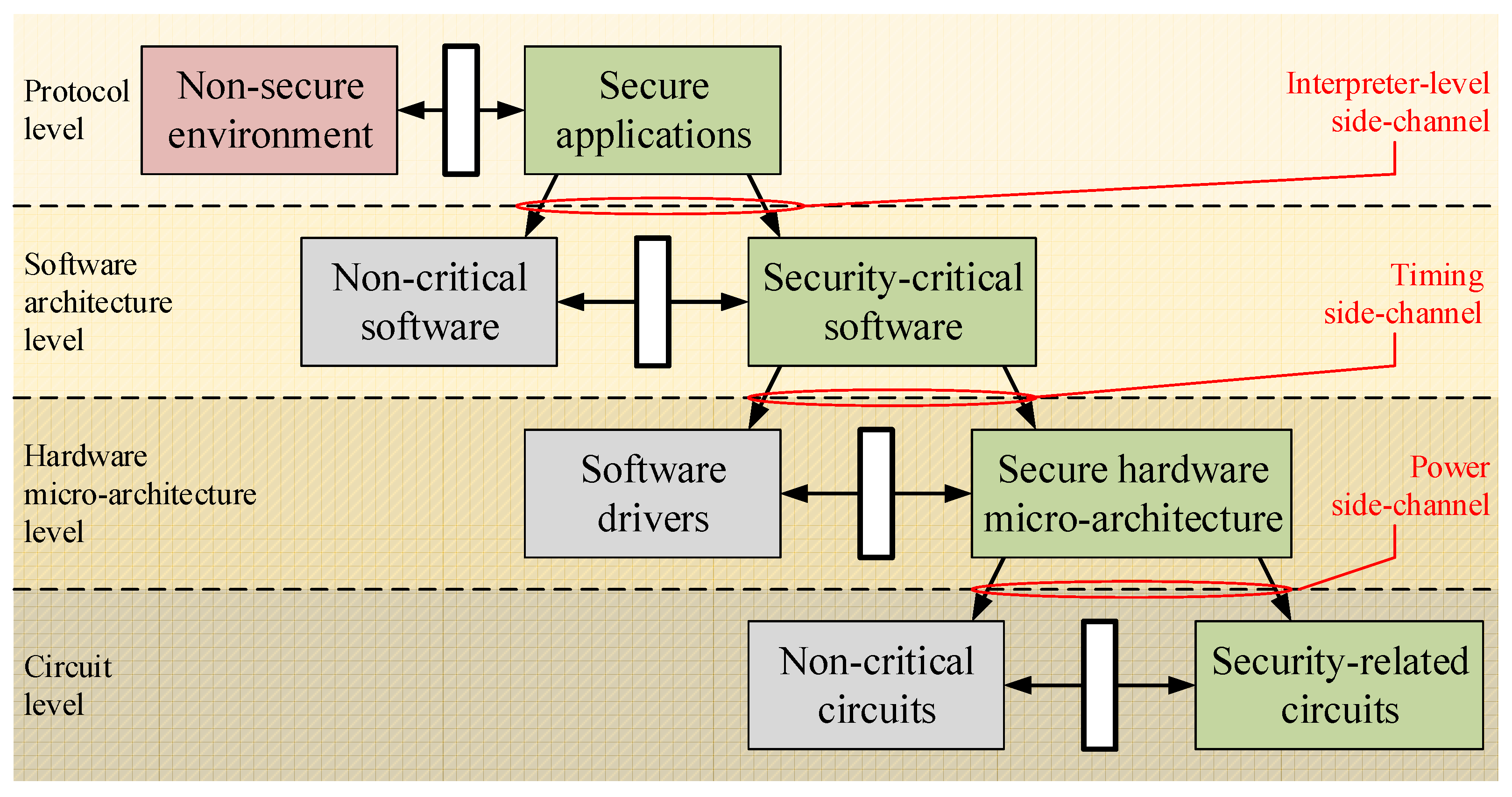

4. Design Methodologies and Key Aspects for Security Modules in Secure Zones

- the Security Services and Functions;

- the Interface Security Policy;

- the Physical Implementation.

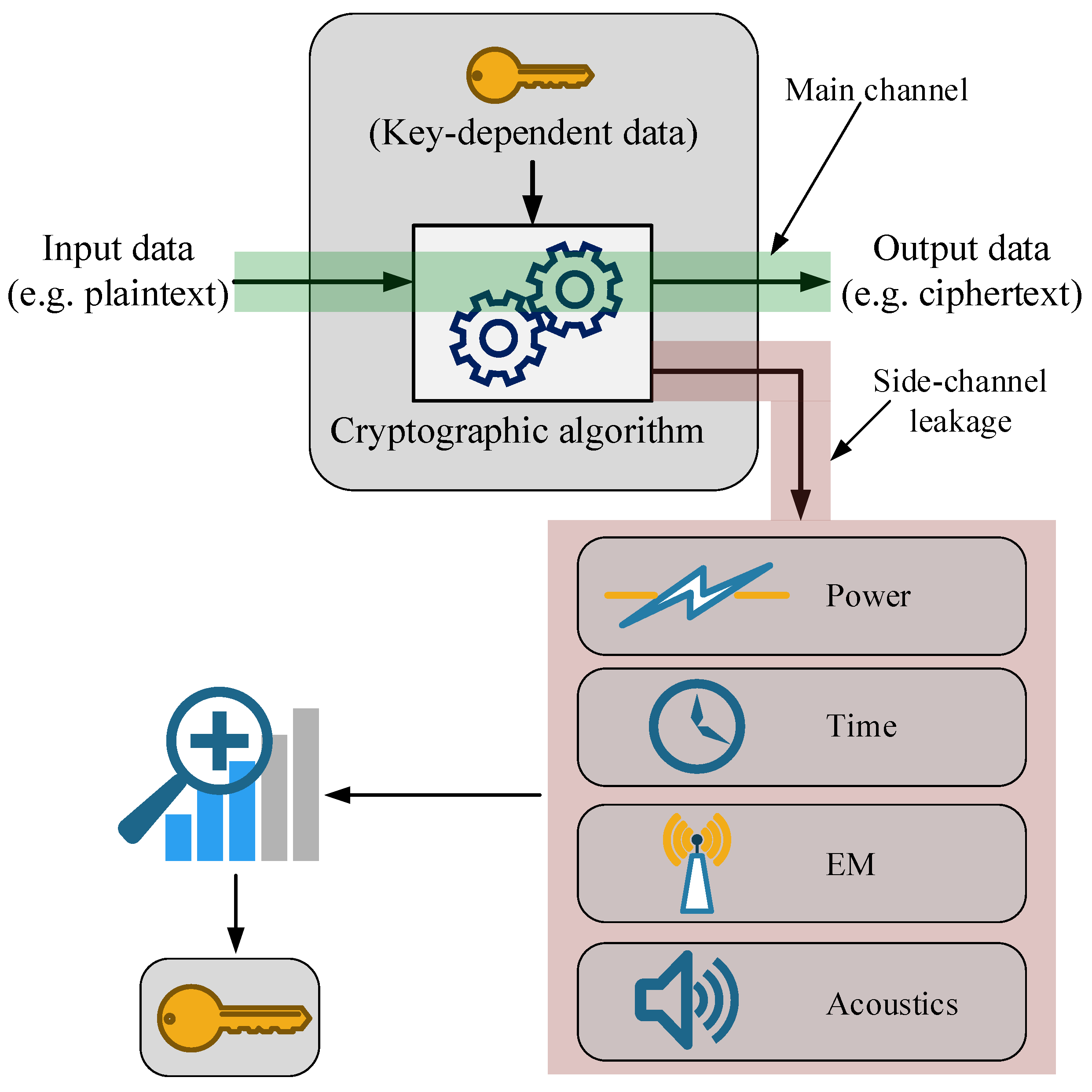

- Cache attack [47,48,49]: This class of attacks is based on monitoring cache accesses in a shared physical system and, as the name suggests, it is mostly applied to software contexts. The protection strategies usually consist of replacing the LUTs with a series of equivalent logical operations, using alternative forms of LUTs, or creating an obvious memory access pattern (i.e., reading all LUT values in a fixed order and using only the one needed) [47,48].

- Timing attack [50,51,52,53]: This category of attacks concentrates on measuring the execution time of routines, targeting software implementations in which different instructions, branches, RAM cache hits, etc., cause time variation in the process. The protection mechanisms typically involve techniques for time equalization and reduction of unpredictable events (such as cache misses, etc.), or insertion of random delays [51,52,53].

- Power analysis [53,54,55,56,57,58,59,60,61,64,65]: This family of attacks is one of the most effective on both hardware and software implementations, and it exploits the power consumption of underlying physical circuits. Concerning the software case, if each opcode of the instruction set architecture can be associated with a different and specific power trace shape, then the series of operations performed by a routine is revealed; on the hardware side, data dependencies over different power traces can be analyzed to recover secret information. The most notorious attack classes of this group are Single Power Analysis (SPA), Differential Power Analysis (DPA), and Correlation Power Analysis (CPA). The first one consists of recovering data values by just observing the shape of a power trace; for instance, in a branched architecture where a certain value of processed information activates a certain branch rather than another one, isolating the branch-specific power profile within a power trace makes it possible to recover the sequence of 0s and 1s. DPA and CPA attacks instead are more sophisticated, and they employ statistical methods to disclose secret information. As can be intuited from what has been expressed so far, each of these attacks requires a certain knowledge of architecture, especially in the case of DPA and CPA, which typically make use of a power consumption model to make a guess of the value of processed data: the further the model from the real architecture, the weaker the guess. For power analysis attacks, the countermeasures usually are implemented by adopting two techniques, masking or hiding, or a mix of both. The former is aimed to reduce or eliminate the dependencies between data and power consumption; the latter instead is aimed to jam the Side-Channel with noise in order to reduce the signal-to-noise ratio of leaked information. Masking typically introduces significant overhead in terms of area and critical path, by requiring up to 5 times the amount of logic resources employed by the unprotected module, and lowering the maximum frequency of the circuit up to 2/3 times [53,56,59,61,65]. On the other hand, hiding usually is realized by coupling the unprotected module in parallel to a block dedicated to noise generation, thus the critical path of the circuit is not affected and the overhead of resources is limited. In that case, the most significant cost concerns are the power consumption, which can introduce an overhead of up to 5 times larger [54,55,57].

- Electromagnetic analysis [62]: This category of attacks relies on leaked electromagnetic radiation. It is usually assimilated to the class of power analysis attack, under the rough assumption that electromagnetic radiation is highly correlated (or proportional) to power consumption. Therefore, attacks and defense mechanisms are developed accordingly to the one of power analysis, using electromagnetic probes, instead of an instrument to measure the current.

- Differential fault analysis [63]: This type of attack has the purpose of discovering secrets by introducing faults while the system is running normally. The corresponding protection mechanisms typically involve architectural redundancy approaches and techniques for concurrent error detection.

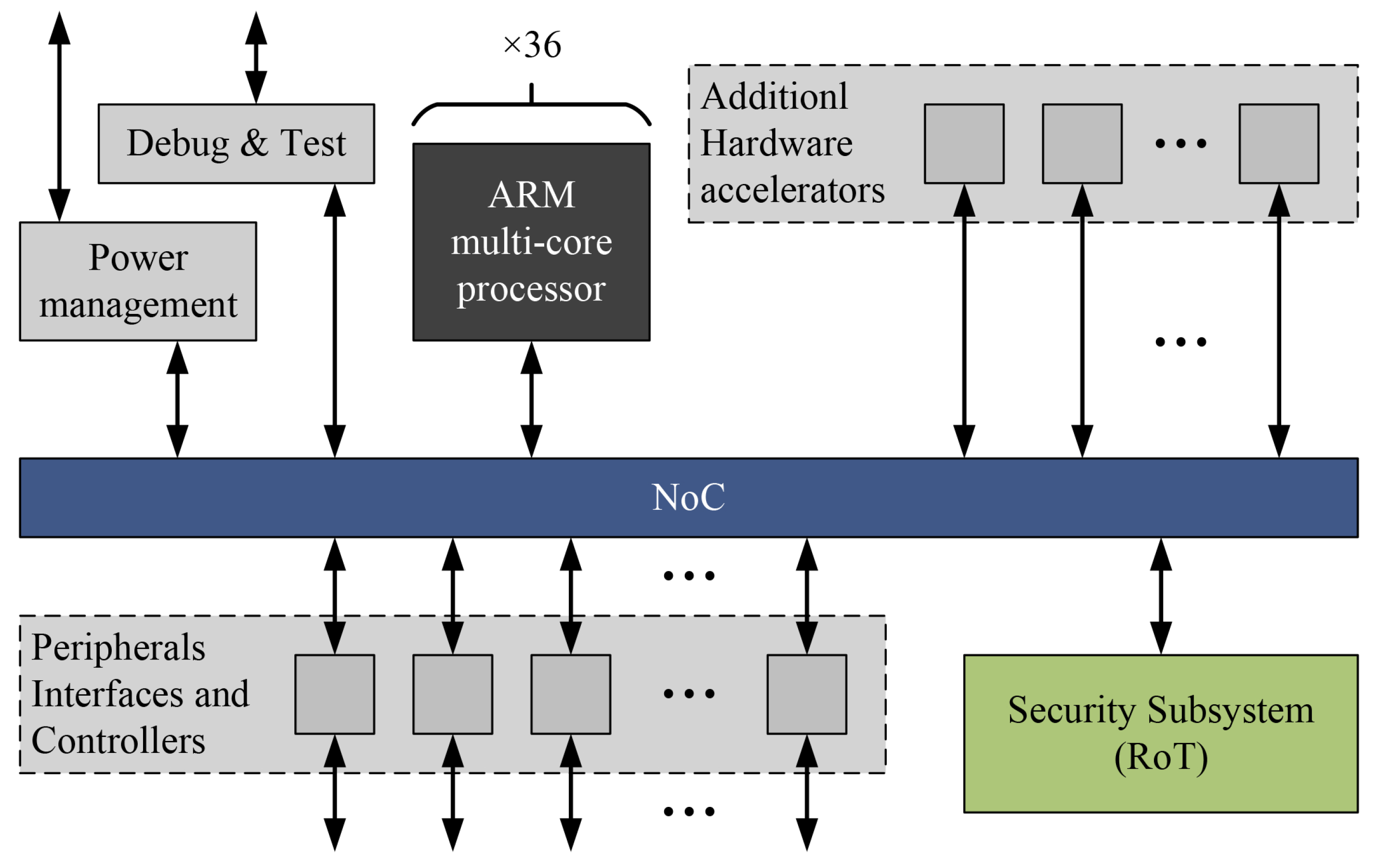

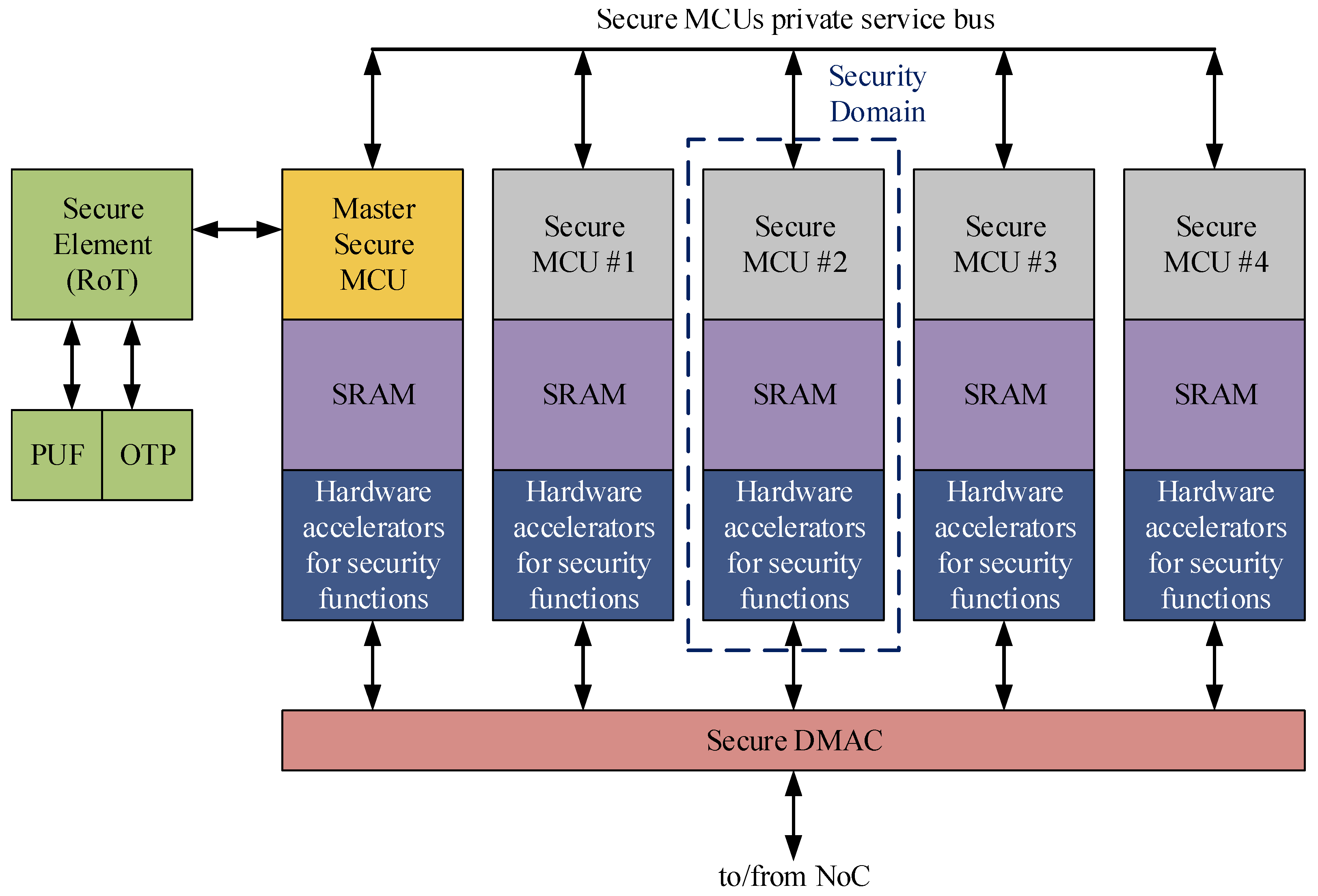

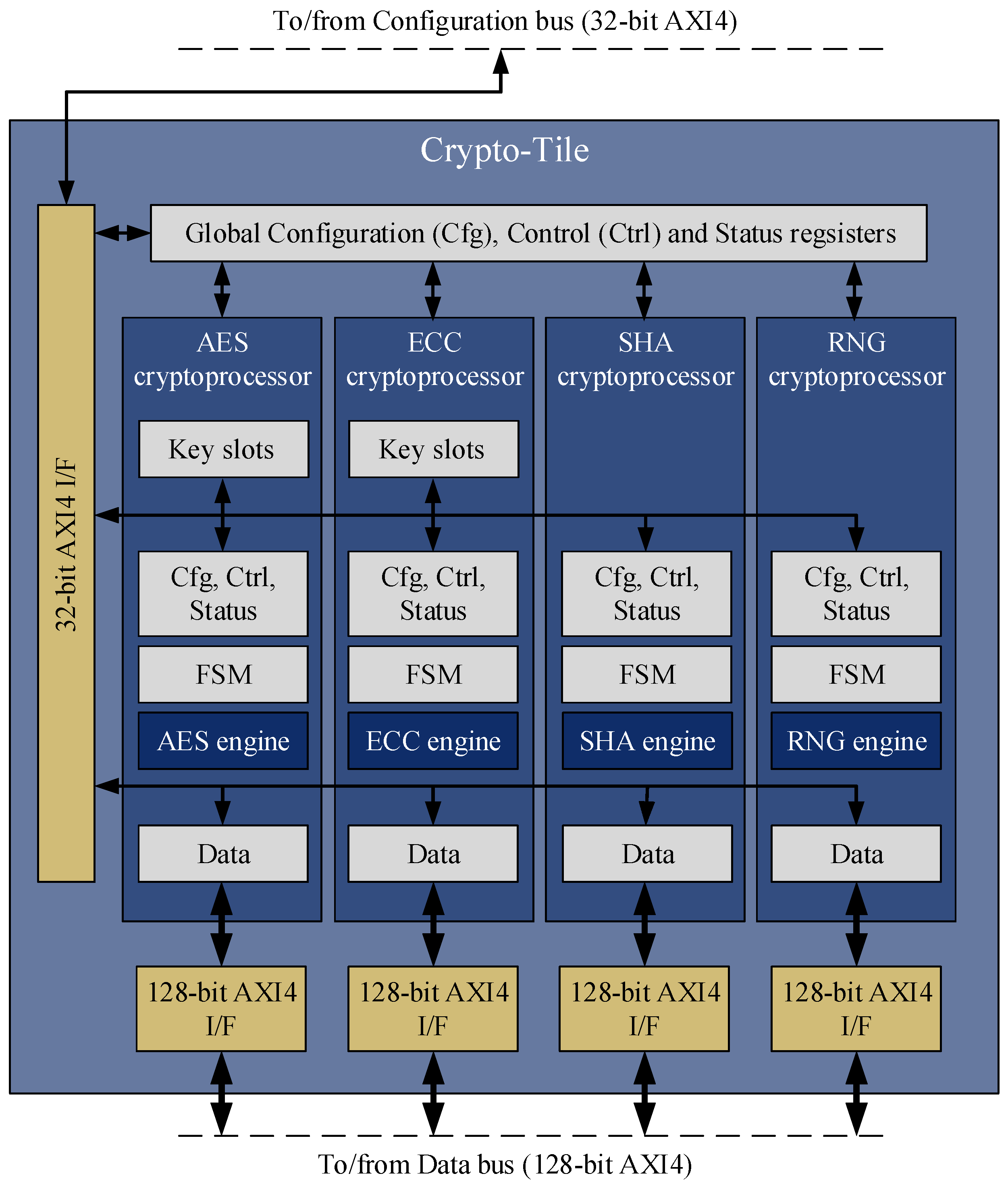

5. Case Study: Cryptographic Hardware Coprocessor for the Secure Subsystem of Rhea GPP

5.1. Security Services

- A coprocessor for symmetric-key cryptography based on the Advanced Encryption Standard (AES) algorithm [17]. This coprocessor offers:

- –

- Confidentiality, through the AES modes operation Electronic CodeBook (ECB), Cipher Block Chaining (CBC), Cipher FeedBack (CFB), Output FeedBack (OFB), and CounTeR (CTR) [70];

- –

- Authenticated Integrity, through the AES mode of operation Cipher-based Message Authentication Code (CMAC) [71];

- –

- –

- Disk encryption, through the AES mode of operation XEX encryption mode with Tweak and ciphertext Stealing (XTS) [75].

For each of the listed modes of operation, the AES coprocessor supports both 128-bit and 256-bit keys, respectively providing a corresponding security level of 128 and 256 bits [43]. - A coprocessor for public-key cryptography based on Elliptic Curve Cryptography (ECC) [16]. This coprocessor offers:

- –

- Acceleration of computationally intensive arithmetic operations over elliptic curves, such as Point Addition and Point Doubling;

- –

- Generation of private keys, key pairs (both private and public), and derivation of corresponding public keys starting from private keys;

- –

- Authentication and non-repudiation, through the Elliptic Curve Digital Signature Algorithm (ECDSA) [76].

For each of the listed functions, the ECC coprocessor supports both 256-bit and 521-bit elliptic curves, in particular the NIST P-256 and the NIST P-521, that provide, respectively, a corresponding security strength of 128 and 256 bits [43]. - A coprocessor for hash functions based on the Secure Hash Algorithm (SHA) [18]. This coprocessor offers integrity through the algorithms SHA2 [77] and SHA-3 [78]. For both the SHA functions, the supported digest sizes are 224, 256, 384, and 512 bits, providing a corresponding security level of 128 (256-bit digest) and 256 (384-bit digest) bits [43].

- A coprocessor for Random Number Generation (RNG). This coprocessor offers:

- –

- Generation of high-entropy key-related material and seeds, through a True Random Number Generator (TRNG) [19];

- –

- Generation of key-related material, non-repeating values, and initialization vectors through a Cryptographically Secure Pseudo-Random Number Generator (CSPRNG) [79], which is seeded thanks to the TRNG.

5.2. Interface Security Policy

- Global Crypto-Tile level: this level concerns the global configuration of the Crypto-Tile;

- Cryptographic Operation level: this level concerns data that are processed during the execution of the cryptographic operations;

- Key material level: this level concerns the keys, their installation in dedicated registers inside the Crypto-Tile, and their storage, access, and utilization statistics.

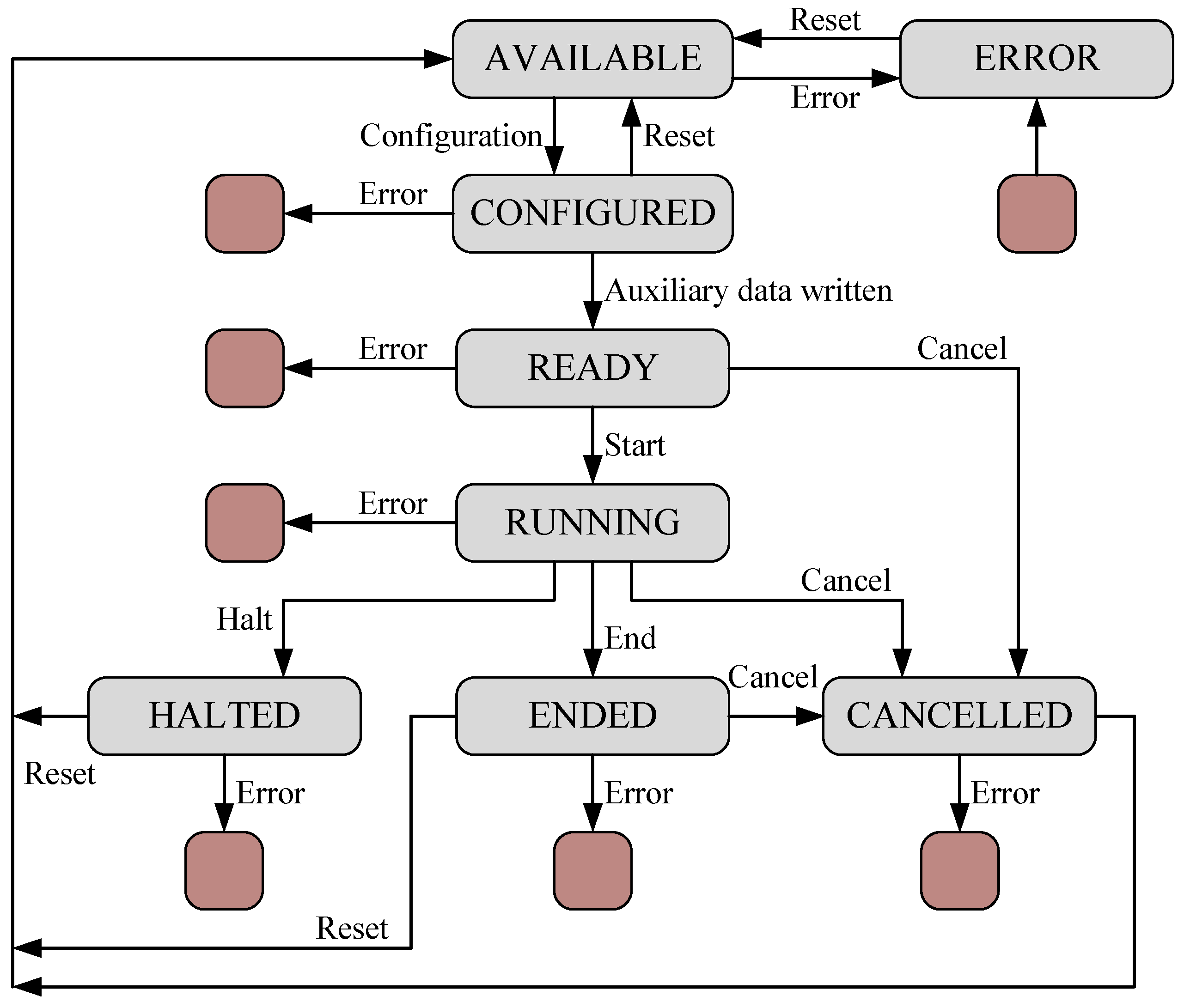

5.3. Physical Implementation

5.4. Comparison with Existing TEEs

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| AES | Advanced Encryption Standard |

| AI | Artificial Intelligence |

| AXI | Advanced eXtensible Interface |

| BSI | Bundesamt für Sicherheit in der Informationstechnik |

| CAVP | Cryptographic Algorithm Validation Program |

| CBC | Cipher Block Chaining |

| CFB | Cipher FeedBack |

| CCM | Counter with CBC-MAC |

| CMAC | Cipher-based Message Authentication Code |

| CMRT | CryptoManager Root-of-Trust |

| CoT | Chain-of-Trust |

| CPA | Correlation Power Analysis |

| CPU | Central Processing Unit |

| CTR | CounTeR |

| CSPRNG | Cryptographically Secure Pseudo-Random Number Generator |

| DoS | Denial-of-Service |

| DPA | Differential Power Analysis |

| ECB | Electronic CodeBook |

| ECC | Elliptic Curve Cryptography |

| ECIES | Elliptic Curve Integrated Encryption Scheme |

| ECDH | Elliptic Curve Diffie-Hellman |

| ECDSA | Elliptic Curve Digital Signature Algorithm |

| ECMQV | Elliptic Curve Menezes-Qu-Vanstone |

| EM | Electromagnetic Emission |

| EMA | Electromagnetic Emission Analysis |

| EPC | Enclave Page Cache |

| EPCM | Enclave Page Cache Map |

| EPI | European Processor Initiative |

| FSM | Finite State Machine |

| GCM | Galois Counter Mode |

| GE | Gate Equivalent |

| GPIO | General Purpose Input/Output |

| GPP | General Purpose Processor |

| HIEE | Hardware-assisted Isolated Execution Environment |

| HMAC | Hash-based Message Authentication Code |

| HPC | High-Performance Computing |

| HSM | Hardware Security Module |

| HW | Hardware |

| IEEE | Institute of Electrical and Electronics Engineers |

| IoT | Internet-of-Things |

| LUT | Look-Up Table |

| MAC | Message Authentication Code |

| MCU | Master Control Unit |

| NIST | National Institute of Standard and Technology |

| OFB | Output FeedBack |

| OTP | One-Time Programmable |

| PQC | Post-Quantum Cryptography |

| PSP | Platform Security Processor |

| RISC | Reduced Instruction Set Computer |

| RNG | Random Number Generator |

| RoT | Root-of-Trust |

| SCA | Side-Channel Attack |

| SGX | Software Guard eXtensions |

| SoC | System-on-Chip |

| SHA | Secure Hash Algorithm |

| SPA | Simple Power Analysis |

| SRAM | Secure RAM |

| SW | Software |

| TEE | Trusted Execution Environment |

| TZASC | TrustZone Address Space Controller |

| TZMA | TrustZone Memory Adapter |

| UART | Universal Asynchronous Receiver-Transmitter |

| UEFI | Unified Extensible Firmware Interface |

| XTS | XEX encryption mode with Tweak and ciphertext Stealing |

References

- Duo, W.; Zhou, M.; Abusorrah, A. A Survey of Cyber Attacks on Cyber Physical Systems: Recent Advances and Challenges. IEEE/CAA J. Autom. Sin. 2022, 9, 784–800. [Google Scholar] [CrossRef]

- Igbekele Emmanuel, O.; Ekele Victoria, C.; Omonigho Efeoghene, I.; Nwachuwku Praise, C. Overview of Recent Cyberattacks: A Systematic Review. In Proceedings of the 2023 International Conference on Science, Engineering and Business for Sustainable Development Goals (SEB-SDG), Omu-Aran, Nigeria, 5–7 April 2023; Volume 1, pp. 1–8. [Google Scholar] [CrossRef]

- Li, Y.; Liu, Q. A comprehensive review study of cyber-attacks and cyber security; Emerging trends and recent developments. Energy Rep. 2021, 7, 8176–8186. [Google Scholar] [CrossRef]

- Sabt, M.; Achemlal, M.; Bouabdallah, A. Trusted Execution Environment: What It is, and What It is Not. In Proceedings of the 2015 IEEE Trustcom/BigDataSE/ISPA, Helsinki, Finland, 20–22 August 2015; Volume 1, pp. 57–64. [Google Scholar] [CrossRef]

- Hoang, T.T.; Duran, C.; Serrano, R.; Sarmiento, M.; Nguyen, K.D.; Tsukamoto, A.; Suzaki, K.; Pham, C.K. Trusted Execution Environment Hardware by Isolated Heterogeneous Architecture for Key Scheduling. IEEE Access 2022, 10, 46014–46027. [Google Scholar] [CrossRef]

- Crocetti, L.; Di Rienzo, R.; Verani, A.; Baronti, F.; Roncella, R.; Saletti, R. A Novel and Robust Security Approach for Authentication, Integrity, and Confidentiality of Lithium-ion Battery Management Systems. In Proceedings of the 2023 IEEE 3rd International Conference on Industrial Electronics for Sustainable Energy Systems (IESES), Shanghai, China, 26–28 July 2023. [Google Scholar] [CrossRef]

- Zhang, N.; Sun, K.; Shands, D.; Lou, W.; Hou, Y.T. TruSpy: Cache Side-Channel Information Leakage from the Secure World on ARM Devices. IACR Cryptol. ePrint Arch. 2016, 2016, 980. [Google Scholar]

- Lipp, M.; Gruss, D.; Spreitzer, R.; Maurice, C.; Mangard, S. Armageddon: Cache attacks on mobile devices. In Proceedings of the 25th USENIX Security Symposium (USENIX Security 16), Austin, TX, USA, 10–12 August 2016; pp. 549–564. [Google Scholar]

- Zhang, X.; Xiao, Y.; Zhang, Y. Return-Oriented Flush-Reload Side Channels on ARM and Their Implications for Android Devices. In Proceedings of the 2016 ACM SIGSAC Conference on Computer and Communications Security. Association for Computing Machinery, Vienna, Austria, 24–28 October 2016; pp. 858–870. [Google Scholar]

- Green, M.; Rodrigues-Lima, L.; Zankl, A.; Irazoqui, G.; Heyszl, J.; Eisenbarth, T. AutoLock: Why Cache Attacks on ARM Are Harder Than You Think. In Proceedings of the 26th USENIX Security Symposium USENIX Security 17), Vancouver, BC, Canada, 16–18 August 2017; pp. 1075–1091. [Google Scholar]

- Bukasa, S.K.; Lashermes, R.; Le Bouder, H.; Lanet, J.L.; Legay, A. How TrustZone could be bypassed: Side-channel attacks on a modern system-on-chip. In Proceedings of the Information Security Theory and Practice. WISTP, Heraklion, Greece, 28–29 September 2017; Lecture Notes in Computer Science (LNCS). Springer: Berlin/Heidelberg, Germany, 2018; Volume 10741, pp. 93–109. [Google Scholar]

- Longo, J.; De Mulder, E.; Page, D.; Tunstall, M. SoC It to EM: ElectroMagnetic Side-Channel Attacks on a Complex System-on-Chip. In Proceedings of the 17th International Workshop on Cryptographic Hardware and Embedded Systems (CHES), Saint-Malo, France, 13–16 September 2015; Lecture Notes in Computer Science (LNCS). Springer: Berlin/Heidelberg, Germany, 2015; pp. 620–640. [Google Scholar]

- Majéric, F.; Bourbao, E.; Bossuet, L. Electromagnetic security tests for SoC. In Proceedings of the 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), Monte Carlo, Monaco, 11–14 December 2016; pp. 265–268. [Google Scholar] [CrossRef]

- Nannipieri, P.; Crocetti, L.; DI Matteo, S.; Fanucci, L.; Saponara, S. Hardware Design of an Advanced-Feature Cryptographic Tile within the European Processor Initiative. IEEE Trans. Comput. 2023, 1–14. [Google Scholar] [CrossRef]

- Zulberti, L.; Di Matteo, S.; Nannipieri, P.; Saponara, S.; Fanucci, L. A Script-Based Cycle-True Verification Framework to Speed-Up Hardware and Software Co-Design: Performance Evaluation on ECC Accelerator Use-Case. Electronics 2022, 11, 3704. [Google Scholar] [CrossRef]

- Di Matteo, S.; Baldanzi, L.; Crocetti, L.; Nannipieri, P.; Fanucci, L.; Saponara, S. Secure Elliptic Curve Crypto-Processor for Real-Time IoT Applications. Energies 2021, 14, 4676. [Google Scholar] [CrossRef]

- Nannipieri, P.; Di Matteo, S.; Baldanzi, L.; Crocetti, L.; Zulberti, L.; Saponara, S.; Fanucci, L. VLSI Design of Advanced-Features AES Cryptoprocessor in the Framework of the European Processor Initiative. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2022, 30, 177–186. [Google Scholar] [CrossRef]

- Nannipieri, P.; Bertolucci, M.; Baldanzi, L.; Crocetti, L.; Di Matteo, S.; Falaschi, F.; Fanucci, L.; Saponara, S. SHA2 and SHA-3 accelerator design in a 7 nm technology within the European Processor Initiative. Microprocess. Microsyst. 2021, 87, 103444. [Google Scholar] [CrossRef]

- Nannipieri, P.; Di Matteo, S.; Baldanzi, L.; Crocetti, L.; Belli, J.; Fanucci, L.; Saponara, S. True Random Number Generator Based on Fibonacci-Galois Ring Oscillators for FPGA. Appl. Sci. 2021, 11, 3330. [Google Scholar] [CrossRef]

- Baldanzi, L.; Crocetti, L.; Di Matteo, S.; Fanucci, L.; Saponara, S.; Hameau, P. Crypto Accelerators for Power-Efficient and Real-Time on-Chip Implementation of Secure Algorithms. In Proceedings of the 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Genoa, Italy, 27–29 November 2019; pp. 775–778. [Google Scholar] [CrossRef]

- Nannipieri, P.; Di Matteo, S.; Zulberti, L.; Albicocchi, F.; Saponara, S.; Fanucci, L. A RISC-V Post Quantum Cryptography Instruction Set Extension for Number Theoretic Transform to Speed-Up CRYSTALS Algorithms. IEEE Access 2021, 9, 150798–150808. [Google Scholar] [CrossRef]

- Crocetti, L.; Di Matteo, S.; Nannipieri, P.; Fanucci, L.; Saponara, S. Design and Test of an Integrated Random Number Generator with All-Digital Entropy Source. Entropy 2022, 24, 139. [Google Scholar] [CrossRef] [PubMed]

- Di Matteo, S.; Gerfo, M.L.; Saponara, S. VLSI Design and FPGA Implementation of an NTT Hardware Accelerator for Homomorphic SEAL-Embedded Library. IEEE Access 2023, 11, 72498–72508. [Google Scholar] [CrossRef]

- ARM Security Technology—Building a Secure System Using TrustZone Technology. Technical Report, ARM, 2005–2009. Available online: https://developer.arm.com/documentation/PRD29-GENC-009492/c (accessed on 19 September 2023).

- ARM. Arm TrustZone Technology. Available online: https://developer.arm.com/ip-products/security-ip/trustzone/trustzone-system-ip (accessed on 19 September 2023).

- ARM. TrustZone for Cortex-A. Available online: https://developer.arm.com/ip-products/security-ip/trustzone/trustzone-for-cortex-a (accessed on 19 September 2023).

- ARM. TrustZone for Cortex-M. Available online: https://developer.arm.com/ip-products/security-ip/trustzone/trustzone-for-cortex-m (accessed on 19 September 2023).

- Khalid, F.; Masood, A. Hardware-Assisted Isolation Technologies: Security Architecture and Vulnerability Analysis. In Proceedings of the 2020 International Conference on Cyber Warfare and Security (ICCWS), Islamabad, Pakistan, 20–21 October 2020; pp. 1–8. [Google Scholar] [CrossRef]

- Intel Software Guard Extensions (Intel SGX)—Key Management on the 3rd Generation Intel® Xeon® Scalable Processor. Technical Report, Intel. 2019. Available online: https://builders.intel.com/docs/networkbuilders/intel-software-guard-extensions-intel-sgx-key-management-on-the-3rd-generation-intel-xeon-sc-1617436024.pdf (accessed on 19 September 2023).

- Intel Software Guard Extensions (Intel SGX)—Developer Guide. Technical Report, Intel. 2018. Available online: https://www.intel.com/content/dam/develop/public/us/en/documents/intel-sgx-developer-guide.pdf (accessed on 19 September 2023).

- Hoekstra, M.; Lal, R.; Pappachan, P.; Phegade, V.; Del Cuvillo, J. Using Innovative Instructions to Create Trustworthy Software Solutions. In Proceedings of the 2nd International Workshop on Hardware and Architectural Support for Security and Privacy, Tel-Aviv, Israel, 23–24 June 2013; Volume 11, pp. 2487726–2488370. [Google Scholar]

- McKeen, F.; Alexandrovich, I.; Berenzon, A.; Rozas, C.V.; Shafi, H.; Shanbhogue, V.; Savagaonkar, U.R. Innovative Instructions and Software Model for Isolated Execution. In Proceedings of the 2nd International Workshop on Hardware and Architectural Support for Security and Privacy, Tel-Aviv, Israel, 23–24 June 2013. Article 10. [Google Scholar]

- Anati, I.; Gueron, S.; Johnson, S.; Scarlata, V. Innovative Technology for CPU Based Attestation and Sealing. In Proceedings of the 2nd International Workshop on Hardware and Architectural Support for Security and Privacy, Tel-Aviv, Israel, 23–24 June 2013. Article 13. [Google Scholar]

- BIOS and Kernel Developer’s Guide (BKDG) for AMD Family 16h Models 30h-3Fh Processors. Technical Report, AMD, 2013–2016. Available online: https://www.amd.com/system/files/TechDocs/52740_16h_Models_30h-3Fh_BKDG.pdf (accessed on 19 September 2023).

- Rambus. Hardware Root of Trust: Everything You Need to Know. Available online: https://www.rambus.com/blogs/hardware-root-of-trust/ (accessed on 19 September 2023).

- Rambus. Introducing the Rambus CryptoManager Root of Trust (CMRT). Available online: https://www.rambus.com/blogs/introducing-the-rambus-cryptomanager-root-of-trust-cmrt/?lang=zh-hans (accessed on 19 September 2023).

- Synopsys. Synopsys tRoot Vx Hardware Secure Modules. Available online: https://www.synopsys.com/dw/ipdir.php?ds=security-troot-hw-secure-module (accessed on 19 September 2023).

- Champagne, D.; Lee, R.B. Scalable architectural support for trusted software. In Proceedings of the HPCA-16 2010 The Sixteenth International Symposium on High-Performance Computer Architecture, Bangalore, India, 9–14 January 2010; pp. 1–12. [Google Scholar]

- Szefer, J.; Lee, R.B. Architectural support for hypervisor-secure virtualization. ACM SIGPLAN Not. 2012, 47, 437–450. [Google Scholar] [CrossRef]

- Suh, G.E.; Clarke, D.; Gassend, B.; Van Dijk, M.; Devadas, S. AEGIS: Architecture for tamper-evident and tamper-resistant processing. In Proceedings of the 17th annual international conference on Supercomputing, San Francisco, CA, USA, 23–27 June 2003; pp. 160–171. [Google Scholar]

- Keller, E.; Szefer, J.; Rexford, J.; Lee, R.B. Nohype: Virtualized cloud infrastructure without the virtualization. In Proceedings of the 37th Annual International Symposium on Computer Architecture, Saint-Malo, France, 19–23 June 2010; pp. 350–361. [Google Scholar]

- Costan, V.; Lebedev, I.; Devadas, S. Sanctum: Minimal hardware extensions for strong software isolation. In Proceedings of the 25th USENIX Security Symposium (USENIX Security 16), Austin, TX, USA, 10–12 August 2016; pp. 857–874. [Google Scholar]

- SP 800-57 Part 1 Rev. 5; Recommendation for Key Management: Part 1—General. NIST: Gaithersburg, MD, USA, 2020.

- Tiri, K. Side-Channel Attack Pitfalls. In Proceedings of the 2007 44th ACM/IEEE Design Automation Conference, San Diego, CA, USA, 4–8 June 2007; pp. 15–20. [Google Scholar]

- Li, Y.; Chen, M.; Wang, J. Introduction to side-channel attacks and fault attacks. In Proceedings of the 2016 Asia-Pacific International Symposium on Electromagnetic Compatibility (APEMC), Shenzhen, China, 18–21 May 2016; Volume 1, pp. 573–575. [Google Scholar]

- Spreitzer, R.; Moonsamy, V.; Korak, T.; Mangard, S. Systematic classification of side-channel attacks: A case study for mobile devices. IEEE Commun. Surv. Tutor. 2017, 20, 465–488. [Google Scholar] [CrossRef]

- Yan, M.; Gopireddy, B.; Shull, T.; Torrellas, J. Secure hierarchy-aware cache replacement policy (SHARP): Defending against cache-based side channel attacks. In Proceedings of the 2017 ACM/IEEE 44th Annual International Symposium on Computer Architecture (ISCA), Toronto, ON, Canada, 24–28 June 2017; pp. 347–360. [Google Scholar] [CrossRef]

- Cho, J.; Kim, T.; Kim, T.; Shin, Y. Real-Time Detection on Cache Side Channel Attacks using Performance Counter Monitor. In Proceedings of the 2019 International Conference on Information and Communication Technology Convergence (ICTC), Jeju, Republic of Korea, 16–18 October 2019; pp. 175–177. [Google Scholar] [CrossRef]

- Kim, H.; Yoon, H.; Shin, Y.; Hur, J. Cache Side-Channel Attack on Mail User Agent. In Proceedings of the 2020 International Conference on Information Networking (ICOIN), Barcelona, Spain, 7–10 January 2020; pp. 236–238. [Google Scholar] [CrossRef]

- Kaushik, P.; Majumdar, R. Timing attack analysis on AES on modern processors. In Proceedings of the 2017 6th International Conference on Reliability, Infocom Technologies and Optimization (Trends and Future Directions) (ICRITO), Noida, India, 20–22 September 2017; pp. 462–465. [Google Scholar] [CrossRef]

- Rani, R.; Venkateswarlu, S. Security against Timing Analysis Attack. Int. J. Electr. Comput. Eng. (IJECE) 2015, 5, 759–764. [Google Scholar] [CrossRef]

- Jayasinghe, D.; Ragel, R.; Elkaduwe, D. Constant time encryption as a countermeasure against remote cache timing attacks. In Proceedings of the 2012 IEEE 6th International Conference on Information and Automation for Sustainability, Beijing, China, 27–29 September 2012; pp. 129–134. [Google Scholar] [CrossRef]

- Seo, S.C.; Kim, H. SCA-Resistant GCM Implementation on 8-Bit AVR Microcontrollers. IEEE Access 2019, 7, 103961–103978. [Google Scholar] [CrossRef]

- Hettwer, B.; Das, K.; Leger, S.; Gehrer, S.; Güneysu, T. Lightweight Side-Channel Protection using Dynamic Clock Randomization. In Proceedings of the 2020 30th International Conference on Field-Programmable Logic and Applications (FPL), Gothenburg, Sweden, 31 August–4 September 2020; pp. 200–207. [Google Scholar] [CrossRef]

- Jayasinghe, D.; Ignjatovic, A.; Parameswaran, S. SCRIP: Secure Random Clock Execution on Soft Processor Systems to Mitigate Power-based Side Channel Attacks. In Proceedings of the 2019 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Westminster, CO, USA, 4–7 November 2019; pp. 1–7. [Google Scholar] [CrossRef]

- Zhou, T.; Zhu, Y.; Jing, N.; Nan, T.; Li, W.; Peng, B. Reliable SoC Design and Implementation of SHA-3-HMAC Algorithm with Attack Protection. In Proceedings of the 2020 IEEE International Conference on Smart Cloud (SmartCloud), Washington, DC, USA, 6–8 November 2020; pp. 88–93. [Google Scholar] [CrossRef]

- Ma, J.W.; Guan, X.G.; Zhou, T.; Sun, T. A new countermeasure against side channel attack for HMAC-SM3 hardware. In Proceedings of the 2017 IEEE 12th International Conference on ASIC (ASICON), Guiyang, China, 25–28 October 2017; pp. 327–330. [Google Scholar] [CrossRef]

- Belaid, S.; Bettale, L.; Dottax, E.; Genelle, L.; Rondepierre, F. Differential power analysis of HMAC SHA-2 in the Hamming weight model. In Proceedings of the 2013 International Conference on Security and Cryptography (SECRYPT), Reykjavik, Iceland, 29–31 July 2013; pp. 1–12. [Google Scholar]

- He, Z.; Wu, L.; Zhang, X. High-speed Pipeline Design for HMAC of SHA-256 with Masking Scheme. In Proceedings of the 2018 12th IEEE International Conference on Anti-Counterfeiting, Security, and Identification (ASID), Xiamen, China, 9–11 November 2018; pp. 174–178. [Google Scholar] [CrossRef]

- Oku, D.; Yanagisawa, M.; Togawa, N. A Robust Scan-based Side-channel Attack Method against HMAC-SHA-256 Circuits. In Proceedings of the 2017 IEEE 7th International Conference on Consumer Electronics—Berlin (ICCE-Berlin), Berlin, Germany, 3–6 September 2017; pp. 79–84. [Google Scholar] [CrossRef]

- Kabin, I.; Dyka, Z.; Kreiser, D.; Langendoerfer, P. Unified field multiplier for ECC: Inherent resistance against horizontal SCA attacks. In Proceedings of the 2018 13th International Conference on Design Technology of Integrated Systems In Nanoscale Era (DTIS), Taormina, Italy, 9–12 April 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Werner, F.T.; Djordjević, A.R.; Zajić, A.G. A Compact Probe for EM Side-Channel Attacks on Cryptographic Systems. In Proceedings of the 2019 IEEE International Symposium on Antennas and Propagation and USNC-URSI Radio Science Meeting, Atlanta, GA, USA, 7–12 July 2019; pp. 613–614. [Google Scholar] [CrossRef]

- Patranabis, S.; Chakraborty, A.; Mukhopadhyay, D.; Chakrabarti, P.P. Fault Space Transformation: A Generic Approach to Counter Differential Fault Analysis and Differential Fault Intensity Analysis on AES-Like Block Ciphers. IEEE Trans. Inf. Forensics Secur. 2017, 12, 1092–1102. [Google Scholar] [CrossRef]

- Randolph, M.; Diehl, W. Power Side-Channel Attack Analysis: A Review of 20 Years of Study for the Layman. Cryptography 2020, 4, 15. [Google Scholar] [CrossRef]

- Chong, K.S.; Shreedhar, A.; Lwin, N.K.Z.; Kyaw, N.A.; Ho, W.G.; Wang, C.; Zhou, J.; Gwee, B.H.; Chang, J.S. Side-Channel-Attack Resistant Dual-Rail Asynchronous-Logic AES Accelerator Based on Standard Library Cells. In Proceedings of the 2019 Asian Hardware Oriented Security and Trust Symposium (AsianHOST), Xi’an, China, 16–17 December 2019; pp. 1–7. [Google Scholar] [CrossRef]

- Benhani, E.M.; Bossuet, L.; Aubert, A. The Security of ARM TrustZone in a FPGA-Based SoC. IEEE Trans. Comput. 2019, 68, 1238–1248. [Google Scholar] [CrossRef]

- Lipp, M. Cache Attacks and Rowhammer on ARM. Master’s Thesis, Institute for Applied Information Processing and Communications, Graz University of Technology, Gratz, Austria, 2016. Available online: https://mlq.me/download/master_thesis.pdf (accessed on 19 September 2023).

- Carru, P. Attack TrustZone with Rowhammer. 2017. Available online: https://grehack.fr/data/2017/slides/GreHack17_Attack_TrustZone_with_Rowhammer.pdf (accessed on 19 September 2023).

- Tang, A.; Sethumadhavan, S.; Stolfo, S. CLKSCREW: Exposing the Perils of Security-Oblivious Energy Management. In Proceedings of the 26th USENIX Security Symposium (USENIX Security 17), Vancouver, BC, Canada, 16–18 August 2017; USENIX Association: Berkeley, CA, USA, 2017; pp. 1057–1074. [Google Scholar]

- FIPS 197; Announcing the Advanced Encryption Standard (AES). NIST: Gaithersburg, MD, USA, 2001.

- SP 800-38B; Recommendation for Block Ciphers Modes of Operation: The CMAC Mode for Authentication. NIST: Gaithersburg, MD, USA, 2005.

- SP 800-38C; Recommendation for Block Ciphers Modes of Operation: The CCM Mode for Authentication and Confidentiality. NIST: Gaithersburg, MD, USA, 2007.

- SP 800-38D; Recommendation for Block Ciphers Modes of Operation: Galois/Counter Mode (GCM) and GMAC. NIST: Gaithersburg, MD, USA, 2007.

- IEEE Std 802.1AE-2018 (Revision of IEEE Std 802.1AE-2006); IEEE Standard for Local and metropolitan area networks-Media Access Control (MAC) Security. IEEE: Piscataway, NJ, USA, 2018. [CrossRef]

- SP 800-38E; Recommendation for Block Ciphers Modes of Operation: The XTS-AES Mode for Confidentiality on Storage Devices. NIST: Gaithersburg, MD, USA,, 2010.

- FIPS 186-4; Digital Signature Standard (DSS). NIST: Gaithersburg, MD, USA, 2013.

- FIPS 180-4; Secure Hash Standard (SHS). NIST: Gaithersburg, MD, USA, 2015.

- FIPS 202; glsSHA-3 Standard: Permutation-Based Hash and Extendable-Output Functions. NIST: Gaithersburg, MD, USA, 2015.

- Baldanzi, L.; Crocetti, L.; Falaschi, F.; Belli, J.; Fanucci, L.; Saponara, S. Digital Random Number Generator Hardware Accelerator IP-Core for Security Applications. In Applications in Electronics Pervading Industry, Environment and Society. ApplePies 2019; Lecture Notes in Electrical Engineering (LNEE); Springer: Berlin/Heidelberg, Germany, 2020; Volume 627, pp. 117–123. [Google Scholar] [CrossRef]

- Moody, D.N. Post-Quantum Cryptography: NIST’s Plan for the Future Status Update on Elliptic Curves and Post-Quantum Crypto. Available online: https://csrc.nist.gov/csrc/media/projects/post-quantum-cryptography/documents/pqcrypto-2016-presentation.pdf (accessed on 19 September 2023).

- Moody, D.N. Update on the NIST Post-Quantum Cryptography Project. Available online: https://csrc.nist.gov/CSRC/media/Presentations/NIST-Status-Update-on-Elliptic-Curves-and-Post-Qua/images-media/moody-dustin-threshold-crypto-workshop-March-2019.pdf (accessed on 19 September 2023).

- Barker, E.; Chen, L.; Keller, S.; Roginsky, A.; Vassilev, A.; Davis, R. Recommendation for Pair-Wise Key-Establishment Schemes Using Discrete Logarithm Cryptography; Technical Report; National Institute of Standards and Technology: Gaithersburg, MD, USA, 2017. [Google Scholar]

- Jablon, D. IEEE P1363 standard specifications for public-key cryptography. In Proceedings of the IEEE NIST Key Management Workshop CTO Phoenix Technologies Treasurer, Gaithersburg, MD, USA, 1–2 November 2001; pp. 1–26. [Google Scholar]

- IEEE 1363a; Standard Specifications for Public-Key Cryptography—Amendment 1: Additional Techniques. IEEE: Piscataway, NJ, USA, 2004.

- FIPS 198-1; The Keyed-Hash Message Authentication Code (HMAC). NIST: Gaithersburg, MD, USA, 2008.

- Crocetti, L.; Nannipieri, P.; Di Matteo, S.; Fanucci, L.; Saponara, S. Review of Methodologies and Metrics for Assessing the Quality of Random Number Generators. Electronics 2023, 12, 723. [Google Scholar] [CrossRef]

- Group, O. CVA6: A Linux-Capable RISC-V CPU. Available online: https://www.hackster.io/news/cva6-a-linux-capable-risc-v-cpu-299a40a5f871 (accessed on 19 September 2023).

- Crocetti, L.; Baldanzi, L.; Bertolucci, M.; Sarti, L.; Carnevale, B.; Fanucci, L. A simulated approach to evaluate side-channel attack countermeasures for the Advanced Encryption Standard. Integration 2019, 68, 80–86. [Google Scholar] [CrossRef]

- Zhang, F.; Zhang, H. SoK: A study of using hardware-assisted isolated execution environments for security. In Proceedings of the Hardware and Architectural Support for Security and Privacy, Seoul, Republic of Korea, 18 June 2016; pp. 1–8. [Google Scholar]

| Rambus CMRT | ARM TrustZone | Intel SGX | AMD PSP | Synopsis tRooT | |

|---|---|---|---|---|---|

| Implementation Strategy | Discrete | Integrated | Integrated | Integrated | Discrete |

| Isolation approach | Physical | Logical | Logical | Physical | Physical |

| Platform(s) | SoC IP | Cortex CPUs | from 6th generation of Intel CPUs | Ryzen CPUs | SoC IP |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Crocetti, L.; Nannipieri, P.; Di Matteo, S.; Saponara, S. Design Methodology and Metrics for Robust and Highly Qualified Security Modules in Trusted Environments. Electronics 2023, 12, 4843. https://doi.org/10.3390/electronics12234843

Crocetti L, Nannipieri P, Di Matteo S, Saponara S. Design Methodology and Metrics for Robust and Highly Qualified Security Modules in Trusted Environments. Electronics. 2023; 12(23):4843. https://doi.org/10.3390/electronics12234843

Chicago/Turabian StyleCrocetti, Luca, Pietro Nannipieri, Stefano Di Matteo, and Sergio Saponara. 2023. "Design Methodology and Metrics for Robust and Highly Qualified Security Modules in Trusted Environments" Electronics 12, no. 23: 4843. https://doi.org/10.3390/electronics12234843

APA StyleCrocetti, L., Nannipieri, P., Di Matteo, S., & Saponara, S. (2023). Design Methodology and Metrics for Robust and Highly Qualified Security Modules in Trusted Environments. Electronics, 12(23), 4843. https://doi.org/10.3390/electronics12234843