1. Introduction

In Internet of Things (IoT) and system-on-chip (SoC) application scenarios, energy-efficient fine-grained power management systems are indispensable for self-power wireless sensors due to the limited power capability of the supply and energy harvester. At high supply voltages (e.g., 1.2 V and above), analog low-dropout regulators (LDOs) can regulate a constant voltage for analog and RF modules due to their excellent noise performance and high PSRR characteristics, which maximize the performance and energy efficiency [

1,

2]. With CMOS process scaling, the intrinsic gain of the transistors is smaller, leading to an analog circuit accuracy reduction. Although the multistage operational transconductance amplifier improves the gain, it also introduces stability issues and considerable power consumption. In addition, in the near-threshold range (62 mV to 0.6 V), the analog LDO (ALDO) also fails to show excellent energy efficiency. Recently, the digital LDO (DLDO) features low voltage operation, process scalability, and other benefits associated with digital-oriented design, which has received the attention of many researchers [

3].

Compared with the DLDO with the power PMOS transistors, the DLDO with the power NMOS transistor can provide additional current through their intrinsic loop (V

gs) to optimize the undershoot voltage and the response time during the output voltage recovery process. Nevertheless, this type of DLDO requires a charge pump circuit and the level shifter to ensure that the gate voltage of the power NMOS transistor is higher than the supply voltage [

4]. This leads to extra area and power consumption in the level shifter, charge pump, and capacitance. The classic digital LDOs improve the clock frequency of the dynamic comparator and the bidirectional shift register (S/R) for a better transient response, but increase the static power I

q in the steady state [

5]. Therefore, it is crucial to enhance the transient response while simultaneously reducing the power consumption.

There are various approaches to enhance the dynamic response of digital LDOs. One method is to use asynchronous clocking [

6] or the self-clock technique [

7] instead of the synchronous clock as the trigger method of the comparator and the S/R. However, asynchronous clocking can make the logic design more intricate and susceptible to voltage and temperature variations, which compromises the robustness of the system. Another strategy involves modifying the structure of the power PMOS transistor array, for instance, a binary-weighted PMOS capacitor array. Because the most significant bit PMOS transistor always offers the maximum current whether large or small jumps occur in the output voltage, this leads to the oscillation phenomenon and a long recovery time when a small output voltage change occurs [

8]. Dual-loop regulation is an effective way to avoid the oscillation phenomenon by utilizing an extra transient detector (TD) to check the output changes. The coarse loop is used to quicken the output level recovery when the output exceeds the detection boundaries, and when the threshold level is not surpassed, the PMOS transistor in the fine loop is switched at each clock edge for high accuracy and current efficiency. However, the continuous-time (CT) comparator in the TD can increase the static power consumption of the digital LDO [

9]. The analog-assisted (AA) technique uses a coupling capacitor C

C with a resistance R

1 that forms a high-pass filter to compensate the transient current to the gate of the PMOS transistor, which is a promising technology as there is no additional static power consumption [

10]. However, the performance is degraded in the light-to-heavy load transient case because the transconductance of the PMOS transistors is too small to fully compensate for the load transient current. Fortunately, the light load current can reach about several hundred μA. The only fly in the ointment is that the transient response can be boosted at the expense of area (C

C = 120 pF). Finally, the fifth technique is adaptive clocking, which selects the clock frequency of the comparator and the S/R. However, the glitch during the fast/slow clock switching process may affect the performance of the circuit [

11].

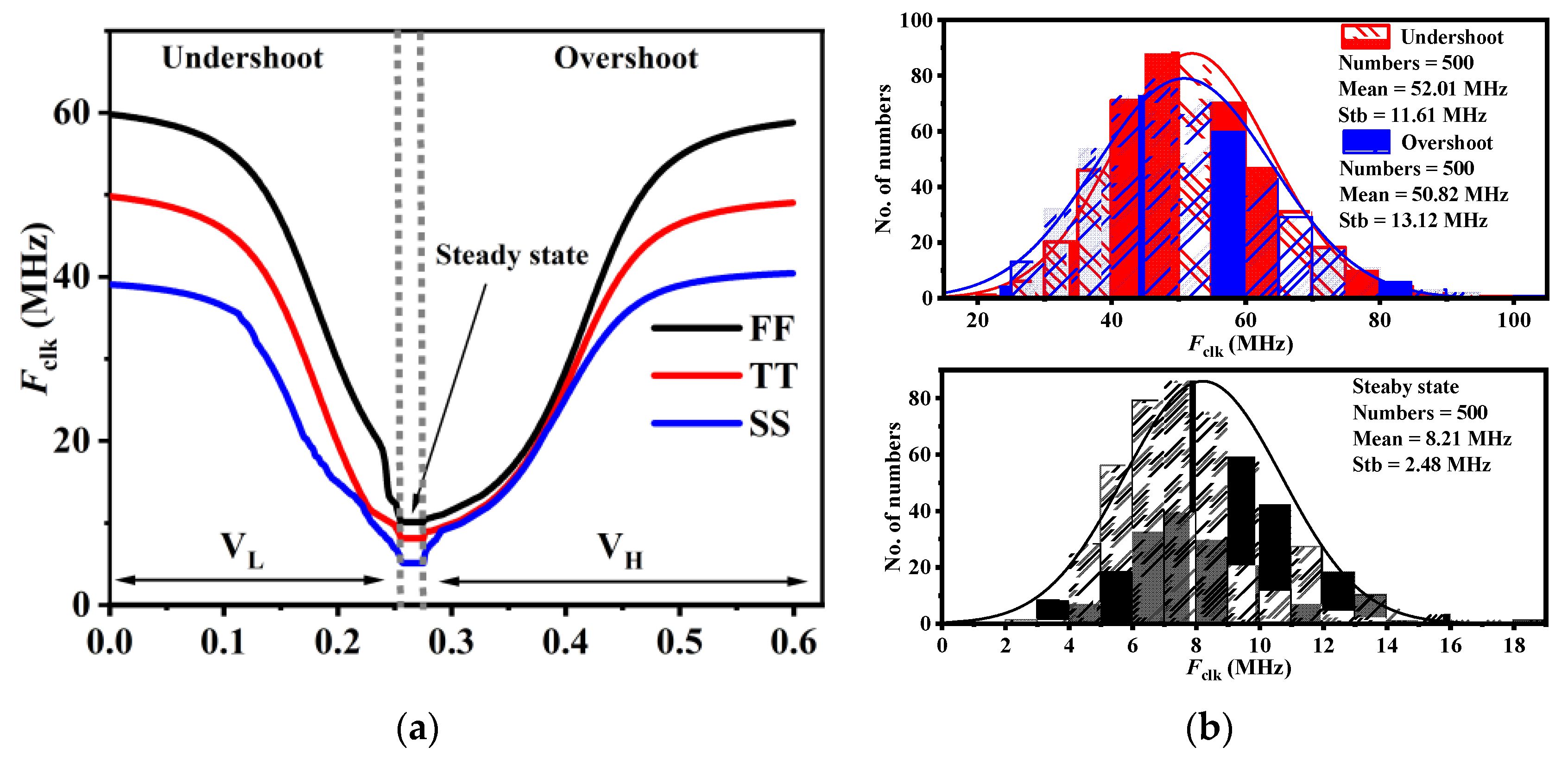

To address the above-mentioned issues, the comparator and bidirectional S/R were controlled with different trigger methods without extra circuit assistance and robustness issues in our work. Specifically, the comparator obtains the quantization result at the rising edge, while the bidirectional S/R then samples and shifts this quantization result at the falling edge. As a result, the transient response can be enhanced because the PMOS array can adjust the output current in the current cycle. In other words, this trigger technology can relax the clock frequency at the steady state by 2×. In addition, a built-in adaptive voltage-controlled oscillator (VCO) clock (AVC) is proposed to reduce both the static and transient power consumption by adjusting the clock frequency of the comparator and bidirectional S/R in real-time according to the output voltage. When the output current change jumps from 0.5 mA to 25 mA within 100 ps, the clock frequency of the AVC is boosted from 8 MHz in the steady state to 50 MHz, which lowers the undershoot voltage and the recovery time in the undershoot case and overshoot case to 335 mV, 2.7 μs, and 2.1 μs. To boost the current efficiency, the self-clock comparator in the transient detector is employed. The post-simulation results show that the proposed DLDO can provide a load current from 0.5 mA to 25 mA and achieve a peak current efficiency of 99.6% at the supply voltage of 0.6 V with an active area of 0.053 mm2 in a standard 0.18 μm CMOS process, leading to the FoM1 and FoM2 of 2.654 ps and 0.13 pF, respectively.

The rest of this paper is organized as follows.

Section 2 describes the architecture and working principle of the proposed DLDO.

Section 3 demonstrates the circuit implementations and design considerations of each circuit module.

Section 4 presents the simulation results and comparisons.

Section 5 concludes this work.

2. Architecture and Working Principle

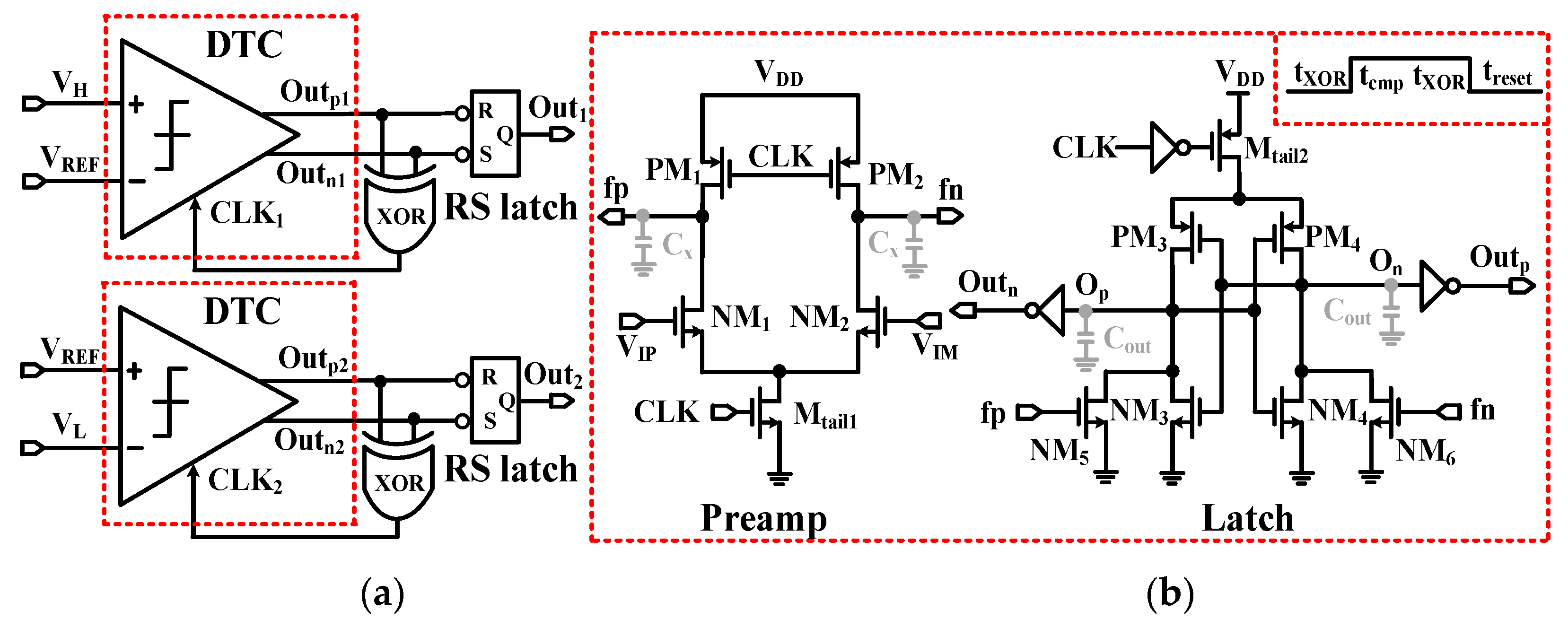

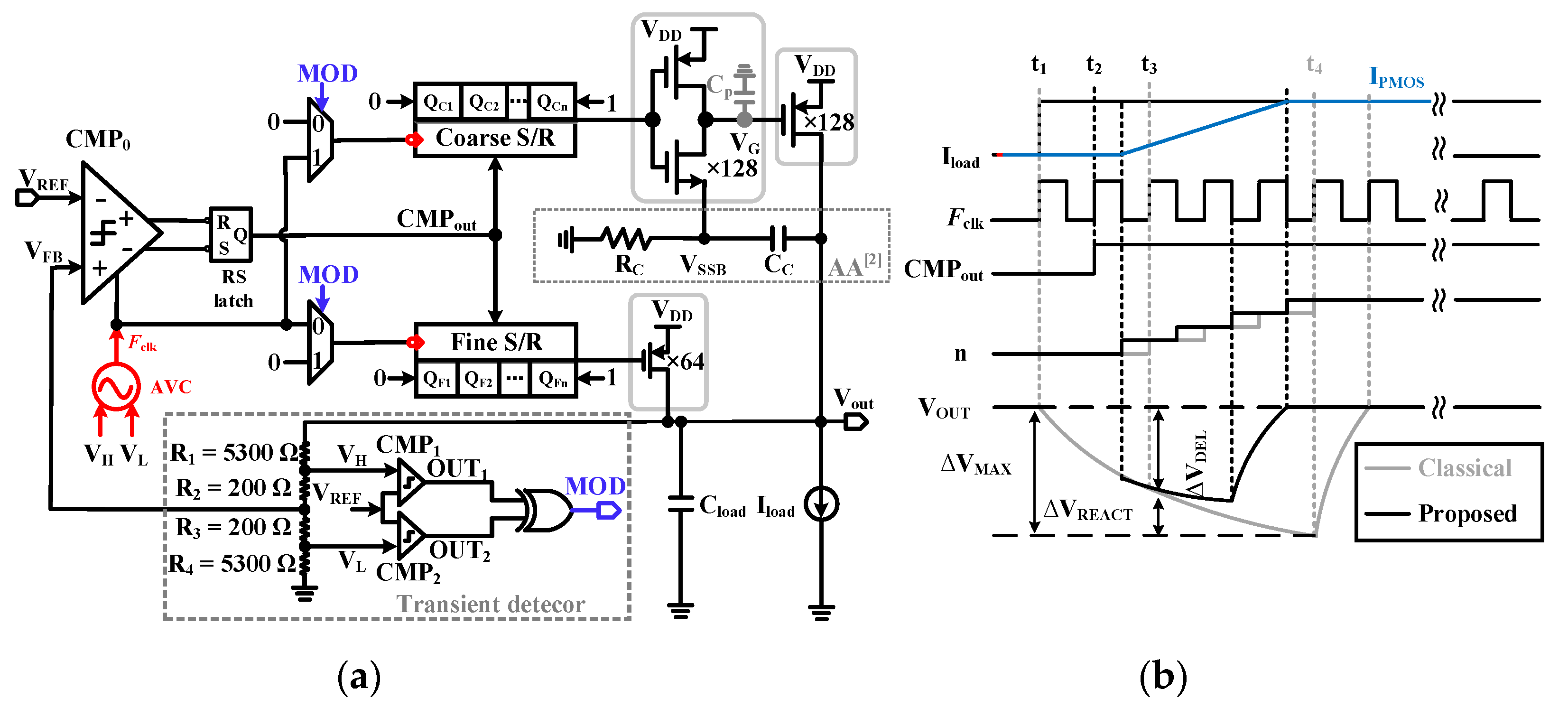

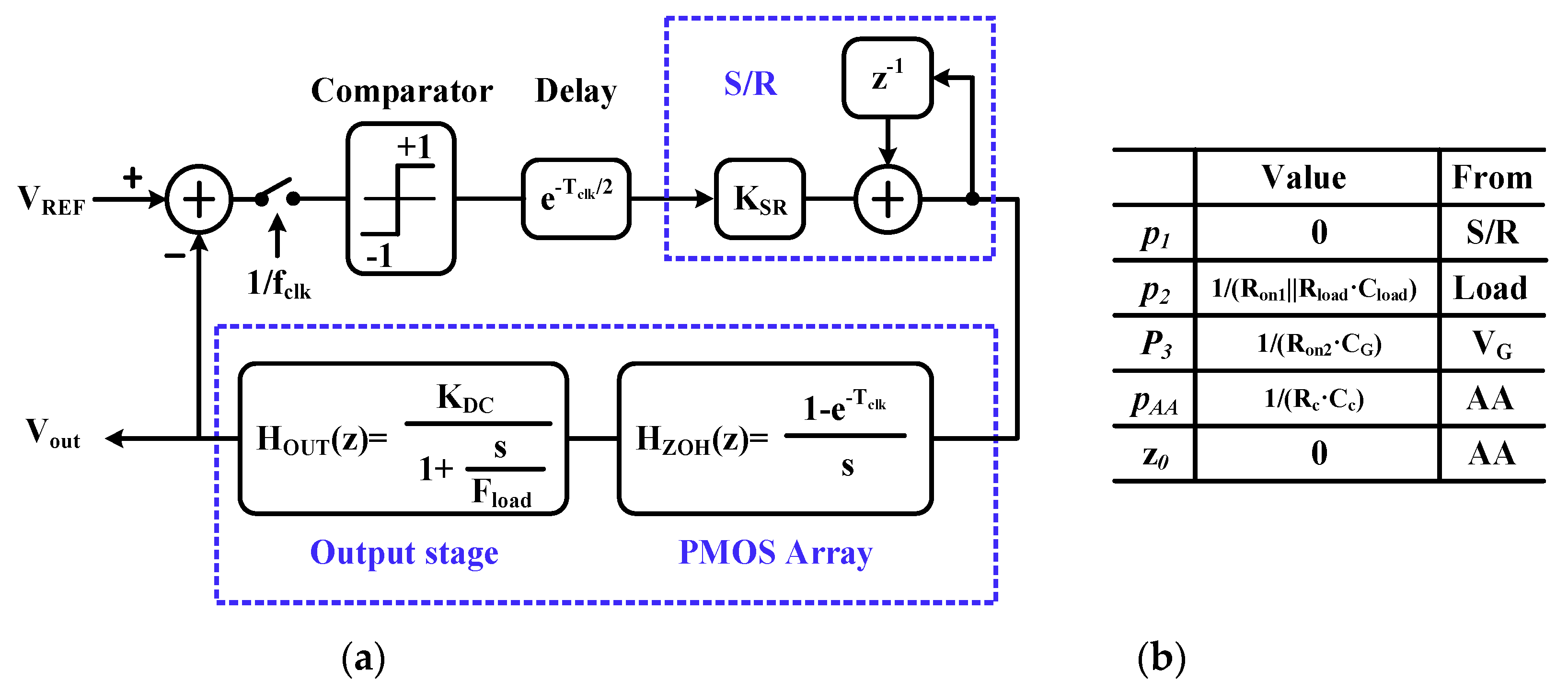

Figure 1a presents the overall architecture of the proposed DLDO with an AA loop from Ref. [

4]. The proposed DLDO consists of the main comparator CMP

0 with an RS latch, two selectors controlled by the MOD signal, the coarse and fine bidirectional S/R, the coarse and fine power PMOS transistor arrays, the AVC, and the TD.

To trade off the power and transient response, the PMOS array is divided by 128 coarse PMOS transistors with a size of 100 μm/0.18 μm and 64 fine PMOS transistors with a size of 10 μm/0.18 μm. The total size of the coarse PMOS array is mainly determined by the maximum load current, while the size of the unit for the fine PMOS transistor is decided by the minimum load current. Under the same maximum output current capability, as the bits of the coarse PMOS array increases, for example, 256 bits, the output current of every unit of the coarse PMOS transistor is halved, which not only increases the area of the coarse bidirectional SR, but also prolongs the recovery time. In contrast, with the decrease in the bit of the coarse PMOS array such as 64 bits, the transient current provided by every coarse PMOS transistor is increased by more than two times at a large undershoot in the output voltage since the source to drain voltage (Vsd) of every coarse PMOS transistor increases from 50 mV in the steady state to several hundred mV in the transient response. The simulation shows that the output current of every coarse PMOS transistor with a size of 400 μm/0.18 μm is 924 μA and 1.8 mA at the Vsd of 50 mV and 300 mV, which is much higher than the total current (828 μA) provided by the fine PMOS array. However, by doing this, the output suffers from the overshoot voltage after the undershoot voltage, which still prolongs the recovery time. More significantly, the proposed DLDO cannot switch from the coarse loop to the fine loop during the output recovery process. Furthermore, the RS latch can protect or temporarily store the main comparator result during the comparator reset phase.

It can be seen from

Figure 1 that the gate voltage of the power PMOS transistors is determined by the coarse/fine loop bidirectional S/R and the AA loop. When the output current increases suddenly, the output voltage of the proposed DLDO decreases sharply, and the output voltage change is assumed as ΔV

out. The AA loop has a faster response than the main loop of the DLDO, and thus the gate voltage can reduce C

C·ΔV

out/(C

C + C

P) immediately to lower the undershoot voltage, where C

P is the parasitic gate capacitor of the power PMOS transistors. In the proposed work, the total size of the fine PMOS array is only 1/20 of that of the coarse PMOS array. Therefore, the undershoot voltage dominantly relies on the coarse PMOS array. Furthermore, even if the AA loop is employed in the fine PMOS array, the undershoot voltage cannot be optimized obviously because the parasitic capacitance of the fine PMOS array is contained and the gate voltage change of all PMOS transistors is reduced under the identical C

C. Therefore, the AA loop is only used for the coarse PMOS array by trading off the undershoot voltage and gate voltage change of the power PMOS transistors.

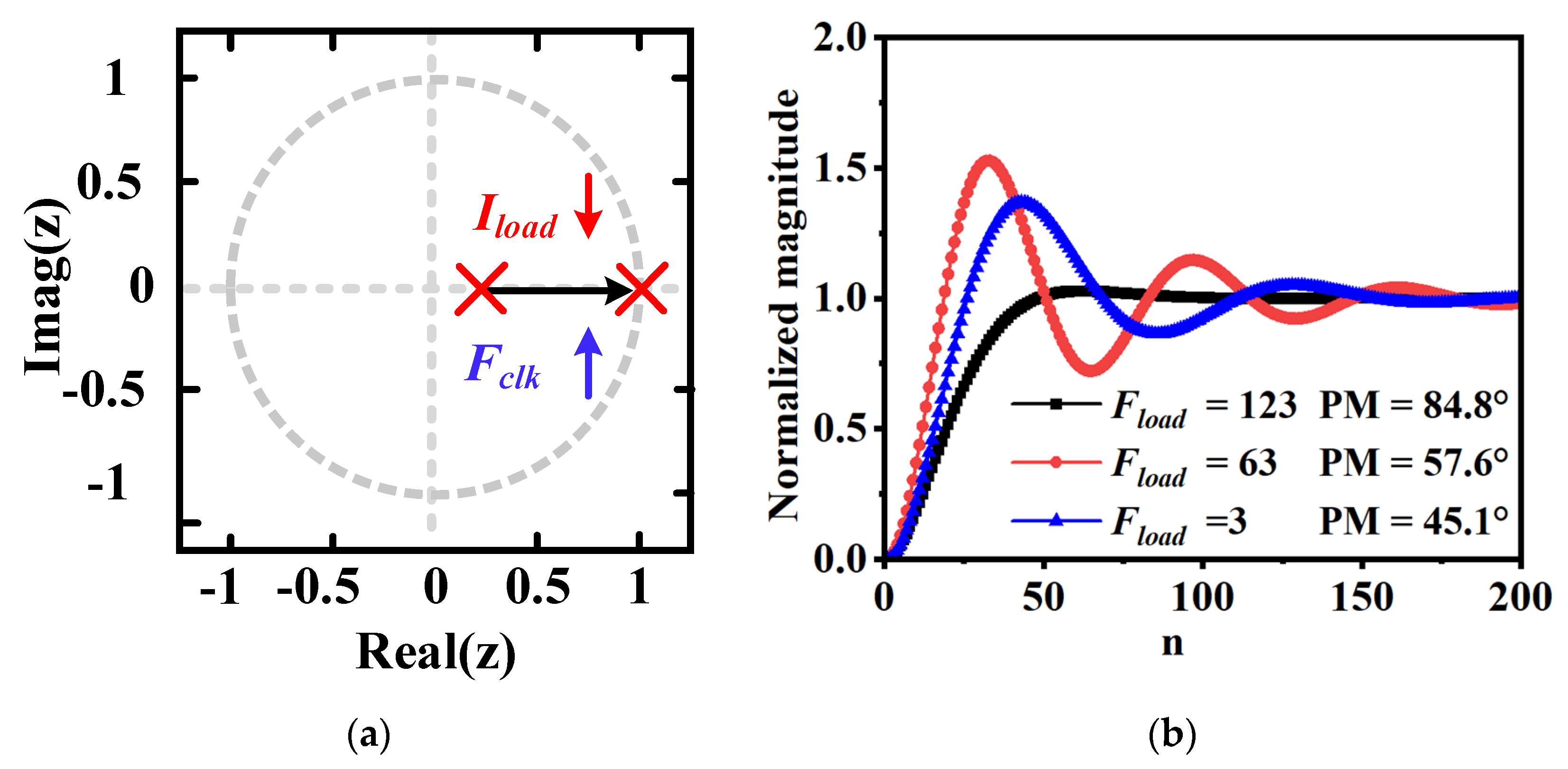

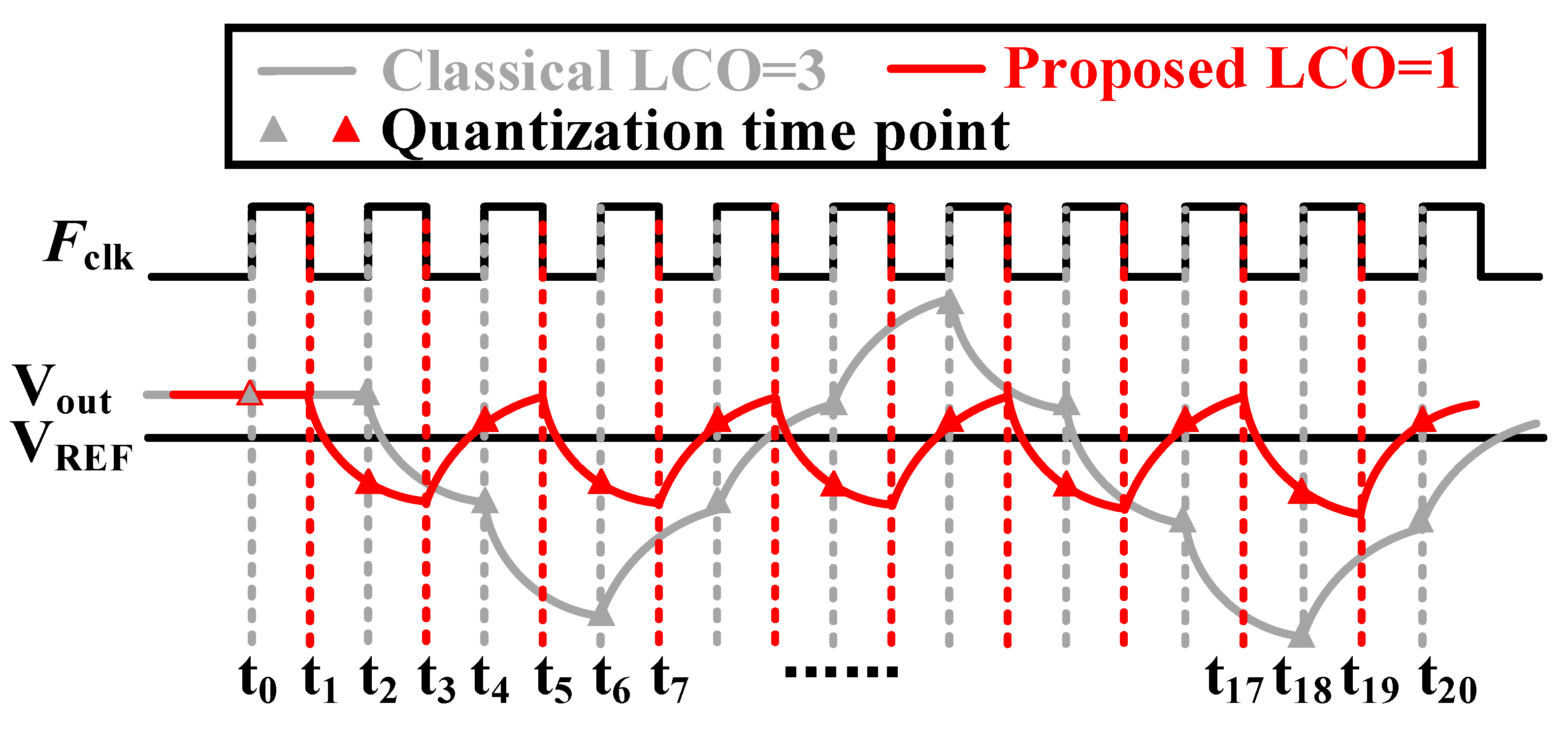

Figure 1b shows the transient response comparison between the classical DLDO [

5] and the proposed DLDO. When the load current (I

load) steps up at t

1 within a rapid edge time, the CMP

0 and the SR latch hardly provide a correct comparison result (CMP

out) due to the limited comparison time (1/(2·

Fclk)). At t

2, the CMP

out turns to the high level at the rising edge of

Fclk. Now, the coarse S/R is selected by the MOD because the V

OUT exceeds the threshold boundary, unlike the S/R of the classical DLDO [

5] and the conventional coarse-fine loop DLDO [

9], which is triggered in the next cycle t

3. The S/R in the proposed DLDO is triggered at the falling edge to turn on the power PMOS transistor to supplement the output current to reduce the ΔV

DEL until the I

PMOS is equal to I

load. In other words, the transient response can be enhanced by triggering the comparator CMP

0 and the S/R at the rising and falling edge, respectively, without the clock frequency increment and any hardware cost.

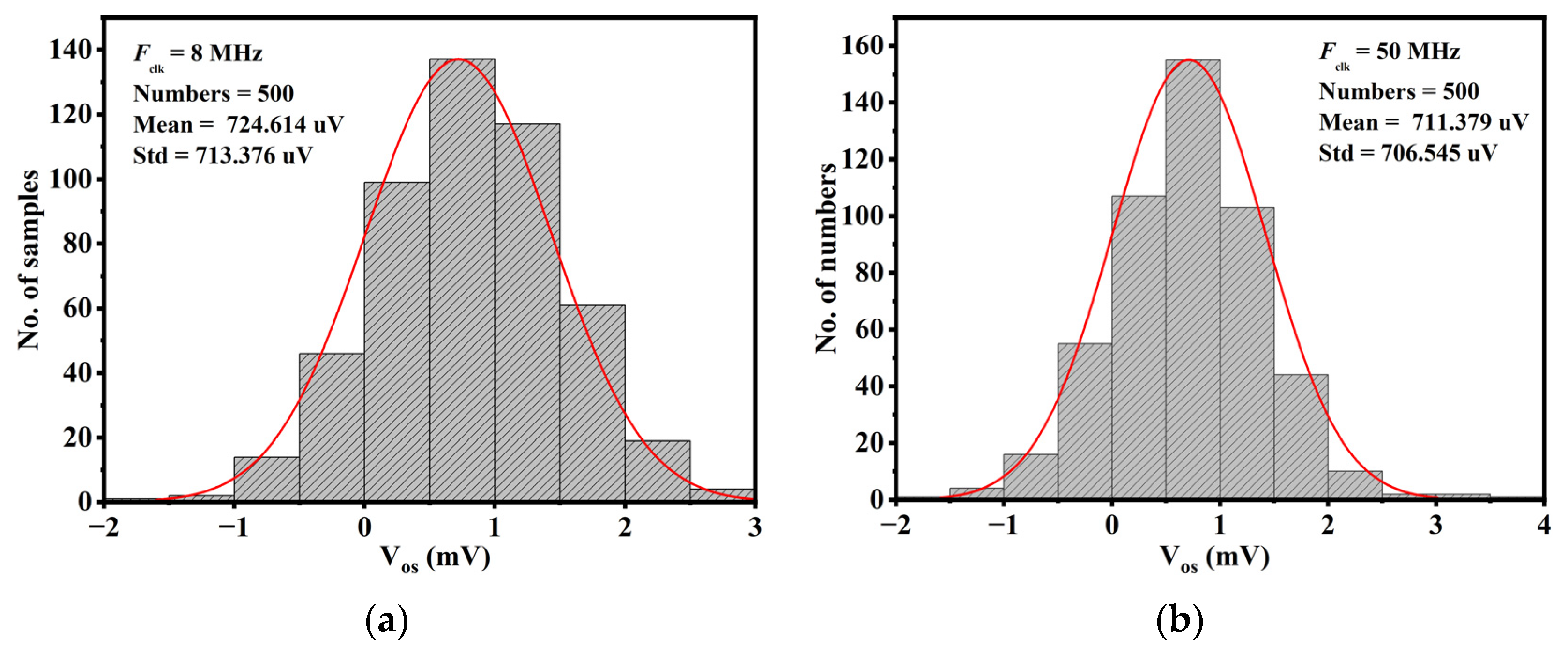

Unlike the conventional TD [

12], the self-clocked comparators CMP

1 and CMP

2 replace two CT comparators to lower the power consumption, and the operation frequency of these two comparators is enhanced to 58 MHz to diminish the comparator’s delay effect on the DLDO at a supply voltage of 0.6 V. The four resistors R

1, R

2, R

3, and R

4 in the TD have resistance values of 5300 Ω, 200 Ω, 200 Ω, and 5300 Ω, respectively. Therefore, V

H, V

FB, and V

L can be calculated as follows:

According to Equation (1), even if there is a resistance mismatch, V

H must be larger than V

REF, while V

L must be smaller than V

REF. If the TD range is too small (2 mV), the proposed DLDO will jump from the fine loop to the coarse loop with a slight change in the output voltage. As a result, the output voltage will oscillate during output recovery due to multiple overshoots and undershoots, resulting in a long recovery time. If the TD range is too large (200 mV), it is difficult to switch the proposed DLDO from the fine loop to the coarse loop with a large jump in the output. As a consequence, this situation also leads to a long recovery time since the current provided by each PMOS transistor in the fine loop is small. In our design, the TD range was designed to be 20 mV by compromising the recovery time in the case of the large jump and the small jump in the output voltage. In addition, the V

H and V

L were designed for 285 mV and 265 mV, respectively, by the series resistor ladder instead of the voltage reference for the dynamic voltage scaling. The voltage reference operating in the subthreshold region or the 2T solution in [

13] can dramatically reduce the static power consumption. However, the series resistor ladder was used in our work for two reasons. Firstly, V

H, V

L, and V

FB vary with the supply voltage to achieve a fixed V

drop. The voltage reference (2T solution) can only provide a fixed level under different PVT conditions, which shrinks the supply voltage range. Secondly, we assumed that a voltage reference with the value of 285 mV was designed with the nanowatt level power consumption. An external operational amplifier is still required to generate a voltage reference value of 265 mV, resulting in additional power consumption and increased circuit complexity. When the load current changes sharply, the overshoot voltage or undershoot voltage exceeds the threshold voltage V

H or V

L, and then the MOD outputs 1. The AVC generates a high-frequency clock. At the same time, the comparator and coarse bidirectional S/R, controlled by this high-frequency clock, can quickly recover the output voltage through a coarse PMOS array until V

FB is recovered between the V

H and V

L levels. More importantly, because the clock frequency (

Fclk) is controlled by the V

H and V

L associated with the output of the DLDO (V

out), it will decrease with the decrease in the undershoot voltage. Therefore, the oscillation at V

out can effectively be avoided during the signal recovery process. When the circuit output is at a steady state or when the overshoot voltage or undershoot voltage is small, MOD outputs 0, and the AVC produces a corresponding low-frequency clock to control the CMP

0 and the fine-loop bidirectional SR for the output voltage recovery. Meanwhile, the coarse bidirectional SR is idle to lower the power consumption.

4. Simulation Results and Comparisons

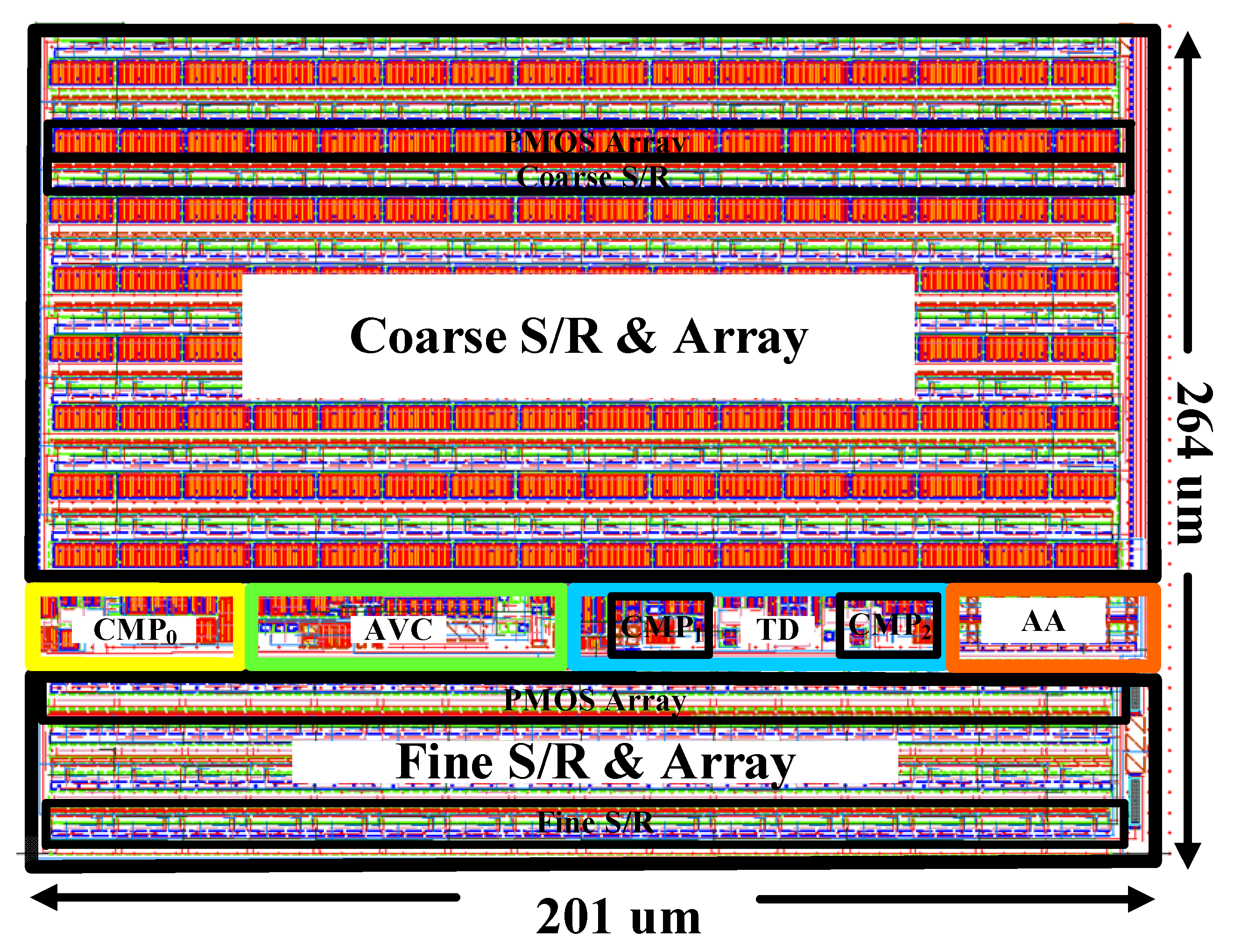

Figure 9 shows that the proposed DLDO occupies an active area of 0.053 mm

2 in a standard 0.18 μm CMOS process including the CMP

0, the AVC, the TD with two self-clocked comparators (CMP

1 and CMP

2), the AA circuit, and the coarse and fine S/R and the power PMOS transistor array.

Figure 10 shows the simulation setup of the proposed DLDO. The total on-chip capacitor (C

C) was 50 pF and the resistors R

a1 and R

a2 were served for the heavy load and light load, which were designed as 22.5 Ω and 1100 Ω, respectively. The switch (S

w) and the inverter (inv

1) are employed to generate the falling and rising edge time of 100 ps for the load transient.

All parasitic effects were considered including the parasitic capacitance from the metal wires to the substrate, the parasitic capacitance among different metal wires, and the parasitic resistance of the wires. The parasitic resistance of the entire proposed DLDO was reduced by the minimum spacing between modules and the multilayer metal interconnection technology. Because the static current of the proposed DLDO was less than 100 μA, the effect of the parasitic resistance was almost negligible. In addition, the offset of the dynamic comparator and resistance mismatch in the TD circuit were suppressed by good matching and dummy technology.

The proposed DLDO provides a load current from 500 μA to 25 mA and consumes a quiescent current of 95.13 μA at the heavy load of 25 mA under a low supply of 0.6 V, resulting in a peak current efficiency of 99.6%. The power consumption is independent of the I

load, and

Figure 11 illustrates the power breakdown of the proposed DLDO in the steady state where the resistors in the TD occupy more than 50% of the total power, and the power of the AVC is only 2.5% of the total power.

The proposed DLDO can regulate V

OUT from 550 mV to 1050 mV with the V

DD varying from 0.6 V to 1.1 V with a dropout voltage of 50 mV.

Figure 12a shows that the line regulation (LR) was 5.8 mV/V at the load current of 0.5 mA and 4.3 mV/V at the heavy load of 25 mA, respectively, while

Figure 12b shows that the best and worst LR were 4.2 mV/V and 6.6 mV/V at the V

REF of 0.75 V and 0.5 V, respectively.

Figure 12c shows that the fluctuation of the load regulation (LD) varied the supply voltage, and the LD as 0.1265 mV/mA at the supply of 0.6 V.

Figure 12d,e verified the LR at the light load of 0.5 mA and LD at the 0.6 V supply at different corners, and the LR and LD remained at the same order of magnitude. To evaluate the transient performance of the proposed DLDO, the proposed DLDO regulator was operated at the V

DD of 600 mV with the V

OUT of 550 mV and the C

C of 50 pF.

Regardless of the analog LDO or the digital LDO, the shorter the T

edge, the more it can reflect the worst undershoot voltage and overshoot voltage of the LDO. Therefore, T

edge was designed to be 100 ps to reflect the worst undershoot voltage and overshoot voltage. The advantage of the capacitor C

C in the AA technology is that the off-chip load capacitor can be reduced to 0 [

10]. In order to intuitively reflect the transient effects of parasitic capacitance and resistance,

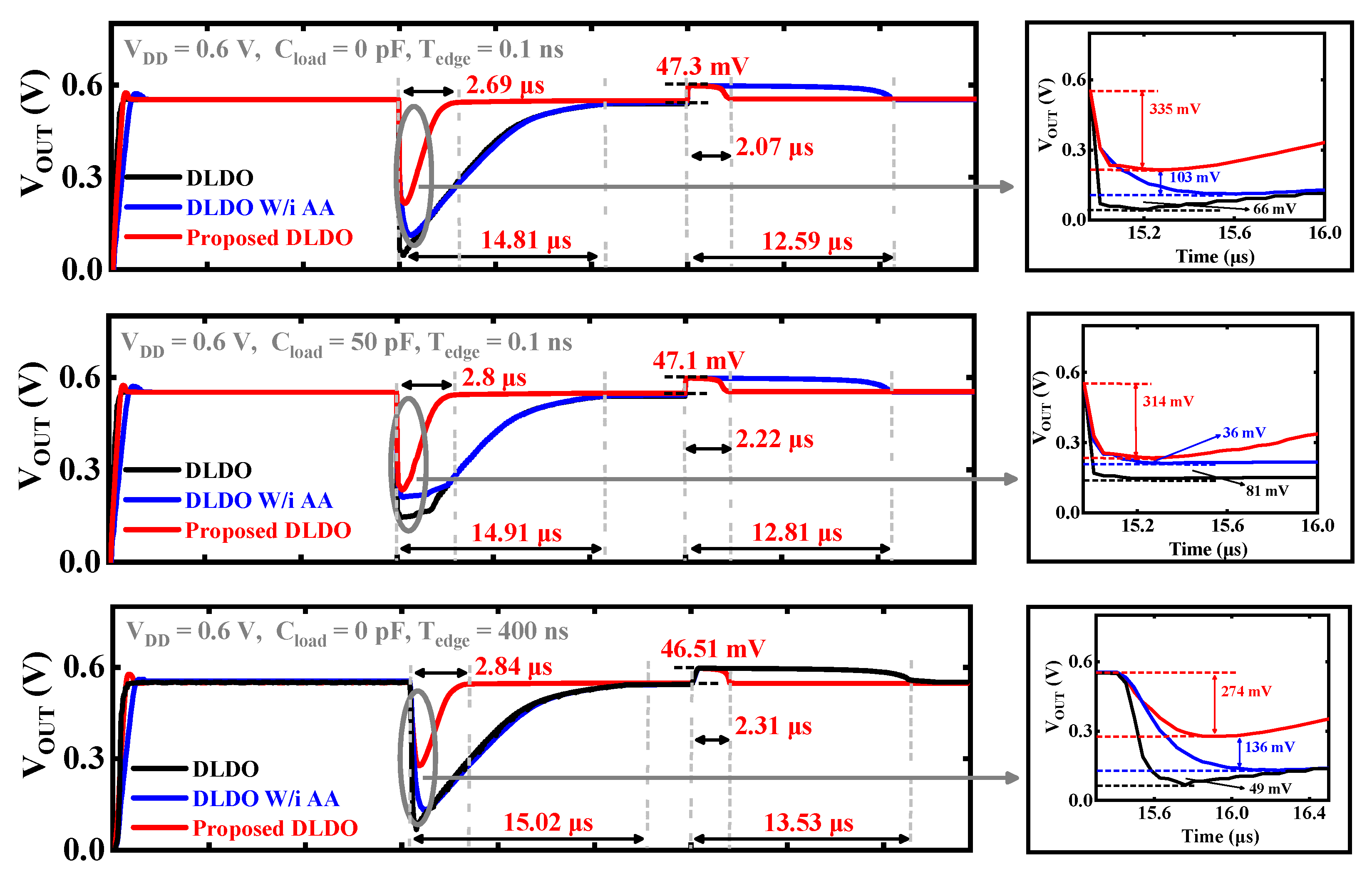

Figure 13 shows that the overshoot voltage and undershoot voltage of the proposed DLDO were almost unchanged, and the recovery time of the undershoot and overshoot was extended by 70 ns and 60 ns, respectively.

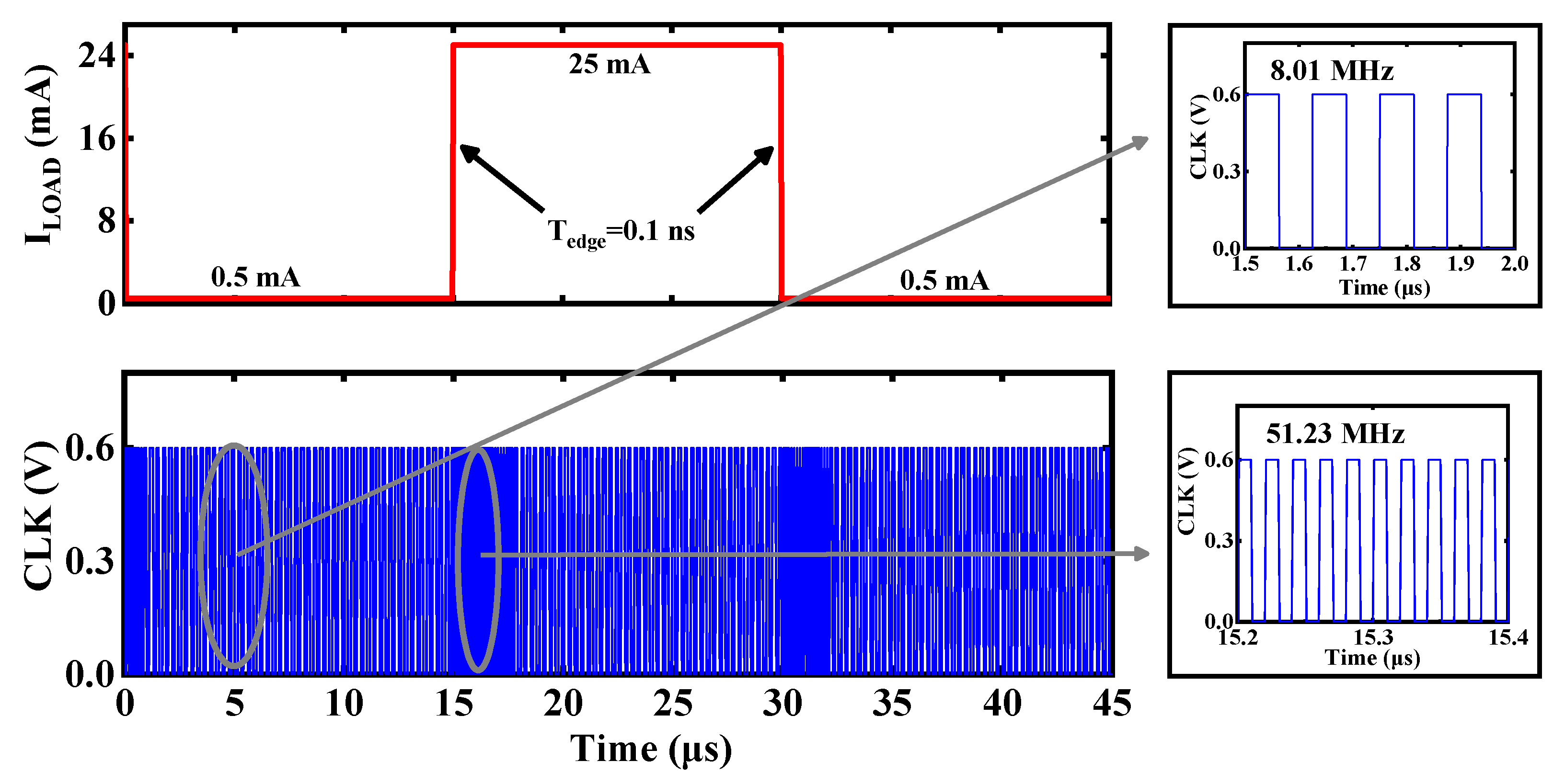

Figure 14 shows the transient response comparison among the conventional LDO, the DLDO with the AA loop, and the proposed double-edge-triggered DLDO with the AA loop and the AVC. At the external clock frequency of 8 MHz, the undershoot voltage of the conventional DLDO with the AA technology decreased by 66 mV than that of the conventional DLDO when the load current stepped up from 0.5 mA to 25 mA at the edge time (I

load) of 100 ps. Compared with the conventional DLDO with the AA technology, the undershoot voltage with the proposed double-edge-triggered DLDO can be reduced from 438 mV to 335 mV, and the recovery time was optimized from 14.8 μs to 2.7 μs in the undershoot case and from 10.5 μs to 2.1 μs in the overshoot case. Meanwhile, it can be seen from

Figure 14 that the clock frequency was enhanced from 8 MHz to 50 MHz by the AVC.

Figure 14 also shows the transient response of the proposed DLDO with and without a load capacitor at a supply of 0.6 V at the different T

edge. As can be seen from

Figure 14, the undershoot voltage with the load capacitor was only 21 mV smaller than that without the load capacitor, while the overshoot voltage was almost constant whether the load capacitor exists or not. This verifies that the C

C in the AA technology can reduce the off-chip load capacitor to 0. Furthermore, when the T

edge was 400 ns as in [

18], the undershoot voltage and overshoot voltage were decreased to 274 mV and 46.51 mV.

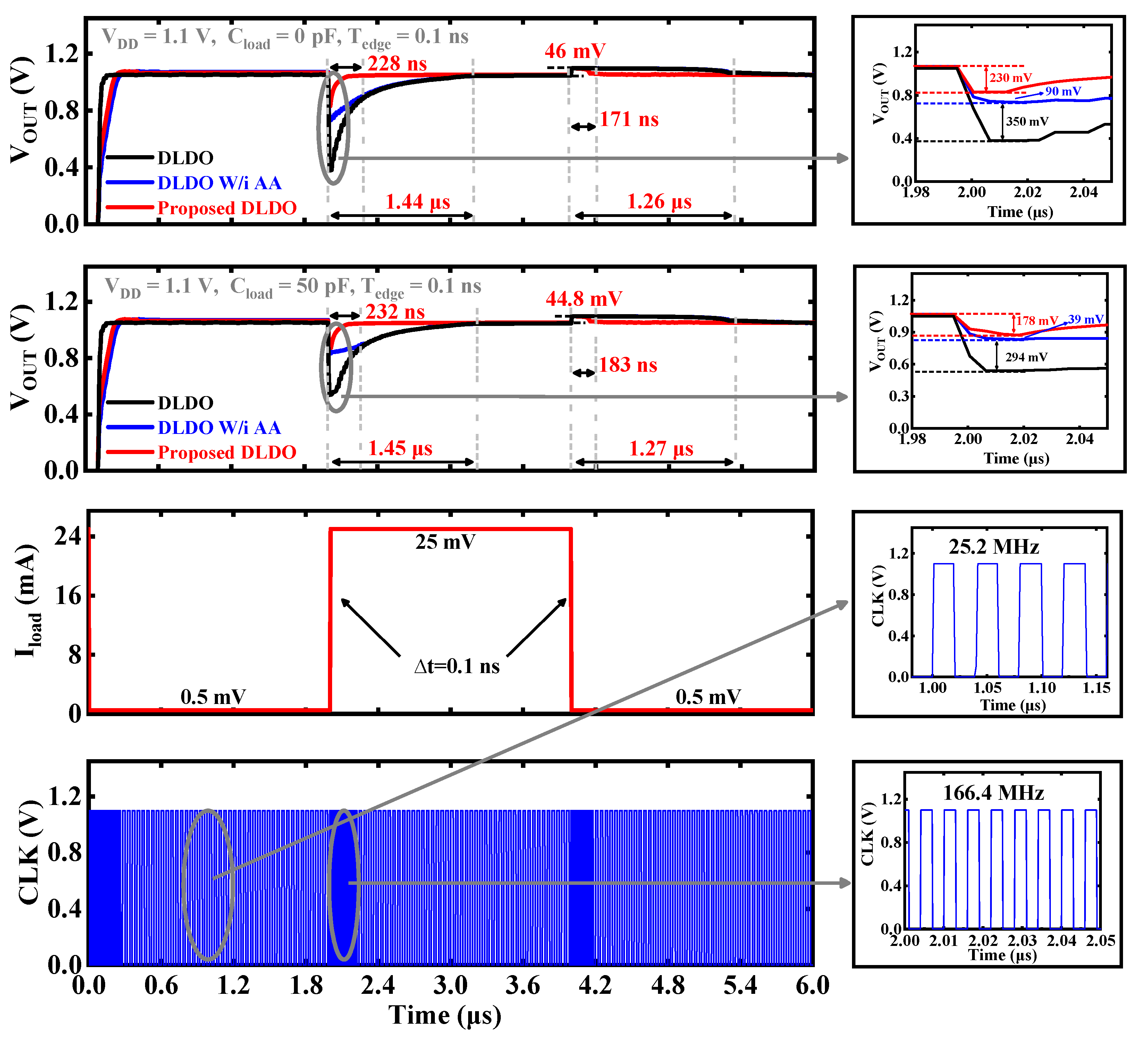

Figure 15 shows the transient response of the proposed DLDO with and without a load capacitor at a supply of 1.1 V. The undershoot voltage and overshoot voltage were 230 mV and 46 mV without the load capacitor, respectively. When a load capacitor (C

load) of 50 pF was added, the undershoot voltage and overshoot voltage decreased to 232 mV and 44.8 mV, respectively. Furthermore, the transient response was also enhanced due to the improvement in the clock frequency of the AVC. Overall, the undershoot voltage and overshoot voltage were optimized with a longer T

edge and a load capacitor.

To verify the robustness of the transient responses, the simulation at different process corners and temperatures is depicted in

Table 2. The undershoot voltage and overshoot voltage at the FF corner had a smaller spike, and the recovery time became faster than the performances at the TT corner with the same temperature, while the performances at the SS corner behaved just right, in contrast. As a result, the worst undershoot voltage and overshoot voltage were 399 mV with a recovery time of 2.7 μs and 48.3 mV with a recovery time of 2.1 μs, respectively. The reason why the overshoot voltage was almost constant is that V

out jumped to almost the supply voltage when the output voltage suddenly dropped from 25 mA to 0.5 mA.

Table 3 illustrates the performance parameters of the proposed DLDO in this paper and compares the simulation performances with the state-of-the-art DLDO architectures. In the steady state, the V

drop voltage is always 50 mV for any supply voltage. Specifically, when the supply voltage is 1.1 V, the output voltage is 1.05 V, while the supply voltage is 600 mV and the output voltage is 550 mV. Compared with [

18,

19], these DLDOs still need a large load capacitor to suppress the voltage fluctuation within 100 mV during the transient response. Compared to works with a fixed clock frequency [

9,

19,

20,

21], the AVC between the steady state and the transient response could better balance the transient responses and static current. Although the load current change could achieve a change of 28 mA in [

22] at the only load capacitor of 9.5 pF, the DLDO consumed up to the quiescent current of about 1 mA, which degraded the current efficiency. The proposed DLDO can fix the stability issues at any load current and thus allows the output change from the minimum to the maximum load current within an edge time of 100 ps because the clock frequency can be adaptively adjusted based on the output voltage in time. Moreover, even though the power of the AVC is included, the quiescent current of the entire DLDO is still very low, resulting in the two FoMs. Meanwhile, we provide a comparison of the related simulation results with the previous publications [

1,

2,

23,

24] in

Table 4 regarding the analog LDOs in electronics. It can be seen from

Table 4 that the static power consumption of the recent analog LDOs is comparable to that of the proposed DLDO. Furthermore, the area of these analog LDOs did not include the area of the load capacitor (C

load). The analog LDO could achieve better FoMs than the proposed DLDO because of the small undershoot voltage and overshoot voltage due to a larger load capacitor and a looser T

edge. The main advantages of the proposed DLDO are the ability to achieve an adjustable output voltage, completely circumvent the load capacitor, and a rigorous T

edge of only 0.1 ns at a low power supply (V

DD < 1.2 V).