A Capacitorless LDO Regulator with Fast Feedback Loop and Damping-Factor-Control Frequency Compensation

Abstract

:1. Introduction

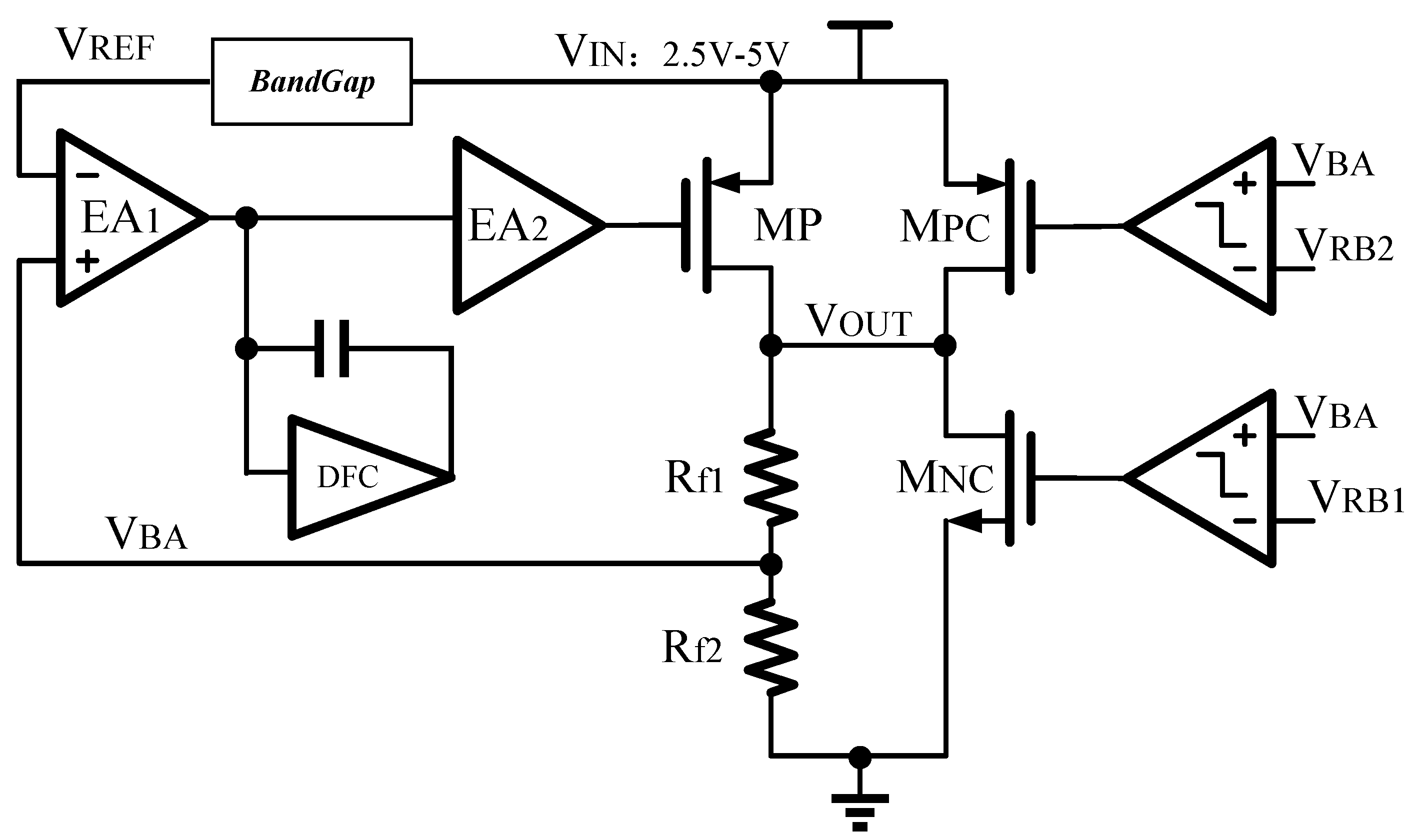

2. Circuit Implementation

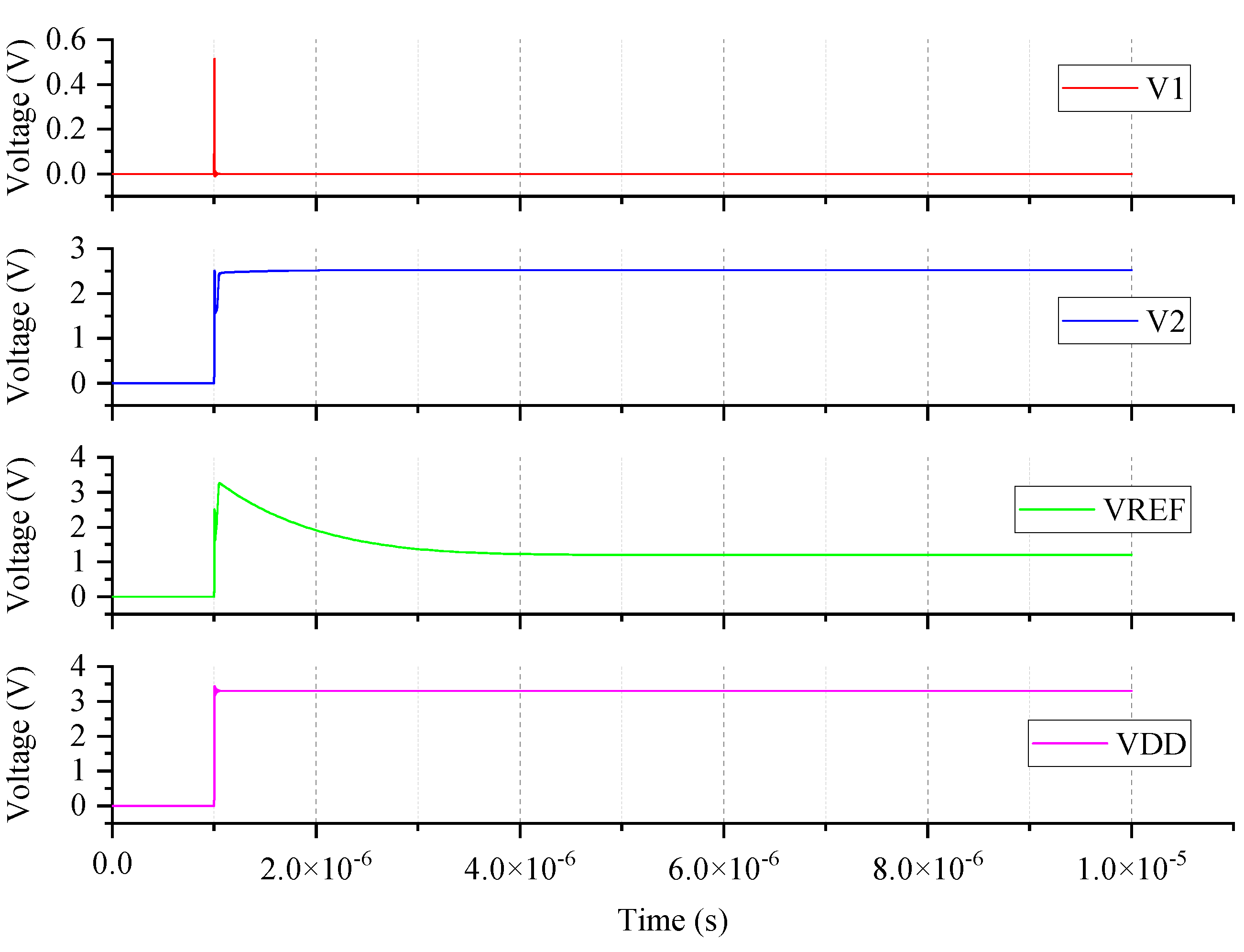

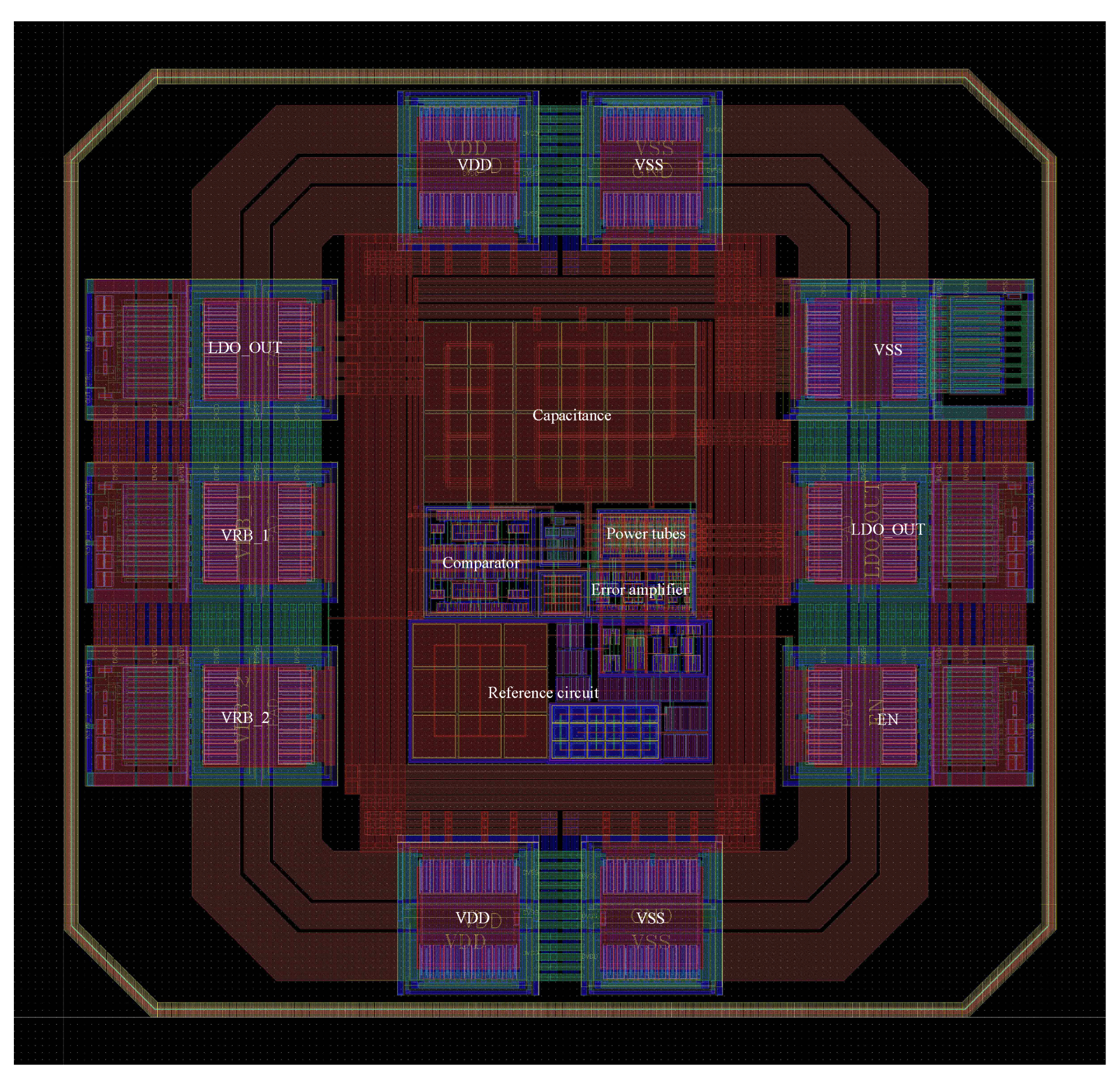

2.1. Reference Circuit

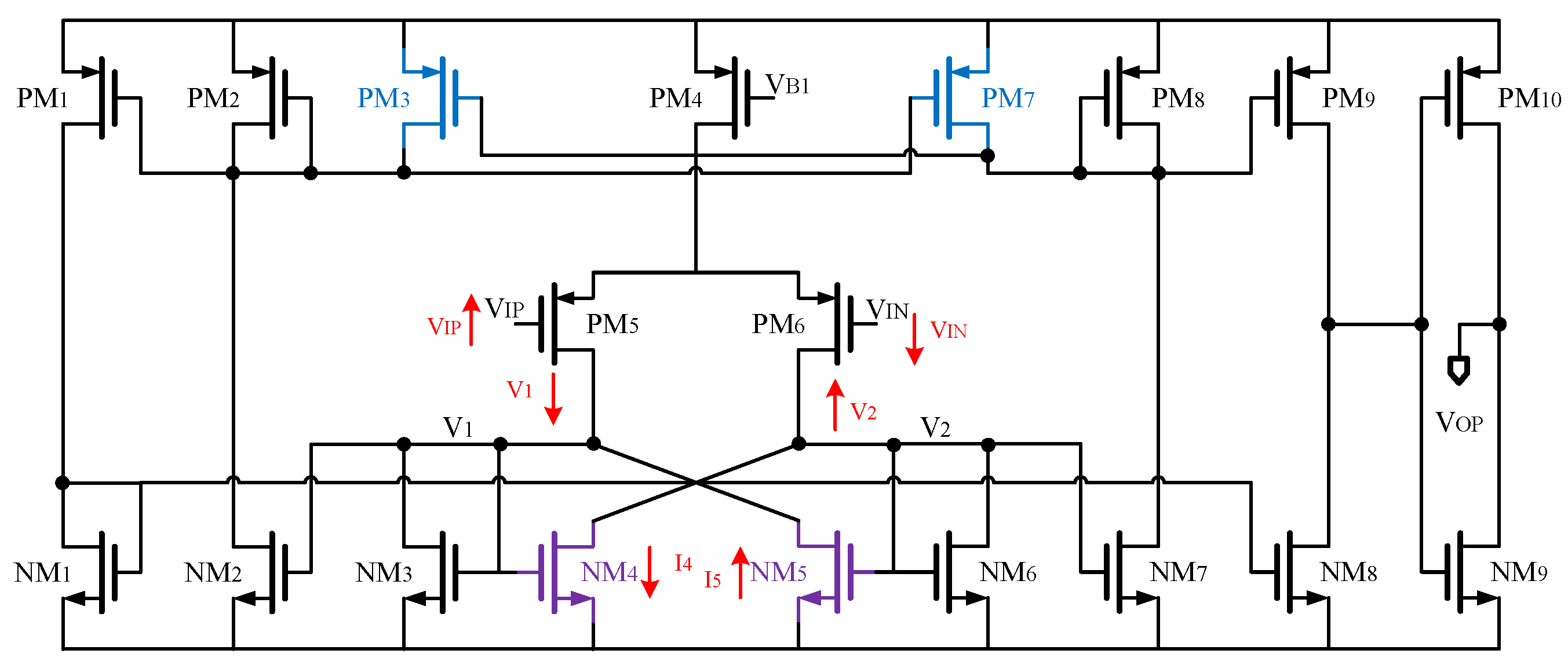

2.2. Error Amplifier and DFC

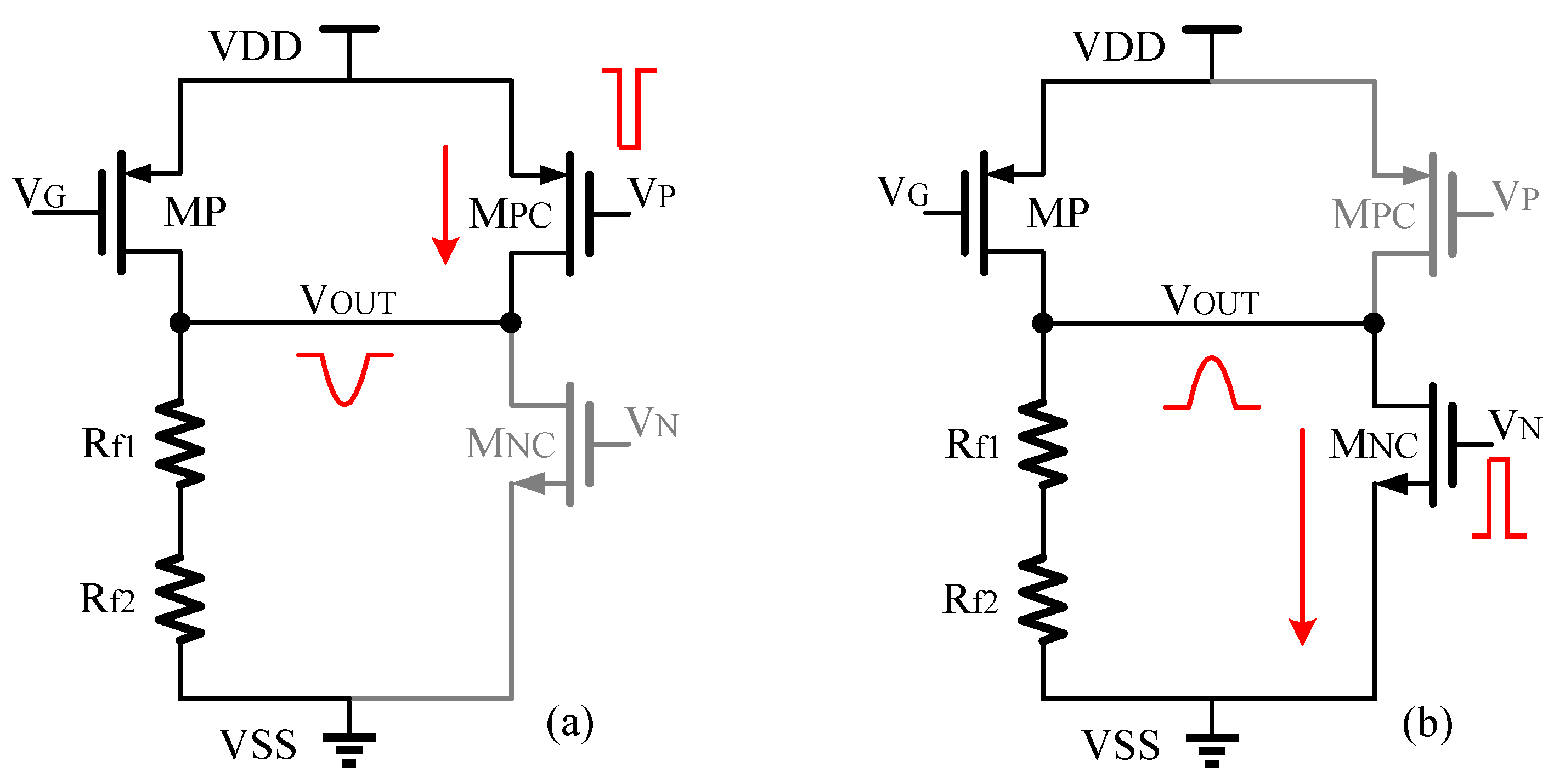

2.3. Fast Feedback Loop

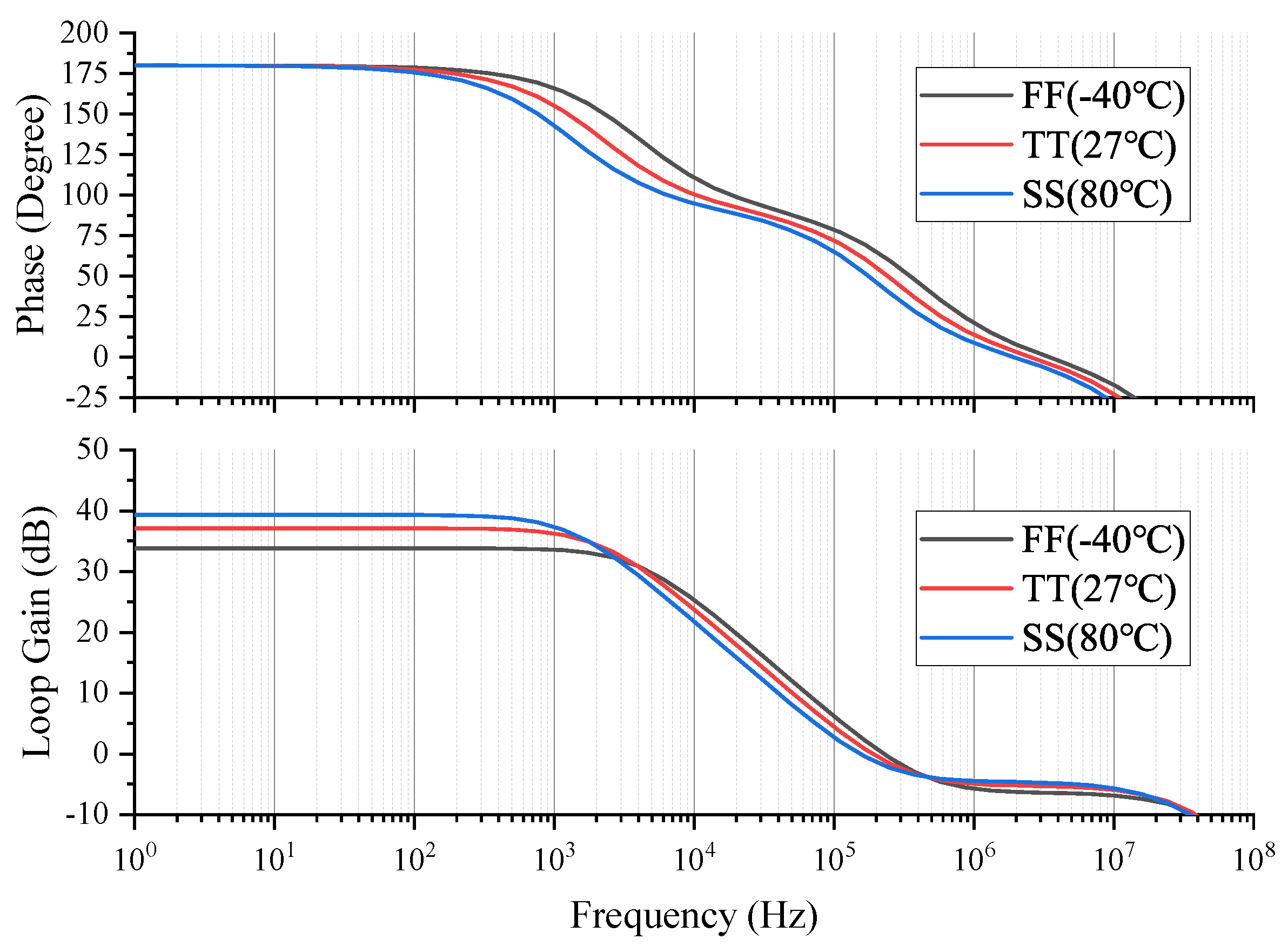

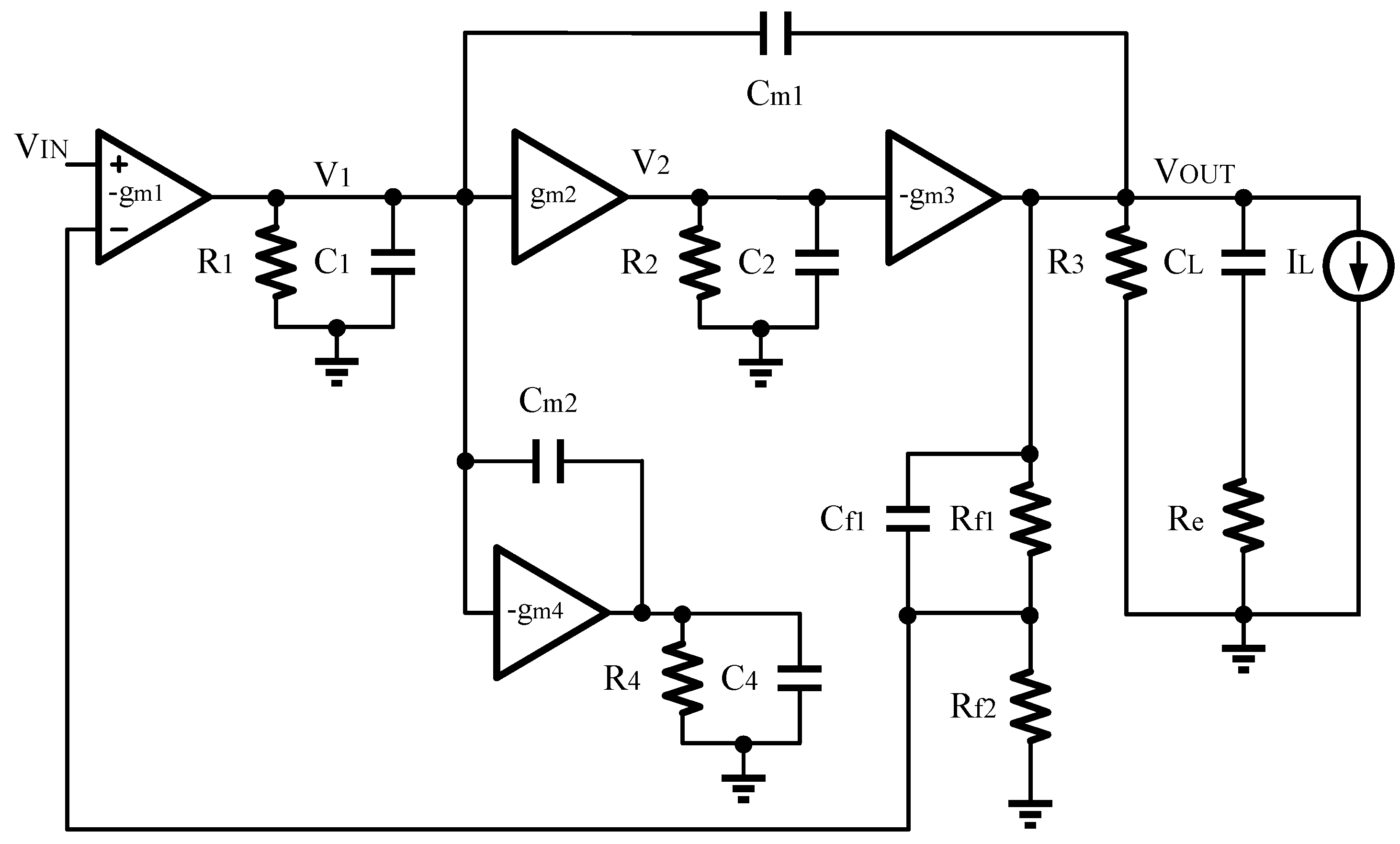

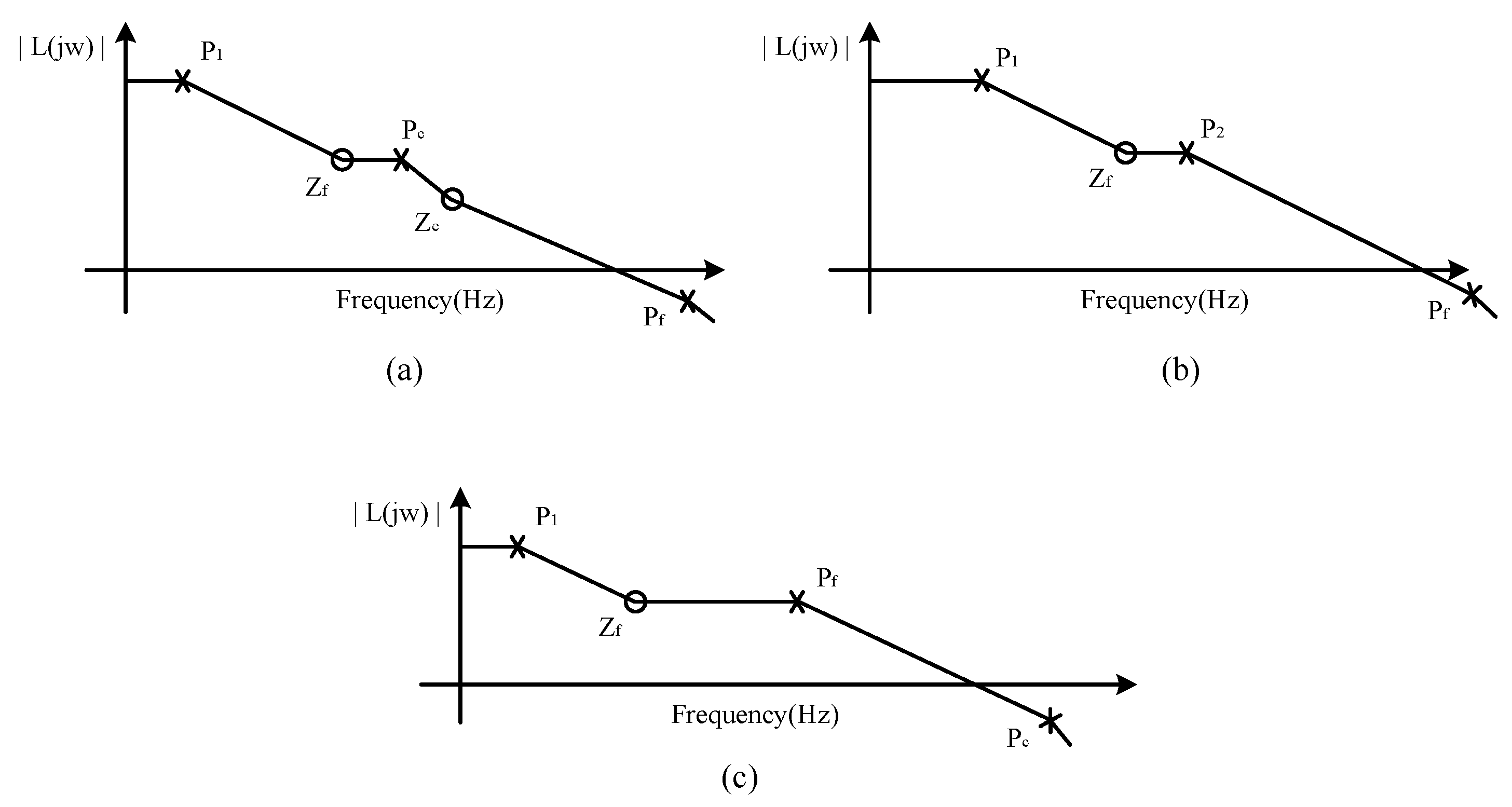

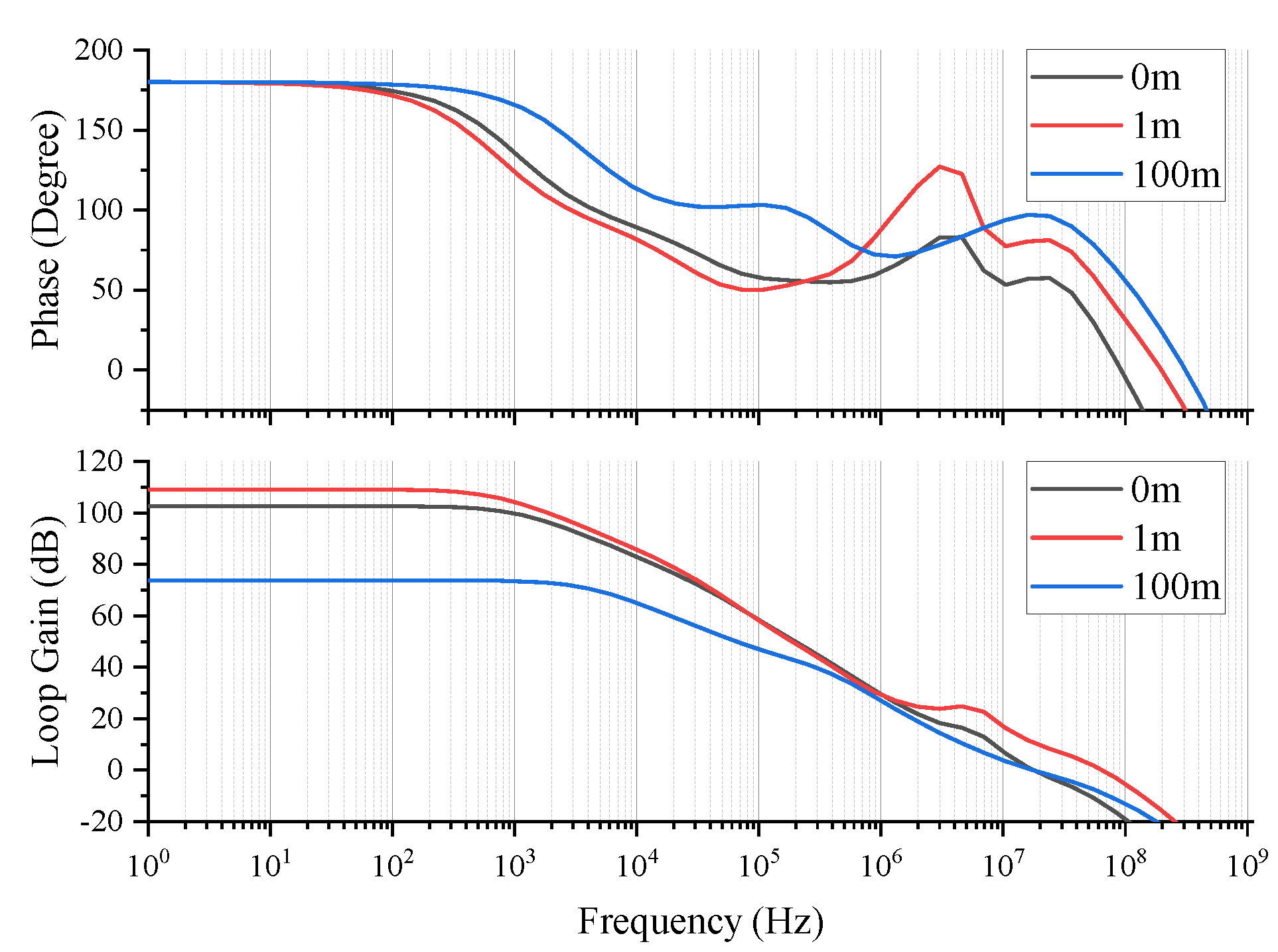

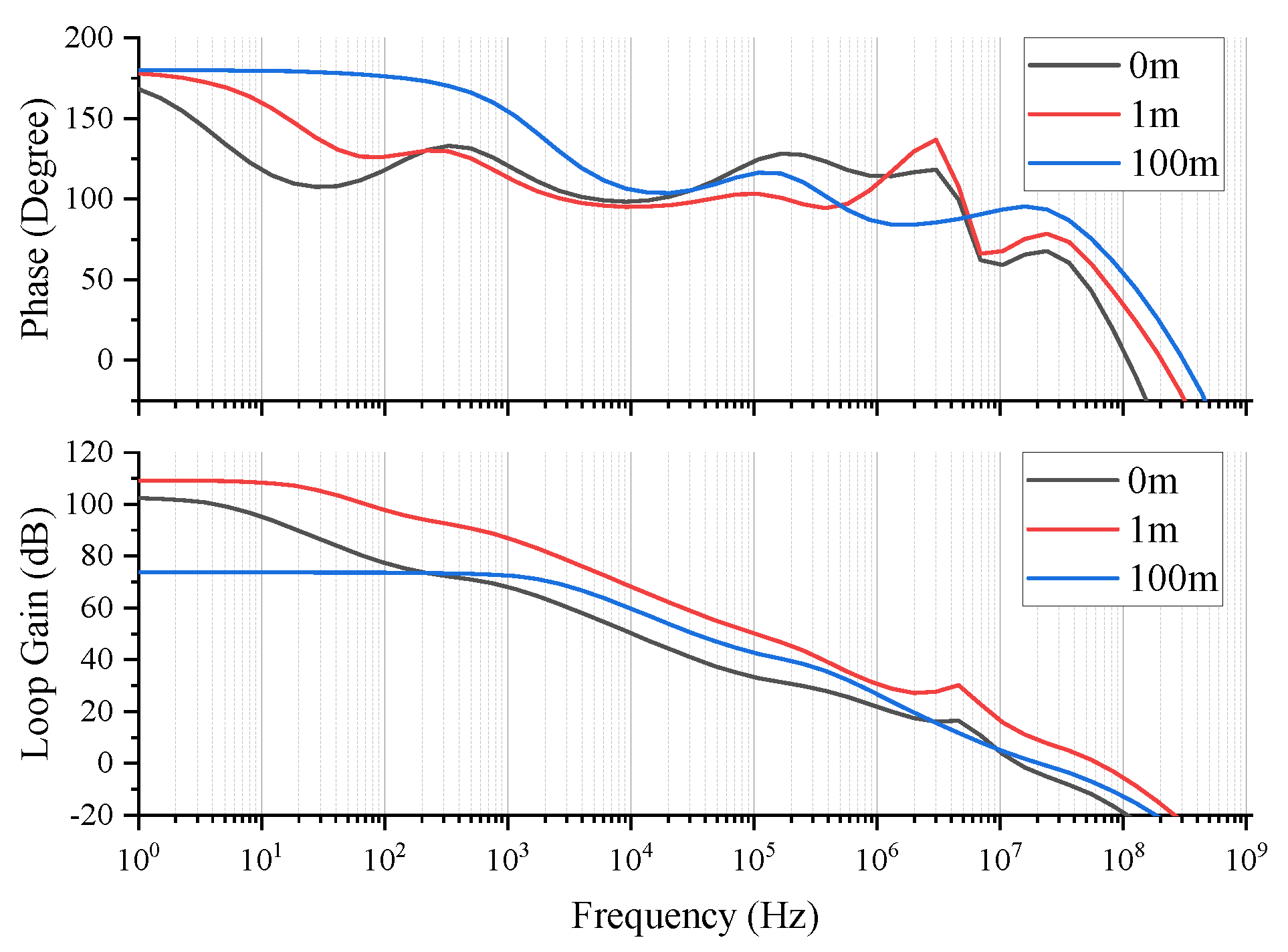

3. Frequency Compensation

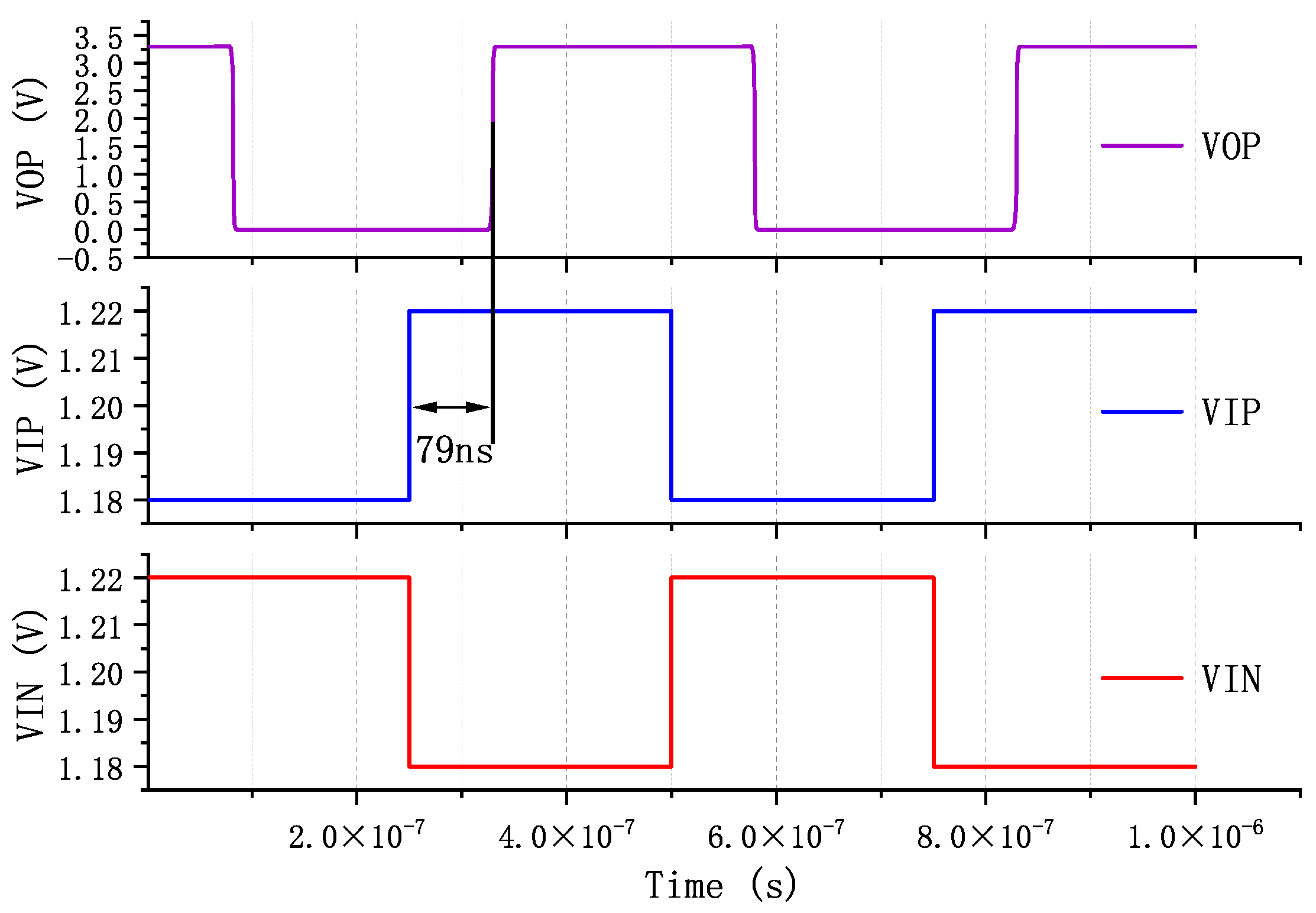

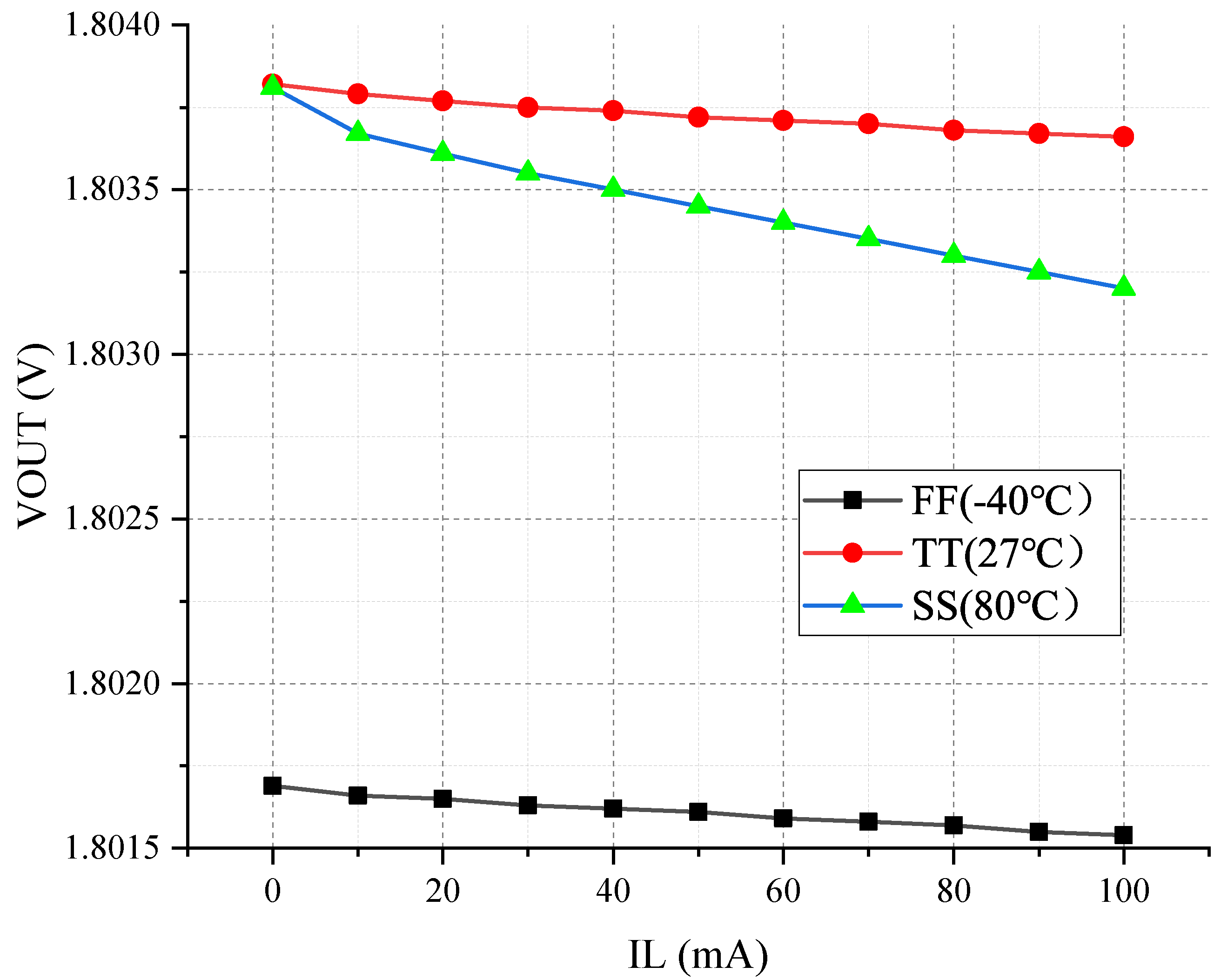

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chong, S.; Chan, P.K. A 0.9-/spl mu/A Quiescent Current Output-Capacitorless LDO Regulator with Adaptive Power Transistors in 65-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1072–1081. [Google Scholar] [CrossRef]

- Desai, C.; Mandal, D.; Bakkaloglu, B.; Kiaei, S. A 1.66 mV FOM Output Cap-Less LDO with Current-Reused Dynamic Biasing and 20 ns Settling Time. IEEE Solid-State Circuits Lett. 2018, 1, 50–53. [Google Scholar] [CrossRef]

- Guo, J.; Leung, K.N. A 6-μ W Chip-Area-Efficient Output-Capacitorless LDO in 90-nm CMOS Technology. IEEE J. Solid-State Circuits 2010, 45, 1896–1905. [Google Scholar] [CrossRef]

- Kim, Y.i.; Lee, S.S. A Capacitorless LDO Regulator with Fast Feedback Technique and Low-Quiescent Current Error Amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2013, 60, 326–330. [Google Scholar] [CrossRef]

- Han, W.; Lee, H. A 340-nA-Quiescent 80-mA-Load 0.02-fs-FOM Active-Capacitor-Based Low-Dropout Regulator in Standard 0.18-μm CMOS. IEEE Solid-State Circuits Lett. 2021, 4, 125–128. [Google Scholar] [CrossRef]

- Mandal, D.; Desai, C.; Bakkaloglu, B.; Kiaei, S. Adaptively Biased Output Cap-Less NMOS LDO with 19 ns Settling Time. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 167–171. [Google Scholar] [CrossRef]

- Jiang, Y.; Wang, L.; Wang, S.; Cui, M.; Zheng, Z.; Li, Y. A Low-Power, Fast-Transient Output-Capacitorless LDO with Transient Enhancement Unit and Current Booster. Electronics 2022, 11, 701. [Google Scholar] [CrossRef]

- Limpisawas, T.; Wattanapanitch, W. A Low-Power Wide-Load-Range Output-Capacitorless Low-Dropout Voltage Regulator with Indirect-Direct Nested Miller Compensation. IEEE Access 2022, 10, 67396–67412. [Google Scholar] [CrossRef]

- Shen, L.; Yan, Z.; Zhang, X.; Zhao, Y.; Wang, Y. Design of High-Performance Voltage Regulators Based on Frequency-Dependent Feedback Factor. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems (ISCAS), New Orleans, LA, USA, 27–30 May 2007; pp. 3828–3831. [Google Scholar] [CrossRef]

- Leung, K.N.; Mok, P. A capacitor-free CMOS low-dropout regulator with damping-factor-control frequency compensation. IEEE J. Solid-State Circuits 2003, 38, 1691–1702. [Google Scholar] [CrossRef]

- Tan, X.L.; Chong, S.S.; Chan, P.K.; Dasgupta, U. A LDO Regulator with Weighted Current Feedback Technique for 0.47 nF–10 nF Capacitive Load. IEEE J. Solid-State Circuits 2014, 49, 2658–2672. [Google Scholar] [CrossRef]

- Ho, E.N.Y.; Mok, P.K.T. A Capacitor-Less CMOS Active Feedback Low-Dropout Regulator with Slew-Rate Enhancement for Portable On-Chip Application. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 80–84. [Google Scholar] [CrossRef]

- Leung, K.N.; Mok, P.; Ki, W.H.; Sin, J. Three-stage large capacitive load amplifier with damping-factor-control frequency compensation. IEEE J. Solid-State Circuits 2000, 35, 221–230. [Google Scholar] [CrossRef]

- Leung, K.N.; Mok, P. Analysis of multistage amplifier-frequency compensation. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2001, 48, 1041–1056. [Google Scholar] [CrossRef]

- Liang, Y.; Diao, S. A Capacitor-Free Low-Dropout Regulator with Low Line Regulation Rate and High Stability. In Proceedings of the 2021 14th International Congress on Image and Signal Processing, BioMedical Engineering and Informatics (CISP-BMEI), Shanghai, China, 23–25 October 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Li, G.; Qian, H.; Guo, J.; Mo, B.; Lu, Y.; Chen, D. Dual Active-Feedback Frequency Compensation for Output-Capacitorless LDO with Transient and Stability Enhancement in 65-nm CMOS. IEEE Trans. Power Electron. 2020, 35, 415–429. [Google Scholar] [CrossRef]

- Gao, M.; Cai, X.; Yan, W.; Zhao, H.; Xia, R.; Gao, Y. A wide input range, external capacitor-less LDO with fast transient response. IEICE Electron. Express 2023, 20, 20230008. [Google Scholar] [CrossRef]

- Lee, Y.S.; Im, Y.C.; Lee, H.; Kim, Y.S. Capless Low-Dropout Regulator with a Dual Feedback Loop and Voltage Dampers. In Proceedings of the 2022 19th International SoC Design Conference (ISOCC), Gangneung-si, Republic of Korea, 19–22 October 2022; pp. 298–299. [Google Scholar] [CrossRef]

- Wook, K.S.; Koo, Y.S. Design of high-reliability LDO regulator with SCR based ESD protection circuit using body technique and load transient detection. IEICE Electron. Express 2022, 19, 20220110. [Google Scholar] [CrossRef]

- Hicham, A.; Qjidaa, H. A 500μA low drop-out voltage regulator in 90-nm CMOS technology. In Proceedings of the 2012 IEEE International Conference on Complex Systems (ICCS), Agadir, Morocco, 5–6 November 2012; pp. 1–4. [Google Scholar] [CrossRef]

- Chen, C.M.; Hung, C.C. A capacitor-free CMOS low-dropout voltage regulator. In Proceedings of the 2009 IEEE International Symposium on Circuits and Systems, Taipei, Taiwan, 24–27 May 2009; pp. 2525–2528. [Google Scholar] [CrossRef]

- Abbasi, M.U.; Bagnall, D.; Bn, V. A high PSRR capacitor-less on—Chip low dropout voltage regulator. In Proceedings of the IEEE 8th International Symposium on Intelligent Systems and Informatics, Subotica, Serbia, 10–11 September 2010; pp. 361–364. [Google Scholar] [CrossRef]

- Hsiao, S.W.; Huang, Y.C.; Liang, D.; Chen, H.W.; Chen, H.S. A 1.5-V 10-ppm//spl deg/C 2nd-order curvature-compensated CMOS bandgap reference with trimming. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems (ISCAS), Kos, Greece, 21–24 May 2006; pp. 565–568. [Google Scholar] [CrossRef]

- Perry, R.T.; Lewis, S.H.; Brokaw, A.P.; Viswanathan, T.R. A 1.4 V Supply CMOS Fractional Bandgap Reference. IEEE J. Solid-State Circuits 2007, 42, 2180–2186. [Google Scholar] [CrossRef]

- Leung, K.N.; Mok, P. A sub-1-V 15-ppm//spl deg/C CMOS bandgap voltage reference without requiring low threshold voltage device. IEEE J. Solid-State Circuits 2002, 37, 526–530. [Google Scholar] [CrossRef]

- Ni, S.; Chen, Z.; Hu, C.; Chen, H.; Wang, Q.; Li, X.; Song, S.; Song, Z. An Output-Capacitorless Low-Dropout Regulator with Slew-Rate Enhancement. Micromachines 2022, 13, 1594. [Google Scholar] [CrossRef]

- Guo, Z.; Li, H.; Li, D.; Fan, S.; Gui, X.; Xue, Z.; Chen, Z.; Geng, L. Topological Classification-Based Splitting–Combining Methodology for Analysis of Complex Multi-Loop Systems and Its Application in LDOs. IEEE Trans. Power Electron. 2019, 34, 7025–7039. [Google Scholar] [CrossRef]

- Kao, S.K.; Chen, J.J.; Liao, C.H. A Multipath Output-Capacitor-Less LDO Regulator. IEEE Access 2022, 10, 27185–27196. [Google Scholar] [CrossRef]

- Giustolisi, G.; Palumbo, G.; Spitale, E. Robust Miller Compensation with Current Amplifiers Applied to LDO Voltage Regulators. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 1880–1893. [Google Scholar] [CrossRef]

- Ming, X.; Kuang, J.J.; Gong, X.C.; Lin, Z.; Xiong, J.; Qin, Y.; Wang, Z.; Zhang, B. A Fast-Transient Capacitorless LDO with Dual Paths Active-Frequency Compensation Scheme. IEEE Trans. Power Electron. 2022, 37, 10332–10347. [Google Scholar] [CrossRef]

- Sakolski, O.; Poongodan, P.K.; Vanselow, F.; Maurer, L. A Feedforward Compensated High-Voltage Linear Regulator with Fast Response, High-Current Sinking Capability. IEEE Solid-State Circuits Lett. 2020, 3, 114–117. [Google Scholar] [CrossRef]

- Lu, Y.; Chen, M.; Wang, K.; Yang, Y.; Wang, H. A Capacitorless Flipped Voltage Follower LDO with Fast Transient Using Dynamic Bias. Electronics 2022, 11, 3009. [Google Scholar] [CrossRef]

| Reference | [30] | [17] | [11] | [31] | [29] | [27] | This Work |

|---|---|---|---|---|---|---|---|

| Year | 2022 | 2023 | 2014 | 2020 | 2012 | 2019 | 2023 |

| Technology (nm) | 350 | 500 | 65 | 180 | 350 | 180 | 180 |

| Chip size (mm) | 0.077 | 0.29 | 0.013 | 0.15 | 0.4 | 0.18 | 0.068 |

| (V) | 2.7∼3.3 | 5.2–20 | 0.75∼1.2 | 70 | 1.2∼1.5 | 3.3 | 2.5–5 |

| (V) | 2.5 | 5 | 0.6 | 66 | 1 | 2.8 | 1.8 |

| IQ (A) | 66 | 244 | 15.9–478 | 288 | 45 | 32 | 76 |

| (max)(mA) | 100 | 100 | 50 | 100 | 50 | 100 | 100 |

| (min)(mA) | 0.01 | 0.22 | 0 | 0 | 1 | 0 | 0 |

| Line regulation (mV/V) | 0.8 | 0.88 | 4 | 90 | N/A | 5.7 | 0.128 |

| Load regulation (mV/mA) | 0.06 | 0.22 | 0.18 | 1.7 | N/A | 0.028 | 0.0017 |

| (min)(pF) | 14 | 5 | 474.1 | 6 | 41 | 1,000,100 | 9 |

| (on-chip capacitance) (pF) | 14 | 5 | 4.1 | 6 | 41 | 100 | 9 |

| (mV) | 255 | 70 | 113 | 2480 | 70 | 640 | 37 |

| PSRR (dB) | −41 (10 kHz) | −49 (100 kHz) | −51 (1 kHz) | N/A | N/A | N/A | −46 (1 kHz) |

| Setting time (s) | 0.7 | 2 | 0.25 | 1.63 | 4 | 52 | 1.6 (99%) |

| Edge time (s) | 0.4 | 1 | 0.1 | 0.3 | 1 | 0.1 | 1 |

| Edge time ratio K | 4 | 10 | 1 | 3 | 10 | 1 | 10 |

| FOM (V × pF/A) | 9.43 | 8.5 | 102.4 | 128.56 | 51.7 | 204,820.5 | 2.531 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ning, Y.; Guo, J.; Jia, Y.; Li, D.; Guo, G. A Capacitorless LDO Regulator with Fast Feedback Loop and Damping-Factor-Control Frequency Compensation. Electronics 2023, 12, 4067. https://doi.org/10.3390/electronics12194067

Ning Y, Guo J, Jia Y, Li D, Guo G. A Capacitorless LDO Regulator with Fast Feedback Loop and Damping-Factor-Control Frequency Compensation. Electronics. 2023; 12(19):4067. https://doi.org/10.3390/electronics12194067

Chicago/Turabian StyleNing, Yongkai, Jiangfei Guo, Yangchen Jia, Duosheng Li, and Guiliang Guo. 2023. "A Capacitorless LDO Regulator with Fast Feedback Loop and Damping-Factor-Control Frequency Compensation" Electronics 12, no. 19: 4067. https://doi.org/10.3390/electronics12194067

APA StyleNing, Y., Guo, J., Jia, Y., Li, D., & Guo, G. (2023). A Capacitorless LDO Regulator with Fast Feedback Loop and Damping-Factor-Control Frequency Compensation. Electronics, 12(19), 4067. https://doi.org/10.3390/electronics12194067