Research and Implementation of High-Efficiency and Low-Complexity LDPC Coding Algorithm

Abstract

:1. Introduction

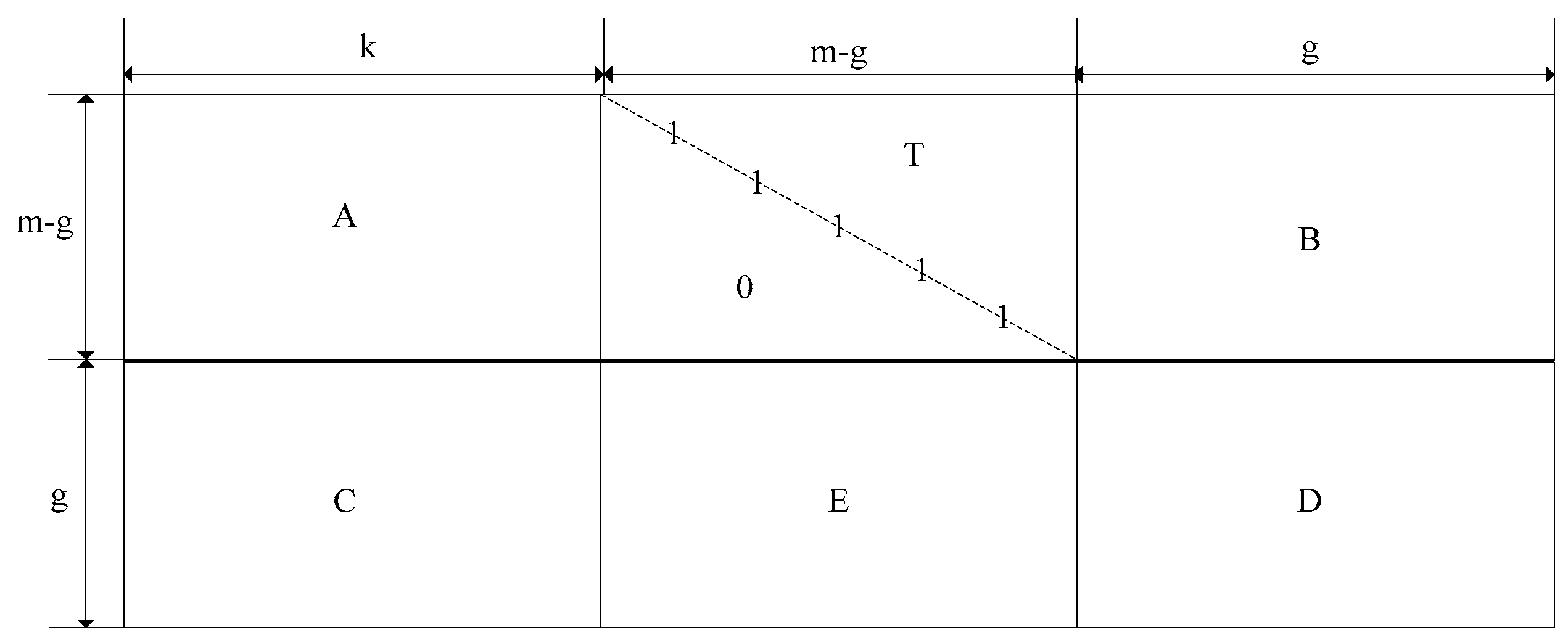

2. LDPC Code in the IEEE802.16e Standard

3. LDPC Coding Algorithm

3.1. Standard Coding Algorithm

3.2. Recursive-Iterative Coding Algorithm

3.3. High-Efficiency and Low-Complexity Coding Algorithm (HE-LC)

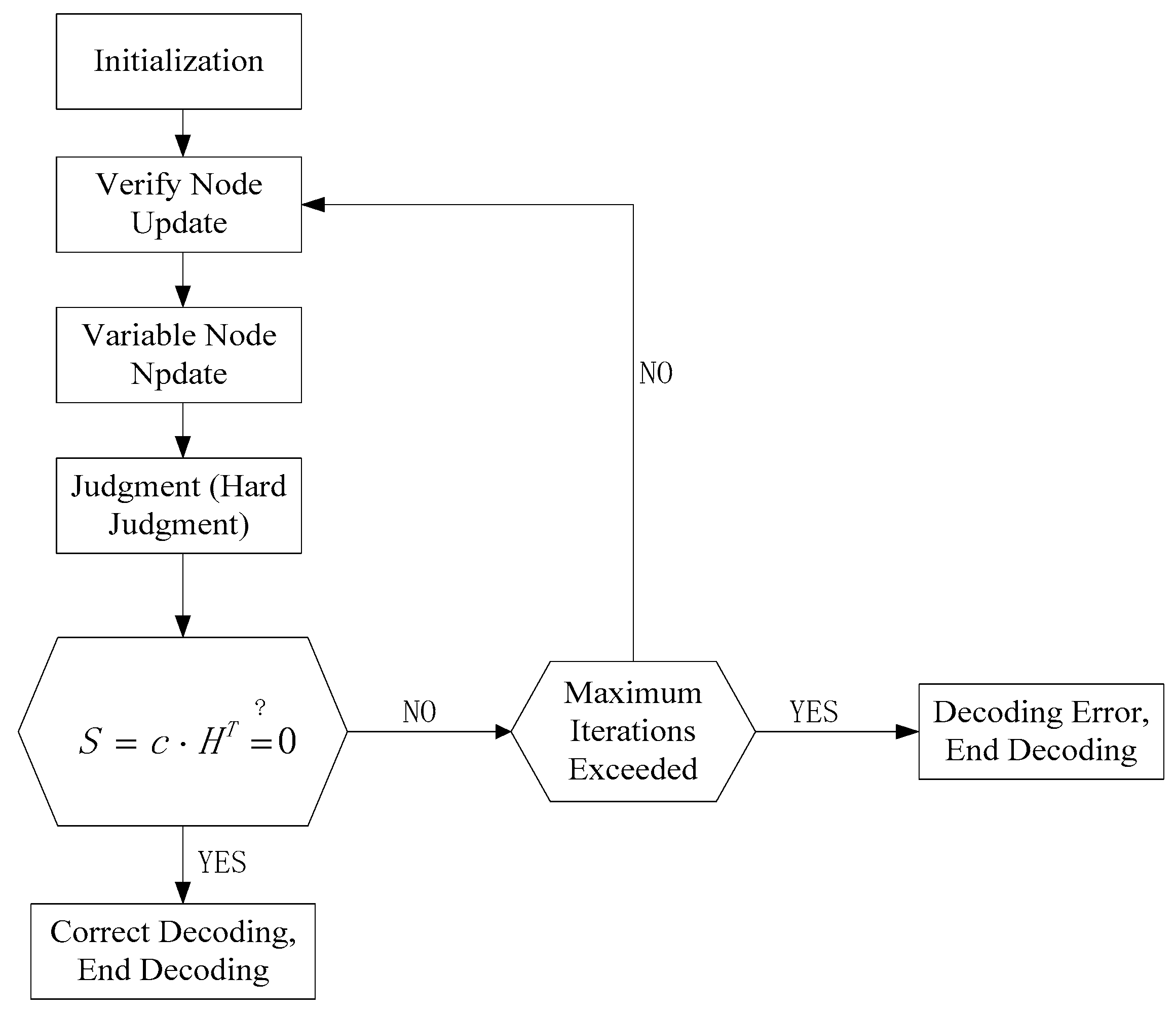

4. LDPC Decoding Algorithm

4.1. Log-Likelihood Ratio-Belief Propagation (LLR–BP) Algorithm

4.2. Min-Sum Algorithm(MSA)

5. Design and Implementation of the Codec

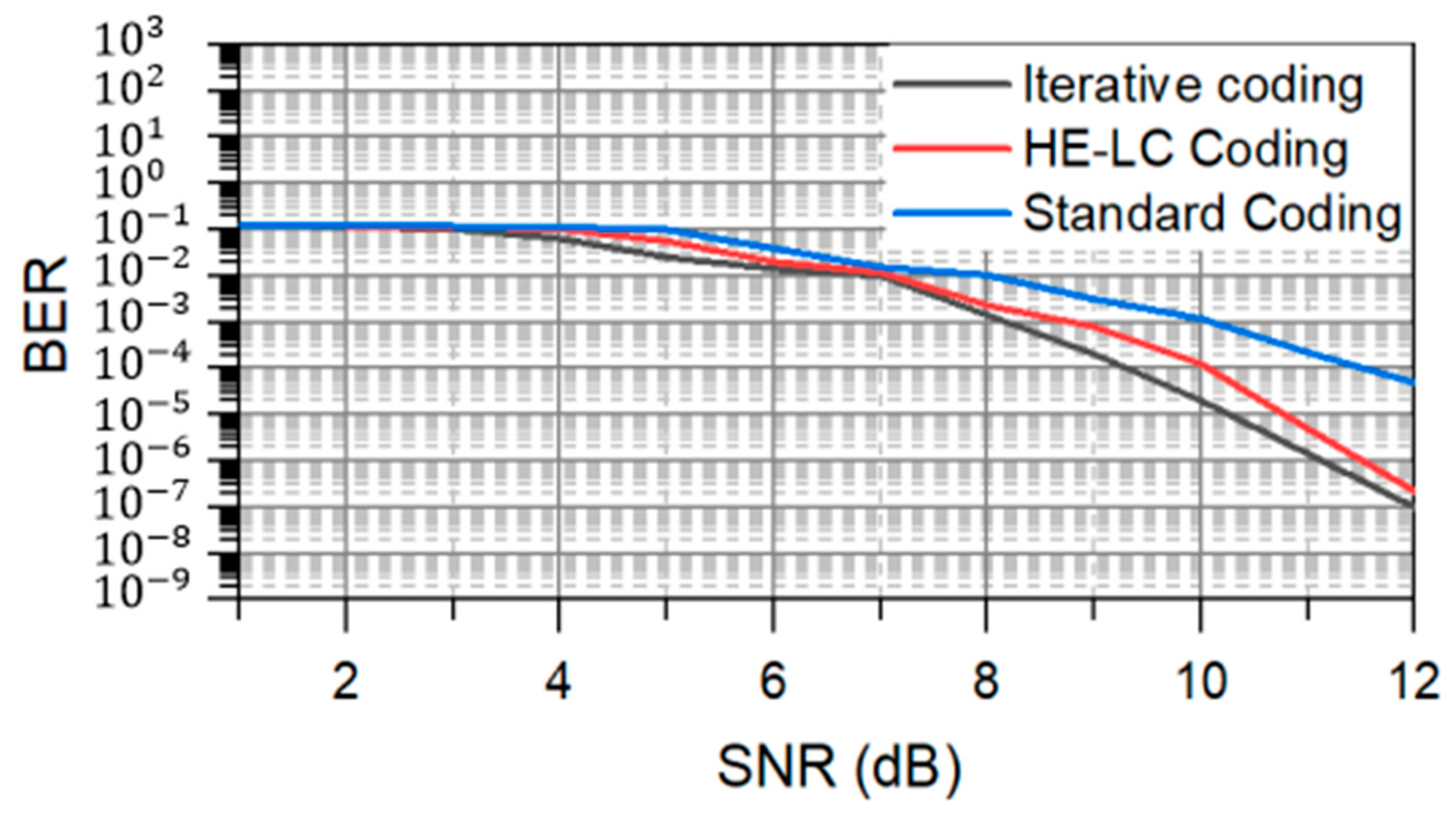

5.1. Performance Analysis of Codec Algorithm

5.2. Coder Design and Implementation

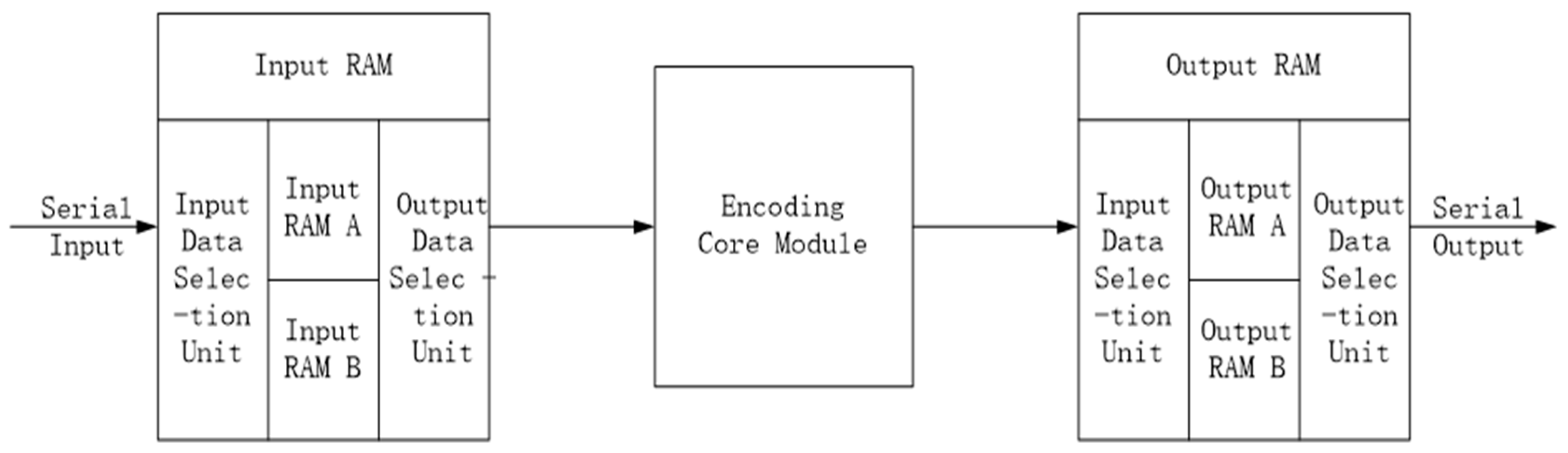

5.2.1. Coder Design

- ①

- Input/output RAM module

- ②

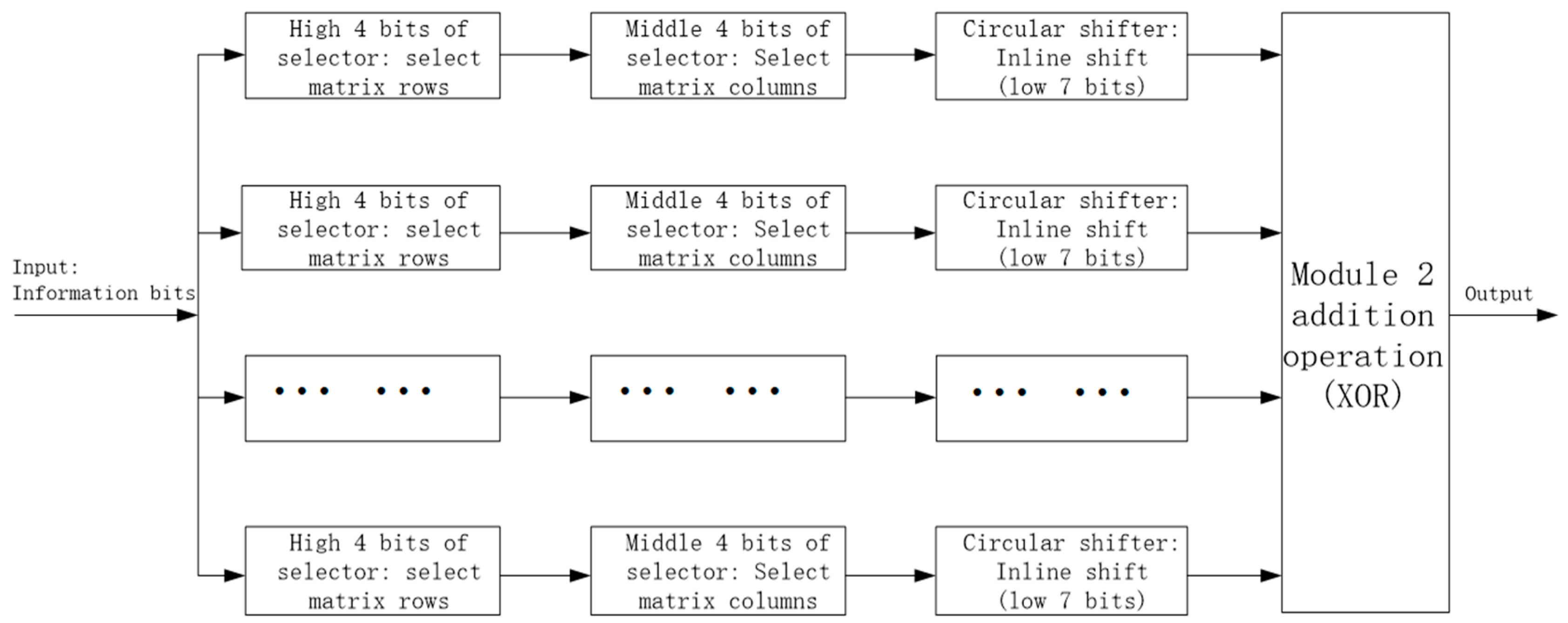

- Matrix Multiplier (MVM) Module

- ③

- Forward Displacer (FS) Module

- ④

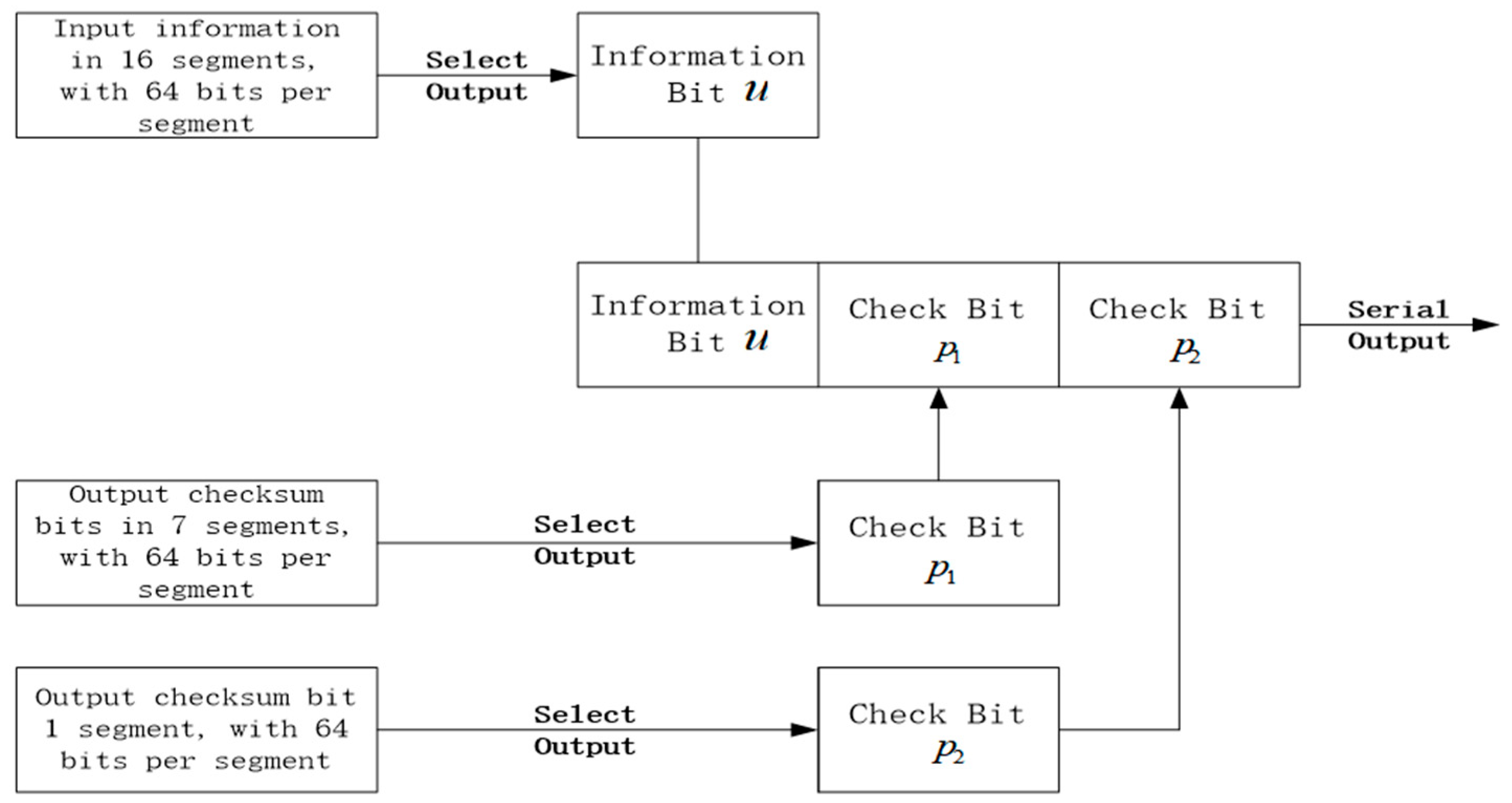

- Code word generator (CWG) module

- ⑤

- Other modules

5.2.2. Coder Implementation

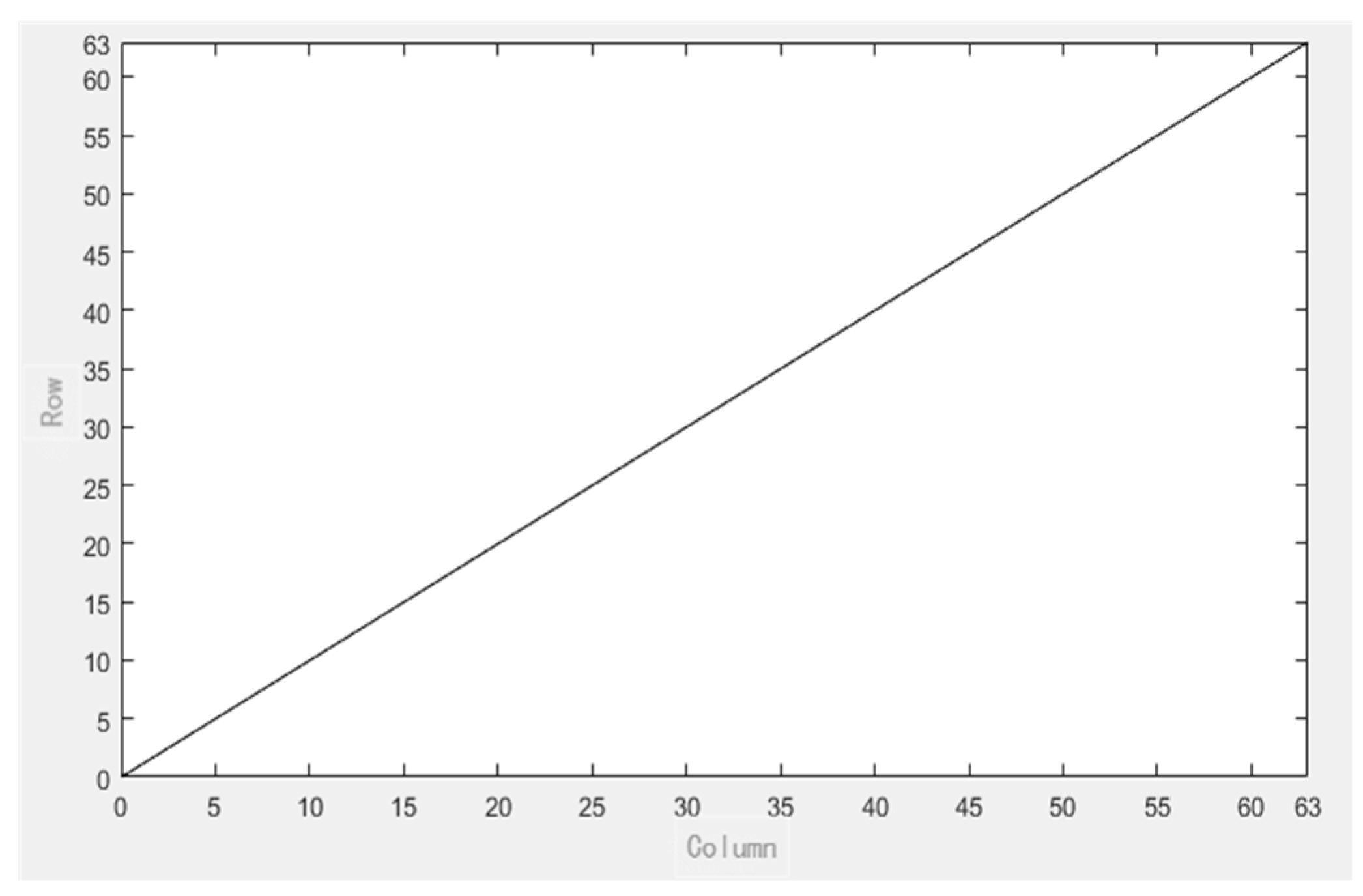

- ①

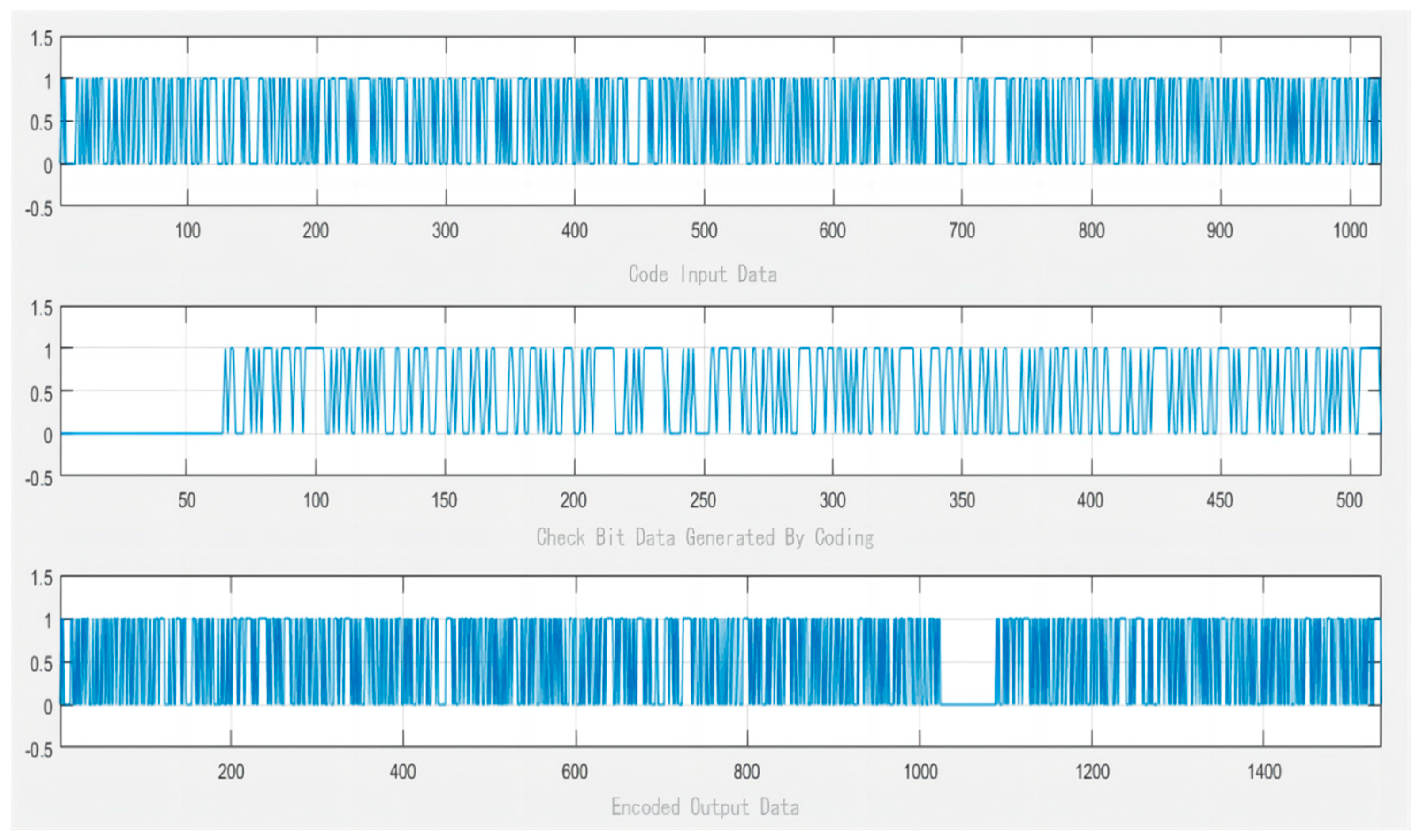

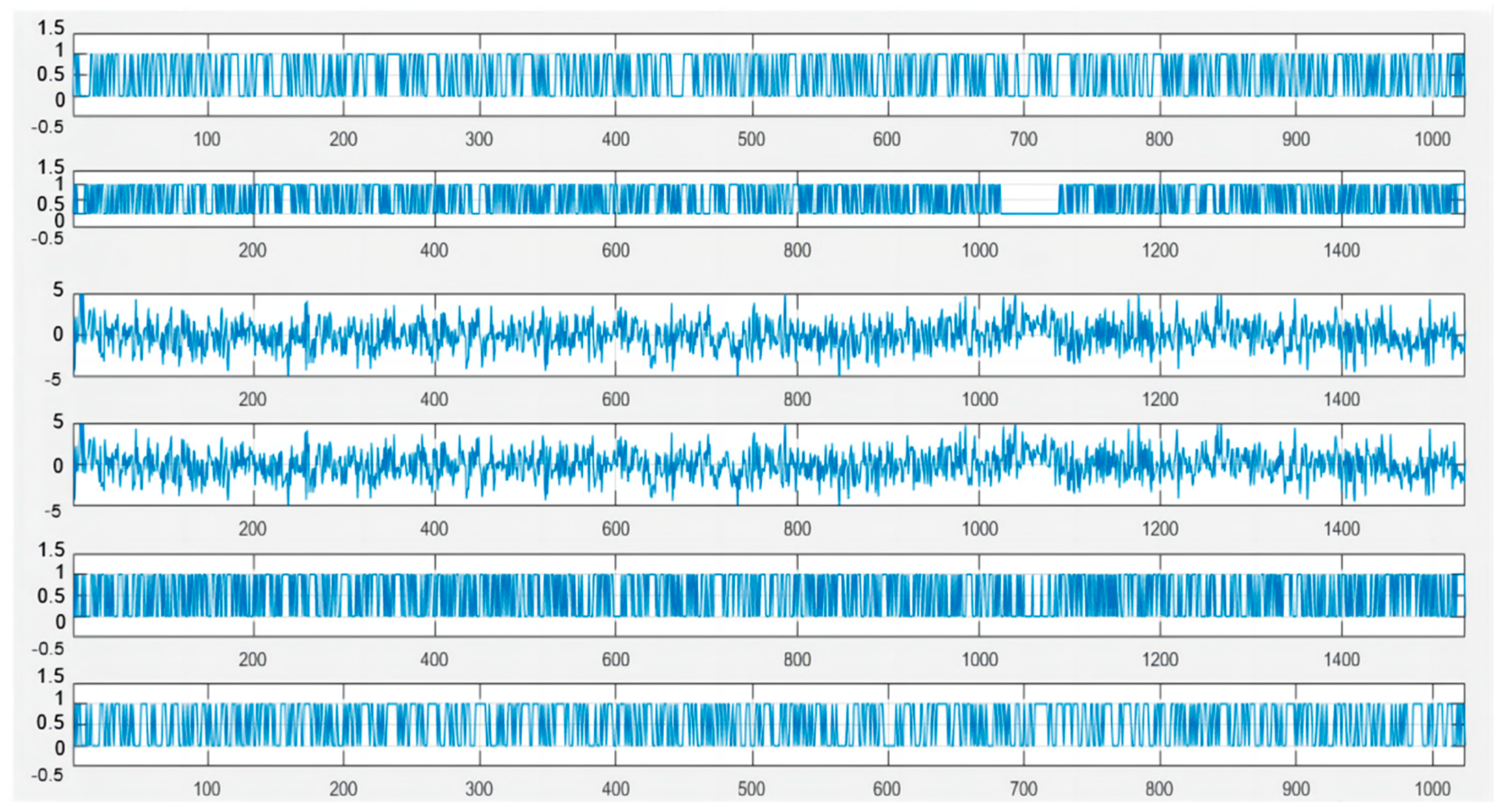

- MATLAB simulation results

- ②

- FPGA Implementation Results

5.3. Decoder Design and Implementation

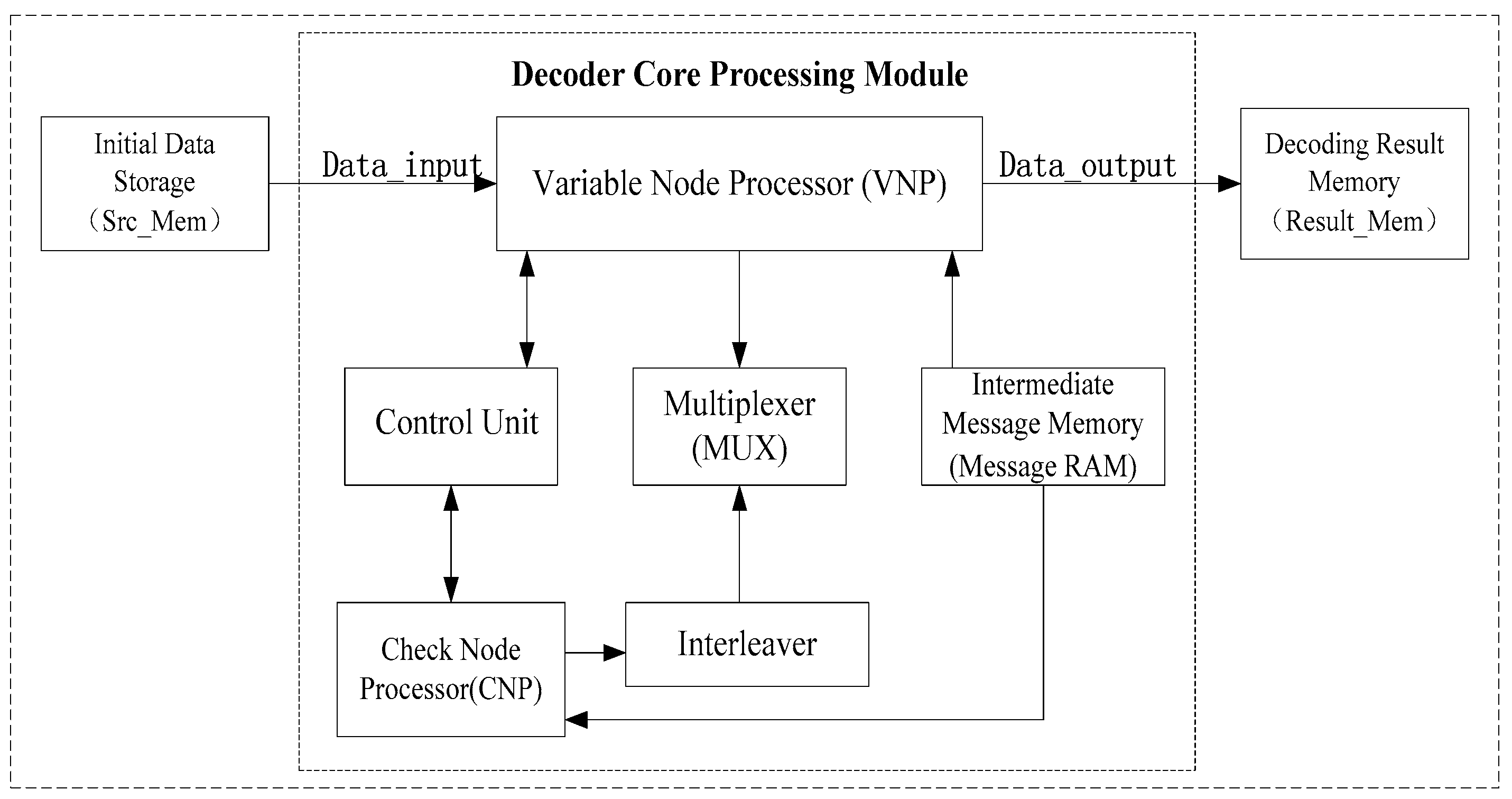

5.3.1. Decoder Design

- ①

- Variable Node Processor (VNP)

- ②

- Verify Node Processor (CNP)

- ③

- Message RAM

- ④

- Control Unit

- ⑤

- Interleaver

- ⑥

- Other module units

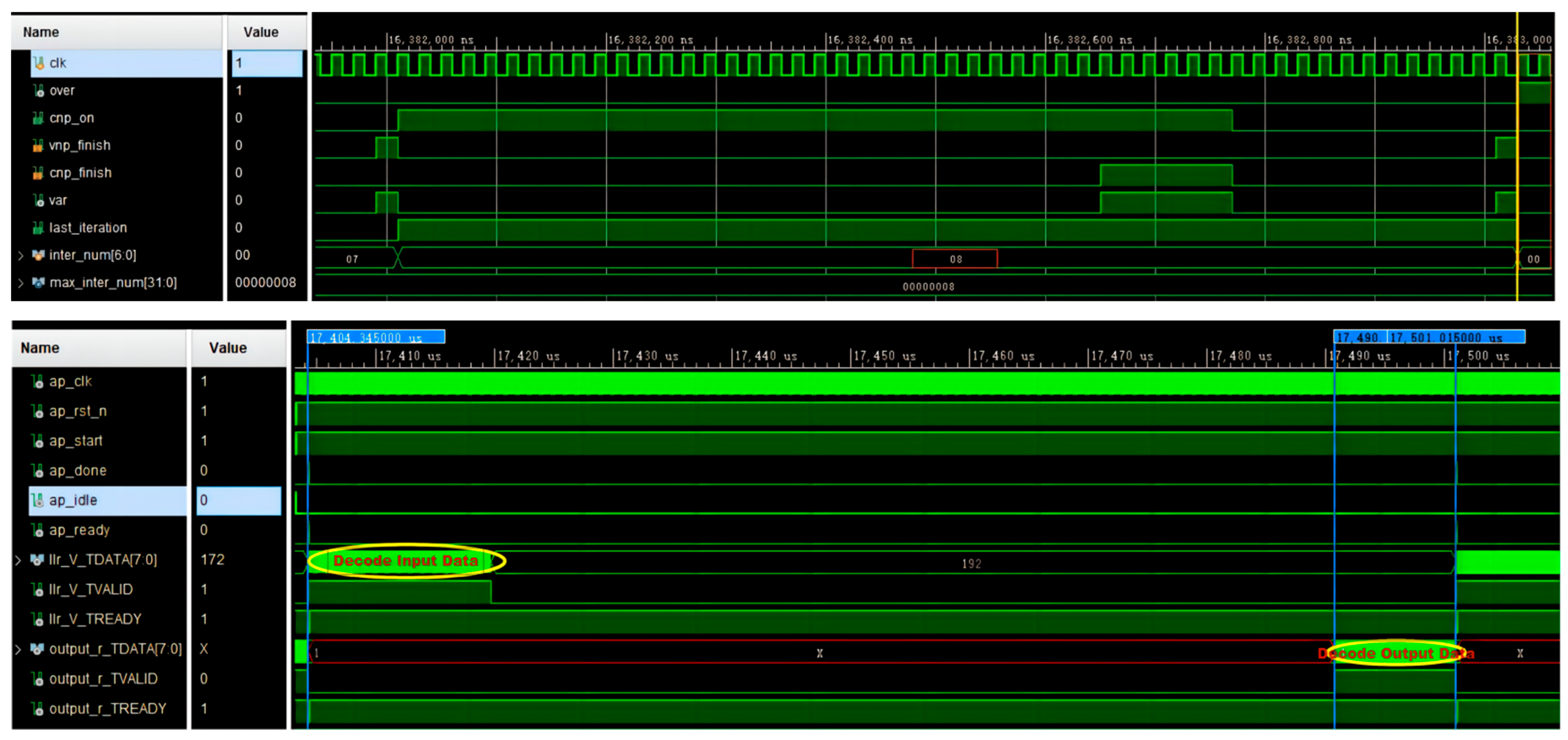

5.3.2. Decoder Implementation

- ①

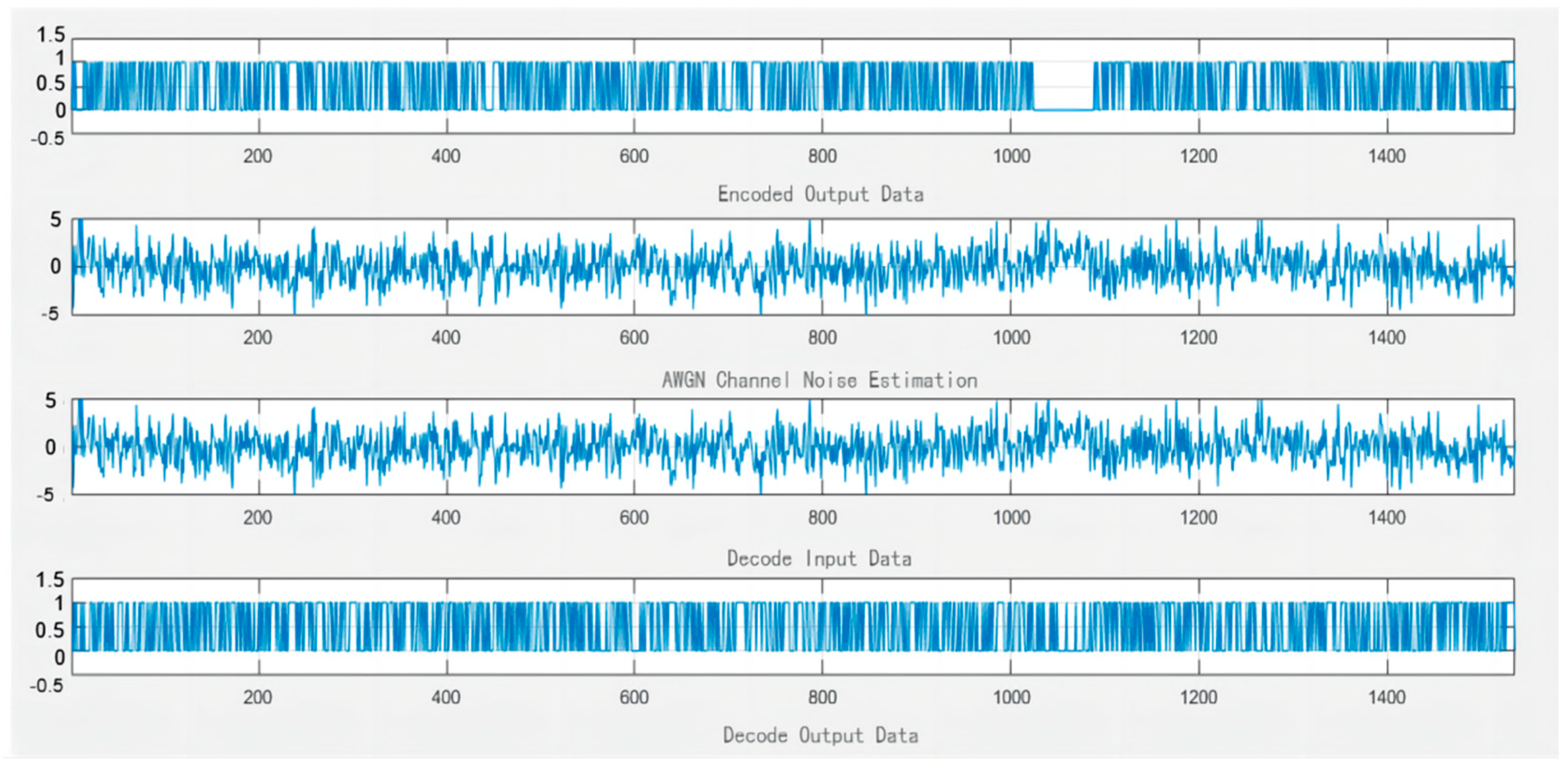

- MATLAB simulation results

- ②

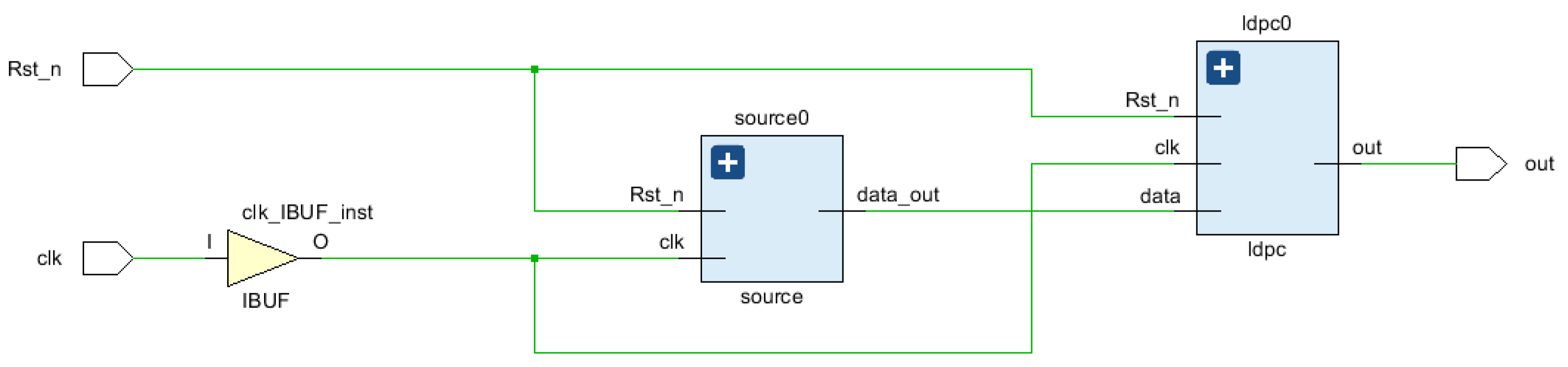

- FPGA Implementation Results

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Liao, X.; Yu, N.; Luo, Z.; Ren, X.; Fang, A. Research and Design of LDPC Codes Based on MATLAB/Simulink. J. Chengdu Univ. (Nat. Sci. Ed.) 2017, 36, 272–275+303. [Google Scholar]

- Gallager, R.G. Low Density Parity Check Codes. IRE Trans. Inf. Theory 1962, 8, 2018–2220. [Google Scholar] [CrossRef]

- MacKay, D.J.; Neal, R.M. Near Shannon Limit Performance of Low Density Parity Check Codes. Electron. Lett. 1996, 32, 1645–1646. [Google Scholar] [CrossRef]

- Xu, R. Design of LDPC Decoder for CCSDS Deep Space Communication Standard; Xi’an University of Technology: Xi’an, China, 2010; pp. 17–18. [Google Scholar]

- Yang, X. Turbo and LDPC Codec and Their Applications; People’s Posts and Telecommunications Publishing House: Beijing, China, 2010. [Google Scholar]

- Wang, M. Design and FPGA Implementation of High Speed LDPC Codec; University of Electronic Science and Technology: Chengdu, China, 2016. [Google Scholar]

- Guo, H. Research on Implementation of LDPC Codes Based on IEEE802.16e Standard; Harbin Institute of Technology: Harbin, China, 2010. [Google Scholar]

- Fan, K. Research and Implementation of LDPC Coding and Decoding Technology Based on IEEE802.16e; Xi’an University of Electronic Science and Technology: Xi’an, China, 2009. [Google Scholar]

- Wu, Z.; Zhang, L.; Zhong, Z.; Liu, R. Reconstruction of LDPC Sparse Check Matrix under High Bit Error Rate. J. Commun. 2021, 42, 1–10. [Google Scholar]

- Du, G. An overview of the principle and application of LDPC codes. China New Commun. 2012, 14, 25–33. [Google Scholar]

- Li, P.; Qi, F.; He, D.; Li, J. Design of IEEE 802.16e standard LDPC encoder based on FPGA. Mod. Navig. 2022, 13, 212–217+222. [Google Scholar]

- Guodong, W.A.; Jinming, L.I.; Zhiwang, Z.H.; Denghui, T.I. Design and Implementation of LDPC Encoder Based on FPGA. J. Meas. Sci. Instrum. 2021, 12, 12–19. [Google Scholar]

- Xue, W.; Yu, H.; Wang, J.; Shu, F. Optimization of High Efficiency LDPC Decoder and Implementation of FPGA. Data Acquis. Process. 2018, 33, 1101–1111. [Google Scholar]

- Sun, N. Research on Parity Check Matrix Construction and Decoding Optimization Algorithm of LDPC Codes; Shandong University: Jinan, China, 2019. [Google Scholar]

- Liao, P. Research and Design Implementation of LDPC Code High Speed Decoder in Deep Space Communication; Yanshan University: Qinghuangdao, China, 2022. [Google Scholar] [CrossRef]

- Shi, S.; Wang, R.; Li, H.; Han, C. Implementation of Multipath Parallel Encoder for LDPC Code. J. Electron. Meas. Instrum. 2021, 35, 83–89. [Google Scholar] [CrossRef]

- Shao, B. Research and Implementation of LDPC Code in 5G Communication System; Xi’an University of Electronic Science and Technology: Xi’an, China, 2022. [Google Scholar] [CrossRef]

- Richardson, T.J.; Urbanke, R.L. Efficient encoding of low-density parity-check codes. IEEE Trans. Inf. Theory 2001, 47, 638–655. [Google Scholar] [CrossRef]

- Lee, J.H.; Sunwoo, M.H. Low-Complexity High-Throughput Bit-Wise LDPC Decoder. J. Signal Process. Syst. 2019, 91, 855–862. [Google Scholar] [CrossRef]

- Zhang, C.; Su, K. Practice of Digital Signal Processing and Engineering Application of FPGA; China Railway Press: Beijing, China, 2013. [Google Scholar]

- Guo, L.; Chen, H. LDPC coding and decoding method based on FPGA for IEEE 802.16e. Autom. Technol. Appl. 2017, 36, 49–53. [Google Scholar]

- Shan, B.; Li, Z. Design and performance analysis of improved LDPC decoding scheme. Comput. Eng. Des. 2019, 40, 1507–1511. [Google Scholar]

- Chen, F. Low Complexity Deep Learning LDPC Decoding; Central South University for Nationalities: Wuhan, China, 2021. [Google Scholar] [CrossRef]

- Yang, H. Research and Implementation of LDPC Decoder in Satellite Communication; Xi’an University of Electronic Science and Technology: Xi’an, China, 2023. [Google Scholar] [CrossRef]

- Luo, X. Research on Hybrid Decoding Algorithms for LDPC Codes; University of Electronic Science and Technology: Chengdu, China, 2022. [Google Scholar] [CrossRef]

- Wang, D. Improvement of Decoding Algorithm Based on LDPC Code and FPGA Implementation; Nanjing University of Information Engineering: Nanjing, China, 2021. [Google Scholar] [CrossRef]

- Wang, L.; Li, J. Design and Implementation of LDPC Decoder Based on FPGA. Electron. Meas. Technol. 2022, 45, 22–27. [Google Scholar] [CrossRef]

- Li, J.; Chen, B. FPGA Implementation of QC-LDPC Decoder Based on Minimum Sum Algorithm. Appl. Sci. Technol. 2020, 47, 35–40. [Google Scholar]

- Chen, F.; Liu, Y.; Tang, C. A Low Complexity Normalized Minimum Sum Decoding Algorithm for LDPC Codes. J. Chongqing Univ. Posts Telecommun. (Nat. Sci. Ed.) 2020, 32, 92–98. [Google Scholar]

- Sun, J.; Li, J. LDPC Minimum Sum Decoding Algorithm and Its IC Physical Design. J. Meas. Sci. Instrum. 2023, 14, 108–115. [Google Scholar]

- Li, J.; Zhang, P.; Wang, L.; Wang, G. An FPGA LDPC decoder for optimizing scaling factors in NMS decoding algorithms. J. Meas. Sci. Instrum. 2022, 13, 398–406. [Google Scholar]

- Yang, P.; Jun, B.; No, J.S.; Park, H. A new two-stage decodingscheme with unreliable path search to lower the error-floor for low-density parity-check codes. IET Commun. 2017, 11, 2173–2180. [Google Scholar] [CrossRef]

- Han, X. Design and Optimization of LDPC Codec in High Speed WLAN System; Beijing University of Posts and Telecommunications: Beijing, China, 2014. [Google Scholar]

- Wang, H.; Guo, D. Design of LDPC decoder based on FPGA. J. Lul. Univ. 2019, 9, 34–40. [Google Scholar]

- Gu, S.; Luo, Z.; Chu, Y.; Xu, Y.; Guo, J. A Suboptimal Optimizing Strategy for Velocity Vector Estimation in Single-Observer Passive Localization. Sensors 2023, 23, 5940. [Google Scholar] [CrossRef]

| Step | Computational Formula |

|---|---|

| Step I | Calculate: , |

| Step II | Calculate: , |

| Step III | Calculate: |

| Step IV | Calculate: |

| Step V | Calculate: |

| Step VI | Calculate: |

| Operating Steps | Complexity |

|---|---|

| Operating Steps | Complexity |

|---|---|

| Site Type | Used | Fixed | Available | Util% |

|---|---|---|---|---|

| Slice LUTs * | 10,752 | 0 | 53,200 | 20.00 |

| LUT as Logic | 10,752 | 0 | 53,200 | 20.00 |

| LUT as Memory | 0 | 0 | 17,400 | 0.00 |

| Slice Registers | 12,658 | 0 | 106,400 | 12.00 |

| Register as Flip Flop | 12,658 | 0 | 106,400 | 12.00 |

| Register as Latch | 0 | 0 | 106,400 | 0.00 |

| F7 Muxes | 1904 | 0 | 26,600 | 7.00 |

| F8 Muxes | 888 | 0 | 13,300 | 7.00 |

| Site Type | Used | Fixed | Available | Util% |

|---|---|---|---|---|

| Slice LUTs * | 36,689 | 0 | 53,200 | 69.00 |

| LUT as Logic | 36,022 | 0 | 53,200 | 68.00 |

| LUT as Memory | 667 | 0 | 17,400 | 4.00 |

| LUT as Distributed RAM | 171 | 0 | ||

| LUT as Shift Register | 496 | 0 | ||

| Slice Registers | 28,536 | 0 | 106,400 | 27.00 |

| Register as Flip Flop | 28,536 | 0 | 106,400 | 27.00 |

| Register as Latch | 0 | 0 | 106,400 | 0.00 |

| F7 Muxes | 2480 | 0 | 26,600 | 9.00 |

| F8 Muxes | 920 | 0 | 13,300 | 7.00 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liao, X.; Guo, J.; Luo, Z.; Xu, Y.; Chu, Y. Research and Implementation of High-Efficiency and Low-Complexity LDPC Coding Algorithm. Electronics 2023, 12, 3696. https://doi.org/10.3390/electronics12173696

Liao X, Guo J, Luo Z, Xu Y, Chu Y. Research and Implementation of High-Efficiency and Low-Complexity LDPC Coding Algorithm. Electronics. 2023; 12(17):3696. https://doi.org/10.3390/electronics12173696

Chicago/Turabian StyleLiao, Xiong, Junxiong Guo, Zhenghua Luo, Yanghui Xu, and Yingjun Chu. 2023. "Research and Implementation of High-Efficiency and Low-Complexity LDPC Coding Algorithm" Electronics 12, no. 17: 3696. https://doi.org/10.3390/electronics12173696

APA StyleLiao, X., Guo, J., Luo, Z., Xu, Y., & Chu, Y. (2023). Research and Implementation of High-Efficiency and Low-Complexity LDPC Coding Algorithm. Electronics, 12(17), 3696. https://doi.org/10.3390/electronics12173696