Throughput/Area-Efficient Accelerator of Elliptic Curve Point Multiplication over GF(2233) on FPGA

Abstract

:1. Introduction

1.1. Related ECPM Hardware Accelerators and Limitations

1.2. Our Objective and Contributions

- We developed a throughput/area-efficient hardware accelerator architecture over with for ECPM computation.

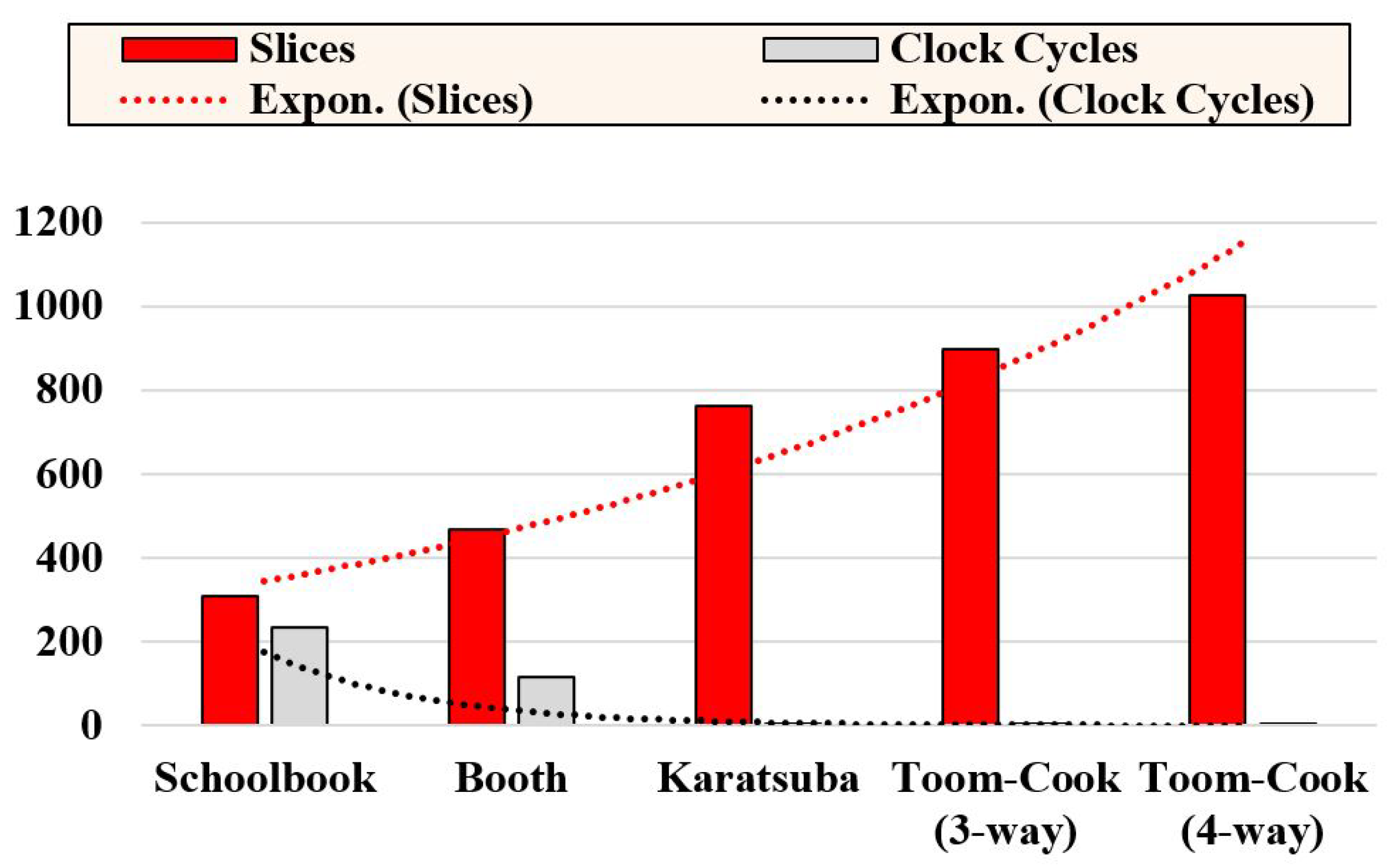

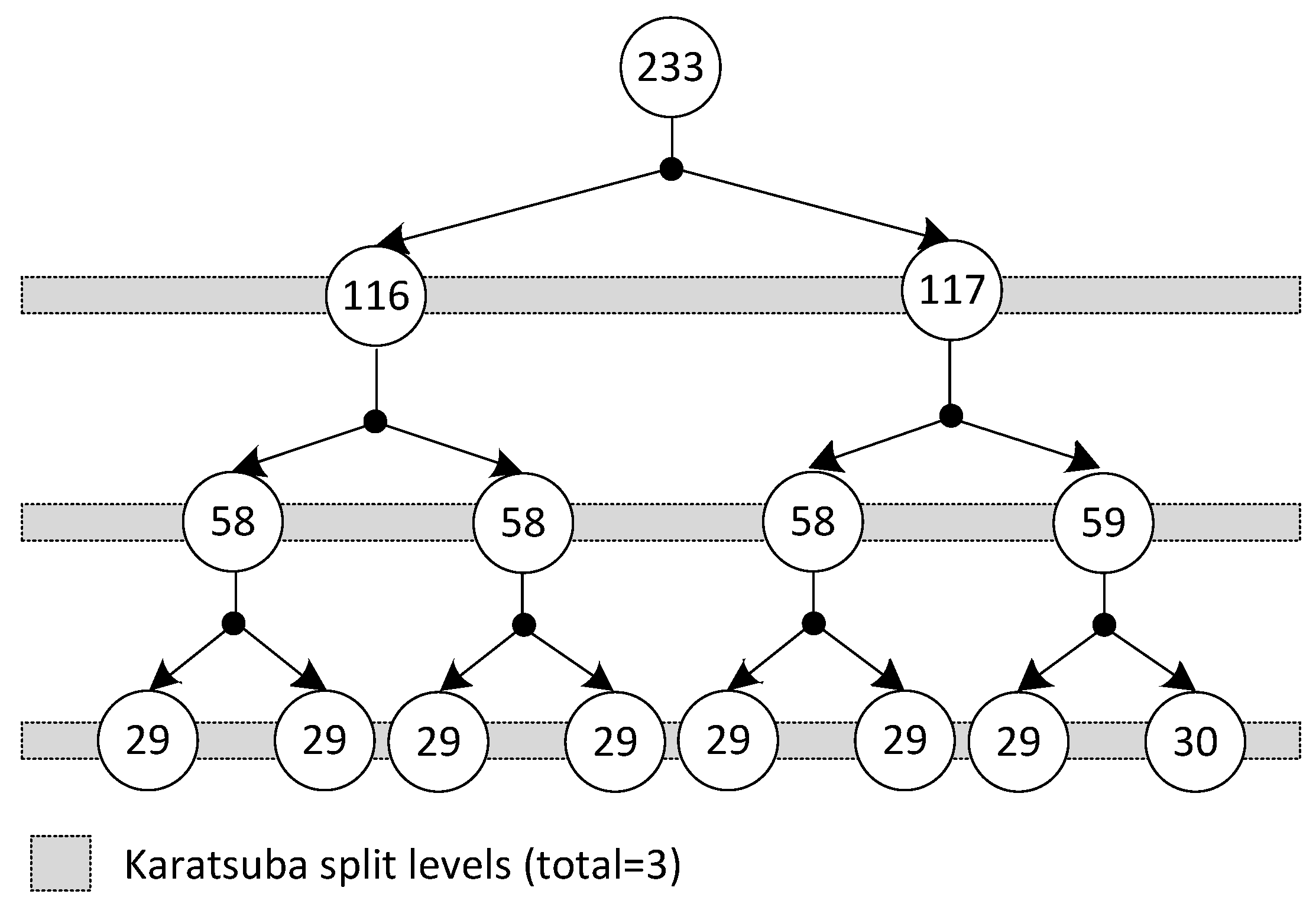

- The throughput of the proposed accelerator architecture was optimized by reducing the total clock cycles. The clock cycles were optimized by implementing a bit-parallel Karatsuba modular multiplier.

- To optimize the area, instead of multiple modular operators, we incorporated a single modular adder, multiplier, and square block in the arithmetic unit of the proposed accelerator architecture. Moreover, we implemented an Itoh–Tsujii inversion algorithm [31] using the existing hardware resources of the Karatsuba multiplier and square units for the multiplicative inverse computations of ECC. These (two) strategies effectively minimized hardware resource utilization.

- A dedicated finite-state-machine (FSM) was implemented for control functionalities.

- A figure-of-merit (FoM) was defined in terms of throughput/area to provide a realistic comparison to state-of-the-art methods.

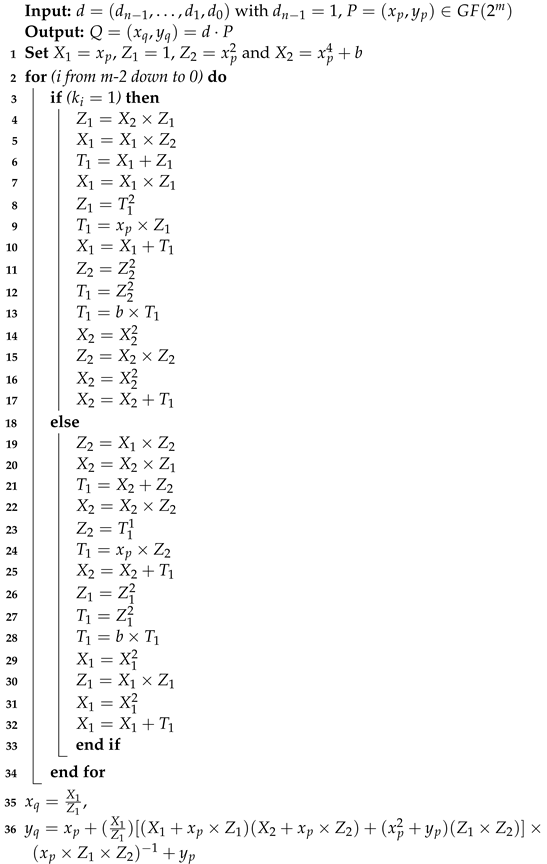

2. ECPM Algorithm over

| Algorithm 1: Montgomery PM algorithm [6]. |

|

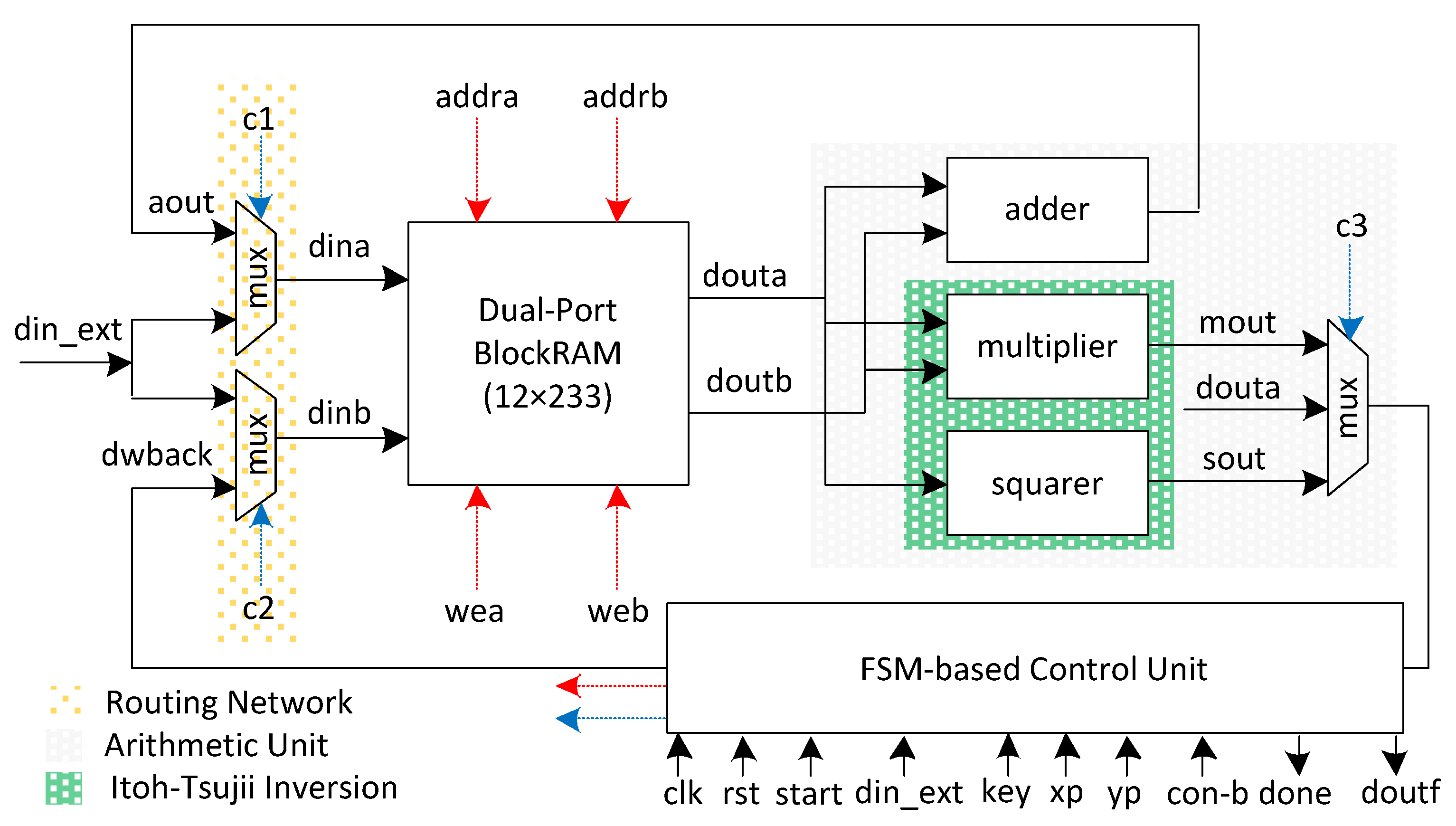

3. Proposed ECPM Hardware Architecture

3.1. Memory Unit

3.2. Routing Network

3.3. Arithmetic Unit

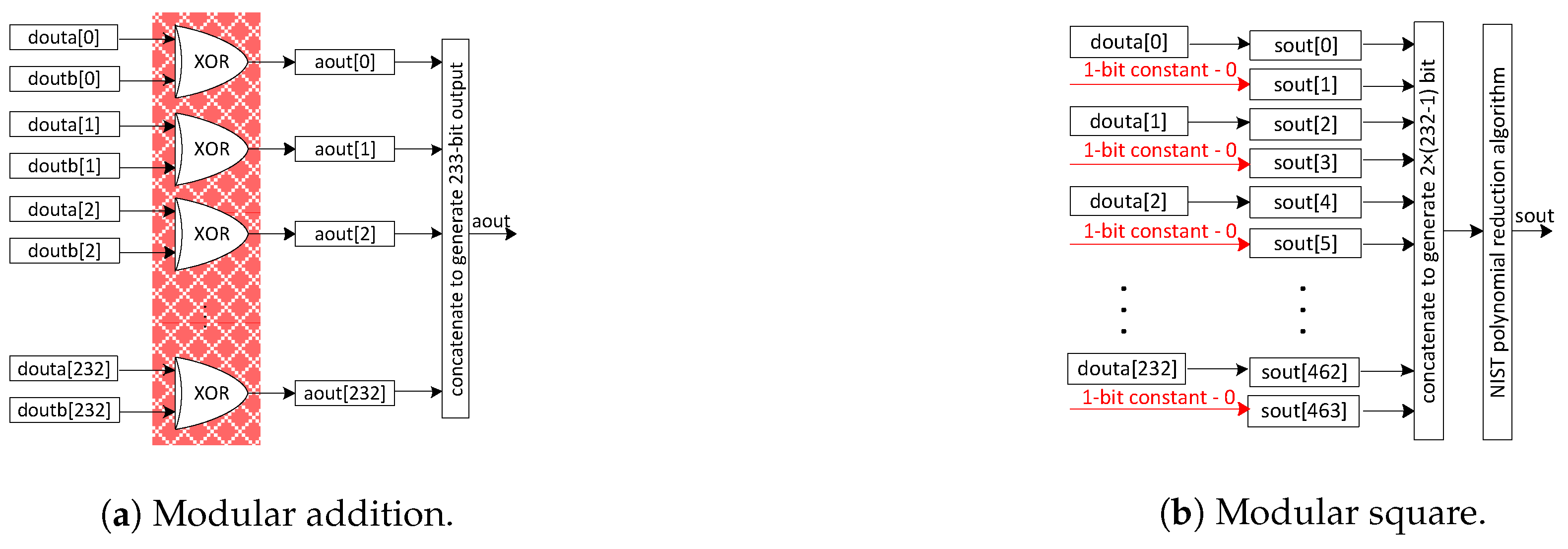

3.3.1. Adder and Square Units

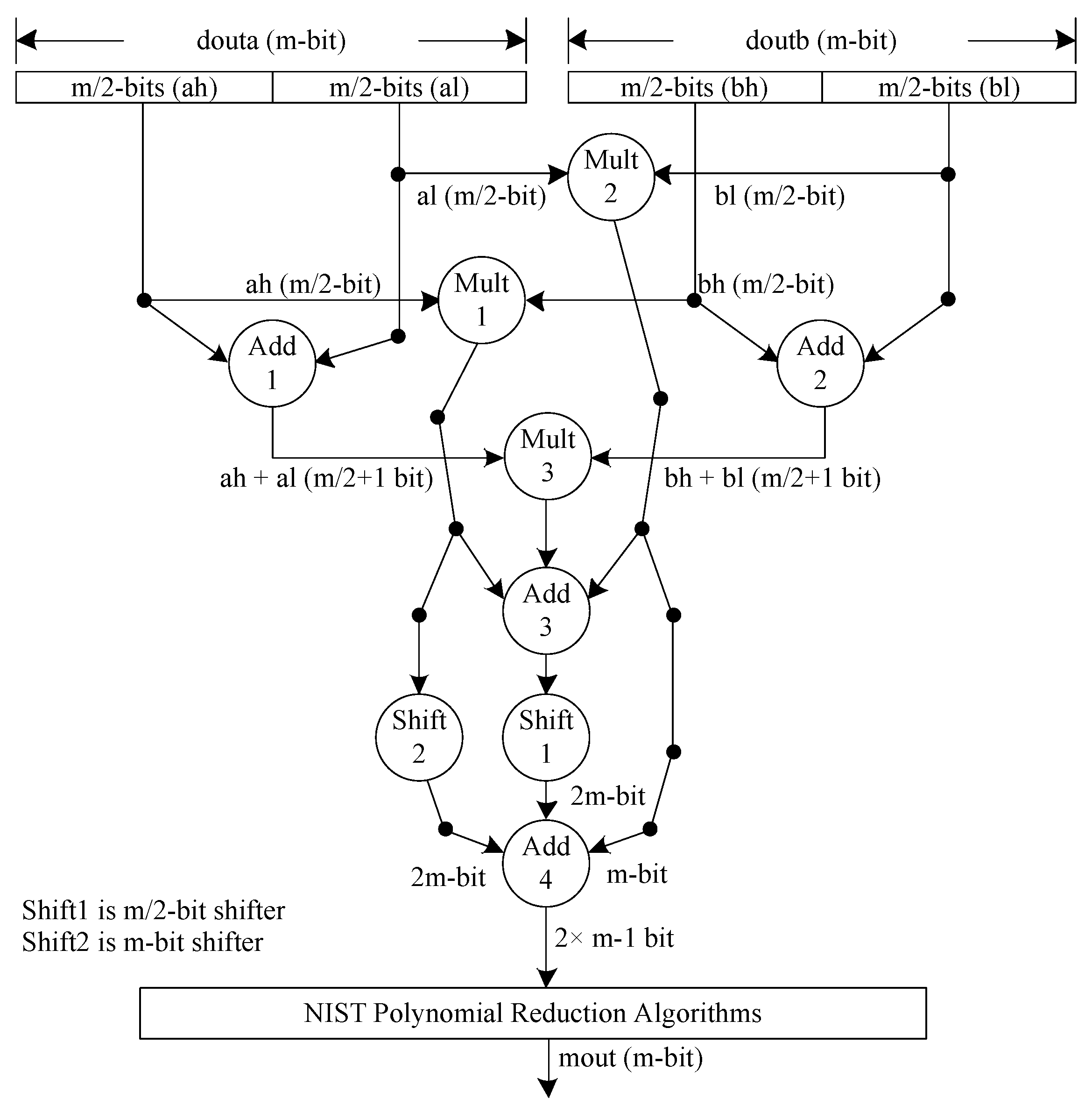

3.3.2. Multiplier Unit

3.3.3. Polynomial Reduction

3.3.4. Modular Inversion

3.4. Control Unit and Clock Cycles’ Calculation

- Affine to projective conversions: The state 0 of the implemented CU is idle, which indicates do not act. The CU generates the control signals for implementing affine to the projective conversion of Algorithm 1 during states 1 to 6. Each state needs one clock cycle for computation; hence, six cycles are needed to implement the affine to projective conversion.

- Point multiplication computation: As shown in Algorithm 1, the ECPM computation in projective coordinates requires 28 instructions: 14 for and 14 for portions. Therefore, to implement these 28 instructions depending on the value of , 29 cycles are required. Out of these 29 cycles, 28 are for implementing 28 instructions of the PA and PD operations of Algorithm 1, while 1 additional clock cycle is necessary to check the value of the and m, where m is a counter that counts the number of points on the specified ECC curve. For with , the value of m increases to 0 when the initial value is . Thus, the PM in projective coordinate takes clock cycles for computation, where m is 233.

- Projective to affine conversion: The projective to affine conversion of the Montgomery ECPM algorithm involves two finite field inversion () computations, as shown in Algorithm 1. We used a single-bit ‘’ signal to monitor these inversion operations. Initially, the ‘’ signal is zero. It remains zero until the completion of the first inversion computation. In the last state of the inversion operation, FSM checks the value of ‘’ signal: if it is 1, the FSM starts generating the control signals for the remaining instructions; otherwise, the FSM sets the ‘’ signal to 1 and starts provoking the control signals to compute the second associated inversion operation. Subsequently, one inversion takes square operations, 10 modular multiplication operations, and utilizes overall clock cycles. Similarly, cycles are needed for two inversion computations. In addition to inversion operations, an additional 18 clock cycles are required to complete the remaining projective to affine conversion instructions of Algorithm 1.

4. Results and Comparison

4.1. Results

4.2. Comparisons

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Simsim, M.T. Internet usage and user preferences in Saudi Arabia. J. King Saud Univ.—Eng. Sci. 2011, 23, 101–107. [Google Scholar] [CrossRef]

- Rashid, M.; Imran, M.; Jafri, A.R.; Al-Somani, T.F. Flexible Architectures for Cryptographic Algorithms—A Systematic Literature Review. J. Circuits Syst. Comput. 2019, 28, 1930003. [Google Scholar] [CrossRef]

- Hankerson, D.; Menezes, A.J.; Vanstone, S. Guide to Elliptic Curve Cryptography. 2004; pp. 1–311. Available online: https://link.springer.com/book/10.1007/b97644 (accessed on 27 June 2023).

- Rivest, R.L.; Shamir, A.; Adleman, L. A method for obtaining digital signatures and public-key cryptosystems. Commun. ACM 1978, 21, 120–126. [Google Scholar]

- Miller, V.S. Use of Elliptic Curves in Cryptography. In Advances in Cryptology—CRYPTO ’85 Proceedings; Williams, H.C., Ed.; Springer: Berlin/Heidelberg, Germany, 1986; pp. 417–426. [Google Scholar]

- Imran, M.; Rashid, M.; Jafri, A.R.; Kashif, M. Throughput/area optimised pipelined architecture for elliptic curve crypto processor. IET Comput. Digit. Tech. 2019, 13, 361–368. [Google Scholar] [CrossRef]

- Rashid, M.; Sonbul, O.S.; Arif, M.; Qureshi, F.A.; Alotaibi, S.S.; Sinky, M.H. A Flexible Architecture for Cryptographic Applications: ECC and PRESENT. Comput. Mater. Contin. 2023, 76, 1009–1025. [Google Scholar] [CrossRef]

- Rashid, M.; Sonbul, O.S.; Zia, M.Y.I.; Kafi, N.; Sinky, M.H.; Arif, M. Large Field-Size Elliptic Curve Processor for Area-Constrained Applications. Appl. Sci. 2023, 13, 1240. [Google Scholar] [CrossRef]

- Arif, M.; Sonbul, O.S.; Rashid, M.; Murad, M.; Sinky, M.H. A Unified Point Multiplication Architecture of Weierstrass, Edward and Huff Elliptic Curves on FPGA. Appl. Sci. 2023, 13, 4194. [Google Scholar] [CrossRef]

- He, Z.; Chen, X. Design and implementation of high-speed configurable ECC co-processor. In Proceedings of the 2017 IEEE 12th International Conference on ASIC (ASICON), Guiyang, China, 25–28 October 2017; pp. 734–737. [Google Scholar] [CrossRef]

- Matutino, P.M.; Araújo, J.; Sousa, L.; Chaves, R. Pipelined FPGA coprocessor for elliptic curve cryptography based on residue number system. In Proceedings of the 2017 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS), Pythagorion, Greece, 17–20 July 2017; pp. 261–268. [Google Scholar] [CrossRef]

- Kashif, M.; Cicek, I.; Imran, M. A Hardware Efficient Elliptic Curve Accelerator for FPGA Based Cryptographic Applications. In Proceedings of the 2019 11th International Conference on Electrical and Electronics Engineering (ELECO), Bursa, Turkey, 28–30 November 2019; pp. 362–366. [Google Scholar] [CrossRef]

- Zeghid, M.; Ahmed, H.Y.; Chehri, A.; Sghaier, A. Speed/Area-Efficient ECC Processor Implementation Over GF(2m) on FPGA via Novel Algorithm-Architecture Co-Design. IEEE Trans. Very Large Scale Integr. Syst. 2023, 31, 1192–1203. [Google Scholar] [CrossRef]

- Khan, Z.U.A.; Benaissa, M. Throughput/Area-efficient ECC Processor Using Montgomery Point Multiplication on FPGA. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 1078–1082. [Google Scholar] [CrossRef]

- Nadikuda, P.K.G.; Boppana, L. An area-time efficient point-multiplication architecture for ECC over GF(2m) using polynomial basis. Microprocess. Microsyst. 2022, 91, 104525. [Google Scholar] [CrossRef]

- Imran, M.; Pagliarini, S.; Rashid, M. An Area Aware Accelerator for Elliptic Curve Point Multiplication. In Proceedings of the 2020 27th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Scotland, UK, 23–25 November 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Wang, D.; Lin, Y.; Hu, J.; Zhang, C.; Zhong, Q. FPGA Implementation for Elliptic Curve Cryptography Algorithm and Circuit with High Efficiency and Low Delay for IoT Applications. Micromachines 2023, 14, 1037. [Google Scholar] [CrossRef]

- Rashid, M.; Imran, M.; Kashif, M.; Sajid, A. An Optimized Architecture for Binary Huff Curves with Improved Security. IEEE Access 2021, 9, 88498–88511. [Google Scholar] [CrossRef]

- Jafri, A.R.; Ul Islam, M.N.; Imran, M.; Rashid, M. Towards an optimized architecture for unified binary huff curves. J. Circuits Syst. Comput. 2017, 26, 1750178. [Google Scholar] [CrossRef]

- Bedoui, M.; Bouallegue, B.; Ahmed, A.M.; Hamdi, B.; Machhout, M.; Mahmoud; Khattab, M. A secure hardware implementation for elliptic curve digital signature algorithm. Comput. Syst. Sci. Eng. 2023, 44, 2177–2193. [Google Scholar] [CrossRef]

- Trujillo-Olaya, V.; Velasco-Medina, J. Hardware implementation of elliptic curve digital signature algorithm over GF(2409) using sha-3. Int. J. Mach. Learn. Comput. 2022, 12, 73–78. [Google Scholar] [CrossRef]

- Khan, S.Z.; Jamal, S.S.; Sajid, A.; Rashid, M. FPGA implementation of elliptic-curve diffie hellman protocol. Comput. Mater. Contin. 2022, 73, 1879–1894. [Google Scholar] [CrossRef]

- FIPS. Digital Signature Standard—Publication 186-5 (Supersedes FIPS 186-4). 2023. Available online: https://doi.org/10.6028/NIST.FIPS.186-5 (accessed on 29 June 2023).

- Barker, E.; Chen, L.; Roginsky, A.; Smid, M. Recommendation for Pair-Wise Key Establishment Schemes Using Discrete Logarithm Cryptography. 2023. NIST Special Publication 800-56A (Revision 2). Available online: http://dx.doi.org/10.6028/NIST.SP.800-56Ar2 (accessed on 16 June 2023).

- Singh, A.; Gutub, A.; Nayyar, A.; Khan, M.K. Redefining food safety traceability system through blockchain: Findings, challenges and open issues. Multimed. Tools Appl. 2023, 82, 21243–21277. [Google Scholar] [CrossRef]

- Almotairi, K.H. Application of internet of things in healthcare domain. J. Umm Al-Qura Univ. Eng. Archit. 2023, 14, 1–12. [Google Scholar] [CrossRef]

- Khan, F.; Jan, M.A.; Alturki, R.; Alshehri, M.D.; Shah, S.T.; Rehman, A.U. A Secure Ensemble Learning-Based Fog-Cloud Approach for Cyberattack Detection in IoMT. IEEE Trans. Ind. Inform. 2023, 19, 10125–10132. [Google Scholar] [CrossRef]

- Khan, Z.U.A.; Benaissa, M. High-Speed and Low-Latency ECC Processor Implementation Over GF( 2m) on FPGA. IEEE Trans. Very Large Scale Integr. Syst. 2017, 25, 165–176. [Google Scholar] [CrossRef]

- Al-Khaleel, O.; Papachristou, C.; Wolff, F.; Pekmestzi, K. An Elliptic Curve Cryptosystem Design Based on FPGA Pipeline Folding. In Proceedings of the 13th IEEE International On-Line Testing Symposium (IOLTS 2007), Crete, Greece, 8–11 July 2007; pp. 71–78. [Google Scholar] [CrossRef]

- Lai, J.Y.; Hung, T.Y.; Yang, K.H.; Huang, C.T. High-performance architecture for Elliptic Curve Cryptography over binary field. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010; pp. 3933–3936. [Google Scholar] [CrossRef]

- Itoh, T.; Tsujii, S. A fast algorithm for computing multiplicative inverses in GF(2m) using normal bases. Inf. Comput. 1988, 78, 171–177. [Google Scholar] [CrossRef]

- Imran, M.; Rashid, M. Architectural review of polynomial bases finite field multipliers over GF(2m). In Proceedings of the 2017 International Conference on Communication, Computing and Digital Systems (C-CODE), Islamabad, Pakistan, 8–9 March 2017; pp. 331–336. [Google Scholar] [CrossRef]

- Kang, B.; Cho, H. FlexKA: A Flexible Karatsuba Multiplier Hardware Architecture for Variable-Sized Large Integers. IEEE Access 2023, 11, 55212–55222. [Google Scholar] [CrossRef]

- Kalaiarasi, M.; Venkatasubramani, V.R.; Rajaram, S. A Parallel Quad Itoh-Tsujii Multiplicative Inversion Algorithm for FPGA Platforms. In Proceedings of the 2020 Third ISEA Conference on Security and Privacy (ISEA-ISAP), Guwahati, India, 27 February–1 March 2020; pp. 31–35. [Google Scholar] [CrossRef]

- Kalaiarasi, M.; Venkatasubramani, V.; Manikandan, M.; Rajaram, S. High performance HITA based Binary Edward Curve Crypto processor for FPGA platforms. J. Parallel Distrib. Comput. 2023, 178, 56–68. [Google Scholar] [CrossRef]

- NIST. Recommended Elliptic Curves for Federal Government Use (1999). Available online: https://csrc.nist.gov/csrc/media/publications/fips/186/2/archive/2000-01-27/documents/fips186-2.pdf (accessed on 22 May 2023).

- Imran, M.; Abideen, Z.U.; Pagliarini, S. A Versatile and Flexible Multiplier Generator for Large Integer Polynomials. J. Hardw. Syst. Secur. 2023. [Google Scholar] [CrossRef]

| Target Device | Power (W) | Area Utilizations | Timing-Related Results | Thrpt (Kbps) | FoM | ||||

|---|---|---|---|---|---|---|---|---|---|

| Slices | LUTs | FFs | Tcycles | Freq (MHz) | Lat (μs) | ||||

| Virtex-6 | 0.921 | 4608 | 17057 | 2487 | 7208 | 310 | 23.25 | 43.01 | 9.33 |

| Virtex-7 | 0.813 | 3584 | 13267 | 1934 | 7208 | 350 | 20.59 | 48.56 | 13.54 |

| Ref. # | Device | Power (mW) | Area Results | Timing Results | Thrpt (Kbps) | FoM | ECC Model/m | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Slices | LUTs | FFs | Tcycles |

Freq

(MHz) |

Lat

(μs) | ||||||

| [6] | Virtex-7 | – | 5120 | 18,953 | 2764 | 5634 | 357 | 15.78 | 63.37 | 12.37 | Weierstrass/ |

| [12] | Artix-7 | – | 4001 | – | 2933 | 173,154 | 89 | 1945 | 0.51 | 0.12 | Weierstrass/ |

| [12] | Artix-7 | – | 4467 | – | 3399 | 173,154 | 143 | 1217 | 0.82 | 0.18 | Weierstrass/ |

| [15] | Virtex-5 | – | – | 14,137 | – | 1476 | 158 | 9.20 | 108.69 | 7.68 | Weierstrass/ |

| [17] | Virtex-7 | – | – | 23.1k | – | – | 105 | 80 | 12.50 | 0.53 | Weierstrass/ |

| [18] | Virtex-7 | 3481 | 7123 | – | – | 15,495 | 371 | 41.7 | 23.98 | 3.36 | BHC/ |

| Ours | Virtex-5 | 0.617 | 4943 | 17,892 | 2756 | 7208 | 317 | 22.73 | 43.99 | 8.89 | Weierstrass/ |

| Virtex-7 | 0.813 | 3584 | 13267 | 1934 | 7208 | 350 | 20.59 | 48.56 | 13.54 | Weierstrass/ | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rashid, M.; Sonbul, O.S.; Zia, M.Y.I.; Arif, M.; Sajid, A.; Alotaibi, S.S. Throughput/Area-Efficient Accelerator of Elliptic Curve Point Multiplication over GF(2233) on FPGA. Electronics 2023, 12, 3611. https://doi.org/10.3390/electronics12173611

Rashid M, Sonbul OS, Zia MYI, Arif M, Sajid A, Alotaibi SS. Throughput/Area-Efficient Accelerator of Elliptic Curve Point Multiplication over GF(2233) on FPGA. Electronics. 2023; 12(17):3611. https://doi.org/10.3390/electronics12173611

Chicago/Turabian StyleRashid, Muhammad, Omar S. Sonbul, Muhammad Yousuf Irfan Zia, Muhammad Arif, Asher Sajid, and Saud S. Alotaibi. 2023. "Throughput/Area-Efficient Accelerator of Elliptic Curve Point Multiplication over GF(2233) on FPGA" Electronics 12, no. 17: 3611. https://doi.org/10.3390/electronics12173611

APA StyleRashid, M., Sonbul, O. S., Zia, M. Y. I., Arif, M., Sajid, A., & Alotaibi, S. S. (2023). Throughput/Area-Efficient Accelerator of Elliptic Curve Point Multiplication over GF(2233) on FPGA. Electronics, 12(17), 3611. https://doi.org/10.3390/electronics12173611