White Rabbit Expansion Board: Design, Architecture, and Signal Integrity Simulations

Abstract

1. Introduction

2. White Rabbit Protocol

3. Architecture of the Expansion Board

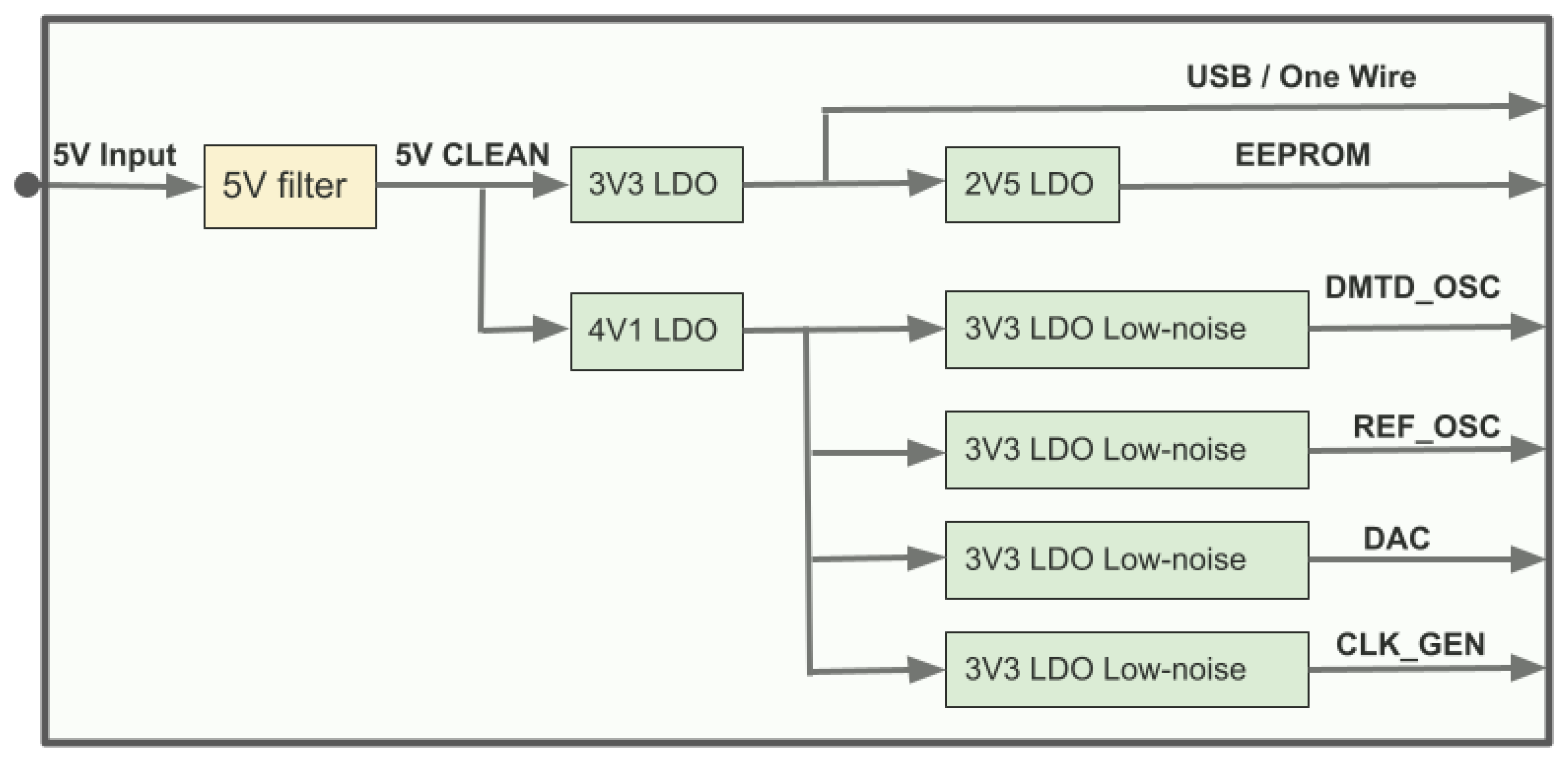

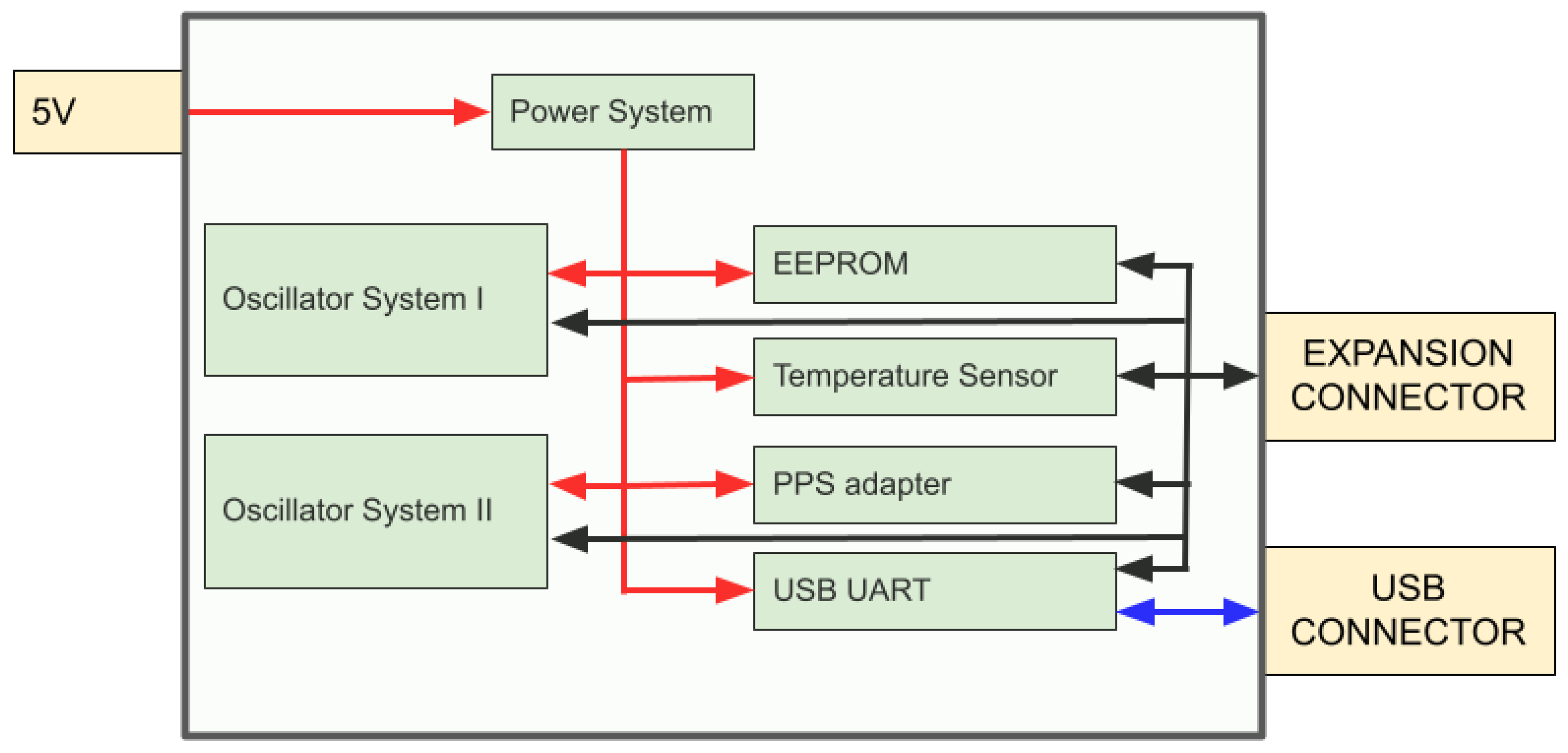

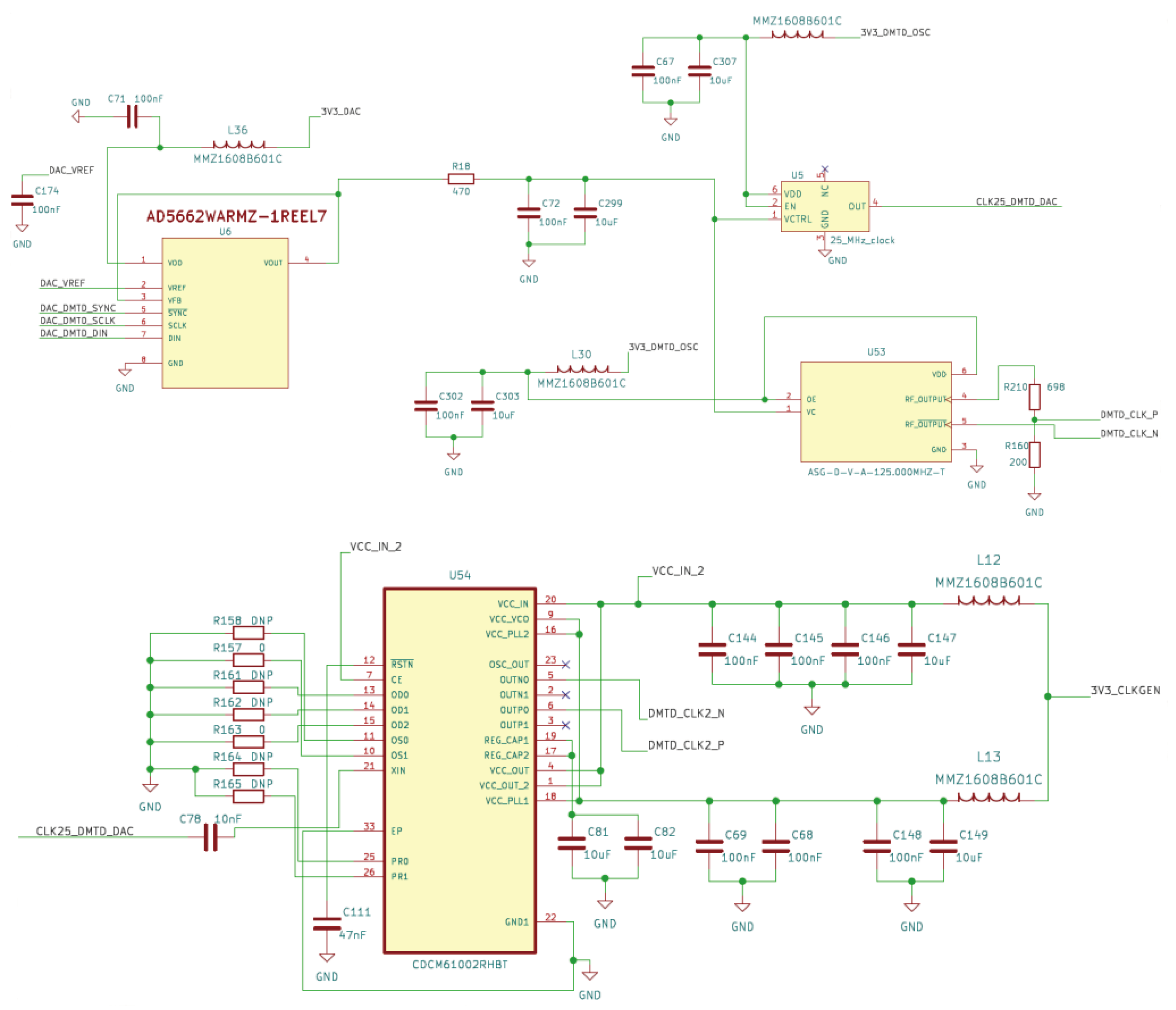

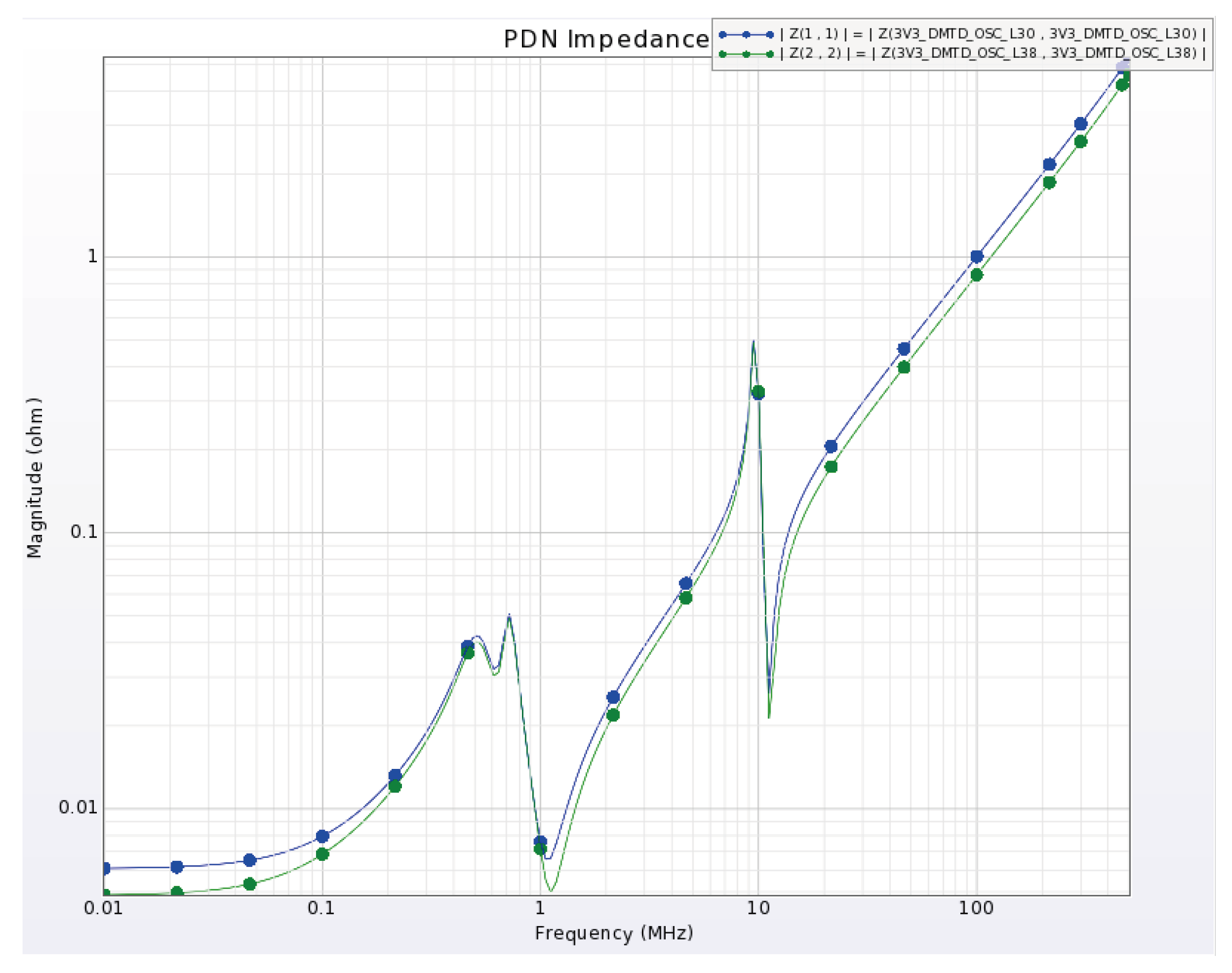

- The power supply subsystem: This subsystem generates all the internal voltages needed. The expansion board is supplied at 5 V. The 5 V is cleaned from high-frequency noise by means of a ferrite bead and supplies the linear regulators where the power rail needed is generated. A 3.3 V voltage is generated, which is used for supplying a USB UART. The 3.3 V output feeds a linear and low-dropout (LDO) where the 2.5 V rail to supply the EEPROM is generated. In addition, the cleaned 5 V feeds another LDO to generate a 4.1 V rail, which is used, in turn, to supply four low-noise LDOs to generate the 3.3 V needed by the oscillator systems. The architecture of the power supply is shown in Figure 3. The low noise 3.3 V outputs are used as a reference by the oscillators, to supply the digital-to-analog converter (DAC), and to supply the secondary clock system. Each of the previous functions is achieved by means of independent rails.

- One-wire temperature sensor, the medium access controller address provider: A one-wire [30] temperature sensor is included in the board. In addition, to provide temperature measurement, the identification number of this sensor is used to generate a unique medium access controller (MAC) [31] address for the protocol. The sensor is accessed with a one-wire interface.

- Electrically erasable programmable read-only memory: An EEPROM allows for the storage of several configuration parameters of the protocol. It can be accessed via an I2C interface and can store the device’s configuration data, such as the MAC address.

- Pulse-per-second adapter: An adapter of the PPS signal generated by the WR PTP Core is included in the expansion board. The PPS signal is an input of the expansion board, which adapts the signal for a SMA connector.

- USB UART: A USB UART with a mini-USB connector has been included to provide access to the WR FPGA through the expansion board. This USB UART is particularly useful for outputting debug messages from the WRPC. The FPGA implementation of a regular UART is relatively simple and it can be connected to any modern computer through the bridge.

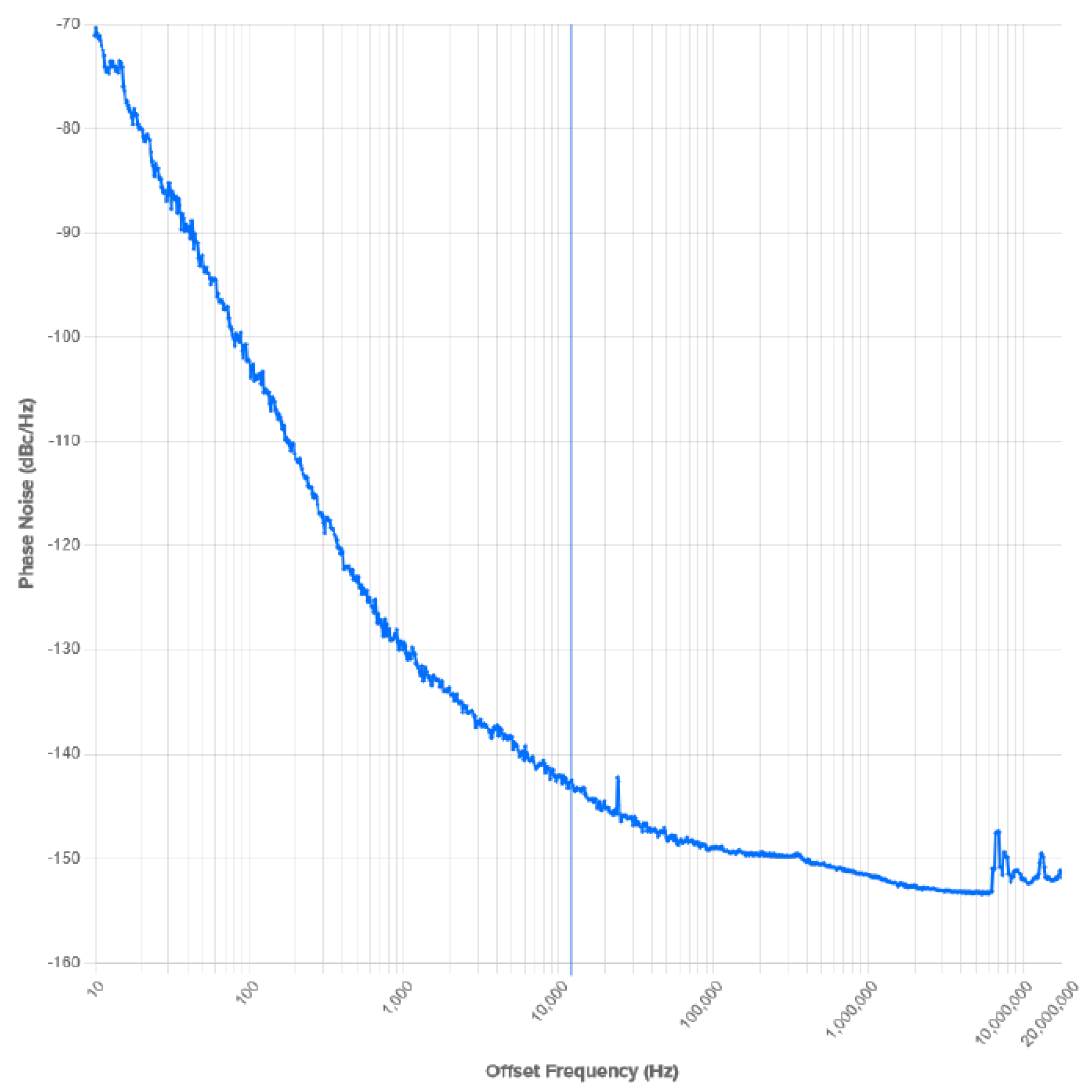

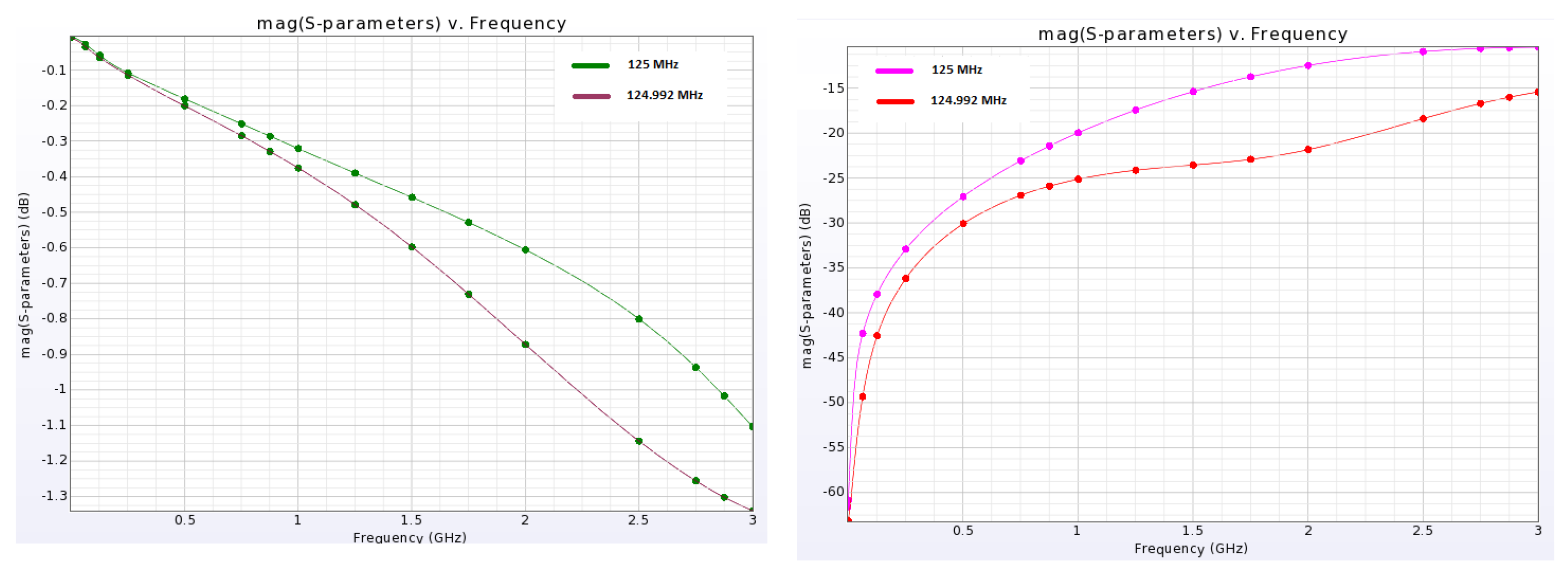

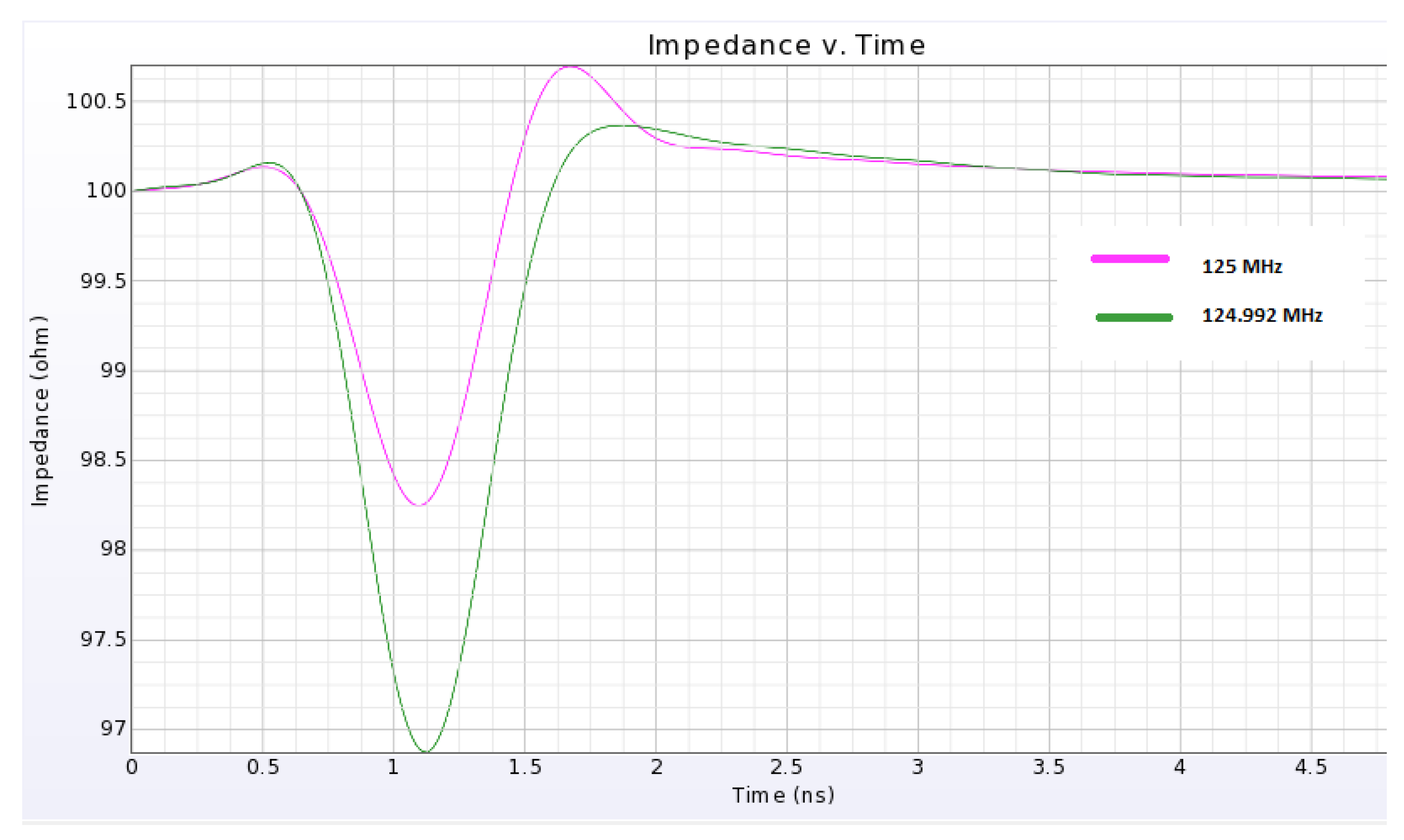

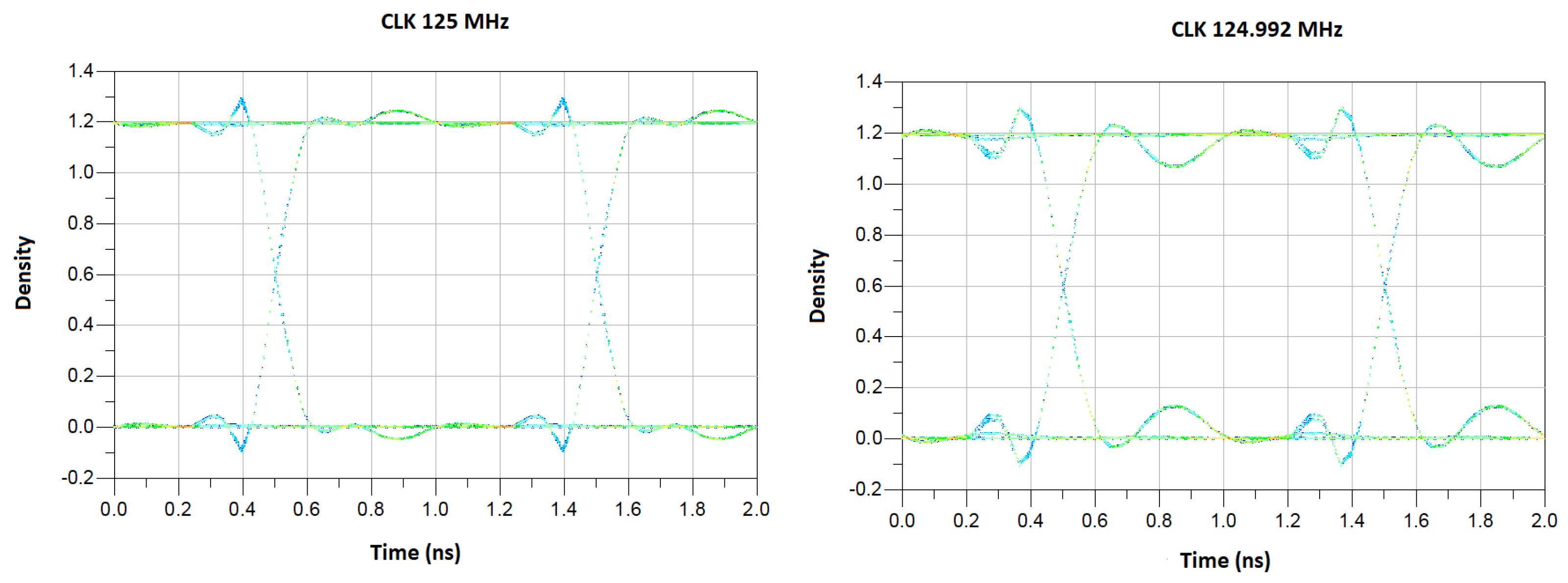

- Oscillator subsystems: These two subsystems generate the clock needed by the WRPC DDMTD running at the FPGA for a precise measurement of the phase. The frequencies generated are 125 MHz and 124.992 MHz.

3.1. Oscillator Subsystems

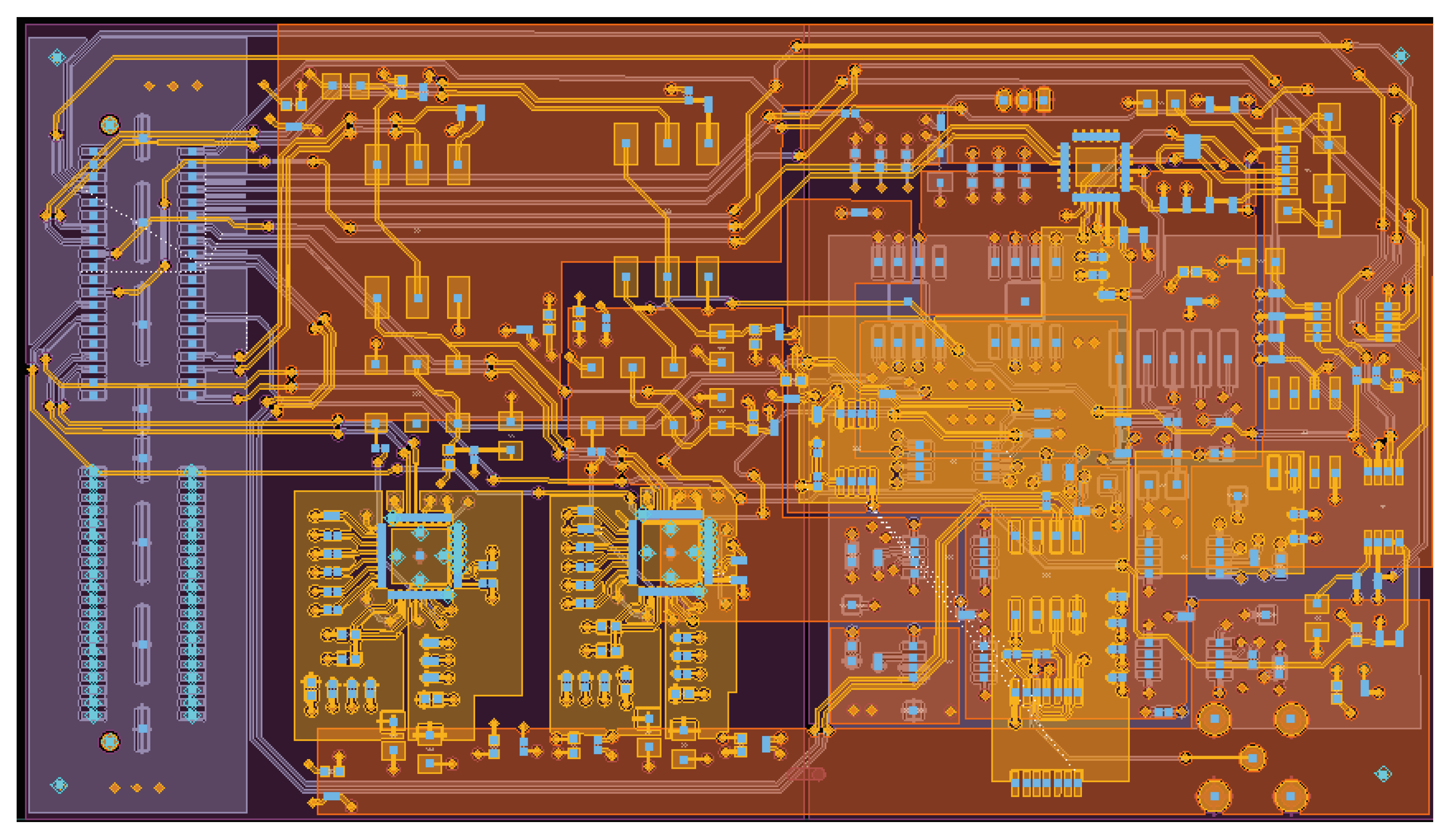

3.2. Printed Circuit Board Layout

4. Power and Signal Integrity Analysis

4.1. Previous Developments and Justification of Virtual Prototyping

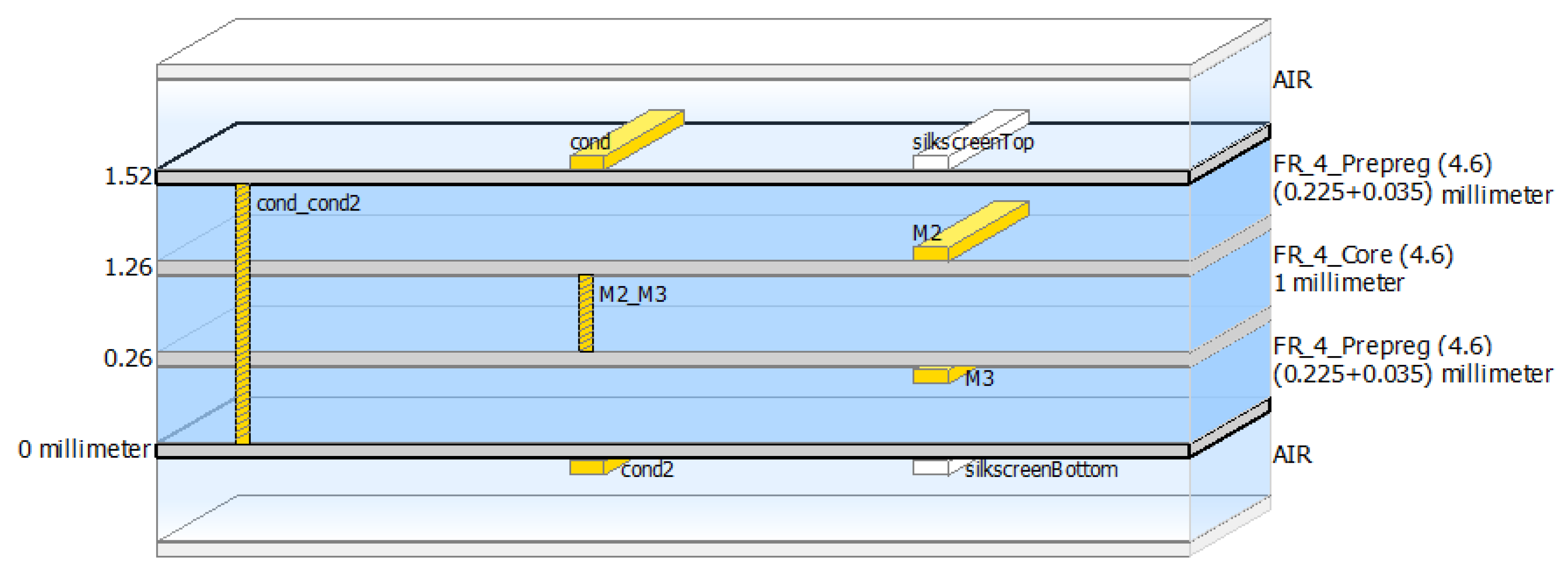

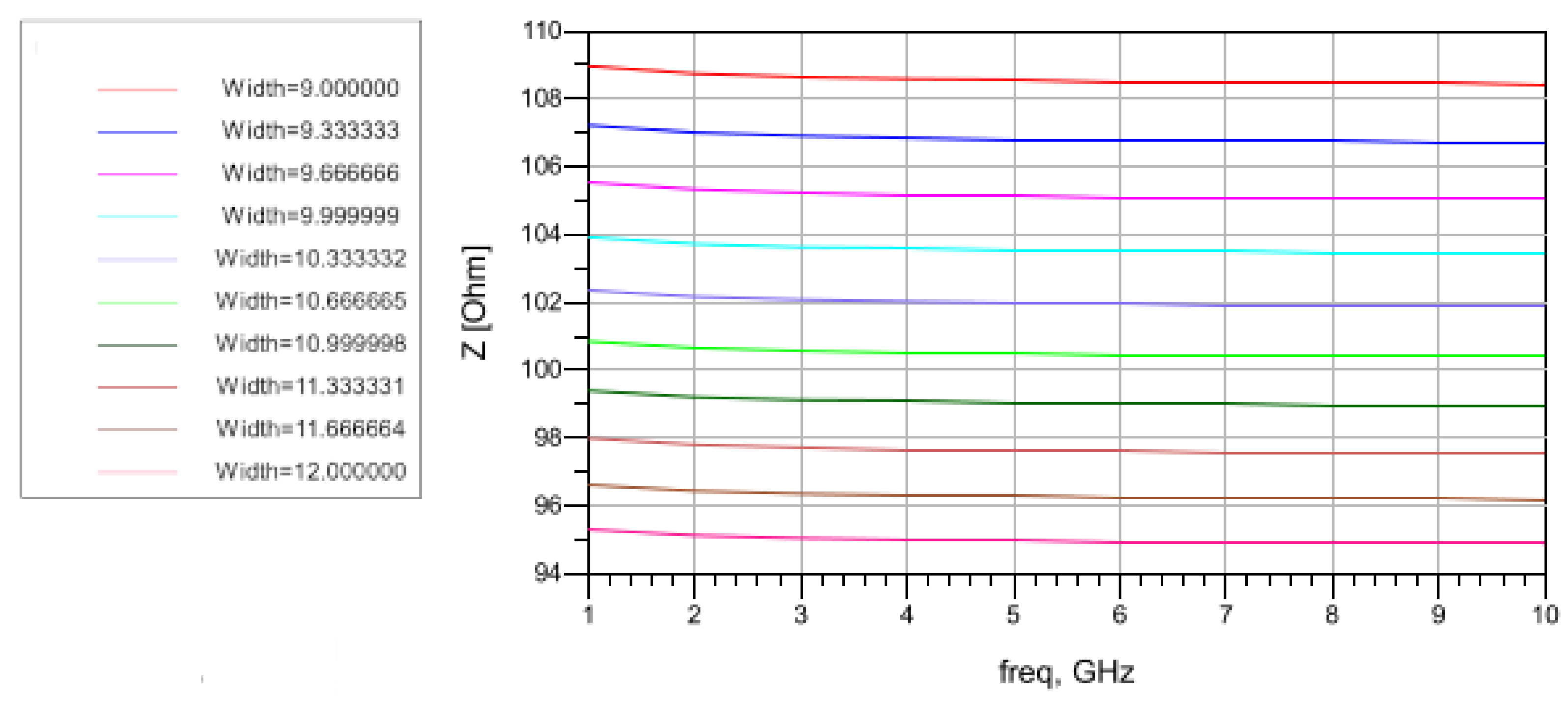

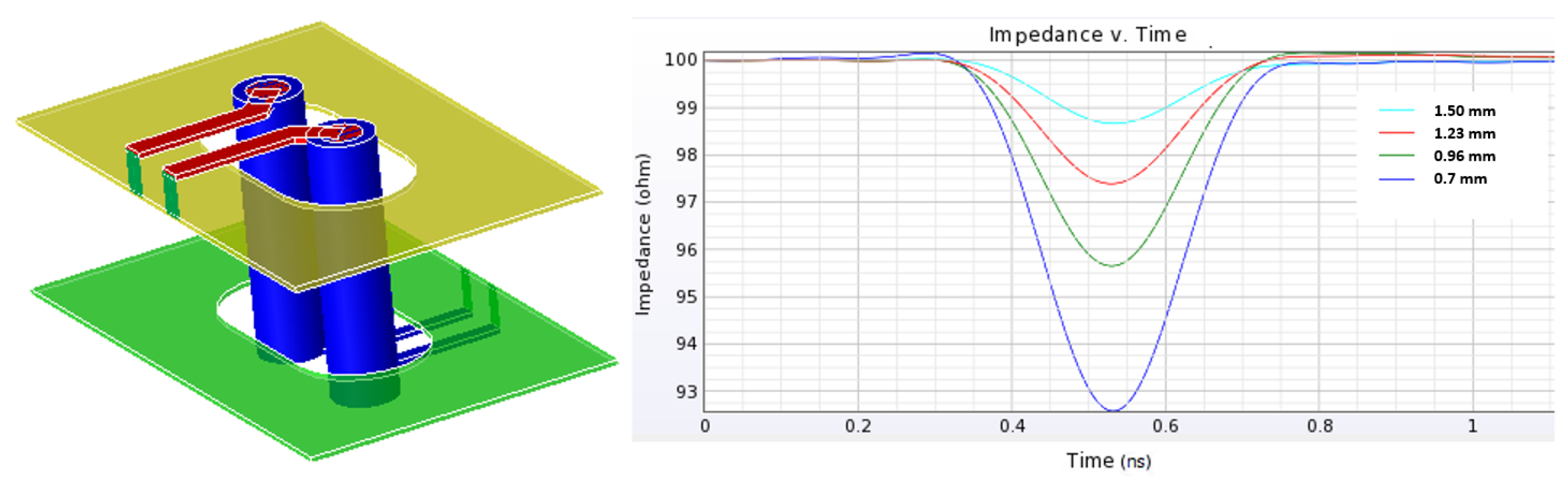

4.2. Pre-layout Signal Integrity Simulations

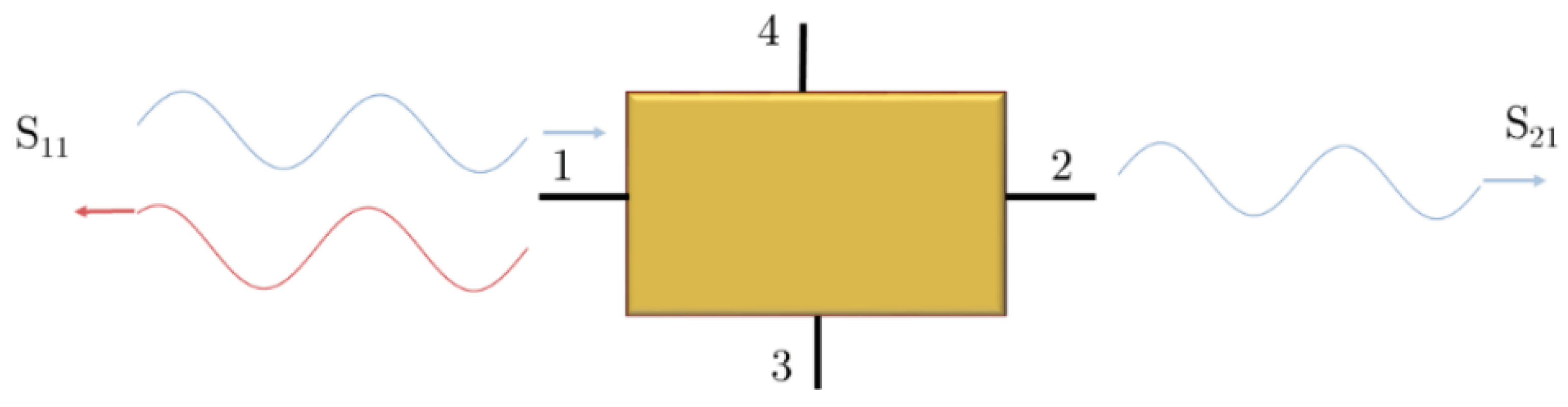

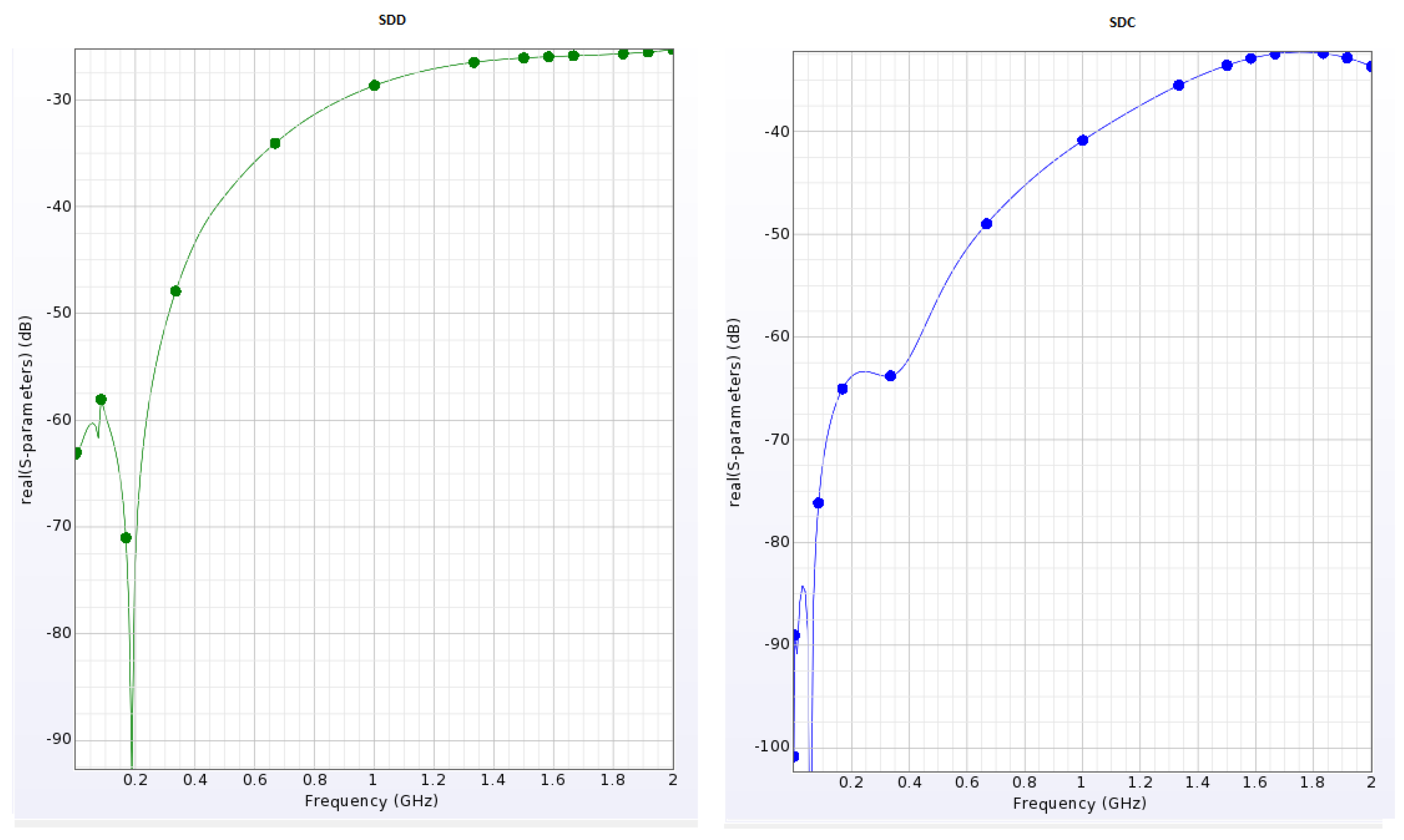

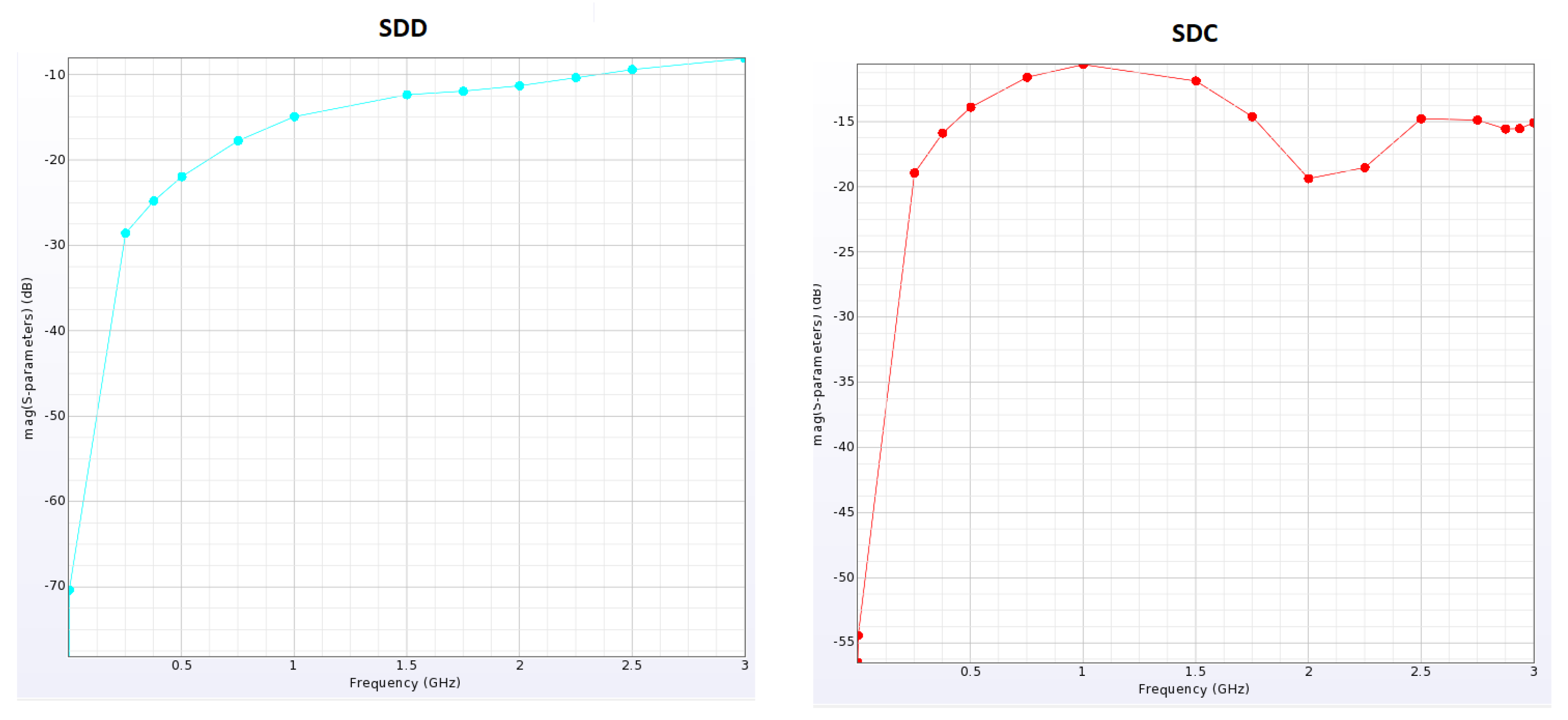

4.3. Post-layout Power and Signal Integrity Simulations

- Inter symbol interference (ISI), produced by the interference of one bit with the next or due to reflections.

- Duty cycle distortion (DCD), produced by alterations in the symmetry of the rising and falling edges, generating a distortion figure with two peaks.

- Periodic jitter (PJ), generated by coupling, noise on power rails, noise on substrates, or instabilities in feedback loops.

5. Conclusions and Future Work

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- IEEE Std 1588-2019; Synchronization Distribution in 5G Transport Networks. (Revision of IEEE Std 1588-2008). IEEE: Manhattan, NY, USA, 2022.

- Venmani, D.; Lagadec, Y.; Lemoult, O.; Deletre, F. Phase and Time Synchronization for 5G C-RAN: Requirements, Design Challenges and Recent Advances in Standardization. EAI Endorsed Trans. Ind. Netw. Intell. Syst. 2018, 5, 155238. [Google Scholar] [CrossRef]

- Li, H.; Han, L.; Duan, R.; Garner, G.M. Analysis of the Synchronization Requirements of 5 g and Corresponding Solutions. IEEE Commun. Stand. Mag. 2017, 1, 52–58. [Google Scholar] [CrossRef]

- Geng, Y.; Liu, S.; Yin, Z.; Naik, A.; Prabhakar, B.; Rosenblum, M.; Vahdat, A. Exploiting a Natural Network Effect for Scalable, Fine-grained Clock Synchronization. In Proceedings of the Symposium on Networked Systems Design and Implementation, Renton, WA, USA, 9–11 April 2018. [Google Scholar]

- Ageron, M.; Aguilar, J.A.; Al Samarai, I.; Albert, A.; Ameli, F.; André, M.; Anghinolfi, M.; Anton, G.; Anvar, S.; Ardid, M.; et al. ANTARES: The first undersea neutrino telescope. Nucl. Instrum. Meth. A 2011, 656, 11–38. [Google Scholar] [CrossRef]

- Adrian-Martinez, S.; Ageron, M.; Aharonian, F.; Aiello, S.; Albert, A.; Ameli, F.; Anassontzis, E.; Andre, M.; Androulakis, G.; Anghinolfi, M.; et al. Letter of intent for KM3NeT 2.0. J. Phys. G 2016, 43, 084001. [Google Scholar] [CrossRef]

- Aartsen, M.G.; Ackermann, M.; Adams, J.; Aguilar, J.A.; Ahlers, M.; Ahrens, M.; Altmann, D.; Andeen, K.; Anderson, T.; Ansseau, I.; et al. The IceCube Neutrino Observatory: Instrumentation and Online Systems. J. Instrum. 2017, 12, P03012. [Google Scholar] [CrossRef]

- Andres, E.; Askebjer, P.; Barwick, S.W.; Bay, R.; Bergström, L.; Biron, A.; Booth, J.; Bouchta, A.; Carius, S.; Carlson, M.; et al. The AMANDA neutrino telescope: Principle of operation and first results. Astropart. Phys. 2000, 13, 1–20. [Google Scholar] [CrossRef]

- Malyshkin, Y. Baikal-GVD neutrino telescope: Design reference 2022. Nucl. Instrum. Meth. A 2023, 1050, 168117. [Google Scholar] [CrossRef]

- Perlin, M. Particle Physics with the Pierre Auger Observatory. SciPost Phys. Proc. 2022, 8, 130. [Google Scholar] [CrossRef]

- Terzian, Y.; Lazio, J. The Square Kilometre Array. Proc. SPIE Int. Soc. Opt. Eng. 2006, 6267, 62672D. [Google Scholar] [CrossRef][Green Version]

- Ferrini, F.; Wild, W. The Cherenkov Telescope Array Observatory Comes of Age. ESO Messenger 2020, 180, 3–8. [Google Scholar] [CrossRef]

- Lipinski, M.; Wlostowski, T.; Serrano, J.; Alvarez, P. White rabbit: A PTP application for robust sub-nanosecond synchronization. In Proceedings of the 2011 IEEE International Symposium on Precision Clock Synchronization for Measurement, Control and Communication, Munich, Germany, 12–16 September 2011; pp. 25–30. [Google Scholar] [CrossRef]

- White Rabbit PTP Core. Available online: https://ohwr.org/projects/wr-cores/wiki/wrpc-core (accessed on 28 February 2012).

- White Rabbit Collaboration. Available online: https://www.white-rabbit.tech/ (accessed on 28 February 2012).

- Serrano, J.; Alvarez, P.; Cattin, M.; Garcia Cota, E.; Lewis, J.; Moreira, P.; Wlostowski, T.; Gaderer, G.; Loschmidt, P.; Dedic, J.; et al. White Rabbit Project. In Proceedings of the ICALEPCS2009, Kobe, Japan, 12–16 October 2009; pp. 93–95. [Google Scholar]

- IEEE Std 1588-2008; IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems. Revision of IEEE Std 1588-2002). IEEE: Manhattan, NY, USA, 2008; pp. 1–269. [CrossRef]

- Lan, Y.K.; Chen, Y.S.; Hou, T.C.; Wu, B.L.; Chu, Y.S. Development Board Implementation and Chip Design of IEEE 1588 Clock Synchronization System Applied to Computer Networking. Electronics 2023, 12, 2166. [Google Scholar] [CrossRef]

- Timing Characteristics of Synchronous Ethernet Equipment Slave Clock: G.8262/Y.1362 International Telecommunication Union. 2010. Available online: https://www.itu.int/rec/dologin_pub.asp?lang=e&id=T-REC-G.8262-201007-S!!PDF-E&type=items (accessed on 7 August 2023).

- IEEE Std 1588-2019; IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems. (Revision ofIEEE Std 1588-2008). IEEE: Manhattan, NY, USA, 2020; pp. 1–499. [CrossRef]

- Li, F.; Liu, W.; Qi, Y.; Li, Q.; Liu, G. An Enhanced Method for Nanosecond Time Synchronization in IEEE 1588 Precision Time Protocol. Processes 2023, 11, 1328. [Google Scholar] [CrossRef]

- Bielewicz, M.; Bancer, A.; Dziedzic, A.; Grzyb, J.; Jaworska, E.; Kasprowicz, G.; Kiecana, M.; Kolasinski, P.; Kuc, M.; Kuklewski, M.; et al. Practical Implementation of an Analogue and Digital Electronics System for a Modular Cosmic Ray Detector—MCORD. Electronics 2023, 12, 1492. [Google Scholar] [CrossRef]

- Aiello, S.; Ameli, F.; Andre, M.; Androulakis, G.; Anghinolfi, M.; Anton, G.; Marinelli, A.; Anton, G.; Ardid, M.; Markou, C.; et al. KM3NeT front-end and readout electronics system: Hardware, firmware and software. J. Astron. Telesc. Instrum. Syst. 2019, 5, 046001. [Google Scholar] [CrossRef]

- Vella Wallbank, J.; Amodeo, M.; Beaumont, A.; Buzio, M.; Di Capua, V.; Grech, C.; Sammut, N.; Giloteaux, D. Development of a Real-Time Magnetic Field Measurement System for Synchrotron Control. Electronics 2021, 10, 2140. [Google Scholar] [CrossRef]

- Jones, T.; Arnold, D.; Tuffner, F.; Cummings, R.; Lee, K. Recent Advances in Precision Clock Synchronization Protocols for Power Grid Control Systems. Energies 2021, 14, 5303. [Google Scholar] [CrossRef]

- Nabwani, M.; Suleymanov, M.; Pinhasi, Y.; Yahalom, A. Real-Time Fault Location Using the Retardation Method. Electronics 2022, 11, 980. [Google Scholar] [CrossRef]

- Rifandi, R.; Assagaf, S.; Ningtyas, Y.D.W.K. An Insight about GPS; Utrecht University Summer School: Utrecht, The Netherlands, 2013. [Google Scholar] [CrossRef]

- Lee, J. Global Positioning/GPS. Int. Encycl. Hum. Geogr. 2009, 68, 548–555. [Google Scholar] [CrossRef]

- Moreira, P.; Alvarez, P.; Serrano, J.; Darwezeh, I.; Wlostowski, T. Digital dual mixer time difference for sub-nanosecond time synchronization in Ethernet. In Proceedings of the 2010 IEEE International Frequency Control Symposium, Newport Beach, CA, USA, 1–4 June 2010; pp. 449–453. [Google Scholar] [CrossRef]

- Overview of 1-Wire Technology and Its Use. Available online: https://www.analog.com/en/technical-articles/guide-to-1wire-communication.html (accessed on 28 February 2012).

- IEEE Std 802.3-2002; IEEE Standard for Information Technology-Telecommunications and Information Exchange between Systems-Local and Metropolitan Area Networks-Specific Requirements Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications. (Revision of IEEE Std 802.3, 2000 edn). IEEE: Manhattan, NY, USA, 2002; pp. 1–1550. [CrossRef]

- Thierauf, S. High-Speed Circuit Board Signal Integrity; Artech House Microwave Library, Artech House: Norwood, MA, USA, 2004. [Google Scholar]

- Chang, K.K.; nan Kuo, C.; Wu, T.L.; Chen, W.L.; Wu, R.B. Equivalent circuit of a through via in multi-layer environment. In Proceedings of the Electrical Performance of Electronic Packaging, Pittsburgh, PA, USA, 22–24 April 1992; pp. 59–61. [Google Scholar] [CrossRef]

- Siebert, K.; Gunther, H.; Frei, S.; Mickisch, W. Modeling of Frequency Dependent Losses of Transmission Lines with VHDL-AMS in Time Domain. In Proceedings of the 2009 20th International Zurich Symposium on Electromagnetic Compatibility, Zurich, Switzerland, 12–16 January 2009; pp. 313–316. [Google Scholar] [CrossRef]

- Hennig, W.; Hoover, S. White Rabbit Time Synchronization for Radiation Detector Readout Electronics. IEEE Trans. Nucl. Sci. 2020, 68, 2059–2065. [Google Scholar] [CrossRef]

- Rogers, B.M. Virtual prototyping and concurrent engineering in PCB manufacturing. IEEE Trans. Electron. Packag. Manuf. 1997, 20, 300–308. [Google Scholar] [CrossRef]

- Zainudeen, P.B.; Althari, A.; Iqbal, M.T. A survey on virtual prototyping tools for PCB design. In Proceedings of the 2018 International Conference on Innovative Trends in Computer Engineering (ITCE), Aswan, Egypt, 19–21 February 2018; pp. 93–98. [Google Scholar] [CrossRef]

- Muir, D.; Panicker, R. The use of virtual prototyping in PCB design. In Proceedings of the 2015 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Suzhou, China, 1–3 July 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Chen, J.Y.; Liu, K.S.; Huang, C.M. Virtual prototyping for signal integrity analysis of high-speed PCBs. IEEE Trans. Electromagn. Compat. 2006, 48, 711–720. [Google Scholar] [CrossRef]

- Silaghi, A.M.; Pescari, C.; Bleoju, C.; De Sabata, A. Solving Automotive Signal Integrity Issues by EMC Simulation. In Proceedings of the 2021 IEEE 27th International Symposium for Design and Technology in Electronic Packaging (SIITME), Timisoara, Romania, 25–30 October 2021; pp. 33–36. [Google Scholar] [CrossRef]

- Silaghi, A.M.; Mueller, F.; De Sabata, A.; Buta, A.P.; Nicolae, P.M. Analysis of Shielding Effectiveness of an Automotive Display through Simulation and Testing. In Proceedings of the 2020 International Symposium on Electromagnetic Compatibility-EMC EUROPE, Rome, Italy, 23–25 September 2020; pp. 1–4. [Google Scholar]

- Silaghi, A.M.; De Sabata, A. EMC Simulation of an Automotive Ethernet Interface. In Proceedings of the 2020 International Symposium on Electronics and Telecommunications (ISETC), Timisoara, Romania, 5–6 November 2020; pp. 1–4. [Google Scholar]

- Behagi, A. RF and Microwave Circuit Design: A Design Approach Using (ADS); Advanced Design System; Techno Search: Thane, India, 2015. [Google Scholar]

- Behagi, A. 100 RF and Microwave Circuit Design: With Keysight (ADS) Solutions; Techno Search: Thane, India, 2018. [Google Scholar]

- Johnson, H.; Graham, M. High-speed Digital Design: A Handbook of Black Magic; Prentice Hall Modern Semiconductor Design; Prentice Hall: Upper Saddle River, NJ, USA, 1993. [Google Scholar]

- Carrió, F.; Gonzalez, V.; Sanchis, E. Basic Concepts of Power Distribution Network Design for High-Speed Transmission. Open Opt. J. 2011, 5, 51–61. [Google Scholar] [CrossRef][Green Version]

- Yee, C.F. Achieving Minimal PDN Impedance, SSN and Jitter on PCB with Embedded Capacitance Material. In Proceedings of the 2018 IEEE International RF and Microwave Conference (RFM), Penang, Malaysia, 17–19 December 2018; pp. 155–158. [Google Scholar] [CrossRef]

- Bogatin, E. Signal and Power Integrity–Simplified; Prentice Hall PTR Signal Integrity Library, Prentice Hall: Upper Saddle River, NJ, USA, 2010. [Google Scholar]

- Mudavath, R.; Naik, B.R. Estimation of Far End Crosstalk and Near End Crosstalk Noise with Mutually Coupled RLC Interconnect Models. In Proceedings of the 2018 International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, India, 3–5 April 2018; pp. 182–185. [Google Scholar] [CrossRef]

- Dou, Q.; Abraham, J.A. Jitter Decomposition in High-Speed Communication Systems. In Proceedings of the 2008 13th European Test Symposium, Verbania, Italy, 25–29 May 2008; pp. 157–162. [Google Scholar] [CrossRef]

- Ren, N.; Fu, Z.; Lei, S.; Liu, H.; Tian, S. Methodology for Digital Synthesis of Deterministic and Random Jitter Generation on Rising or Falling Edges of Data Pattern. Electronics 2019, 8, 1510. [Google Scholar] [CrossRef]

| Differential Signal | Common Signal | ||||

|---|---|---|---|---|---|

| Port 1 | Port 2 | Port 1 | Port 2 | ||

| Differential Signal | Port 1 | SDD | SDD | SDC | SDC |

| Port 2 | SDD | SDD | SDC | SDC | |

| Common Signal | Port 1 | SCD | SCD | SCC | SCC |

| Port 2 | SCD | SCD | SCC | SCC | |

| Contribution | Abracom | |

|---|---|---|

| 125 MHz | 124.992 MHz | |

| Random Jitter RMS | 0.11 ps | 0.12 ps |

| Inter Symbols (ISI) | 0.09 ps | 0.14 ps |

| Duty Cycle distortion (DCD) | 0.01 ps | 0.01 ps |

| Periodic (PJ) RMS | 0.26 ps | 0.16 ps |

| Total | 1.56 ps | 1.74 ps |

| Eye aperture (width) | 94.6% | 95.3% |

| Eye aperture (height) | 97.1% | 83.4% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Real, D.; Calvo, D.; Zornoza, J.d.D.; Manzaneda, M. White Rabbit Expansion Board: Design, Architecture, and Signal Integrity Simulations. Electronics 2023, 12, 3394. https://doi.org/10.3390/electronics12163394

Real D, Calvo D, Zornoza JdD, Manzaneda M. White Rabbit Expansion Board: Design, Architecture, and Signal Integrity Simulations. Electronics. 2023; 12(16):3394. https://doi.org/10.3390/electronics12163394

Chicago/Turabian StyleReal, Diego, David Calvo, Juan de Dios Zornoza, and Mario Manzaneda. 2023. "White Rabbit Expansion Board: Design, Architecture, and Signal Integrity Simulations" Electronics 12, no. 16: 3394. https://doi.org/10.3390/electronics12163394

APA StyleReal, D., Calvo, D., Zornoza, J. d. D., & Manzaneda, M. (2023). White Rabbit Expansion Board: Design, Architecture, and Signal Integrity Simulations. Electronics, 12(16), 3394. https://doi.org/10.3390/electronics12163394