Analytical Approach to Improve the Performance of a Fully Integrated Class-F Power Amplifier with 0.13 µm BiCMOS Technology Using Drain–Bulk Capacitor Modulation

Abstract

1. Introduction

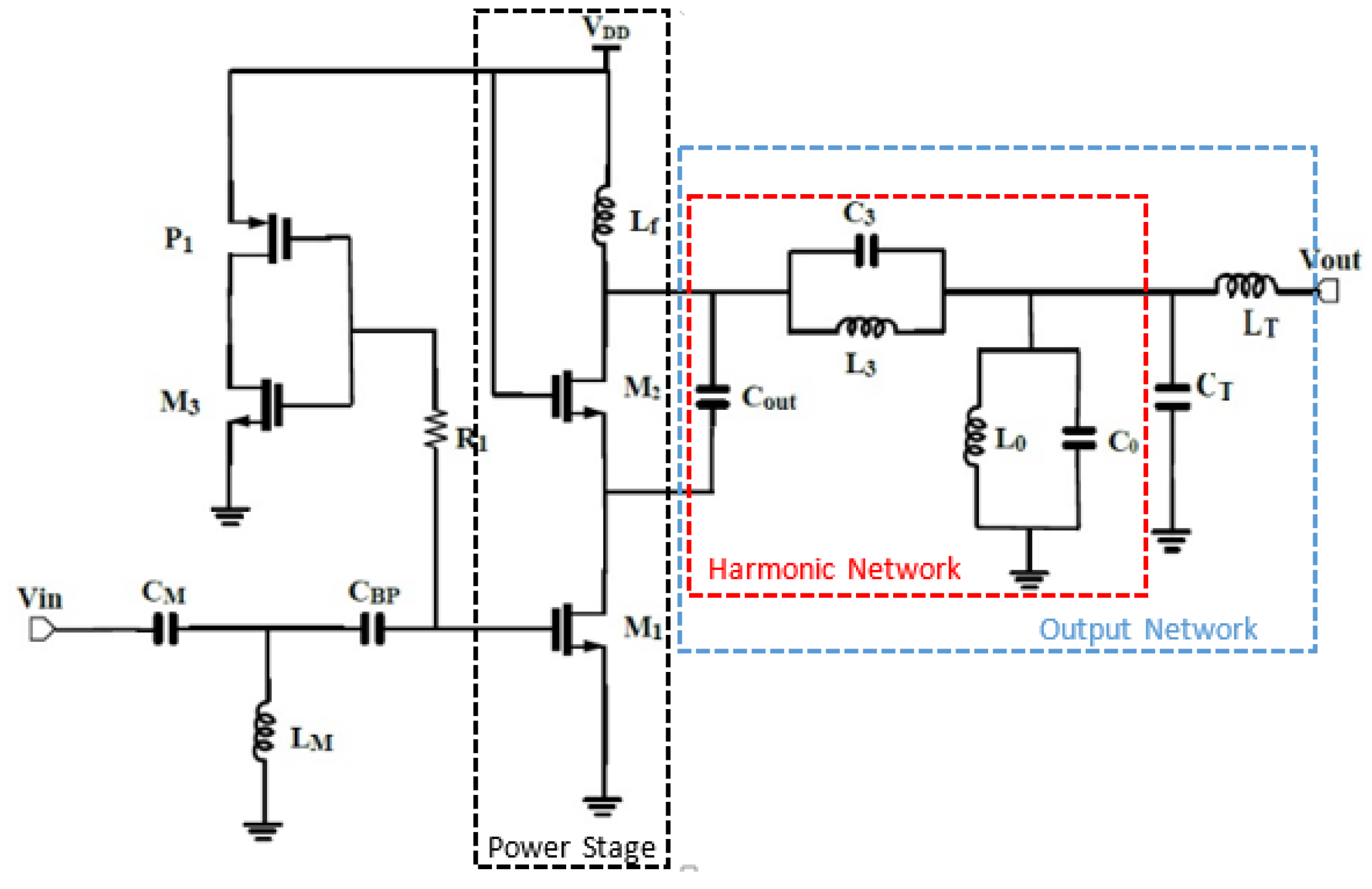

2. Proposed Class-F PA Structure

2.1. Theoretical Study of Class-F Power Amplifiers

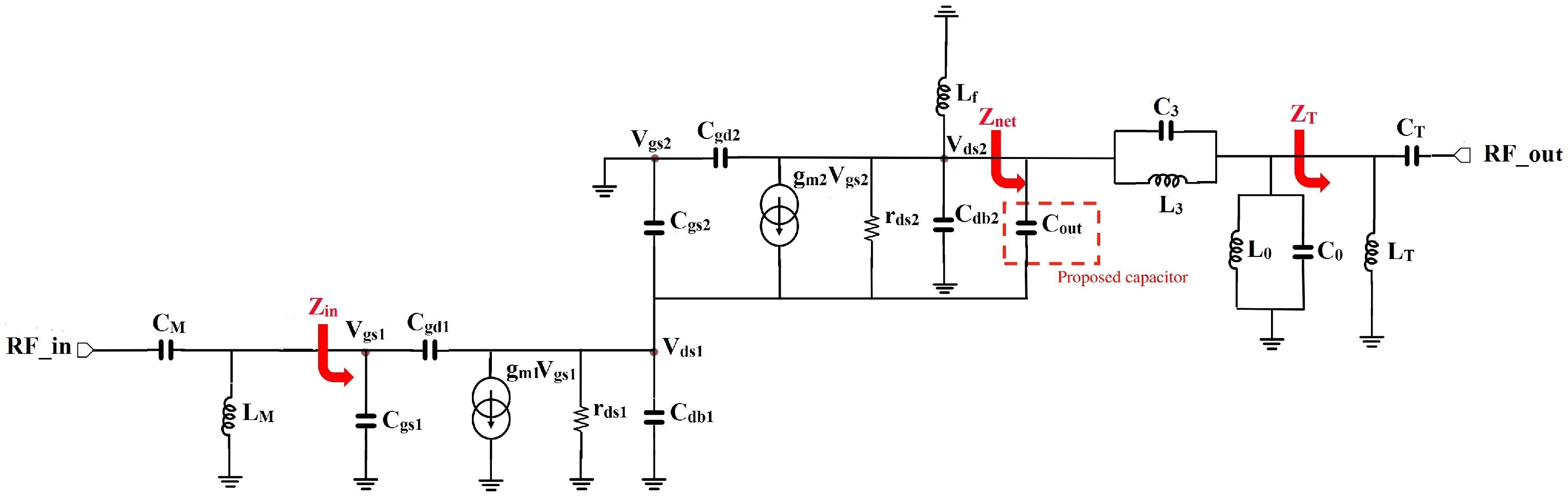

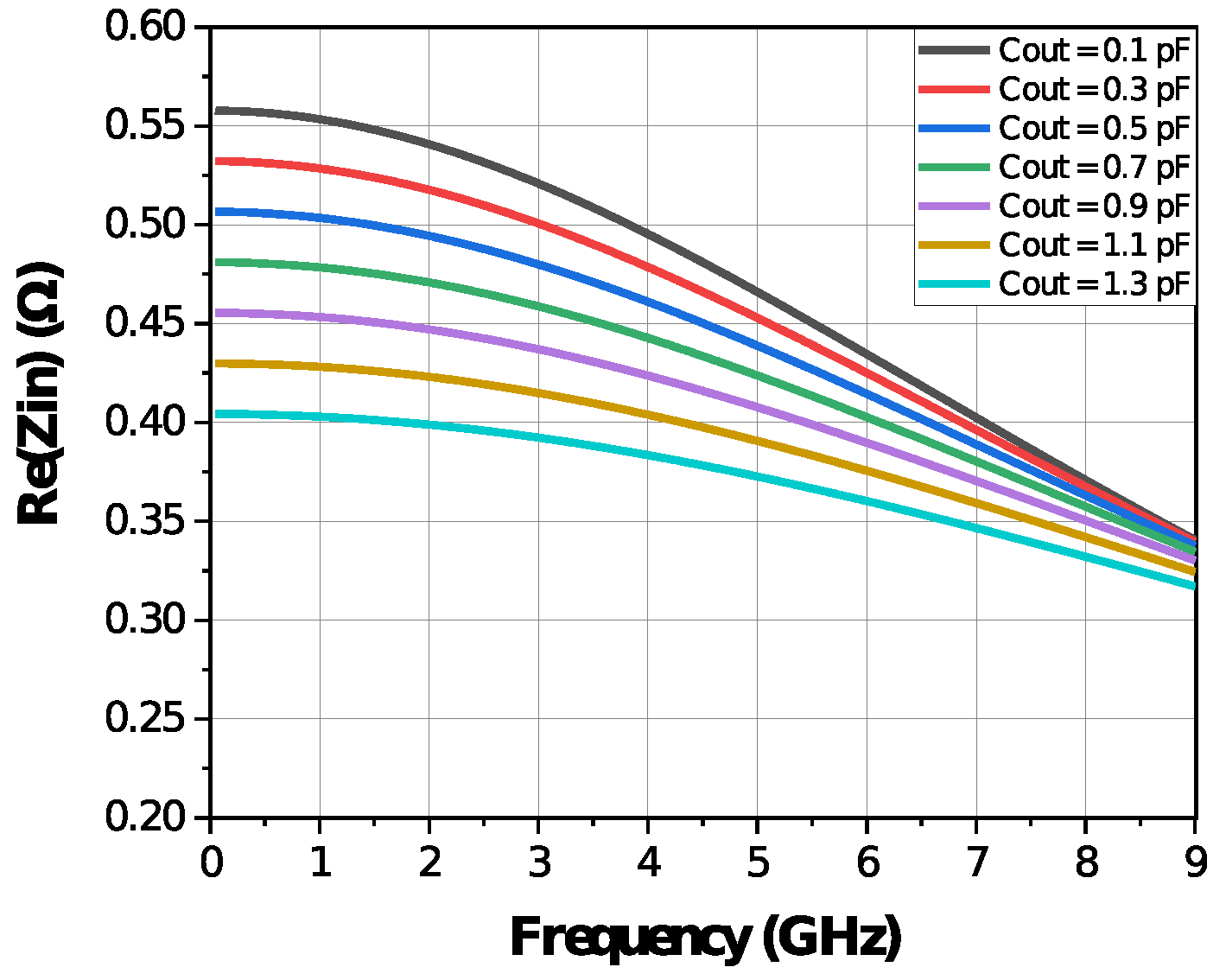

2.2. The Added Output Capacitance’s Effect on the Input Impedance and Stability of the Designed PA

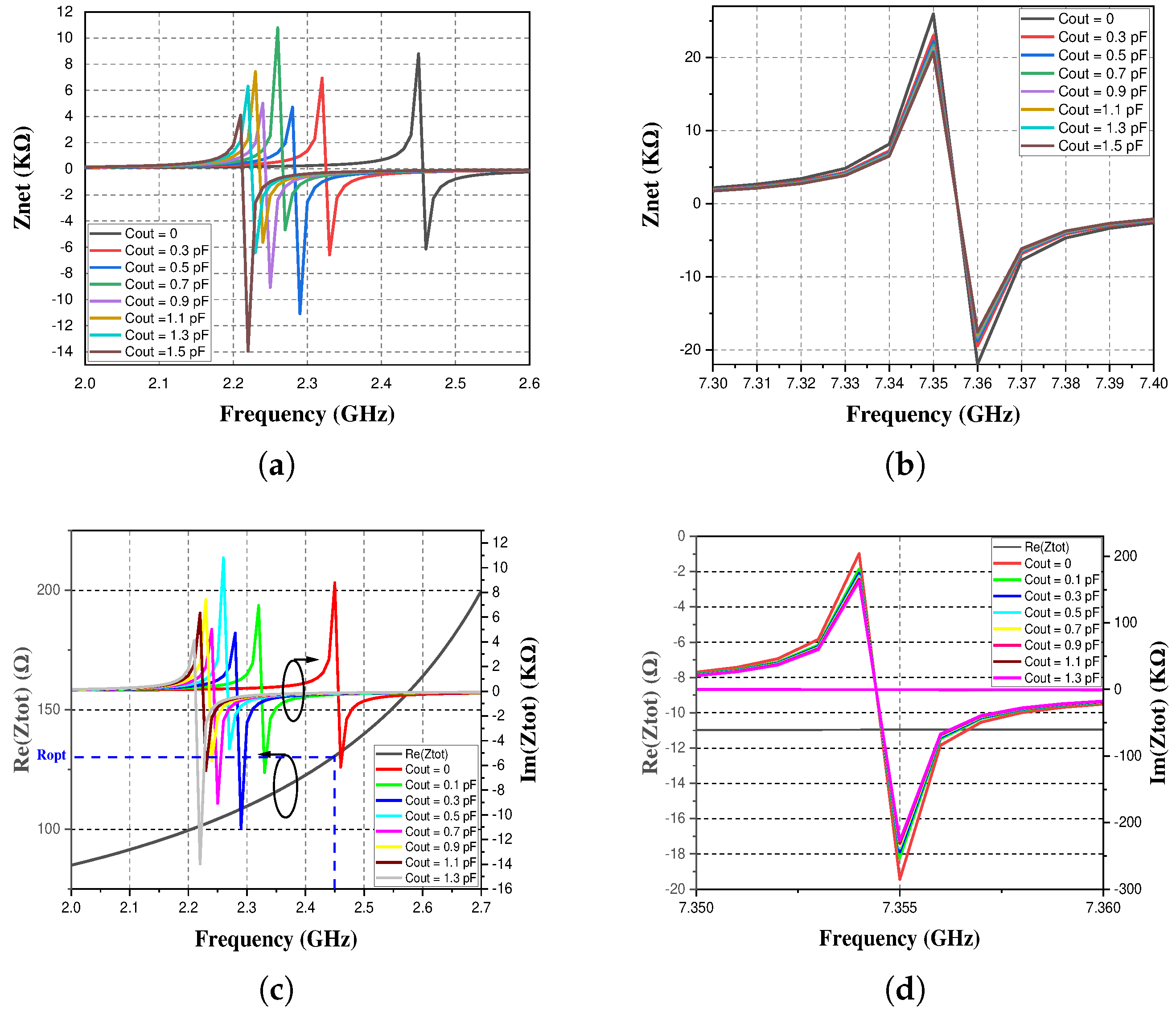

2.3. Impact of the Added Output Capacitance on the Output Network Impedance

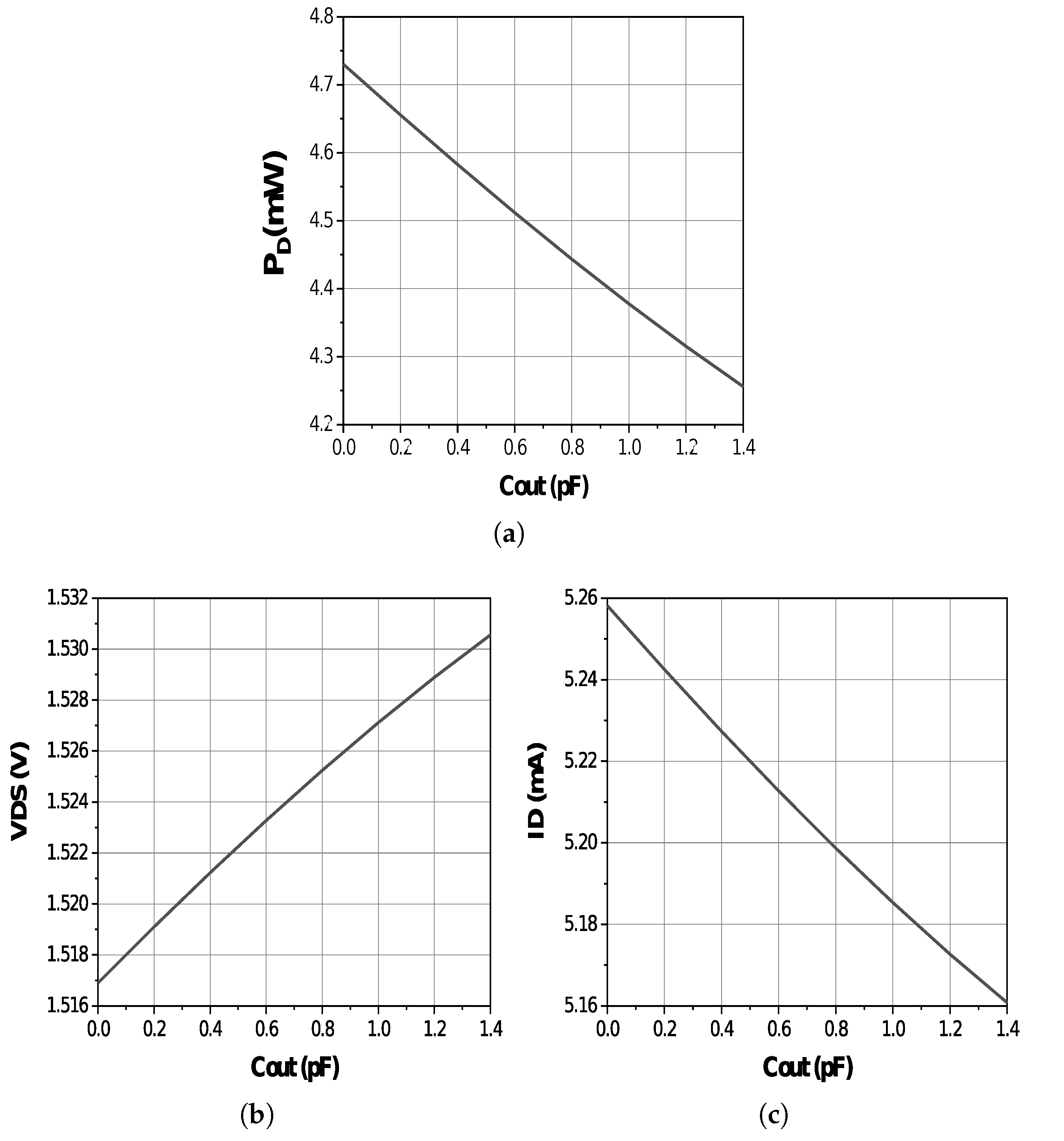

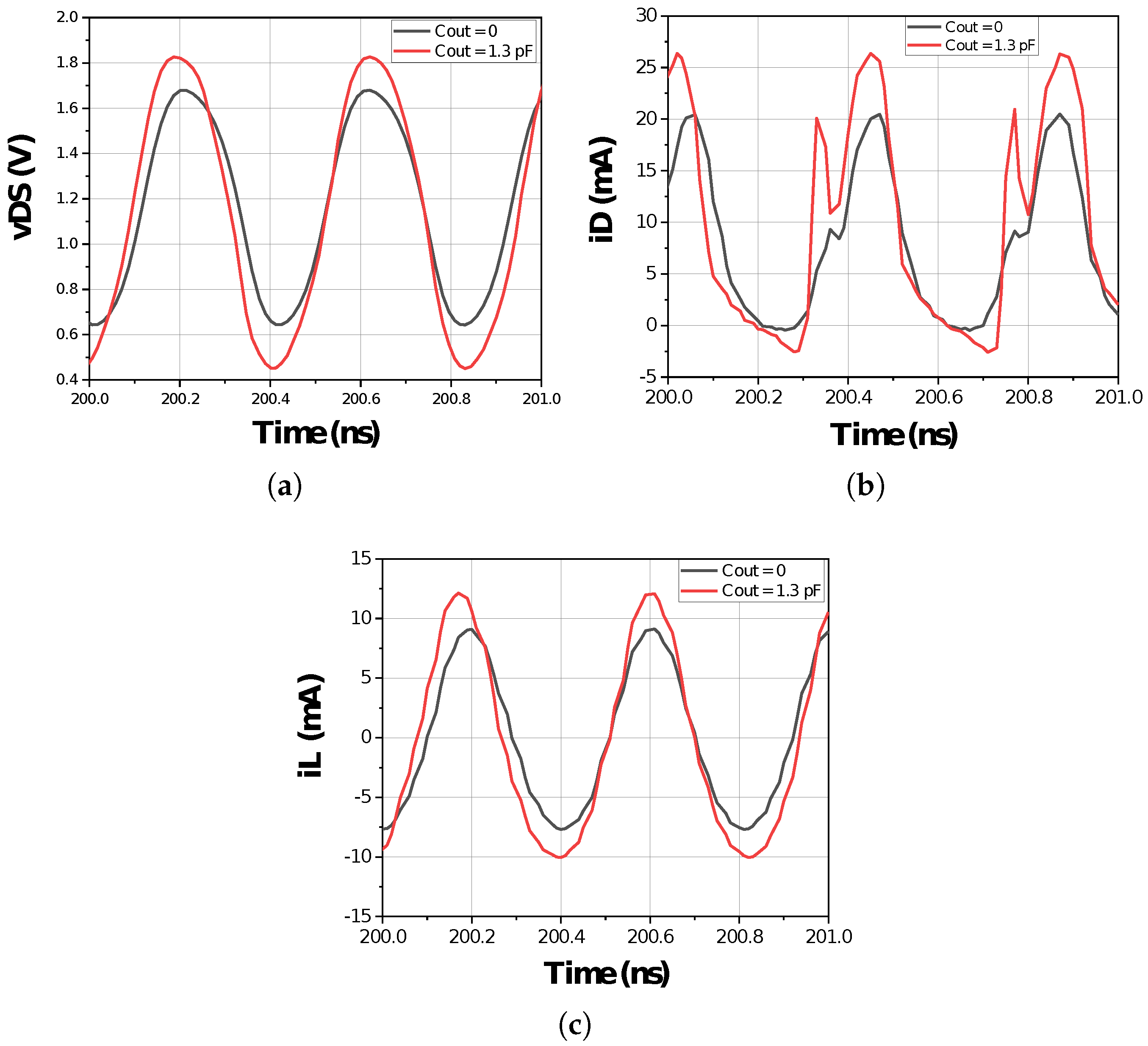

2.4. Added Output Capacitance’s Impact on Parameters at the Drain Level

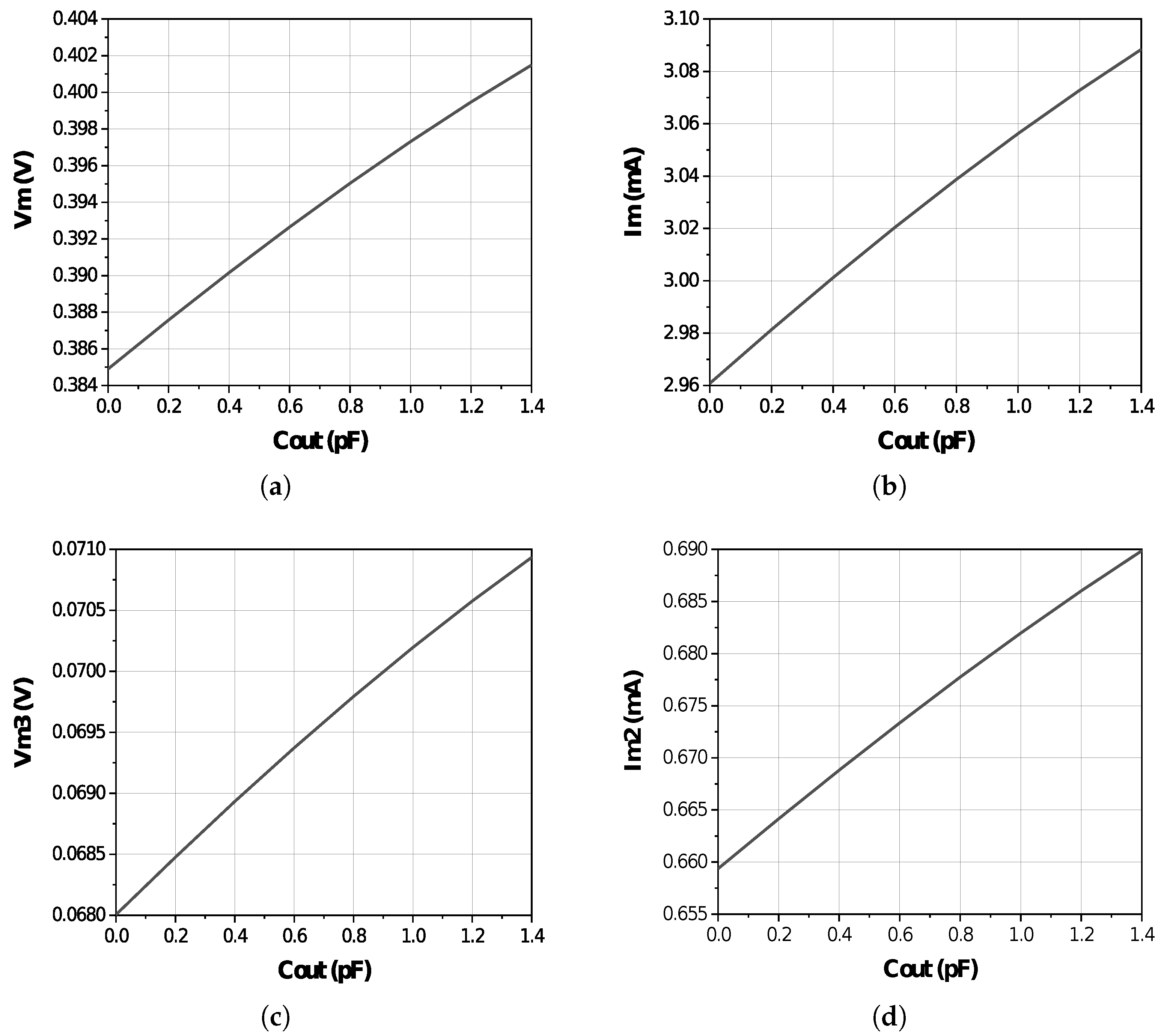

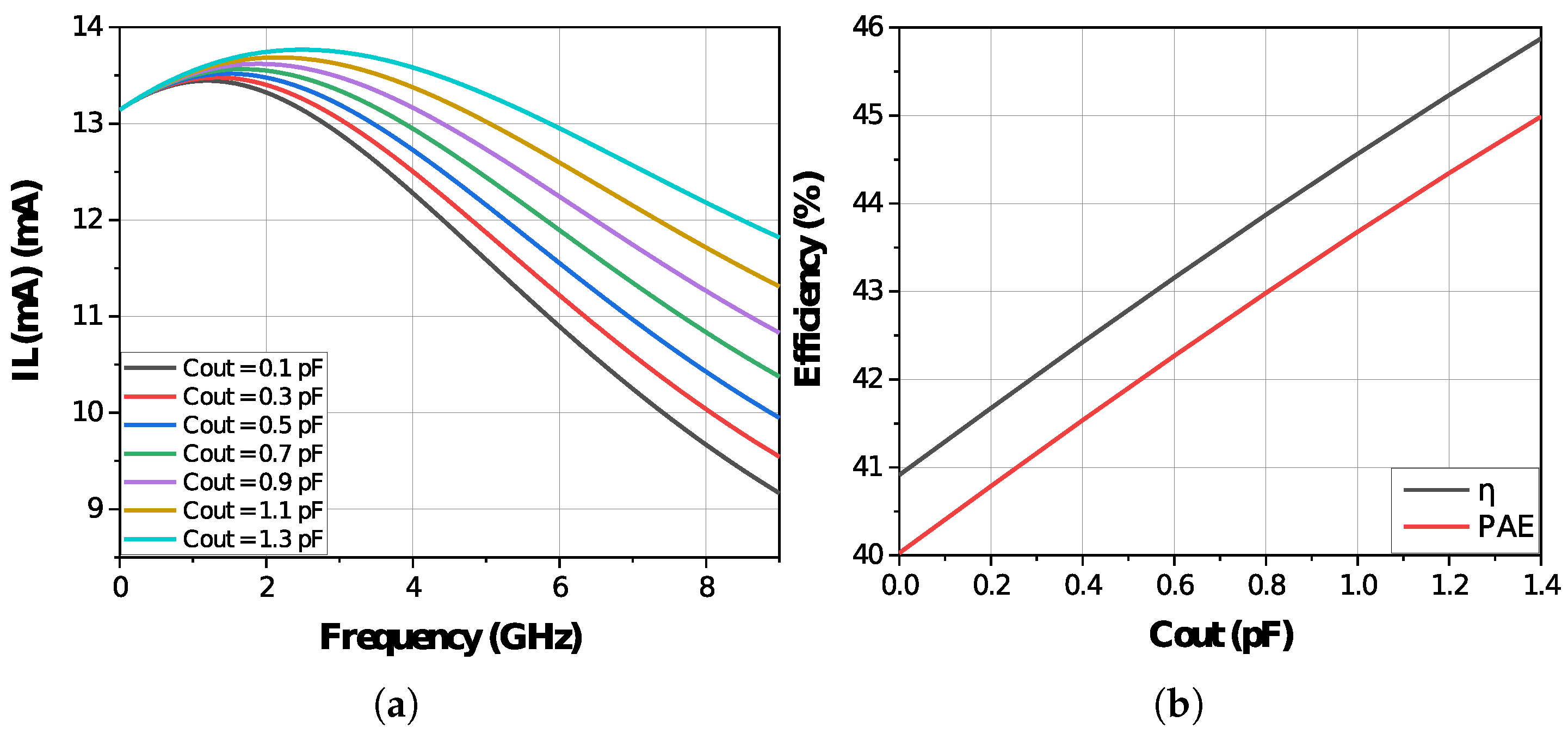

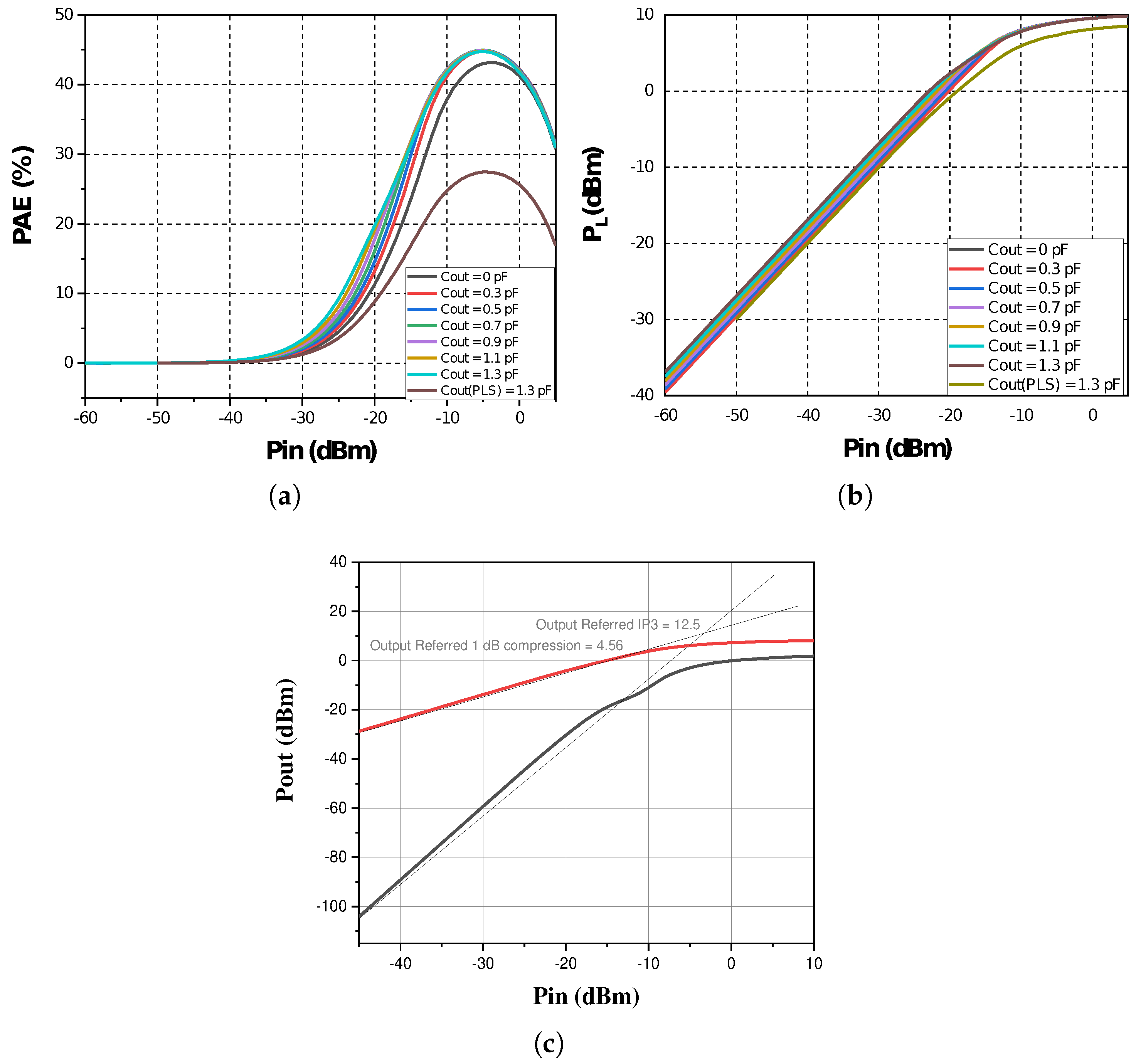

2.5. The Added Output Capacitor’s Impact on Class-F Power Amplifier Performance

3. Class-F Power Amplifier Design with Lossy Components

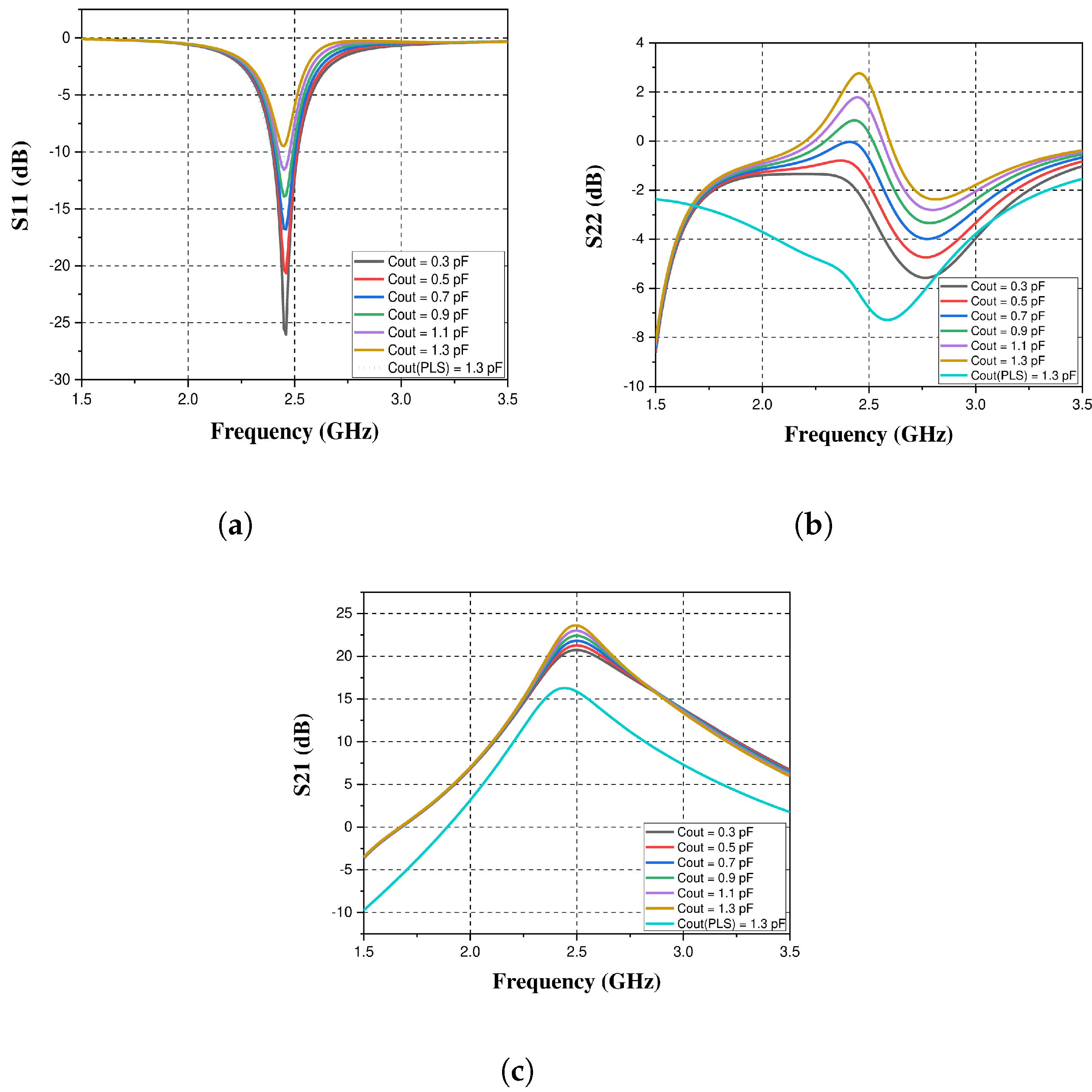

3.1. Performance of Real Class-F Power PAs

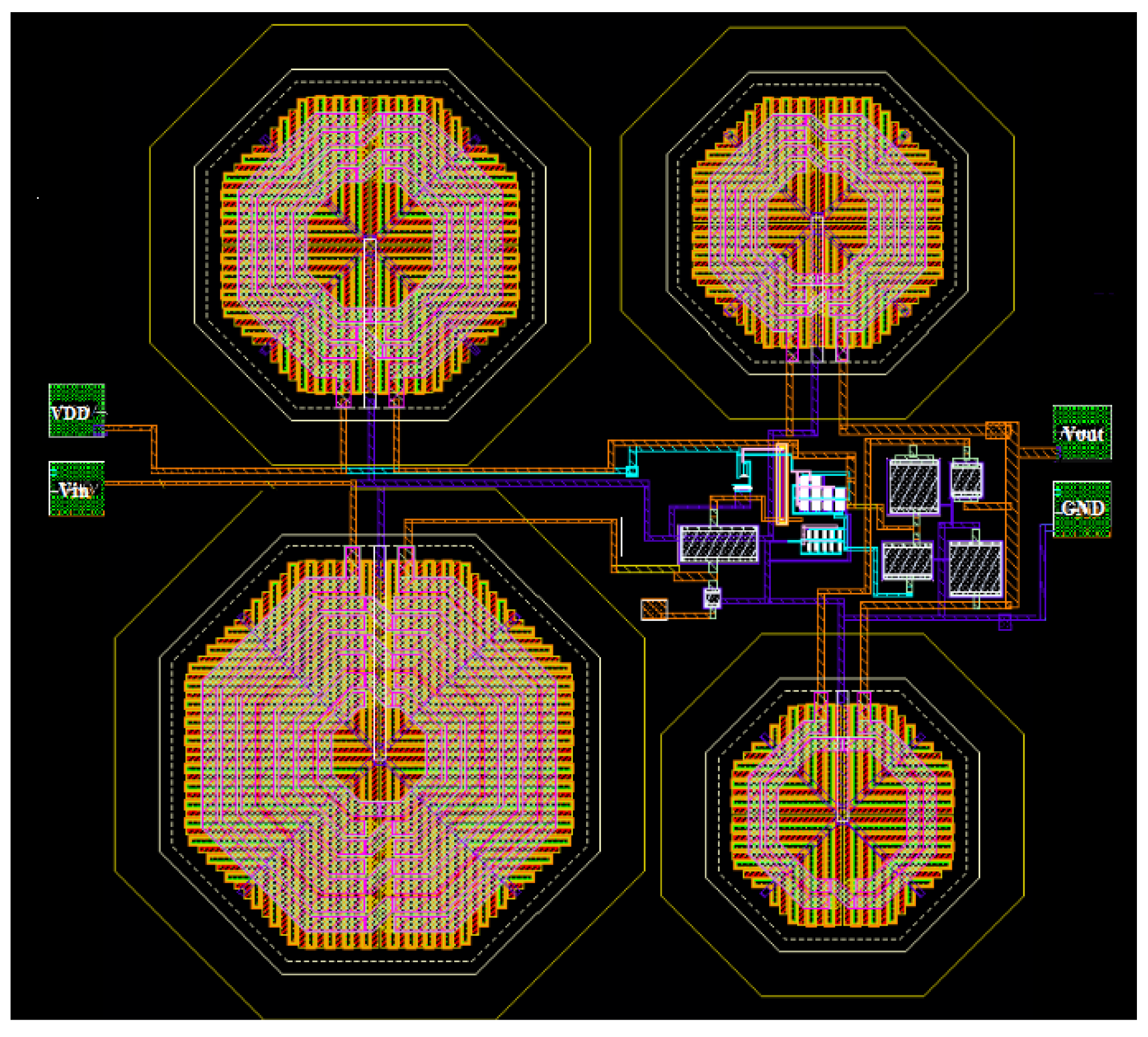

3.2. Layout of the Designed Class-F Power Amplifier

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Niknejad, A.M.; Chowdhury, D.; Chen, J. Design of CMOS power amplifiers. IEEE Trans. Microw. Theory Tech. 2012, 60, 1784–1796. [Google Scholar] [CrossRef]

- Cripps, S.C. RF Power Amplifiers for Wireless Communications; Artech House: Norwood, MA, USA, 2006; Volume 2. [Google Scholar]

- Kazimierczuk, M.K. RF Power Amplifiers; John Wiley & Sons: Hoboken, NJ, USA, 2014. [Google Scholar]

- Im, D.; Kwon, K.; Lee, I.Y. A 1.9-GHz silicon-on-insulator CMOS stacked-FET power amplifier with uniformly distributed voltage stresses. Int. J. Circuit Theory Appl. 2017, 45, 1660–1672. [Google Scholar] [CrossRef]

- Gilasgar, M.; Barlabé, A.; Pradell, L. A 2.4 GHz CMOS class-F power amplifier with reconfigurable load-impedance matching. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 66, 31–42. [Google Scholar] [CrossRef]

- Ali, S.N.; Agarwal, P.; Baylon, J.; Heo, D. Reconfigurable high efficiency power amplifier with tunable coupling coefficient based transformer for 5G applications. In Proceedings of the 2017 IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 4–9 June 2017; pp. 1177–1180. [Google Scholar]

- Kim, J.H.; Park, C.S. A feedback technique to compensate for AM-PM distortion in linear CMOS class-F power amplifier. IEEE Microw. Wirel. Compon. Lett. 2014, 24, 725–727. [Google Scholar] [CrossRef]

- Iguchi, S.; Saito, A.; Watanabe, K.; Sakurai, T.; Takamiya, M. Design Method of Class-F Power Amplifier With Output Power of -20 dBm and Efficient Dual Supply Voltage Transmitter. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 2978–2986. [Google Scholar] [CrossRef]

- Ma, C.; Liu, Y.; Pan, W.; Tang, Y. 0.4–3.0 GHz highly efficient harmonic-tuned power amplifier. Electron. Lett. 2015, 51, 1911–1913. [Google Scholar] [CrossRef]

- Kumaran, A.K.; Pashaeifar, M.; D’Avino, M.; de Vreede, L.C.; Alavi, M.S. On-chip output stage design for a continuous class-F power amplifier. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–5. [Google Scholar]

- Raab, F.H. Class-F power amplifiers with maximally flat waveforms. IEEE Trans. Microw. Theory Tech. 1997, 45, 2007–2012. [Google Scholar] [CrossRef]

- Sharma, T.; Darraji, R.; Ghannouchi, F.; Dawar, N. Generalized continuous class-F harmonic tuned power amplifiers. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 213–215. [Google Scholar] [CrossRef]

- Carrubba, V.; Akmal, M.; Quay, R.; Lees, J.; Benedikt, J.; Cripps, S.C.; Tasker, P.J. The continuous inverse class-F mode with resistive second-harmonic impedance. IEEE Trans. Microw. Theory Tech. 2012, 60, 1928–1936. [Google Scholar] [CrossRef]

- Lu, Z.; Chen, W. Resistive second-harmonic impedance continuous class-F power amplifier with over one octave bandwidth for cognitive radios. IEEE J. Emerg. Sel. Top. Circuits Syst. 2013, 3, 489–497. [Google Scholar] [CrossRef]

- Sessou, K.K.; Neihart, N.M. An Integrated 700–1200-MHz Class-F PA With Tunable Harmonic Terminations in 0.13 um CMOS. IEEE Trans. Microw. Theory Tech. 2015, 63, 1315–1323. [Google Scholar] [CrossRef]

- Ye, L.; Chen, J.; Kong, L.; Alon, E.; Niknejad, A.M. Design considerations for a direct digitally modulated WLAN transmitter with integrated phase path and dynamic impedance modulation. IEEE J. Solid-State Circuits 2013, 48, 3160–3177. [Google Scholar] [CrossRef]

- Liao, H.Y.; Chen, J.H.; Chiou, H.K.; Wang, S.M. Harmonic control network for 2.6 GHz CMOS class-F power amplifier. In Proceedings of the 2009 IEEE International Symposium on Circuits and Systems, Taipei, Taiwan, 24–27 May 2009; pp. 1321–1324. [Google Scholar]

- Hu, S.; Kousai, S.; Wang, H. 2.8 A broadband CMOS digital power amplifier with hybrid class-G Doherty efficiency enhancement. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Love, M.; Thian, M.; Grebennikov, A. A 5-GHz Class-E3F2 power amplifier with 51% PAE and 21-dBm output power on 65nm CMOS. In Proceedings of the 2017 IEEE 18th Wireless and Microwave Technology Conference (WAMICON), Cocoa Beach, FL, USA, 24–25 April 2017; pp. 1–4. [Google Scholar]

- Mansour, M.; Zekry, A.; Ali, M.K.; Shawkey, H. Analysis and Design of a 5G Multi-Mode Power Amplifier using 130 nm CMOS technology. In Proceedings of the 2021 22nd International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 7–9 April 2021; pp. 280–284. [Google Scholar]

- Dong, L.; He, S.; You, F.; Lei, Q. High-efficiency Class-F- 1 power amplifier design with input harmonic manipulation. In Proceedings of the 2012 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications, Santa Clara, CA, USA, 15–18 January 2012; pp. 1–4. [Google Scholar]

- Tsai, M.D.; Lin, C.C.; Chen, P.Y.; Chang, T.Y.; Tseng, C.W.; Lin, L.C.; Beale, C.; Tseng, B.; Tenbroek, B.; Chiu, C.S.; et al. 13.1 A fully integrated multimode front-end module for GSM/EDGE/TD-SCDMA/TD-LTE applications using a Class-F CMOS power amplifier. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 216–217. [Google Scholar]

- Chakrabarti, A.; Krishnaswamy, H. High-power high-efficiency class-E-like stacked mmWave PAs in SOI and bulk CMOS: Theory and implementation. IEEE Trans. Microw. Theory Tech. 2014, 62, 1686–1704. [Google Scholar] [CrossRef]

- Peng, X.; Yin, J.; Mak, P.I.; Yu, W.H.; Martins, R.P. A 2.4-GHz ZigBee Transmitter Using a Function-Reuse Class-F DCO-PA and an ADPLL Achieving 22.6% (14.5%) System Efficiency at 6-dBm (0-dBm) Pout. IEEE J. Solid-State Circuits 2017, 52, 1495–1508. [Google Scholar] [CrossRef]

- Chen, F.; Wang, Y.; Hsiao, Y.H.; Lin, J.L.; Chen, Y.C.; Wang, H. A 4.6-GHz Class-F- 1 high power CMOS power amplifier. In Proceedings of the 2017 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Seoul, Republic of Korea, 30 August–1 September 2017; pp. 183–185. [Google Scholar]

| Parameter | (V) | (max) % | (dBm) | (V) | (pF/m) | (fF) | (pF) | (nH) | (pF) | (pF) | (pF) | (pF) | (pF) |

| Value | 1.2 | 70 | 8 | 0.24 | 0.014 | 0.14 | 0.175 | 7.78 | 4.24 | 0.48 | 0.018 | 0.056 | 1.176 |

| Parameter | (pF) | (nH) | (nH) | (pF) | (nH) | (pF) | (nH) | (pF) | (mA/V) | (mA/V) | |||

| Value | 0.424 | 2.4 | 0.642 | 0.736 | 1.91 | 2.22 | 1.26 | 0.555 | 1.17.10 | 5.6.10 | 0.38 | 0.128 | 130 |

| Ref. | Technology | Frequency (GHz) | VDD (V) | PDC (mW) | PL (dBm) | GP (dB) | PAE (%) | Area (mm) | Class | ITRS FOM | Technique |

|---|---|---|---|---|---|---|---|---|---|---|---|

| [5] | CMOS | 2.4 | 3–4 | - | 18.7 ** 19.5 *** (Sat) | 10.2 ** 11.5 *** | 28.9 ** 26 *** | 2.56 | F | 32.75 | - Reconfigurable load-impedance matching. |

| [7] | 0.18 m CMOS | 0.869 | 3.3 | - | 26.7 *** (max) | 31.2 *** | 34.2 *** | 1.496 | F | - | - Off-chip OMN and feedback. |

| [8] | 40 nm CMOS | 2.4 | 0.56–0.2 | - | −20 *** (Sat) | - | 42 *** | 0.3 | F | - | - Merging OMN and Filter to improve an output power. |

| [10] | 40 nm CMOS | 2.4 | 2.7 | - | 27 ** (Sat) | - | 68 ** (Sat) | - | F | - | - Design of CCF PA with Transformer Balun, RF Shock, 2nd Harmonic Branch. |

| [17] | 0.18 m CMOS | 2.6 | 1.8 | 716.4 | ≈21 *** (sat) | 13.1 *** | 24.4 *** | 0.998 | F | 36.27 | - Tunable harmonic termination. |

| [20] | CMOS | 4.8 | 3 | 136/26 | 23/22.3 ** (Sat) | 24/27 ** | 29.5/28.6 ** (Sat) | 0.53 | F | 55.32 | - Linear/switching modes with tuning output network. |

| [22] | 153 nm CMOS | 2.4 | 3.5 | - | 31.5 *** (Sat) | 35.3 *** | 35 *** | 2.9 | F | - | - GSM/EDGE/TD- SCDMA/TD-LTE by transformer combination. |

| [24] | 65 nm CMOS | 2.4 | 0.3–0.7 | 15.3 (Sat) | 6 *** (Sat) | – | 26.1 *** (Sat) | 0.39 | F | - | - Function reuse class-F DCO-PA + ADPLL. |

| [25] | CMOS | 4.6 | 3.6 | 158 | 27.8 *** (Sat) | 11.6 *** | 32 *** (Sat) | 2.32 | F | 47.71 | - Differential topology based on the transformer combiner. |

| This work | BiCMOS | 2.4 | 1.2 | 5–8 | 8 **(Sat) (+5 PBO) 4.56 ** (−1 dB) | 20 ** (+5 PBO) | 28 ** (+10 PBO) | 0.43 | F | 35.05 | - Tuned output network by cascode stage output capacitor modulation. |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Traiche, S.; Trabelsi, M.; Bououden, A.; Yagoub, M.C.E. Analytical Approach to Improve the Performance of a Fully Integrated Class-F Power Amplifier with 0.13 µm BiCMOS Technology Using Drain–Bulk Capacitor Modulation. Electronics 2023, 12, 2784. https://doi.org/10.3390/electronics12132784

Traiche S, Trabelsi M, Bououden A, Yagoub MCE. Analytical Approach to Improve the Performance of a Fully Integrated Class-F Power Amplifier with 0.13 µm BiCMOS Technology Using Drain–Bulk Capacitor Modulation. Electronics. 2023; 12(13):2784. https://doi.org/10.3390/electronics12132784

Chicago/Turabian StyleTraiche, Smail, Mohamed Trabelsi, Ali Bououden, and Mustapha C. E. Yagoub. 2023. "Analytical Approach to Improve the Performance of a Fully Integrated Class-F Power Amplifier with 0.13 µm BiCMOS Technology Using Drain–Bulk Capacitor Modulation" Electronics 12, no. 13: 2784. https://doi.org/10.3390/electronics12132784

APA StyleTraiche, S., Trabelsi, M., Bououden, A., & Yagoub, M. C. E. (2023). Analytical Approach to Improve the Performance of a Fully Integrated Class-F Power Amplifier with 0.13 µm BiCMOS Technology Using Drain–Bulk Capacitor Modulation. Electronics, 12(13), 2784. https://doi.org/10.3390/electronics12132784