Survey of Reliability Research on 3D Packaged Memory

Abstract

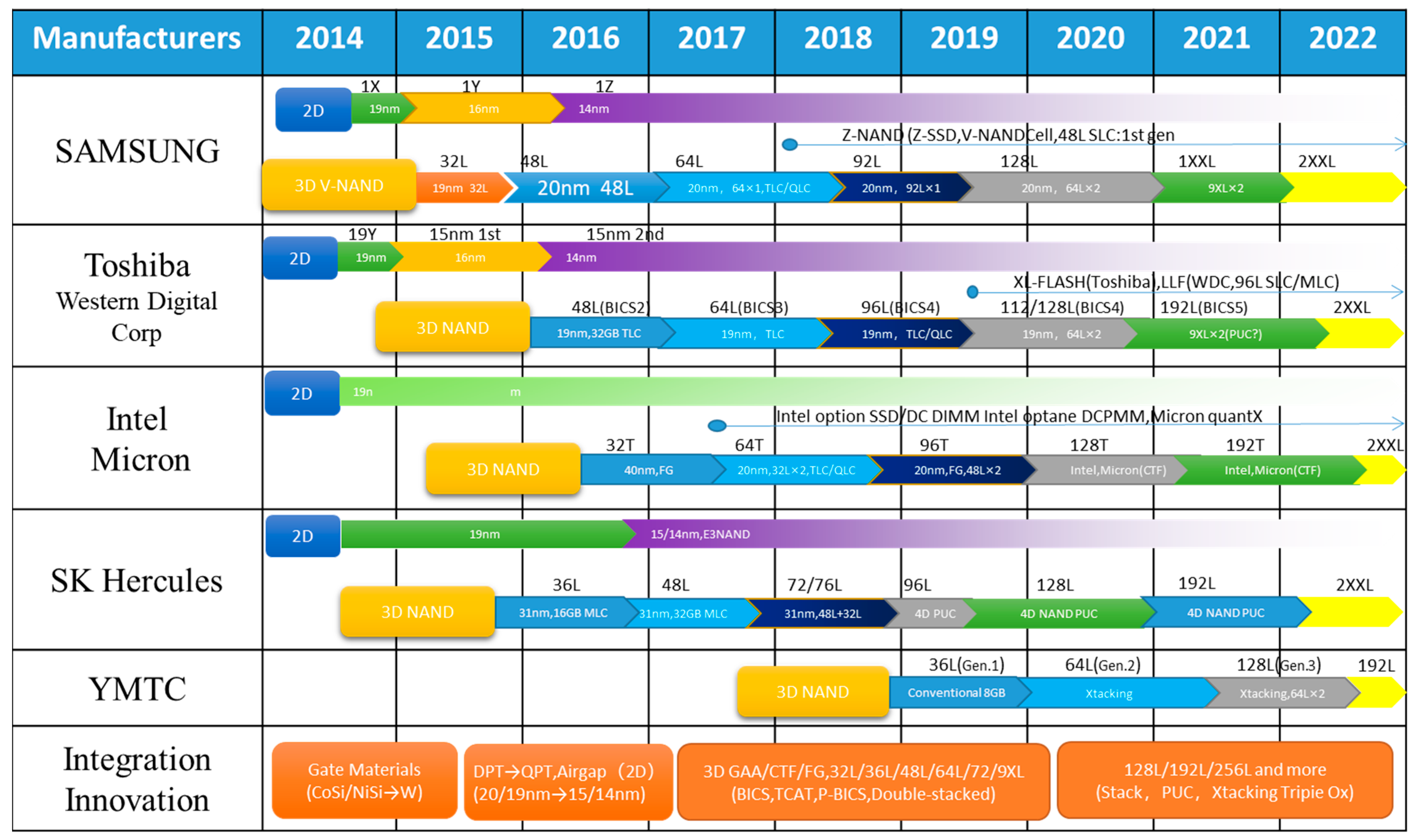

:1. Introduction

2. 3D Packaging Structure of Memory

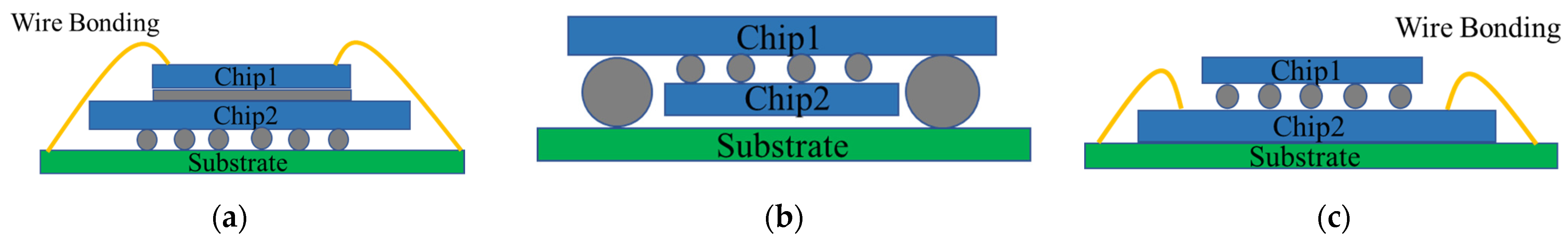

2.1. CoC (ChIP-on-Chip) Structure

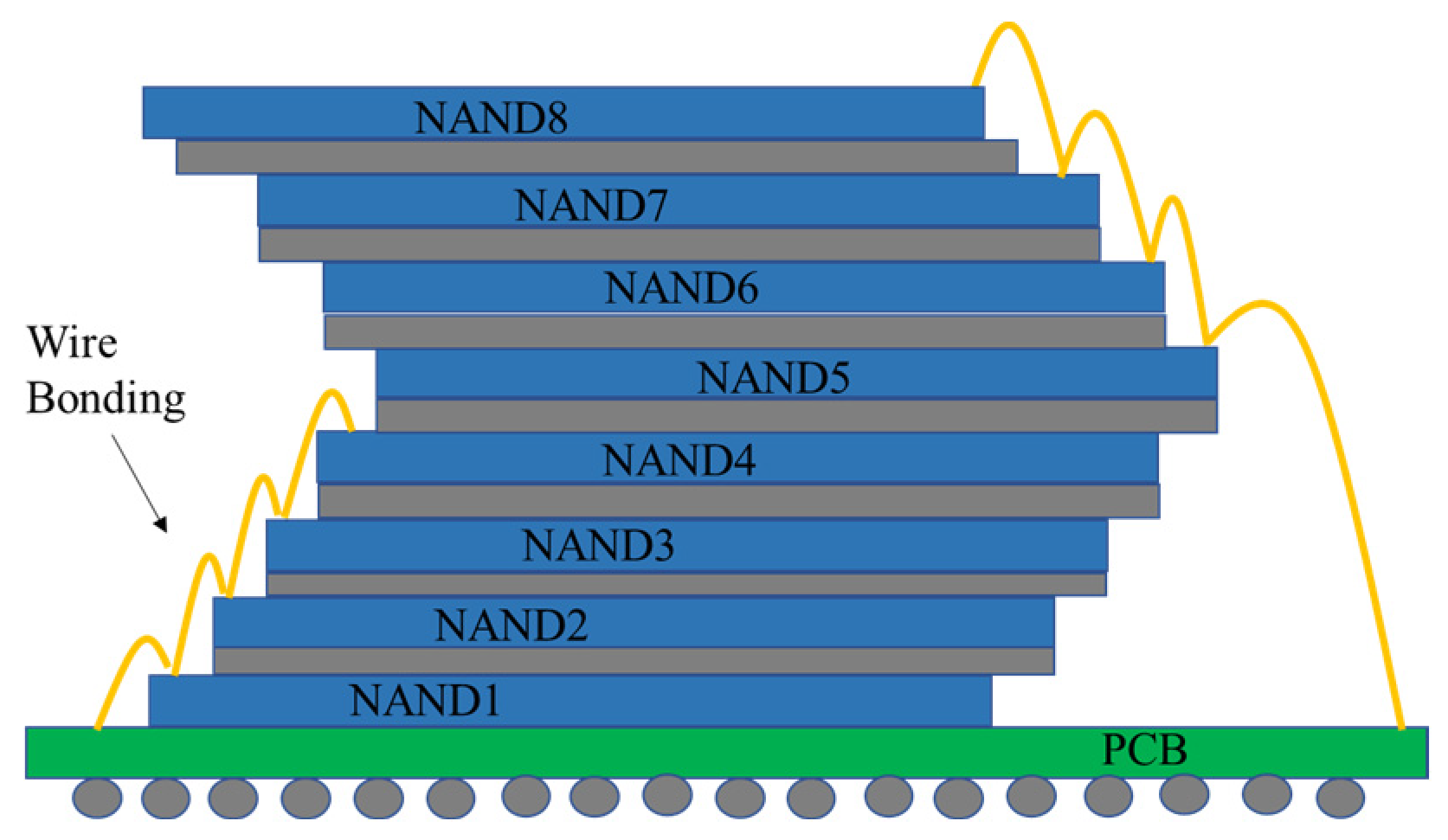

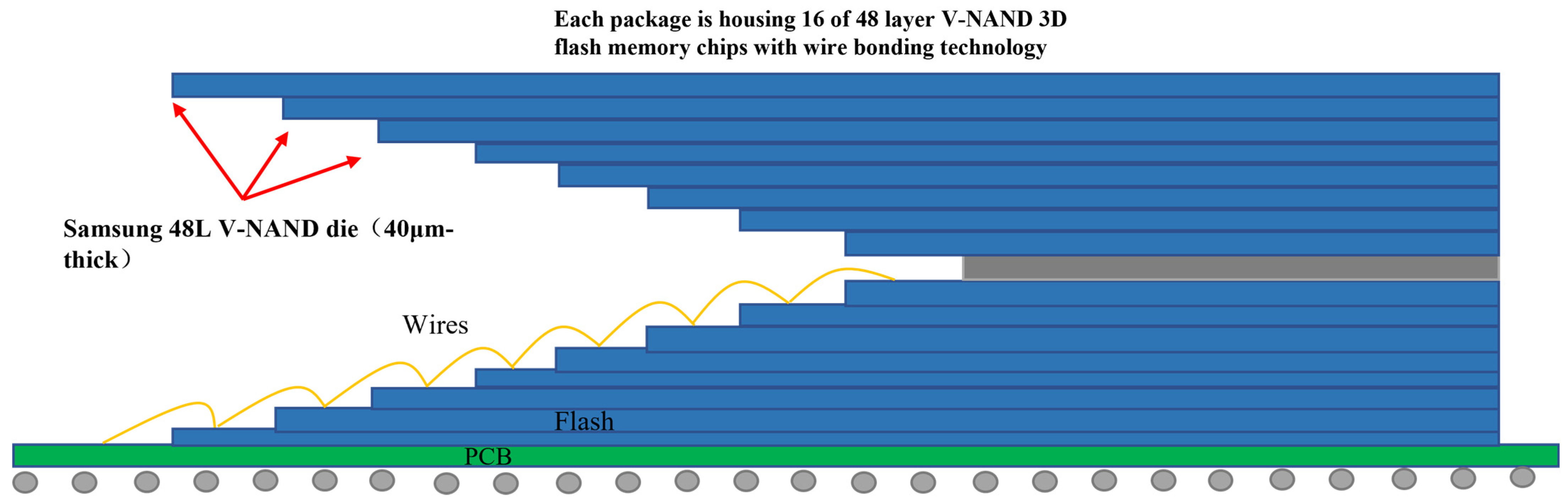

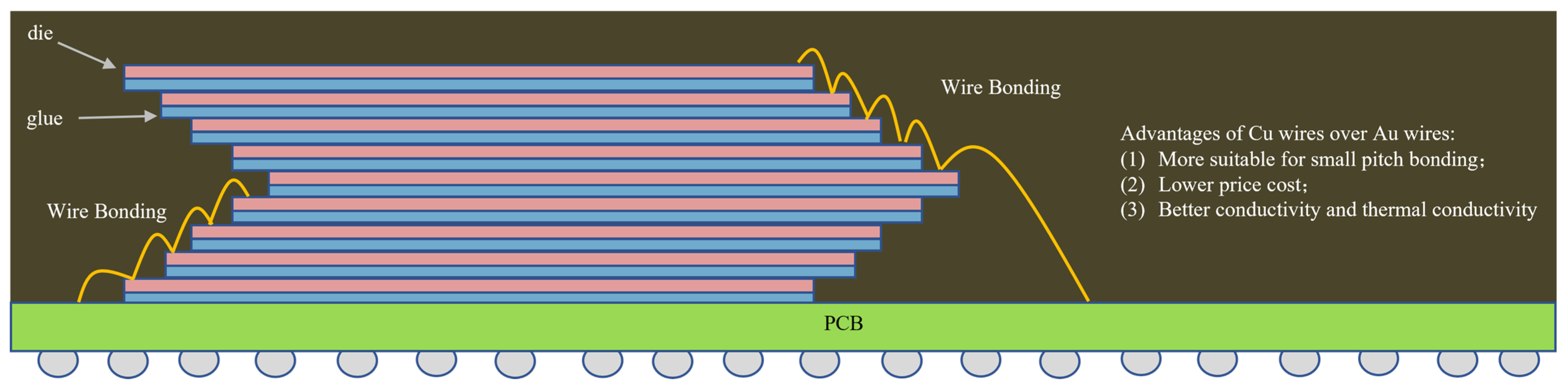

2.1.1. WB Interconnecting Structure

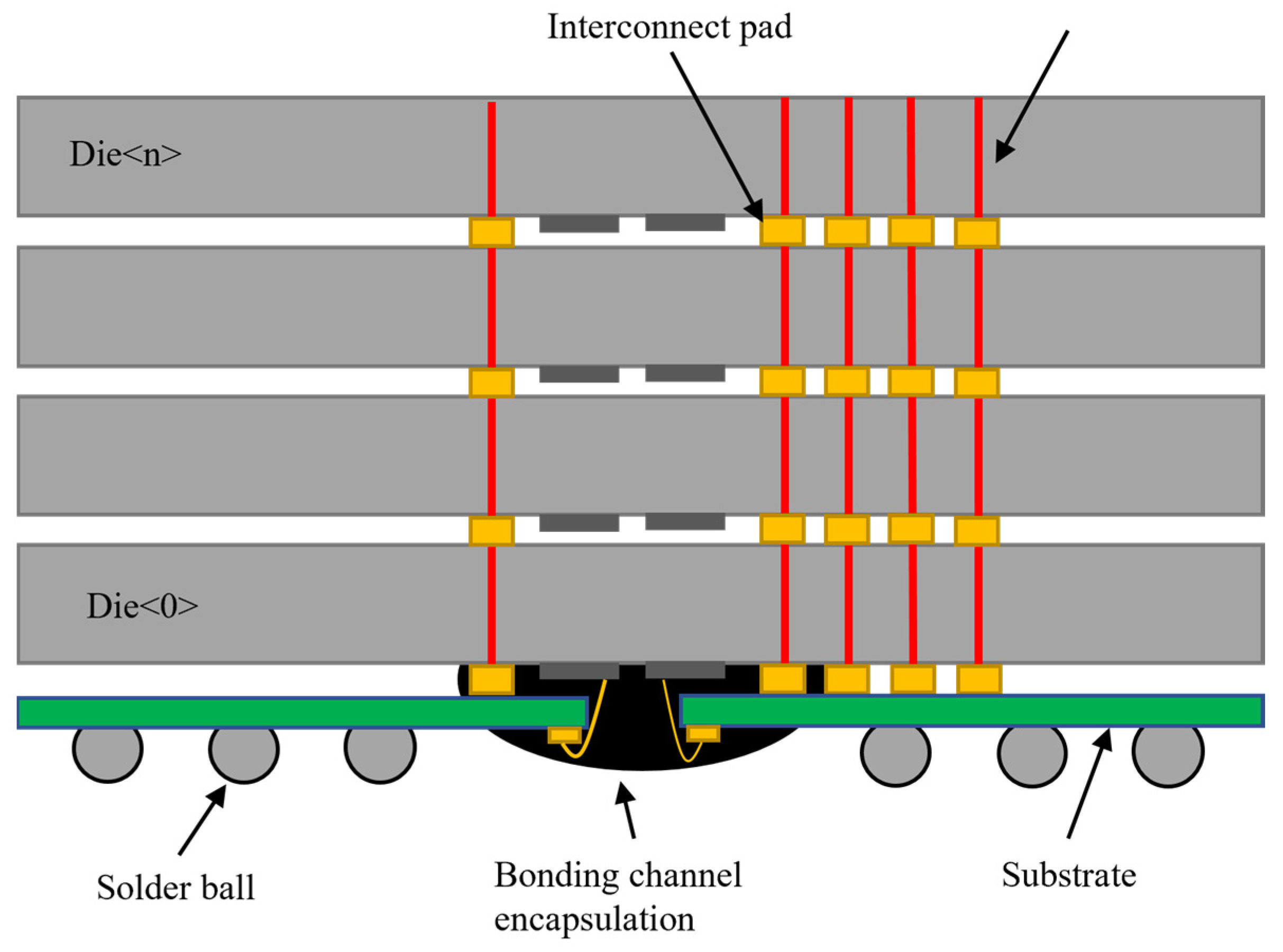

2.1.2. TSV Interconnection Structure

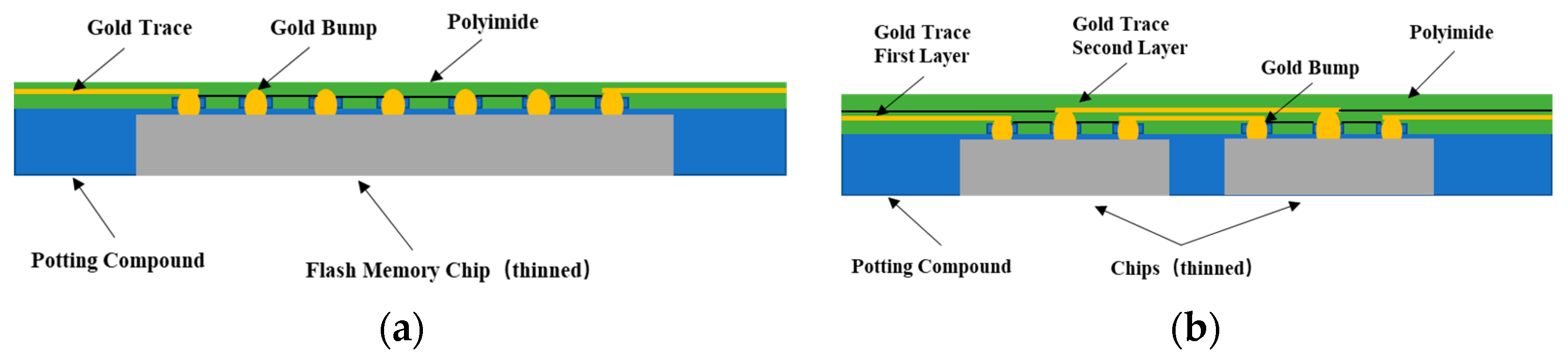

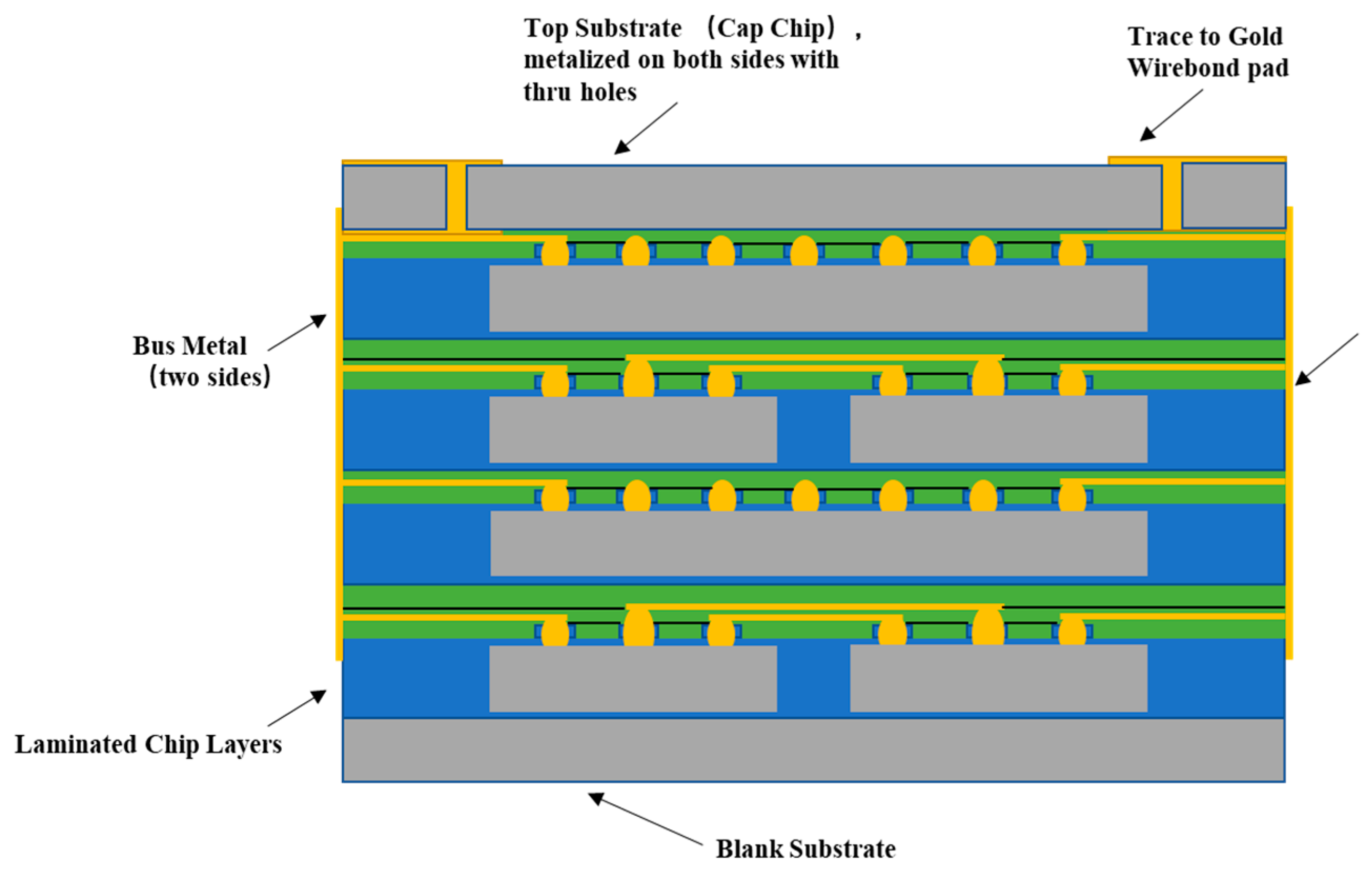

2.2. Package-Stacking Structure

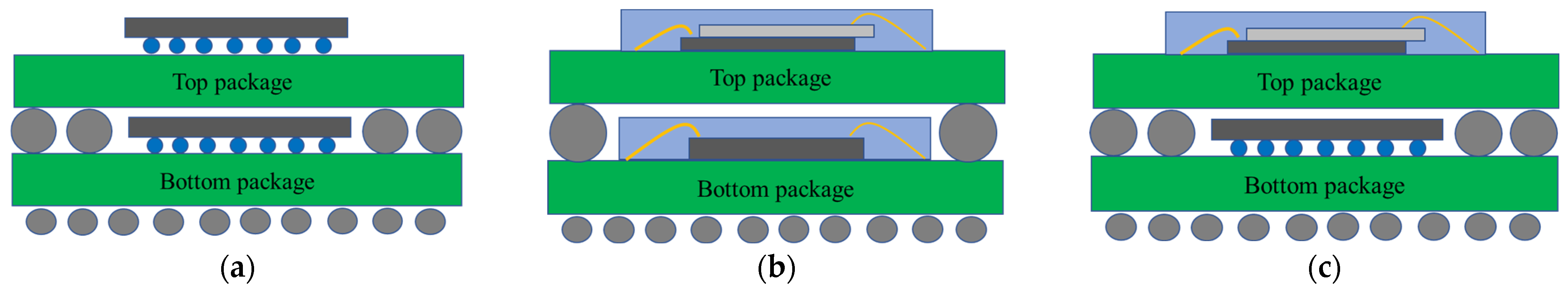

2.2.1. PoP Structure

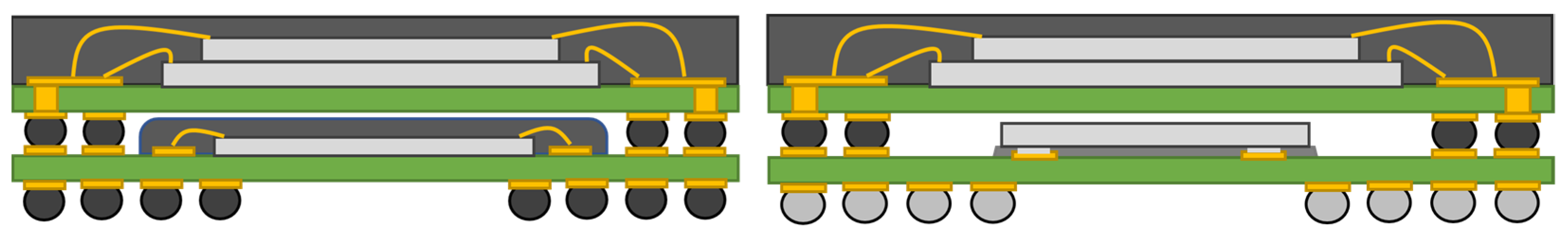

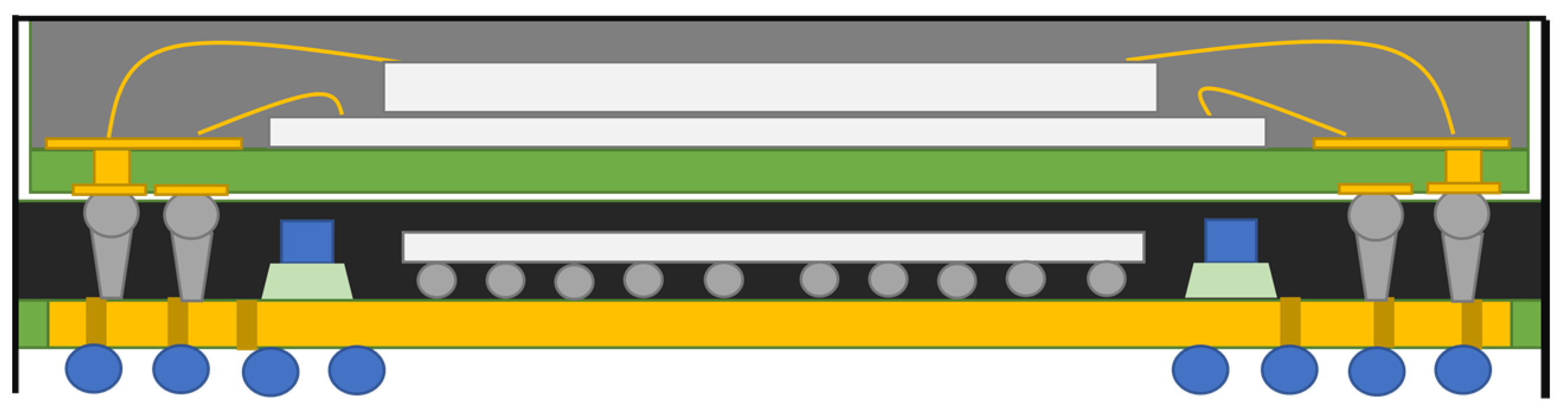

2.2.2. PiP Structure

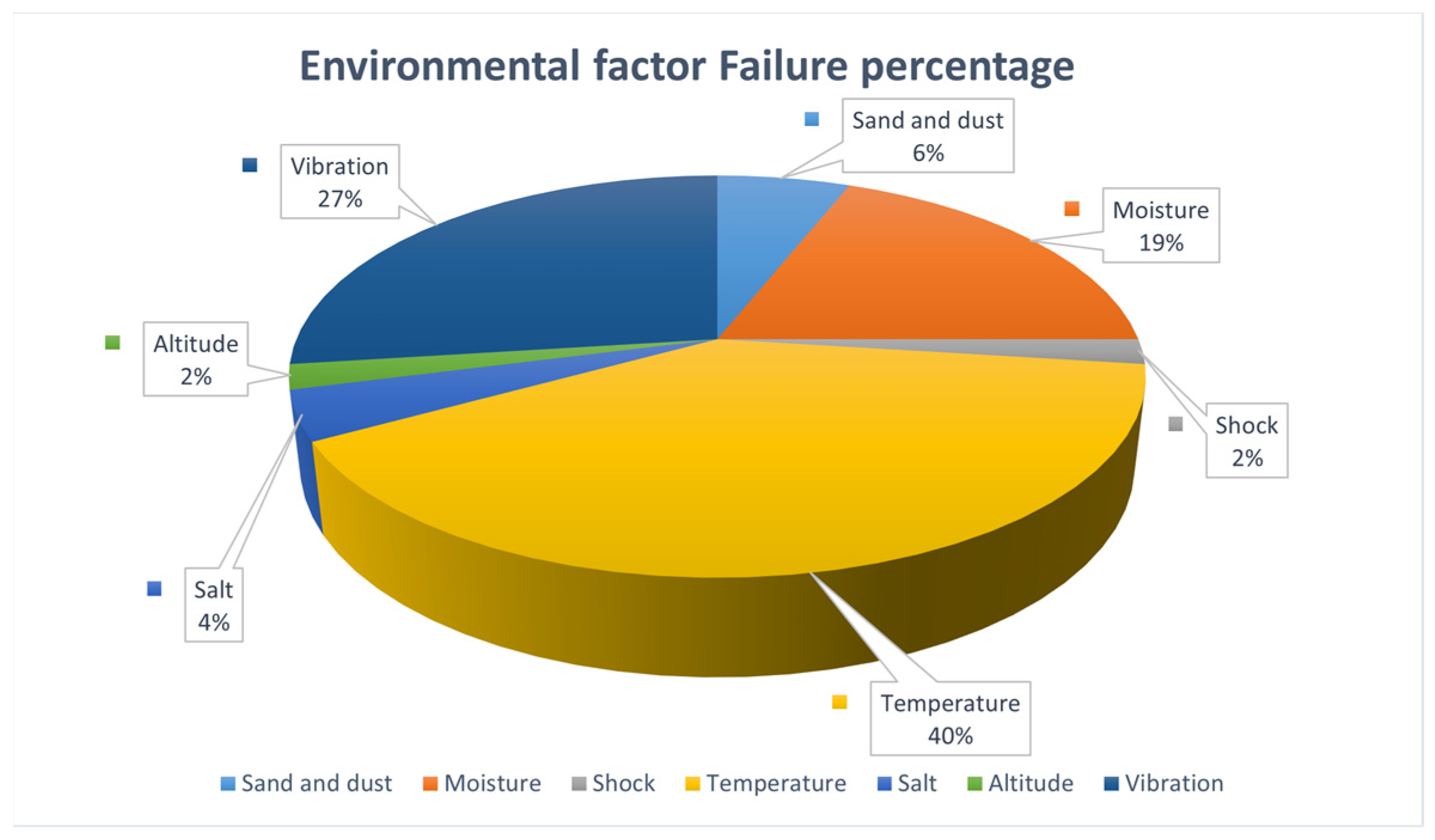

3. Failure Reason Analysis of 3D Packaging Memory

3.1. The Influence of Thermal Stress on Reliability

3.2. The Influence of Mechanical Stress on Reliability

3.3. The Influence of Hygrothermal Stress on Reliability

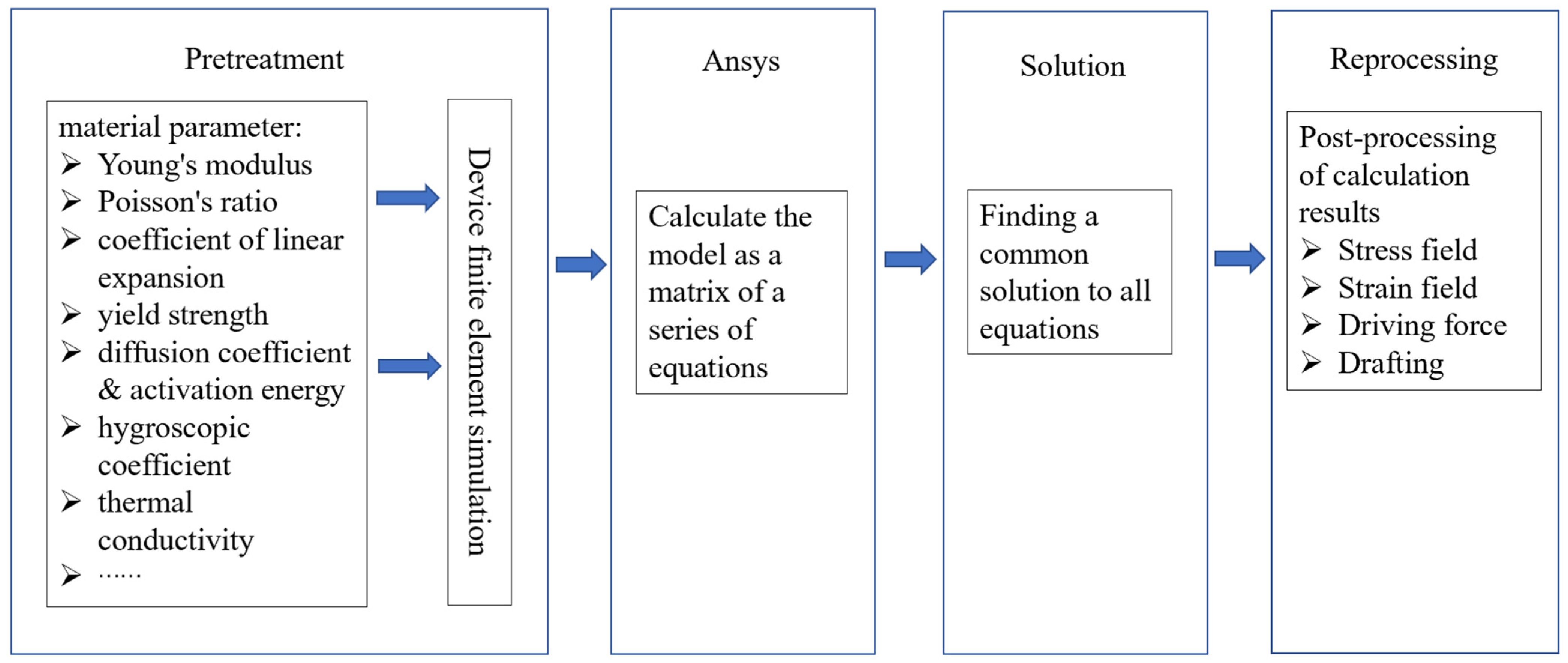

4. Reliability Theories for 3D Packaging Memory

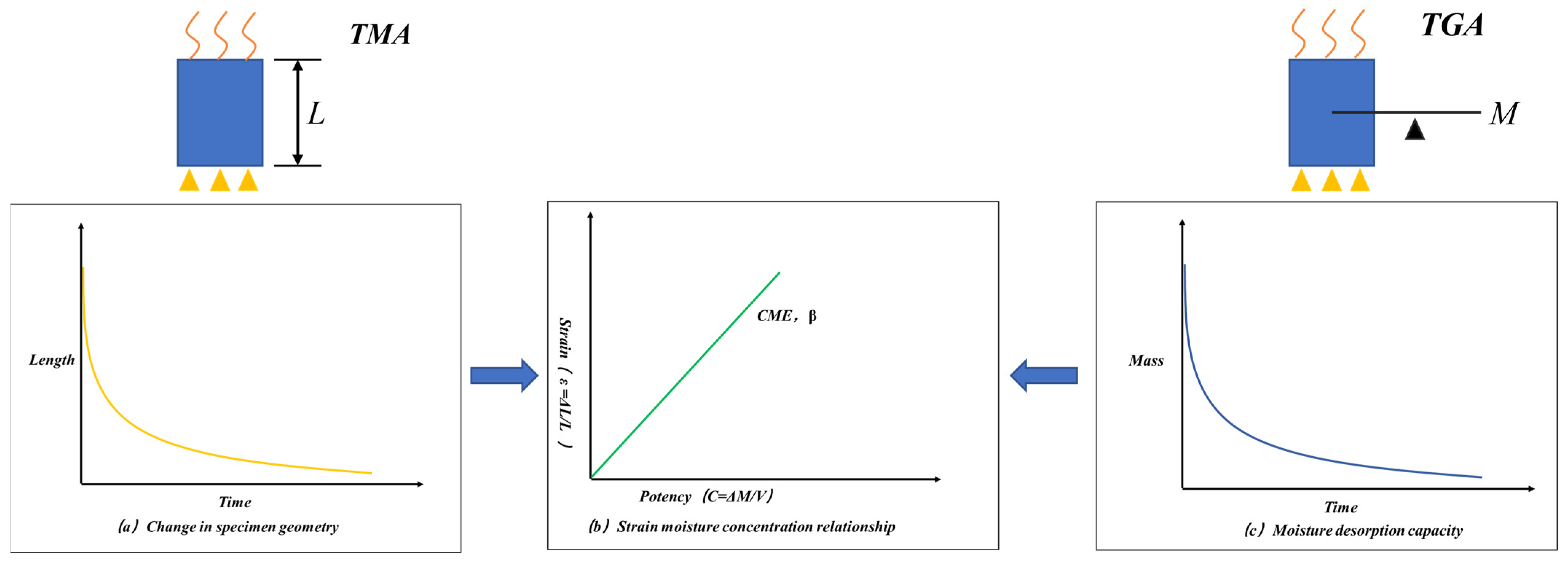

4.1. Theories of Hygrothermal Stress on Reliability

4.1.1. Moisture Diffusion

4.1.2. Moisture Stress Distribution

4.2. Theories of the Effect of Thermal Stress on Reliability

4.2.1. Temperature Field

4.2.2. Thermal Stress

4.3. Theories of Mechanical Stress on Reliability

4.3.1. Random Vibration

4.3.2. Sinusoidal Vibration

4.3.3. Drop-Induced Shock

5. Typical Models for Fatigue Life Prediction of Solder Joint

5.1. Fatigue Life Prediction Models of Solder Joints Based on Plastic Deformation

5.1.1. Coffin–Manson Model

5.1.2. Engelmaier Model

5.2. Fatigue Life Prediction Models of Solder Joints Based on Creep Deformation

5.2.1. Knecht–Fox Model

5.2.2. Syed Model

5.3. Fatigue Life Prediction Models of Solder Joints Based on Fracture Mechanics

5.3.1. Paris Model

5.3.2. J-Integral Model

5.4. Fatigue Life Prediction Models of Solder Joints Based on Energy

5.4.1. Akay Model

5.4.2. Darveaux Model

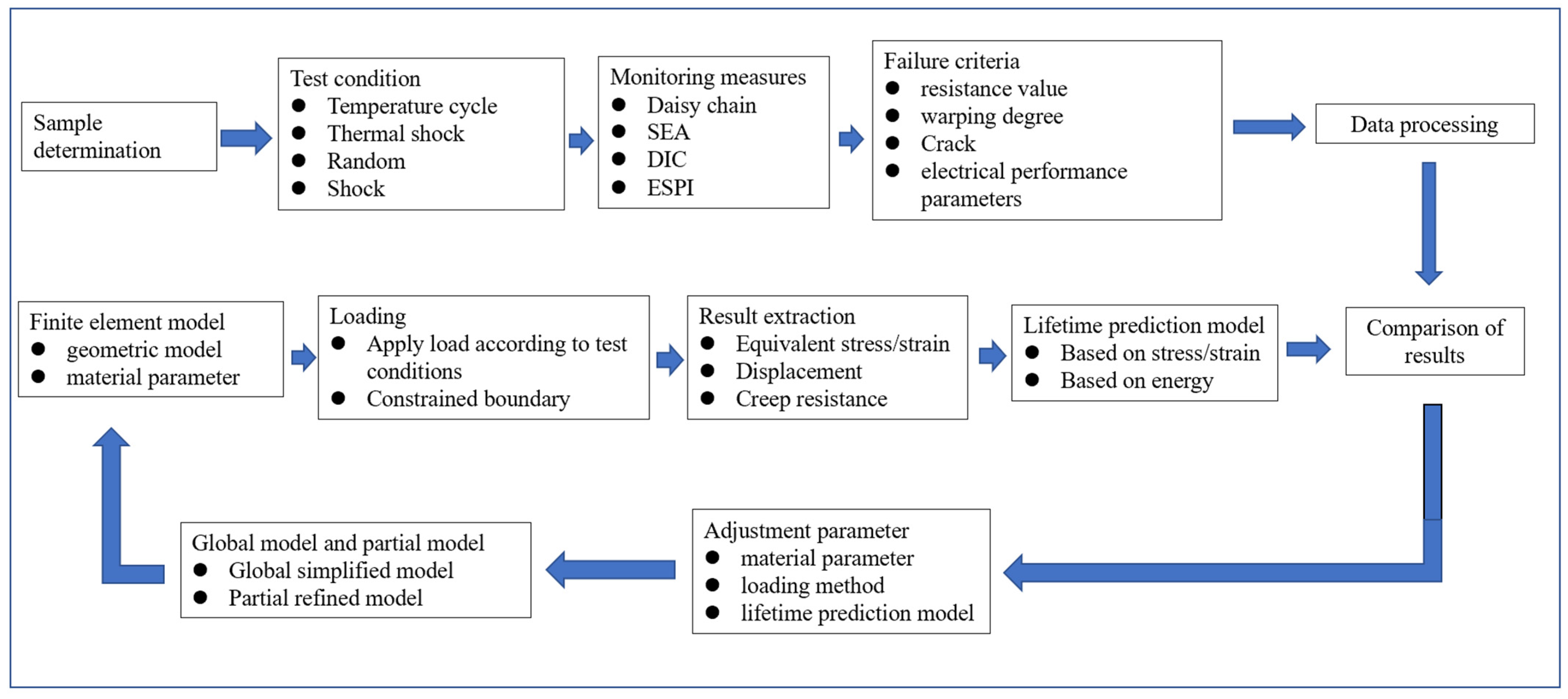

6. Studies on the Reliability of 3D Packaged Memory

6.1. The Reliability of PoP Memory under Thermal Stress

6.2. The Reliability of PoP Memory under Hygrothermal Stress

6.3. The Reliability of PoP Memory under Mechanical Stress

6.4. The Reliability of CoC Package Memory under Thermal Stress

6.5. The Reliability of CoC Package Memory under Hygrothermal Stress

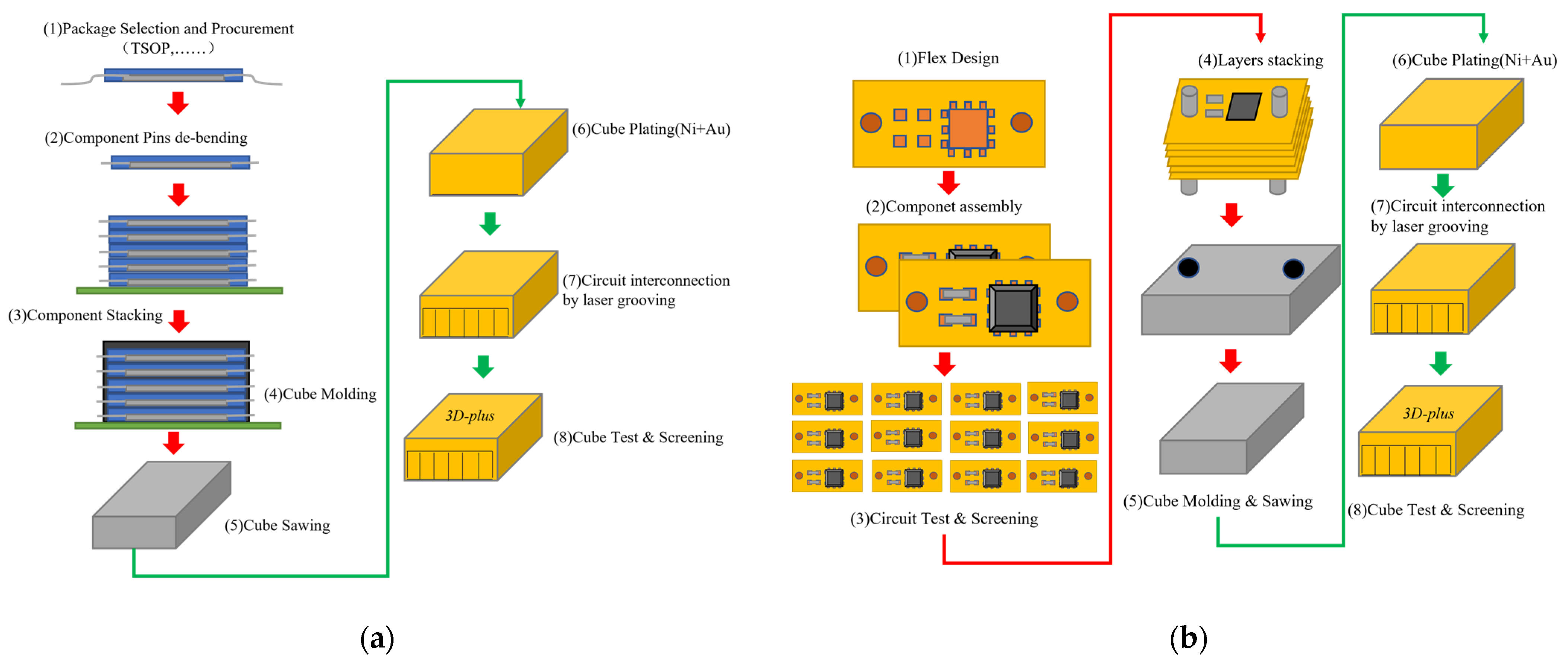

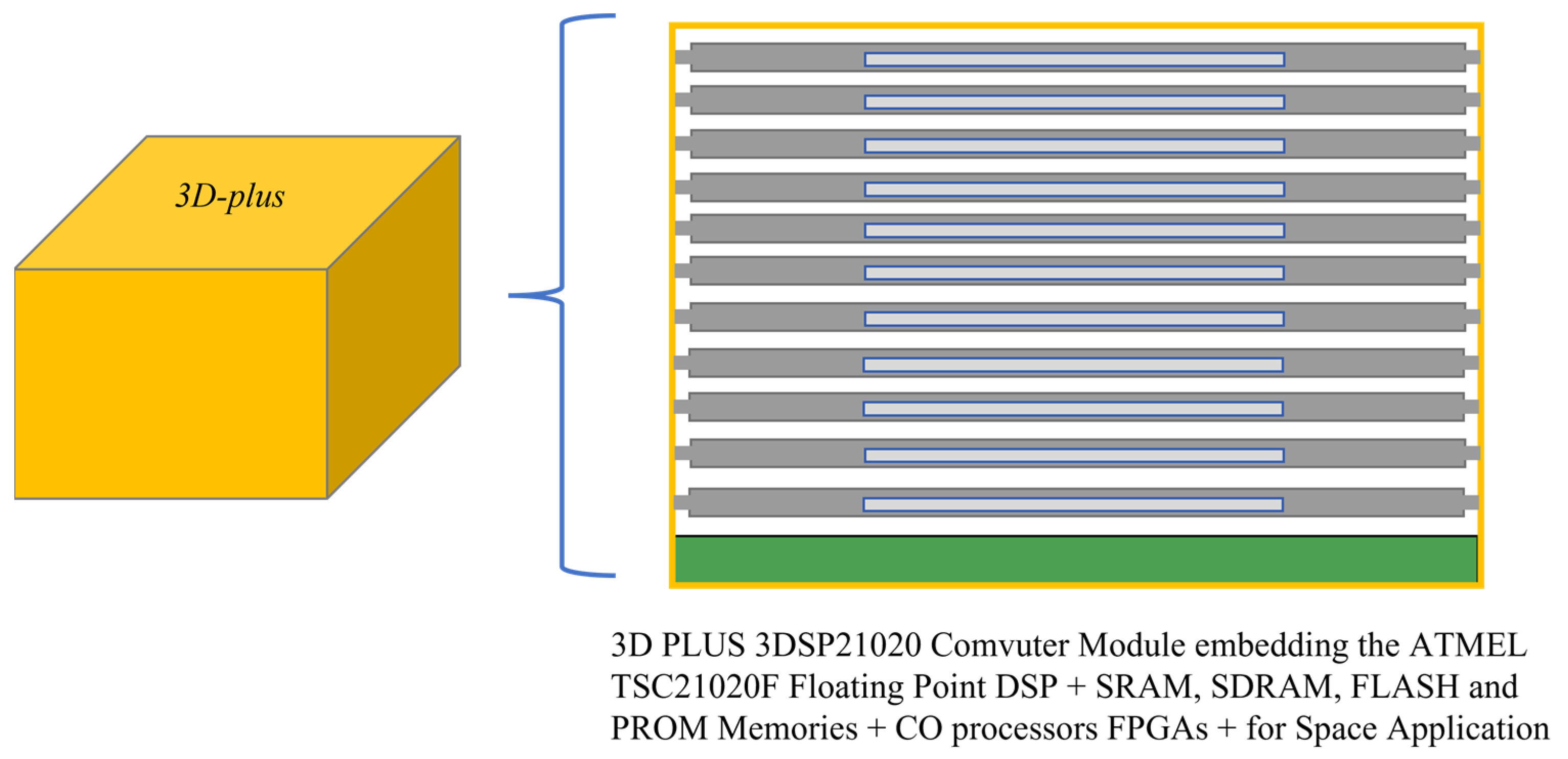

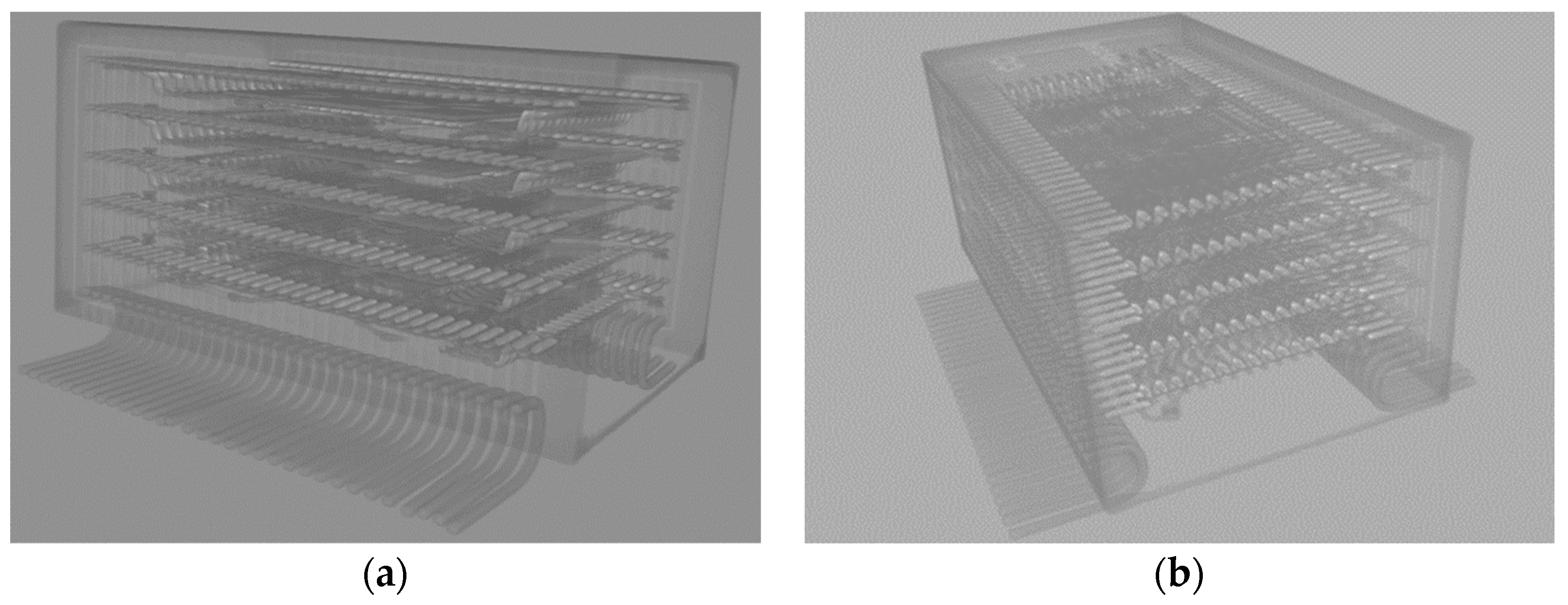

6.6. The Reliability of PiP Memory

6.7. Discussion of Typical Formulae for Predicting the Fatigue Life of Solder Joints

6.8. Current Reliability Research on 3D Packaging Memory under Multi-Stress Coupling

7. Discussion

8. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Yoshida, A.; Taniguchi, J.; Murata, K.; Kada, M.; Yamamoto, Y.; Takagi, Y.; Notomi, T.; Fujita, A. A study on package stacking process for package-on-package (PoP). In Proceedings of the 56th Electronic Components and Technology Conference 2006, San Diego, CA, USA, 30 May–02 June 2006; p. 6. [Google Scholar]

- Sun, P.; Leung, V.; Yang, D.; Lou, R.; Shi, D.; Chung, T. Development of a new package-on-package (PoP) structure for next-generation portable electronics. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 1957–1963. [Google Scholar]

- Eslampour, H.; Joshi, M.; Park, S.; Shin, H.; Chung, J. Advancements in Package-on-Package (PoP) technology, delivering performance, form factor & cost benefits in next generation Smartphone processors. In Proceedings of the 2013 IEEE 63rd Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013; pp. 1823–1828. [Google Scholar]

- Rochat, G. COB and COC for low cost and high density package. In Proceedings of the Seventeenth IEEE/CPMT International Electronics Manufacturing Technology Symposium ‘Manufacturing Technologies-Present and Future’, Austin, TX, USA, 2–4 October 1995; pp. 109–111. [Google Scholar]

- Umemoto, M.; Tanida, K.; Nemoto, Y.; Hoshino, M.; Kojima, K.; Shirai, Y.; Takahashi, K. High-performance vertical interconnection for high-density 3D chip stacking package. In Proceedings of the 2004 Proceedings 54th Electronic Components and Technology Conference, Las Vegas, NV, USA, 4 June 2004; pp. 616–623. [Google Scholar]

- Kawano, M.; Takahashi, N.; Kurita, Y.; Soejima, K.; Komuro, M.; Matsui, S. Three-dimensional packaging technology for stacked DRAM with 3-Gb/s data transfer. IEEE Trans. Electron. Devices 2008, 55, 1614–1620. [Google Scholar] [CrossRef]

- Fan, X. Wafer level packaging (WLP): Fan-in, fan-out and three-dimensional integration. In Proceedings of the 2010 11th International Thermal, Mechanical & Multi-Physics Simulation, and Experiments in Microelectronics and Microsystems (EuroSimE), Bordeaux, France, 26–28 April 2010; pp. 1–7. [Google Scholar]

- Garrou, P. Wafer level chip scale packaging (WL-CSP): An overview. IEEE Trans. Adv. Packag. 2000, 23, 198–205. [Google Scholar] [CrossRef]

- Fan, X.; Han, Q. Design and reliability in wafer level packaging. In Proceedings of the 2008 10th Electronics Packaging Technology Conference, Singapore, 9–12 December 2008; pp. 834–841. [Google Scholar]

- Motoyoshi, M. Through-silicon via (TSV). Proc. IEEE 2009, 97, 43–48. [Google Scholar] [CrossRef]

- Tummala, R.R. 3D system package architecture as alternative to 3D stacking of ICs with TSV at system level. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 3–4. [Google Scholar]

- Hummler, K.; Sapp, B.; Lloyd, J.R.; Kruger, S.; Olson, S.; Park, S.B.; Murray, B.; Jung, D.; Cain, S.; Park, A. TSV and Cu-Cu direct bond wafer and package-level reliability. In Proceedings of the 2013 IEEE 63rd Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013; pp. 41–48. [Google Scholar]

- Ivankovic, A.; Buisson, T.; Kumar, S.; Pizzagalli, A.; Azemar, J.; Beica, R. 2.5D Interposers and advanced organic substrates landscape: Technology and market trends. Int. Symp. Microelectron. 2015, 2015, 41–45. [Google Scholar] [CrossRef]

- Chen, Y.; Cheng, S.; Hu, D.; Tseng, T. Ultra-thin line embedded substrate manufacturing for 2.1D/2.5D SiP application. In Proceedings of the 2015 International Conference on Electronics Packaging and iMAPS All Asia Conference (ICEP-IAAC), Kyoto, Japan, 14–17 April 2015; pp. 166–169. [Google Scholar]

- Deng, Y.; Maly, W.P. Interconnect characteristics of 2.5-D system integration scheme. In Proceedings of the 2001 International Symposium on Physical Design, New York, NY, USA, 1–4 April 2001; pp. 171–175. [Google Scholar]

- Zheng, J.; Zhang, Z.; Chen, Y.; Shi, J. 3D stacked package technology and its application prospects. In Proceedings of the 2009 International Conference on New Trends in Information and Service Science, Beijing, China, 30 June–2 July 2009; pp. 528–533. [Google Scholar]

- Lim, S.K. Physical design for 3D system on package. IEEE Des. Test Comput. 2005, 22, 532–539. [Google Scholar]

- Ye, N.; Li, Q.; Zhang, H.; Ji, Z.; Yang, X.; Chiu, C.; Takiar, H. Challenges in assembly and reliability of thin NAND memory die. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1840–1846. [Google Scholar]

- Huang, H.; Micheloni, R. 3D multi-chip integration and packaging technology for NAND flash memories. In 3D Flash Memories; Springer: Berlin/Heidelberg, Germany, 2016; pp. 261–279. [Google Scholar]

- Kwak, H.; Ryu, S.; Cho, S.; Kim, J.; Yang, Y.; Kim, J. Non-destructive thickness characterisation of 3D multilayer semiconductor devices using optical spectral measurements and machine learning. Light Adv. Manuf. 2021, 2, 9–19. [Google Scholar] [CrossRef]

- Arreghini, A.; Delhougne, R.; Subirats, A.; Hikavyy, A.; Vecchio, E.; Sebaai, F.; Breuil, L.; Furnemont, A. First demonstration of SiGe channel in macaroni geometry for future 3D NAND. In Proceedings of the 2017 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–4. [Google Scholar]

- Sako, M.; Watanabe, Y.; Nakajima, T.; Sato, J.; Muraoka, K.; Fujiu, M.; Kono, F.; Nakagawa, M.; Masuda, M.; Kato, K. A low power 64 Gb MLC NAND-flash memory in 15 nm CMOS technology. IEEE J. Solid-State Circuit 2015, 51, 196–203. [Google Scholar]

- Yu, S.; Chen, P. Emerging memory technologies: Recent trends and prospects. IEEE Solid-State Circuits Mag. 2016, 8, 43–56. [Google Scholar] [CrossRef]

- Li, Y. 3D NAND memory and its application in solid-state drives: Architecture, reliability, flash management techniques, and current trends. IEEE Solid-State Circuits Mag. 2020, 12, 56–65. [Google Scholar] [CrossRef]

- Kim, S.S.; Yong, S.K.; Kim, W.; Kang, S.; Park, H.W.; Yoon, K.J.; Sheen, D.S.; Lee, S.; Hwang, C.S. Review of semiconductor flash memory devices for material and process issues. Adv. Mater. 2022; early view. [Google Scholar]

- Yang-Scharlotta, J.Y.; Guertin, S.M. Recent Advances in Commercial Memories and Potential Contribution to GN&C Miniaturation; NASA: Washington, DC, USA, 2016.

- Gendepujari, K.R. Cantilever Based Nonvolatile Memories: A Survey; Sardar Vallabhbhai National Institute of Technology, SURAT: Gujarat, India, 2020. [Google Scholar]

- Ishimaru, K. Challenges of Flash Memory for Next Decade. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–5. [Google Scholar]

- Choe, J. Memory Technology 2021: Trends & Challenges. In Proceedings of the 2021 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Dallas, TX, USA, 27–29 September 2021; pp. 111–115. [Google Scholar]

- Or-Bach, Z. Monolithic 3D Integration—An Update. In NANO-CHIPS 2030; Springer: Berlin/Heidelberg, Germany, 2020; pp. 117–125. [Google Scholar]

- Chinese Academy of Cyberspace Studies. The Development of Information Technology. In China Internet Development Report 2020: Blue Book for World Internet Conference; Springer: Berlin/Heidelberg, Germany, 2022; pp. 49–67. [Google Scholar]

- Choe, J. Comparison of Current 3D NAND Chip & Cell Architecture; Flash Memory Summit: Santa Clara, CA, USA, 2019. [Google Scholar]

- Lau, J.H. Semiconductor Advanced Packaging; Springer Nature: Berlin/Heidelberg, Germany, 2021; ISBN 9811613761. [Google Scholar]

- Lau, J.H. 3D IC Integration and Packaging; McGraw-Hill Education: New York, NY, USA, 2016; ISBN 0071848061. [Google Scholar]

- Zhong, Z.W. Wire bonding using copper wire. Microelectron. Int. 2009, 26, 10–16. [Google Scholar] [CrossRef]

- Lannon, J.; Gregory, C.; Lueck, M.; Huffman, A.; Temple, D. High density Cu-Cu interconnect bonding for 3-D integration. In Proceedings of the 2009 59th Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009; pp. 355–359. [Google Scholar]

- Schneider-Ramelow, M.; Ehrhardt, C. The reliability of wire bonding using Ag and Al. Microelectron. Reliab. 2016, 63, 336–341. [Google Scholar] [CrossRef]

- Carson, F.; Kim, Y. The development of a novel stacked package: Package in package. In Proceedings of the IEEE/CPMT/SEMI 29th International Electronics Manufacturing Technology Symposium, San Jose, CA, USA, 14–16 July 2004; pp. 91–96. [Google Scholar]

- Hsieh, M.; Kang, K.; Choi, H.; Kim, Y. Thin profile flip chip package-on-package development. In Proceedings of the 2016 11th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), Taipei, Taiwan, China, 26–29 October 2016; pp. 143–147. [Google Scholar]

- Lau, J.H.; Lau, J.H. Advanced Packaging Trends. In Semiconductor Advanced Packaging; Springer: Singapore, 2021; pp. 465–489. [Google Scholar]

- Hsieh, M. Advanced flip chip package on package technology for mobile applications. In Proceedings of the 2016 17th International Conference on Electronic Packaging Technology (ICEPT), Wuhan, China, 16–19 August 2016; pp. 486–491. [Google Scholar]

- Dreiza, M.; Kim, J.S.; Smith, L. Joint project for mechanical qualification of next generation high density package-on-package (PoP) with through mold via technology. In Proceedings of the 2009 European Microelectronics and Packaging Conference, Rimini, Italy, 15–18 June 2009; pp. 1–8. [Google Scholar]

- Yoshida, A.; Ishibashi, K. Design and stacking of an extremely thin chip-scale package. In Proceedings of the 53rd Electronic Components and Technology Conference, New Orleans, LA, USA, 27–30 May 2003; pp. 1095–1100. [Google Scholar]

- Lau, J.H. Heterogeneous integration of PoP. In Heterogeneous Integrations; Springer: Berlin/Heidelberg, Germany, 2019; pp. 205–219. [Google Scholar]

- Tzeng, Y.L.; Kao, N.; Chen, E.; Lai, J.Y.; Wang, Y.P.; Hsiao, C.S. Warpage and stress characteristic analyses on package-on-package (PoP) structure. In Proceedings of the 2007 9th Electronics Packaging Technology Conference, Singapore, 10–12 December 2007; pp. 482–487. [Google Scholar]

- Sun, W.; Zhu, W.H.; Wang, C.K.; Sun, A.Y.; Tan, H.B. Warpage simulation and DOE analysis with application in package-on-package development. In Proceedings of the EuroSimE 2008-International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Micro-Systems, Freiburg, Germany, 20–23 April 2008; pp. 1–8. [Google Scholar]

- Dreiza, M.; Yoshida, A.; Ishibashi, K.; Maeda, T. High density PoP (package-on-package) and package stacking development. In Proceedings of the 2007 Proceedings 57th Electronic Components and Technology Conference, Sparks, NV, USA, 29 May–1 June 2007; pp. 1397–1402. [Google Scholar]

- Vijayanath, V. Assembly Process Development for Fine Pitch (0.4 Mm) Package-on-Package Devices in a Lead-Free Assembly Environment; Department of Systems Science and Industrial Engineering, Thomas, J. Watson School of Engineering, State University of New York at Binghamton: Binghamton, NY, USA, 2010; ISBN 1124247025. [Google Scholar]

- Geczy, A.; Illyefalvi-Vitez, Z. Package–on–package–review on a promising packaging technology. In Proceedings of the 33rd International Spring Seminar on Electronics Technology, ISSE 2010, Warsaw, Poland, 12–16 May 2010; pp. 117–122. [Google Scholar]

- Zwenger, C.; Smith, L.; Kim, J. Next Generation Package-on-Package (PoP) Platform with Through Mold Via (TMV™) Interconnection Technology. In Proceedings of the IMAPS Device Packaging Conference, Scottsdale, AZ, USA, 10–12 March 2009. [Google Scholar]

- Rao, V.S.; Chong, C.T.; Ho, D.; Zhi, D.M.; Choong, C.S.; Ps, S.L.; Ismael, D.; Liang, Y.Y. Process and reliability of large fan-out wafer level package based package-on-package. In Proceedings of the 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 615–622. [Google Scholar]

- Faure, C.; Val, A.; Couderc, P.; Chandler, N.; Preziosi, E.; Ousten, Y.; Levrier, B. 3D system-in-package: Technology improvements for volume manufacturing. In Proceedings of the IMAPS MicroTech 2006, Cambridge, UK, 7–8 March 2006. [Google Scholar]

- Plante, J.; Shaw, H. Evaluation of 3D plus packaging test structures for NASA Goddard Space Flight Center. In Proceedings of the European Space Components Conference, ESCCON 2002, Toulouse, France, 24–27 September 2002; p. 213. [Google Scholar]

- Deterre, M. Toward an Energy Harvester for Leadless Pacemakers. Ph.D. Thesis, Université Paris-Sud, Paris, France, 2013. [Google Scholar]

- Strickland, M.; Johnson, R.W.; Gerke, D. 3-D Packaging: A Technology Review; Auburn University: Auburn, AL, USA, 23 June 2005. [Google Scholar]

- Berthet, P.; de Saint Roman, D. An efficient means to meet the challenges of very high density packaging in space applications. In Proceedings of the 2003 IEEE Aerospace Conference Proceedings, Big Sky, MT, USA, 8–15 March 2003; pp. 6–2535. [Google Scholar]

- Val, C.; Vassal, M.; Lignier, O.; Mardiguian, M. www.3d-plus.com. Fr. Pat. 1990, 90, 15473. [Google Scholar]

- Carson, J.C. Advances in Chip Level Packaging; Irvine Sensors Corporation: Costa Mesa, CA, USA, 2002; Volume 36. [Google Scholar]

- Martin, P.L. Electronic Failure Analysis Handbook: Techniques and Applications for Electronic and Electrical Packages, Components, and Assemblies; McGraw-Hill Education: New York, NY, USA, 1999; ISBN 0070410445. [Google Scholar]

- Kinjo, N.; Ogata, M.; Nishi, K.; Kaneda, A.; Dušek, K. Epoxy molding compounds as encapsulation materials for microelectronic devices. In Speciality Polymers/Polymer Physics; Springer: Berlin/Heidelberg, Germany, 1989; Volume 88, pp. 1–48. [Google Scholar]

- Chen, Y.; Li, P. The “popcorn effect” of plastic encapsulated microelectronic devices and the typical cases study. In Proceedings of the 2011 International Conference on Quality, Reliability, Risk, Maintenance, and Safety Engineering, Xi’an, China, 17–19 June 2011; pp. 482–485. [Google Scholar]

- Li, X.; Sun, R.; Wang, Y. A review of typical thermal fatigue failure models for solder joints of electronic components. IOP Conf. Ser. Mater. Sci. Eng. 2017, 242, 12103. [Google Scholar] [CrossRef]

- Weronski, A. Thermal Fatigue of Metals; CRC Press: Boca Raton, FL, USA, 1991; ISBN 0429178085. [Google Scholar]

- Clarke, N.P.; Wolff, W.M.; Gokelman, J.J.; Von Gierke, H.E.; Vo, H.H.F. Simulation of aerospace flight acceleration and dynamic pressure environments for biodynamics research. J. Spacecr. Rocket. 1967, 4, 751–757. [Google Scholar] [CrossRef] [Green Version]

- Xia, J.; Li, G.; Zhou, B.; Cheng, L. PoP assembly reliability test and assessment under random vibration loading. In Proceedings of the 2016 17th International Conference on Electronic Packaging Technology (ICEPT), Wuhan, China, 16–19 August 2016; pp. 406–410. [Google Scholar]

- Ohring, M. Reliability and Failure of Electronic Materials and Devices; Elsevier: Amsterdam, The Netherlands, 1998; ISBN 0080516076. [Google Scholar]

- Lall, P.; Pecht, M.; Hakim, E.B. Influence of Temperature on Microelectronics and System Reliability: A Physics of Failure Approach; CRC Press: Boca Raton, FL, USA, 1997; ISBN 0849394503. [Google Scholar]

- Lee, M.C.; Peppas, N.A. Models of moisture transport and moisture-induced stresses in epoxy composites. J. Compos. Mater. 1993, 27, 1146–1171. [Google Scholar]

- Tay, A.A.; Lin, T. Moisture diffusion and heat transfer in plastic IC packages. IEEE Trans. Compon. Packag. Manuf. Technol. Part A 1996, 19, 186–193. [Google Scholar] [CrossRef]

- Fan, X.; Zhao, J. Moisture diffusion and integrated stress analysis in encapsulated microelectronics devices. In Proceedings of the 2011 12th International Conference on Thermal, Mechanical & Multi-Physics Simulation and Experiments in Microelectronics and Microsystems, Linz, Austria, 18–20 April 2011; pp. 1–8. [Google Scholar]

- Paul, A.; Laurila, T.; Vuorinen, V.; Divinski, S.V. Fick’s laws of diffusion. In Thermodynamics, Diffusion and the Kirkendall Effect in Solids; Springer: Berlin/Heidelberg, Germany, 2014; pp. 115–139. [Google Scholar]

- Fan, X.; Suhir, E. Moisture Sensitivity of Plastic Packages of IC Devices; Springer: Berlin/Heidelberg, Germany, 2010; ISBN 1441957197. [Google Scholar]

- Wong, E.; Rajoo, R. Moisture absorption and diffusion characterisation of packaging materials—Advanced treatment. Microelectron. Reliab. 2003, 43, 2087–2096. [Google Scholar] [CrossRef]

- Wong, E.H.; Teo, Y.C.; Lim, T.B. Moisture diffusion and vapour pressure modeling of IC packaging. In Proceedings of the 1998 48th Electronic Components and Technology Conference, Seattle, WA, USA, 25–28 May 1998; pp. 1372–1378. [Google Scholar]

- Stellrecht, E.; Han, B.; Pecht, M.G. Characterization of hygroscopic swelling behavior of mold compounds and plastic packages. IEEE Trans. Compon. Packag. Technol. 2004, 27, 499–506. [Google Scholar] [CrossRef]

- Tee, T.Y.; Ng, H.S. Whole field vapor pressure modeling of QFN during reflow with coupled hygro-mechanical and thermo-mechanical stresses. In Proceedings of the 52nd Electronic Components and Technology Conference 2002, San Diego, CA, USA, 28–31 May 2002; pp. 1552–1559. [Google Scholar]

- Khoo, C.; Liu, J. Moisture sorption in some popular conductive adhesives. Circuit World 1996, 22, 9–15. [Google Scholar]

- Luo, S.; Wong, C.P.; Leisen, J. Fundamental study on moisture absorption in epoxy for electronic application. In Proceedings of the International Symposium on Advanced Packaging Materials Processes, Properties and Interfaces, Braselton, GA, USA, 11–14 March 2001; pp. 293–298. [Google Scholar]

- Wong, E.H.; Koh, S.W.; Rajoo, R.; Lim, T.B. Underfill swelling and temperature-humidity performance of flip chip PBGA package. In Proceedings of the 3rd Electronics Packaging Technology Conference (EPTC 2000), Singapore, 7 December 2000; pp. 258–262. [Google Scholar]

- Boley, B.A.; Weiner, J.H. Theory of Thermal Stresses; Courier Corporation: Chelmsford, MA, USA, 2012; ISBN 0486143864. [Google Scholar]

- Wang, X.; Shao, M. Theory and Numerical Methods of Finite Element Method; Tsinghua University Press: Beijing, China, 1997. [Google Scholar]

- Fu, Z.; He, J. Modal Analysis; Elsevier: Amsterdam, The Netherlands, 2001; ISBN 0080511783. [Google Scholar]

- Newland, D.E. An Introduction to Random Vibrations, Spectral & Wavelet Analysis; Courier Corporation: Chelmsford, MA, USA, 2012; ISBN 0486136965. [Google Scholar]

- Soong, T.T.; Grigoriu, M. Random vibration of mechanical and structural systems. NASA STI/Recon Tech. Rep. A 1993, 93, 14690. [Google Scholar]

- Lalanne, C. Random Vibration; CRC Press: Boca Raton, FL, USA, 2020; ISBN 0367812096. [Google Scholar]

- Henderson, G.R.; Piersol, A.G. Fatigue damage related descriptor for random vibration test environments. Sound Vib. 1995, 29, 20–25. [Google Scholar]

- Lalanne, C. Mechanical Vibration and Shock Analysis, Sinusoidal Vibration; John Wiley & Sons: Hoboken, NJ, USA, 2014; ISBN 1848216440. [Google Scholar]

- Cheng, H.; Cheng, H.; Lu, S.; Juang, J.; Chen, W. Drop impact reliability analysis of 3-D chip-on-chip packaging: Numerical modeling and experimental validation. IEEE Trans. Device Mater. Reliab. 2013, 14, 499–511. [Google Scholar] [CrossRef]

- Syed, A.R. Thermal fatigue reliability enhancement of plastic ball grid array (PBGA) packages. In Proceedings of the 1996 Proceedings 46th Electronic Components and Technology Conference, Orlando, FL, USA, 28–31 May 1996; pp. 1211–1216. [Google Scholar]

- Qi, H.; Osterman, M.; Pecht, M. A rapid life-prediction approach for PBGA solder joints under combined thermal cycling and vibration loading conditions. IEEE Trans. Compon. Packag. Technol. 2009, 32, 283–292. [Google Scholar] [CrossRef]

- Yu, D.; Al-Yafawi, A.; Nguyen, T.T.; Park, S.; Chung, S. High-cycle fatigue life prediction for Pb-free BGA under random vibration loading. Microelectron. Reliab. 2011, 51, 649–656. [Google Scholar] [CrossRef]

- Ridout, S.; Bailey, C. Review of methods to predict solder joint reliability under thermo-mechanical cycling. Fatigue Fract. Eng. Mater. Struct. 2007, 30, 400–412. [Google Scholar] [CrossRef]

- Madenci, E.; Guven, I.; Kilic, B. Fatigue Life Prediction of Solder Joints in Electronic Packages with Ansys®; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2002; ISBN 1402073305. [Google Scholar]

- Dudek, R. Characterization and modelling of solder joint reliability. In Mechanics of Microelectronics; Springer: Berlin/Heidelberg, Germany, 2006; pp. 377–468. [Google Scholar]

- Lee, W.W.; Nguyen, L.T.; Selvaduray, G.S. Solder joint fatigue models: Review and applicability to chip scale packages. Microelectron. Reliab. 2000, 40, 231–244. [Google Scholar] [CrossRef]

- Su, S.; Akkara, F.J.; Thaper, R.; Alkhazali, A.; Hamasha, M.; Hamasha, S. A state-of-the-art review of fatigue life prediction models for solder joint. J. Electron. Packag. 2019, 141, 040802. [Google Scholar] [CrossRef]

- Cui, H. Accelerated temperature cycle test and Coffin-Manson model for electronic packaging. In Proceedings of the Annual Reliability and Maintainability Symposium, Alexandria, VA, USA, 24–27 January 2005; pp. 556–560. [Google Scholar]

- Chauhan, P.; Osterman, M.; Lee, S.R.; Pecht, M. Critical review of the Engelmaier model for solder joint creep fatigue reliability. IEEE Trans. Compon. Packag. Technol. 2009, 32, 693–700. [Google Scholar] [CrossRef]

- Zhang, L.; Han, J.; He, C.; Guo, Y. Reliability behavior of lead-free solder joints in electronic components. J. Mater. Sci. Mater. Electron. 2013, 24, 172–190. [Google Scholar] [CrossRef]

- Osterman, M.; Pecht, M. Strain range fatigue life assessment of lead-free solder interconnects subject to temperature cycle loading. Solder. Surf. Mt. Technol. 2007, 19, 12–17. [Google Scholar] [CrossRef]

- Salmela, O.; Andersson, K.; Perttula, A.; Särkkä, J.; Tammenmaa, M. Modified Engelmaier’s model taking account of different stress levels. Microelectron. Reliab. 2008, 48, 773–780. [Google Scholar] [CrossRef]

- Che, F.X.; Pang, J.H. Fatigue reliability analysis of Sn–Ag–Cu solder joints subject to thermal cycling. IEEE Trans. Device Mater. Reliab. 2012, 13, 36–49. [Google Scholar] [CrossRef]

- Ramachandran, V.; Wu, K.C.; Chiang, K.N. Overview study of solder joint reliablity due to creep deformation. J. Mech. 2018, 34, 637–643. [Google Scholar] [CrossRef]

- Wong, E.; Van Driel, W.D.; Dasgupta, A.; Pecht, M. Creep fatigue models of solder joints: A critical review. Microelectron. Reliab. 2016, 59, 1–12. [Google Scholar] [CrossRef]

- Shao, J.; Zeng, C.; Wang, Y. Research progress on physics-of-failure based fatigue stress-damage model of solder joints in electronic packing. In Proceedings of the 2010 Prognostics and System Health Management Conference, Macao, China, 12–14 January 2010; pp. 1–6. [Google Scholar]

- Li, X.; Wang, Z. Thermo-fatigue life evaluation of SnAgCu solder joints in flip chip assemblies. J. Mater. Process. Technol. 2007, 183, 6–12. [Google Scholar] [CrossRef]

- Syed, A. Updated life prediction models for solder joints with removal of modeling assumptions and effect of constitutive equations. In Proceedings of the EuroSime 2006-7th International Conference on Thermal, Mechanical and Multiphysics Simulation and Experiments in Micro-Electronics and Micro-Systems, Como, Italy, 24–26 April 2006; pp. 1–9. [Google Scholar]

- Qiu, B.; Xiong, J.; Wang, H.; Zhou, S.; Yang, X.; Lin, Z.; Liu, M.; Cai, N. Survey on Fatigue Life Prediction of BGA Solder Joints. Electronics 2022, 11, 542. [Google Scholar] [CrossRef]

- Zhu, Q.S.; Gao, F.; Ma, H.C.; Liu, Z.Q.; Guo, J.D.; Zhang, L. Failure behavior of flip chip solder joint under coupling condition of thermal cycling and electrical current. J. Mater. Sci. Mater. Electron. 2018, 29, 5025–5033. [Google Scholar] [CrossRef]

- Qu, X.; Chen, Z.; Qi, B.; Lee, T.; Wang, J. Board level drop test and simulation of leaded and lead-free BGA-PCB assembly. Microelectron. Reliab. 2007, 47, 2197–2204. [Google Scholar] [CrossRef]

- Luan, J.; Tee, T.Y.; Pek, E.; Lim, C.T.; Zhong, Z.; Zhou, J. Advanced numerical and experimental techniques for analysis of dynamic responses and solder joint reliability during drop impact. IEEE Trans. Compon. Packag. Technol. 2006, 29, 449–456. [Google Scholar] [CrossRef]

- Lee, H. Finite Element Simulations with ANSYS Workbench 18; SDC Publications: Mission, KS, USA, 2018; ISBN 1630571733. [Google Scholar]

- Börgesson, L. Abaqus. In Developments in Geotechnical Engineering; Elsevier: Amsterdam, The Netherlands, 1996; Volume 79, pp. 565–570. ISBN 0165-1250. [Google Scholar]

- Stolarski, T.; Nakasone, Y.; Yoshimoto, S. Engineering Analysis with ANSYS Software; Butterworth-Heinemann: Oxford, UK, 2018; ISBN 0081021658. [Google Scholar]

- Macneal, R.H.; Mccormick, C.W. The NASTRAN computer program for structural analysis. Comput. Struct. 1971, 1, 389–412. [Google Scholar] [CrossRef]

- Zhang, Z.; Wang, X.; Ren, H.; Jia, S.; Yang, H. Simulation study on thermo-fatigue failure behavior of solder joints in package-on-package structure. Microelectron. Reliab. 2017, 75, 127–134. [Google Scholar] [CrossRef]

- Wang, Y. Research on the Reliability of Package-on-Package in Different Temperature Environ; Jiangsu University: Zhenjiang, China, 2016. [Google Scholar]

- Wang, H.; Wang, B.; Ran, H.; Yan, Z.; Lu, F.; Xie, H. Warpage Behaviors and Reliability in TMV PoP. Semicond. Technol. 2018, 43, 462–467. [Google Scholar]

- Tang, X. Research on Pop Stacked Package Realiability under Thermal Shock Load; Jiangsu University: Oxford, UK, 2015. [Google Scholar]

- Chen, Z.; Jung, B.Y.; Lim, S.P.S.; Velez, D.S.; Ho, D.S.W.; Zhang, X. Thermo-mechanical reliability study on Package on Package (PoP) with Embedded Wafer Level Package (eWLP). In Proceedings of the 2014 IEEE 16th Electronics Packaging Technology Conference (EPTC), Singapore, 3–5 December 2014; pp. 812–816. [Google Scholar]

- Liu, H.; Yang, S.; Li, G. Effects of Hygro-Thermal Stress on the Reliability of Package-on-Package. Semicond. Technol. 2010, 35, 1054–1058. [Google Scholar]

- Liu, H.; Yang, S. Thermo-mechanical reliability analysis of package-on-package assembly. In Proceedings of the 2011 International Conference on Quality, Reliability, Risk, Maintenance, and Safety Engineering, Xi’an, China, 17–19 June 2011; pp. 203–207. [Google Scholar]

- Guedon-Gracia, A.; Feng, W.; Delétage, J.; Verdier, F.; Fremont, H. Moisture induced effects in PoP. In Proceedings of the EuroSimE 2009—10th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems, Delft, The Netherlands, 26–29 April 2009; pp. 1–6. [Google Scholar]

- Chen, Z.; Chong, S.C.; Zheng, B.; Jung, B.Y.; Chai, T.C.; Zhang, X. Reliability study on through mold via (TMV) for 3D microelectronic packaging under thermal and moisture loadings. In Proceedings of the 2013 IEEE 15th Electronics Packaging Technology Conference (EPTC 2013), Singapore, 11–13 December 2013; pp. 524–529. [Google Scholar]

- Xia, J.; Li, G.; Li, B.; Cheng, L. Optimal design for vibration reliability of package-on-package assembly using FEA and taguchi method. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 1482–1487. [Google Scholar]

- Yang, B.; Li, D.; Yang, H.; Hu, Y.; Yang, P. Vibrational fatigue and reliability of package-on-package stacked chip assembly. Microelectron. J. 2019, 92, 104609. [Google Scholar] [CrossRef]

- Tang, H.; Wu, Z.; Lui, Z. Random vibration simulation and analysis of PoP solder joints with different structure parameters. In Proceedings of the 2012 13th International Conference on Electronic Packaging Technology & High Density Packaging, Guilin, China, 13–16 August 2012; pp. 1168–1171. [Google Scholar]

- Liu, S. Study on the Viscoplasticity of Sn3.0Ag0.5Cu and Reliability of the PoP Package under Thermal-Vibration Load; Taiyuan University of Science and Technology: Taiyuan, China, 2021. [Google Scholar]

- Fan, Z. Research on Reliability of Board Level Package-on-Package in Drop Impact. South China University of Technology. In Proceedings of the 2010 11th International Conference on Electronic Packaging Technology & High Density Packaging, Xi’an, China, 16–19 August 2010. [Google Scholar]

- Yao, X.; Ren, H.; Fan, H.; Zhang, X. Study on dynamic property of the PoP packages under drop impact. Sci. Sin. Phys. Mech. Astron. 2013, 43, 289–296. [Google Scholar]

- Zhang, L.; Long, W.; Zhong, S. Effect of Thermal Cyclic Loading on Stress-Strain Response and Fatigue Life of 3D Chip Stacking Structure. Chin. J. Mech. Eng. 2021, 34, 115. [Google Scholar] [CrossRef]

- Jiang, T.; Wu, C.; Su, P.; Chia, P.; Li, L.; Son, H.; Suh, M.; Kim, N.; Im, J.; Huang, R. Effect of high temperature storage on the stress and reliability of 3D stacked chip. In Proceedings of the 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 1122–1127. [Google Scholar]

- Tsai, H.; Kuo, C. Thermal stress and failure location analysis for through silicon via in 3D integration. J. Mech. 2016, 32, 47–53. [Google Scholar] [CrossRef]

- Yuwen, H.; Qin, H.; Zhou, M.; Zhang, X. The interfacial thermo-mechanical reliability of 3D memory-chip stacking with through silicon via array. In Proceedings of the 2015 16th International Conference on Electronic Packaging Technology (ICEPT), Changsha, China, 11–14 August 2015; pp. 568–573. [Google Scholar]

- Zhang, Z.; Deng, Y.; Liu, Y.; Jin, Y. Reliability simulation of metal bump in a three-dimensional chip stacking structure. In Proceedings of the 2010 11th International Conference on Electronic Packaging Technology & High Density Packaging, Xi’an, China, 16–19 August 2010; pp. 1218–1220. [Google Scholar]

- Tang, Y.; Liao, X.; Huang, J.; Wu, Z.; Liu, G. Reliability of the Stacked Dices Package under the Hygrothermal Environment. Semicond. Technol. 2014, 39, 539–544. [Google Scholar]

- Zhu, W.; Lai, P.; Yang, S. Effect of hygro-thermo-mechanical stress on reliability of stacked die package. In Proceedings of the 2011 International Symposium on Advanced Packaging Materials (APM), Xiamen, China, 25–28 October 2011; pp. 204–208. [Google Scholar]

- Hua, Z.K.; Li, C.Y.; Luo, Y.X.; Cao, L.Q.; Zhang, J.H. FEM analysis of moisture distribution in stacked die package. In Proceedings of the 2007 8th International Conference on Electronic Packaging Technology, Shanghai, China, 14–17 August 2007; pp. 1–4. [Google Scholar]

- Yan, A.; Qin, L.; Kang, X. Effects of moisture diffusion and hygrothermal stress on reliability of SCSP. Electron. Compon. Mater. 2008, 27, 69–73. [Google Scholar]

- Wang, J.; Park, S. Non-linear finite element analysis on stacked die package subjected to integrated vapor-hygro-thermal-mechanical stress. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1394–1401. [Google Scholar]

- Lv, Q. Research on Reliability of 3D-Plus Memory Stacks on PCB. Electron. Process Technol. 2016, 37, 336–338. [Google Scholar]

- Bao, N.; Wang, C.J.; Zhu, L.; Song, S.G. Effects of different solder alloys on reliability of 3D PLUS solder joint. Adv. Mater. Res. 2011, 314–316, 1038–1042. [Google Scholar] [CrossRef]

- Zhou, S.; Lin, Z.; Qiu, B.; Wang, H.; Xiong, J.; He, C.; Zhou, B.; Pan, Y.; Huang, R.; Bao, Y. Evaluation of Solder Joint Reliability in 3D Packaging Memory Devices under Thermal Shock. Electronics 2022, 11, 2556. [Google Scholar] [CrossRef]

- Dargnies, T.; Herath, J.; Ng, T.; Val, C.; Goupy, J.F.; David, J.P.; Engineer, S.E. Radiation tolerant and intelligent memory for space. In Proceedings of the MAPLD International Conference, Washington, DC, USA, 7–9 September 2005. [Google Scholar]

- Fan, Z.; Chen, X.; Jiang, Y.; Li, X.; Zhang, S.; Wang, Y. Effects of multi-cracks and thermal-mechanical coupled load on the TSV reliability. Microelectron. Reliab. 2022, 131, 114499. [Google Scholar] [CrossRef]

- Han, L.; Wang, H.; Huang, C.; Li, W.; Cai, J. 3D Package CSP Solder Joints Morphological Parameters Sensitivity Analysis and Optimization in Temperature-vibration Coupling Environment. In Proceedings of the 2020 21st International Conference on Electronic Packaging Technology (ICEPT), Guangzhou, China, 12–15 August 2020. [Google Scholar]

- Jia, S.; Sheng, S.; Qi, D.; Peng, Z.; Xiang, Y. Electric-thermo-structural coupling analysis of through silicon via in 3D stacked packaging structure. Electron. Compon. Mater. 2019, 38, 42–47. [Google Scholar]

- Zhao, T.; Wei, H.; Ge, H. The Stress Analysis of Moisture-Thermal Coupling Based on an Advanced 3D Packaging. In Proceedings of the 2022 7th International Conference on Integrated Circuits and Microsystems (ICICM), Xi′an, China, 28–31 October 2022. [Google Scholar]

- Rai, S.; Talawar, B. Nonvolatile Memory Technologies: Characteristics, Deployment, and Research Challenges. In Frontiers of Quality Electronic Design (QED); Springer: Cham, Switzerland, 2023; pp. 137–173. [Google Scholar]

- Zhao, W. Editorial for the Special Issue on Advanced Interconnect and Packaging. Micromachines 2023, 14, 171. [Google Scholar] [CrossRef]

- Khakifirooz, A.; Anaya, E.; Balasubrahrmanyam, S.; Bennett, G.; Castro, D.; Egler, J.; Fan, K.; Ferdous, R.; Ganapathi, K.; Guzman, O. A 1.67 Tb, 5b/Cell Flash Memory Fabricated in 192-Layer Floating Gate 3D-NAND Technology and Featuring a 23.3 Gb/mm2 Bit Density. In Proceedings of the 2023 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2023; pp. 27–29. [Google Scholar]

| No. | Test Items | Test Method | Remarks |

|---|---|---|---|

| 1 | Thermal cycles under vacuum | 10−6 Torr 10 Cycles −40 °C/+70 °C, 2 °C/min, 1 h par palier | / |

| 2 | Electrical tests | Electrical tests at −55 °C/+25 °C/+125 °C | / |

| 3 | Thermal cycles | 500 cycles −55 °C/+125 °C 10 °C/mn, 15 mn par palier | External visual inspection and electrical tests −55 °C/+25 °C/+125 °C at 100, 300, and 500 cycles |

| 4 | Temperature and humidity under bias | 1000 h +85 °C and 85% RH | External visual inspection and electrical tests −55 °C/+25 °C/+125 °C at 240, 500, and 1000 h |

| 5 | Life test or high-temperature storage | 2000 h +125 °C | External visual inspection and electrical tests −55 °C/+25 °C/+125 °C at 500, 1000, and 2000 h |

| 6 | Power cycling | 30,000× ON/OFF 120 s ON (+110 °C) 60 s OFF (+40 °C) | External visual inspection and electrical tests −55 °C/+25 °C/+125 °C at 15 K and 30 K O/O cycles |

| No. | Test Items | Test Method | Remarks |

|---|---|---|---|

| 1 | Thermal conditioning | +125 °C, 48 h | / |

| 2 | Voltage conditioning | +125 °C, 320 h | / |

| 3 | Thermal characterization | 14 steps of 20 °C between −55 °C to 125 °C | / |

| 4 | Temperature and humidity under bias | 620 h +85 °C and 85% RH | C-SAM and X-ray |

| 5 | Mechanical shock | MIL-STD-883 Method 2002 200 G, 0.5 ms | / |

| 6 | Sine vibration | MIL-STD-202 Condition A 10 G to 22.5 G | / |

| 7 | Random vibration | MIL-STD-883 Method 2026 Condition E (16.4 G) Condition B (7.3 G) | / |

| Typical Environmental Stress | Test Item | Typical Failure Mode |

|---|---|---|

| Temperature stress | High temperature | Functional performance failure, material degradation. |

| Low temperature | Functional performance failure, material degradation. | |

| Thermal shock | Functional performance failure, mark shedding, shell coating fading, delamination. | |

| Temperature cycling | Functional performance failure, mark shedding, shell coating fading, delamination. | |

| Hygrothermal stress | Steady damp heat | Mark shedding, corrosion, functional performance failure, delamination, etc. |

| Pressure cooker | Mark shedding, pin breakage, internal filler precipitation, corrosion, functional performance failure, delamination, etc. | |

| Mechanical stress | Shock | Pin fracture or crack, ceramic body fracture or crack, cover plate leakage, glass insulator crack, bonding wire fracture or collapse, etc. |

| Vibration | Pin fracture, ceramic body fracture or crack, cover plate leakage, glass insulator crack, bonding wire fracture or collapse, etc. | |

| Constant acceleration | Functional performance failure, chip detachment, bonding wire lead detachment or collapse, cover plate leakage, shell fracture or cracking, etc. |

| Characteristic | Heat Diffusion | Research Conclusion |

|---|---|---|

| Variable | Temperature | Relative humidity (W) |

| Conductivity | λ (W·m−1·K−1) | D·Csat (kg·s−1·m−1) |

| Specific heat capacity | c (J·kg−1·K−1) | Csat (kg·m−3) |

| Test Type | Test Items | Typical Conditions | Purpose |

|---|---|---|---|

| Thermal test | Temperature cycling | Method 1010 test condition C −65–+150 °C, Transfer time: 1 min, dwell time: 10 min | This test is conducted to determine the resistance of a component to high- and low-temperature extremes and the effect of alternate exposures to these extremes. |

| Thermal shock | Method 1011 test condition C −65–+150 °C, Transfer time: 10 s, dwell time: 2 min | The purpose of this test is to determine the resistance of the component to sudden exposure to extreme changes in temperature and the effect of alternate exposures to these extremes. | |

| Mechanical test | Random vibration | Method 2026 test condition E 20 (m/s2)2/Hz, 169.1 m/s2 | This test is conducted to determine the ability of the microcircuit to withstand the dynamic stress exerted by random vibration applied between upper and lower frequency limits in order to simulate the vibrations experienced in various service field environments. |

| Mechanical shock | Method 2002 test condition D 49,000 m/s2, 0.3 ms | The shock test is intended to determine the suitability of devices for use in electronic equipment. They may be subjected to moderately severe shocks as a result of suddenly applied forces or abrupt changes in motion caused by rough handling, transportation, or field operations. | |

| Humidity test | Moisture resistance | Method 1004 test 80–100% RH, 10 continuous cycles | The moisture resistance test is performed for the purpose of rapidly evaluating the resistance of component parts and constituent materials to the deteriorative effects of high-humidity and -heat conditions typical of tropical environments |

| Life test | Steady-state life | Method 1005 test condition B +125 °C, 1000 h | The steady-state life test is performed to demonstrate the quality or reliability of devices subjected to specific conditions over an extended time period. |

| Research Approach | Methods | Conclusions | References |

|---|---|---|---|

| Experiment, finite element simulation, model prediction | Temperature cycle test and Coffin–Manson model were used to evaluate the thermal fatigue reliability of solder joints. | The results indicate that the maximum accumulated inelastic hysteric energy in the fine-pitch ball grid array (FBGA) structure at the bottom of the product occurs on solder balls, and the two symmetric angles of the solder balls are prone to thermal fatigue and cracks, with thermal fatigue damage extending rapidly from the outer ball array to the inner ball array. By analyzing the failure data of solder balls, a thermal fatigue failure criterion was defined, where the critical failure probability value was approximately 80%. | Zhi-Hao Zhang [116] |

| Experiment, finite element simulation, model prediction | Thermal shock, the off-line coupling test of temperature cycle and thermal shock, as well as Knecht–Fox model were used to evaluate the reliability of solder joints. | The results indicate that both the top and bottom solder joints of PoP packaging show periodic changes in strain, with stress mainly concentrated on the solder joints and chips, and with solder joints being the most prone to failure. The maximum stress of the bottom chip is greater than that of the top chip, and the overall stress of the bottom solder joint is greater than that of the top solder joint. Moreover, the maximum stress of the bottom solder ball is located on the corner solder ball at the outermost corner of the solder ball array. | Wang Yang [117] |

| Experiment | Moiré interferometry was used to measure the warpage deformation of the ball grid array (BGA) in the upper and lower layers of PoP packaging devices during reflow welding. Moreover, the reliability of PoP packaging with different assembly processes under the same warpage condition was compared and analyzed via accelerated temperature cycling and four-point bending cycle tests. | The results indicate that the top-layer BGA of PoP packaging can have a high reliability whether dipped with flux or solder paste, whereas the bottom-layer BGA is significantly less reliable when dipped with solder paste in the four-point bending cycle test. | Wang Hongxia [118] |

| Experiment, finite element simulation, model prediction | Thermal shock test and Knecht–Fox model were used to evaluate the reliability of solder joints. | The results indicate that the stress of the entire packaging is concentrated on the internal chip and solder joints, with the maximum stress at the corner solder joints of the bottom solder ball array, which is the weak link of PoP packaging devices. Moreover, the stress of each row of solder balls shows a trend of gradually increasing from the center to the edge, and there is no significant difference between the stress of each row of balls at the top. The larger the size of the packaging chip, the lower the reliability of solder joints. | Xiusheng [119] |

| Finite element simulation | Finite element simulation was used to evaluate the reliability of solder joints under temperature cycling load. | The results indicate that the key solder ball is located in the solder balls in the diagonal corner of the bottom packaging. The reliability of solder joints can be improved by increasing the diameter and spacing of solder balls and reducing the thickness of the bottom packaging. In addition, the selection of an appropriate bottom filler and bonding material is also helpful for improving the reliability of solder joints. | Zhaohui Chen [120] |

| Research Approach | Methods | Conclusions | References |

|---|---|---|---|

| Finite element simulation | Finite element simulation was used to study the influence of moisture stress introduced by hygroscopic expansion and thermal stress introduced during reflow welding on the reliability of PoP packaging. | The results indicate that the maximum hygrothermal–mechanical stress occurs at the corners of the solder ball at the packaging edge, and the hygrothermal–mechanical stress of the top packaging chip is greater than that of the bottom packaging chip. The hygrothermal–mechanical stress of the outer solder ball is larger than that of the inner solder ball, and the hygrothermal–mechanical stress of the solder ball mainly occurs at the corners. | Liu Hailong [121] |

| Experiment, finite element simulation | High-temperature storage and damp heat test were used to evaluate the reliability of PoP packaging solder joints. | The results indicate that the hygrothermal stress at 85 °C/85% RH has no significant effect on the warpage of PoP packaging, but the thermal stress leads to a larger warpage of PoP packaging, with the increasing the thickness of IMC. | Liu Hailong [122] |

| Experiment, finite element simulation | Finite element simulation and a damp heat test were used to evaluate the reliability of the top, bottom, and entire PoP packaging. | The results indicate that the overall moisture absorption of PoP packaging is greater than the sum of two individual components, but the warping deformation is less than either of the two individual components. | A. Guedon-Gracia [123] |

| Experiment, finite element simulation | Damp heat, reflow welding, and temperature cycling tests were used to evaluate the reliability of the TMV structure. | The results indicate that the critical position is located at the outer edge of the electrocoppering solder pad under reflow temperature and hygrothermal load conditions. The strain energy release rate of delamination between the copper and molding compound interface depends on the coefficient of thermal expansion and the elastic modulus of the molding compound. With the increase in the CME of the molding compound, the strain energy release rate sharply increases. The strain energy release rate of the outer edge delamination of the electrocoppering pad sharply increases with the increase in the thickness of plated copper. Moreover, it can increase with the increase in the length of the copper plate under reflux load. When the delamination length is less than 10 μm at 150 °C, it increases with the increase in the delamination length and decreases with the increase in the thickness of the molding plastic. | Zhaohui Chen [124] |

| Research Approach | Methods | Conclusions | References |

|---|---|---|---|

| Experiment, finite element simulation | Random vibration test and finite element simulation were used to evaluate the reliability of PoP packaging devices subjected to dynamic stress. | The results indicate that the reliability of the bottom component of PoP packaging is significantly lower than that of the top component, and the outermost solder ball of the bottom component is the weak link in PoP packaging under a vibration load. | Xia Jiang [125] |

| Experiment, finite element simulation, model prediction | Sinusoidal vibration test and rain-flow counting method were used to evaluate the vibration fatigue characteristics and reliability of PoP packaging. | The results indicate that the dynamic response of PoP packaging shows a strong nonlinearity. Using the same cycle times, the higher the order of magnitude of input, the lower the reliability. | Bing Yang [126] |

| Experiment, finite element simulation | Random vibration test was used to evaluate the reliability of solder joints and then analyze the influence of PoP packaging size on reliability. | The results indicate that the maximum stress in the bottom package occurs at the corners of the outermost solder ball array, and the maximum stress in the top package occurs at the corners of the innermost solder ball array. The change in the heights of solder joints has a great impact on the stress of the bottom-package solder joint, whereas it has less of an influence on the stress of top-package solder joints. The stress of top-package solder joints significantly increases as the standoff increases and decreases with increasing diameter. The combination height of the molding compound and the bump in the top package is proportional to the maximum stress of the top package and inversely proportional to the maximum stress of the bottom package. | Tang Haili [127] |

| Experiment, finite element simulation | Temperature cycling test and thermal vibration test were used to evaluate the reliability of PoP packaging solder joints. | The results indicate that the stress changes in the solder joints show a synchronous and opposite trend with the change in temperature, and the stress at the solder joint decreases with the increase in holding time during the holding stage. Different conditions such as temperature, holding time, and temperature change rate can all have an impact on random vibration. When subjected to random vibration at high temperature, the maximum stress of the solder joint is greater than that at low temperatures, and the solder joint stress is transferred from the central part of the inner-ring solder joint to the outer-ring solder joint. | Liu Zhaoyun [128] |

| Experiment, finite element simulation | Finite element method was used to simulate the reliability of PoP packaging components with different structural sizes and materials under dynamic stress and drop impact load. | The results indicate that the maximum normal tensile stress of solder joints decreases with the increase in PCB damping and solder joint diameter. The maximum normal tensile stress of truncated spherical solder joint is greater than that of cylindrical solder joint. The maximum tensile stress of lead-free solder joints decreases with the increase in tin content, and the maximum tensile stress is greater than that of the tin–lead solder joint. | Fan Zerui [129] |

| Experiment, finite element simulation | Finite element method was used to simulate the dynamic response of PoP packaging components under drop impact load and then analyze the failure mechanism of solder joints. | The results indicate that the maximum normal tensile stress of key solder joints in PoP packaging components decreases with the increase in PCB damping and solder joint diameter. The maximum normal tensile stress of a truncated spherical solder joint is greater than that of a cylindrical solder joint. The maximum tensile stress of lead-free solder joints is greater than that of tin–lead solder joints, and for lead-free solder, the maximum tensile stress of corner solder joints decreases with the increase in tin content. | Yao Xiaohu [130] |

| Research Approach | Methods | Conclusions | References |

|---|---|---|---|

| Experiment, finite element simulation, model prediction | Temperature cycle test, Taguchi method, and Arrenius high-acceleration model were used to evaluate the reliability of IMC solder joints and Sn3.9Ag0.6Cu solder joints. | The results indicate that the maximum stress–strain was observed in the second solder joint on the diagonal of the IMC solder joint array. For the Sn3.9Ag0.6Cu solder joint array, the corner solder joints show the maximum stress–strain values, and these areas are the locations of crack propagation. The stress–strain and fatigue life of solder joints are more sensitive to residence and temperature, especially high temperatures. Increasing temperature or residence time, or decreasing temperature, can reduce the stress–strain levels of solder joints and extend their fatigue life. | Liang Zhang [131] |

| Experiment, finite element simulation | The effect of high-temperature storage (HTS) on the stress in and around Cu TSVs in 3D stacked chips was studied using scanning white-beam X-ray microdiffraction. | The results indicate that high-temperature stress can reduce the bonding force of copper and silicon in TSV and accelerate the aging and reduce the reliability of TSV in the long term. | Tengfei Jiang [132] |

| Experiment, finite element simulation | Temperature cycling test and finite element simulation were used to study the reliability of the TSV structure. | The results indicate that the maximum thermal stress occurs not only at the nickel annular edge but also at the corners of pads. This may result in failure or delamination of TSV pads. The maximum Von Mises stress increases with the diameter ratio and pad diameter. Based on these results, this study helps to obtain a clear thermal stress distribution of the TSV array, and possible failure regions in the TSV structure are identified. | H.-Y. Tsai [133] |

| Finite element simulation | Finite element simulation was used to evaluate the influence of temperature cycling stress on the reliability of the TSV structure and interface. | The residual thermal stress largely occurs at the interface of the bottom TSV chip and PCB due to the mismatch of CTE. The stress in the outer corner of the TSV array is significantly higher than that in the center. The Cu/SAC305/Cu interconnect between the chips has very little influence on the maximum interfacial stress of the TSV structure, and the solder suffers from relatively low stress. On the other hand, the accumulated plastic strain of copper increases as the thermal cycle increases and ultimately reaches a static hardening state. The TSV device suffers a similar equivalent stress at high and low temperatures with different stress states; a large standoff height of Cu-Cu interconnects will help relieve stress in the device. | Hui-Hui Yuwen [134] |

| Finite element simulation | Finite element simulation was used to evaluate the reliability of ball bumps under temperature cycling load. | The results indicate that Von Mises plastic strain increases with the increase in the number of stacked chips. The metal bumps in lower layers have greater Von Mises plastic strain than upper layers on average. The bump outside has a greater general Von Mises plastic strain than that inside. The weak point of this stacking structure in a 3D chip lies in the metal bumps on the edge of the substrate. | Zhou Zhang [135] |

| Research Approach | Methods | Conclusions | References |

|---|---|---|---|

| Experiment, finite element simulation | Damp heat test and reflow welding test were used to evaluate the reliability of CoC packaging components. | The results indicate that, in a hygrothermal environment, moisture absorption between the substrate and bonding layers of each chip is much lower than that of the plastic packaging material, and the moisture absorption of the bottom bonding layer is higher than that of the top bonding layer. Moreover, the maximum hygrothermal stress and thermal stress in the reflow soldering test are both in the corners of the bottom chip, and their values are 1.3 times higher than those for pure thermal stress. | Tang Yu [136] |

| Finite element simulation | Finite element method was used to simulate the influence of moisture diffusion and hygrothermal stress on the reliability of CoC packaging devices. | The simulation results show that the bottom die-attach endured higher thermal stress conditions after moisture preconditioning under 85 ć/85% RH. In a simulation of hygroscopic swelling stress during the reflow process, it was indicated that the critical position for package reliability is located at the corner of the bottom die and the interface between the bottom die-attach and die. The reliability of the bottom layers is relatively low in a hygrothermal environment. | Wenmin Zhu [137] |

| Finite element simulation | Finite element method was used to simulate the influence of moisture diffusion and hygrothermal stress on the reliability of CoC packaging devices. | The results show that the substrate and bottom adhesive are rapidly absorbed during a moisture diffusion simulation. This reduces the mechanical properties of the stacked die, and this finding may provide a valid solution that can prevent the current failures observed in the industry. | Z K Hua [138] |

| Finite element simulation | Finite element method was used to simulate the influence of moisture diffusion and hygrothermal stress on the reliability of CoC packaging devices. | The results indicate that the influence of hydrothermal stress is greater than that of individual thermal stress, and the hydrothermal stress is about 1.3 times higher than thermal stress on average. The suspension area between the top chip and the spacer is a dangerous location for chip stress concentration, which is a unique phenomenon of CoC packaging. | Ye Anlin [139] |

| Finite element simulation | Finite element method was used to simulate the influence of moisture diffusion and hygrothermal stress on the reliability of CoC packaging devices. | The results indicate that the moisture desorption during the reflow welding process is faster than that in pretreatment. The maximum stress appears in the bottom chip and the bonding layer of chip interconnection. Hygroscopic expansion and internal vapor pressure can exert a significant impact on stress. Furthermore, the combined stress and warpage are far greater than a single stress factor. Under the combined effects of hygro-mechanical stress, thermal–mechanical stress, and vapor-pressure-induced stress, the strain energy release rate increases with temperature during reflow. | Jing Wang [140] |

| Research Approach | Methods | Conclusions | References |

|---|---|---|---|

| Finite element simulation | Finite element method was used to simulate the reliability of solder joints under random vibration and temperature cycles. | The results indicate that the design of screw fixing points on printed circuit boards is key to improving the reliability of 3D-Plus memory board level assembly, and the reliability can be further improved using epoxy adhesive reinforcement. | Lv Qiang [141] |

| Finite element simulation | Finite element simulation and Anand model were used to evaluate the effects of tin–lead solder 63Sn37Pb and lead-free solder 95.5Sn3.8Ag0.7Cu on the reliability of 3D-Plus memory solder joints. | The results indicate that the solder joint stress and plastic strain show significant periodic changes. By comparing the two equivalent stress and plastic strain curves of lead-free solder and tin–lead solder, it can be found that the reliability of 95.5Sn3.8Ag0.7Cu solder is greater than that of 63Sn37Pb solder. | Nuo Bao [142] |

| Experiment, finite element simulation | Finite element simulation and thermal shock test were used to evaluate the reliability of solder joints. | The results indicate that the failure of solder joints is mainly caused by thermal fatigue, and the cracks are caused by the accumulation of plastic and creep strains. Crack initiation and propagation are mainly affected by the accumulation of inelastic strain, with the change trend affected by the difference in thermal expansion coefficients. | Zhou Shuai [143] |

| Experiment | Anti-radiation tests, such as total ionization dose (TID) and single-event effects (SEE), were used to evaluate the reliability of products for space applications. | The results indicate that the device can withstand a total ionizing dose of 100 Krad (Si) and a SEE of 60 MeV/mg·cm2, meeting the requirements of aerospace missions. | T.Dargines [144] |

| Experiment | Temperature, humidity, electrical stress, vibration, and impact tests were used to evaluate product reliability. | The results indicate that the device can function normally within the temperature range of −55–125 °C and withstand a high order of mechanical stress and thermal stress, much higher than industrial/commercial 3D packaging memory products, thus further proving the applicability of the product in the field of high reliability. | Jeannette Plante [53] |

| Research Approach | Methods | Conclusions | References |

|---|---|---|---|

| Finite element simulation | Finite element simulation and numerical analysis were used to discuss the influence of cracks and thermal–mechanical coupling loads on the reliability of TSV structure. | The results indicate that the crack propagation of the TSV structure is influenced by the coupling factors of material plasticity, crack length, location, direction, crack number, and load conditions. Thermal–mechanical coupling loads can significantly improve the capability of crack propagation. | Zhengwei Fan [145] |

| Finite element simulation | Finite element simulation was used to study the reliability of a 3D packaging CSP solder joint under thermal–vibration coupling loads. | The results indicate that the stress–strain distribution in solder joints is uneven, with the maximum stress–strain at the outermost corner of the solder joint array, and the stress–strain at the top solder joint is greater than that at the bottom solder joint. | LiShuai Han [146] |

| Finite element simulation | Finite element simulation was used to analyze the influence of electric–thermal coupling loads on the reliability of TSV structure. | The results indicate that there is a large current density and equivalent stress at the corner of the TSV/Micro-bumps interface, which easily leads to the failure of TSV structure. The electro-thermal–mechanical reliability of the TSV structure can be improved by increasing the diameter and decreasing the length of the through-holes. With the increase in SiO2 layer thickness, the maximum current density increases, and the maximum equivalent stress decreases. | YU Sijia [147] |

| Finite element simulation | Finite element simulation was used to analyze the influence of wet–thermal coupling loads on the reliability of 3D CoC packaging. | The results show that the most susceptible region for reliability risk impact in 3D chip-stacked packages is the interface between the solder ball, corresponding layer, and substrate. The hygrothermal coupling equivalent stresses near the solder ball edges are the most demanding in the package. | Tingting Zhao [148] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, S.; Ma, K.; Wu, Y.; Liu, P.; Hu, X.; Nie, G.; Ren, Y.; Qiu, B.; Cai, N.; Xu, S.; et al. Survey of Reliability Research on 3D Packaged Memory. Electronics 2023, 12, 2709. https://doi.org/10.3390/electronics12122709

Zhou S, Ma K, Wu Y, Liu P, Hu X, Nie G, Ren Y, Qiu B, Cai N, Xu S, et al. Survey of Reliability Research on 3D Packaged Memory. Electronics. 2023; 12(12):2709. https://doi.org/10.3390/electronics12122709

Chicago/Turabian StyleZhou, Shuai, Kaixue Ma, Yugong Wu, Peng Liu, Xianghong Hu, Guojian Nie, Yan Ren, Baojun Qiu, Nian Cai, Shaoqiu Xu, and et al. 2023. "Survey of Reliability Research on 3D Packaged Memory" Electronics 12, no. 12: 2709. https://doi.org/10.3390/electronics12122709

APA StyleZhou, S., Ma, K., Wu, Y., Liu, P., Hu, X., Nie, G., Ren, Y., Qiu, B., Cai, N., Xu, S., & Wang, H. (2023). Survey of Reliability Research on 3D Packaged Memory. Electronics, 12(12), 2709. https://doi.org/10.3390/electronics12122709