Simple and Accurate Model for the Propagation Delay in MCML Gates

Abstract

:1. Introduction

2. Review of the MCML Inverter Delay Model

2.1. Propagation Delay

2.2. Evaluating the Parameters of the Delay Model

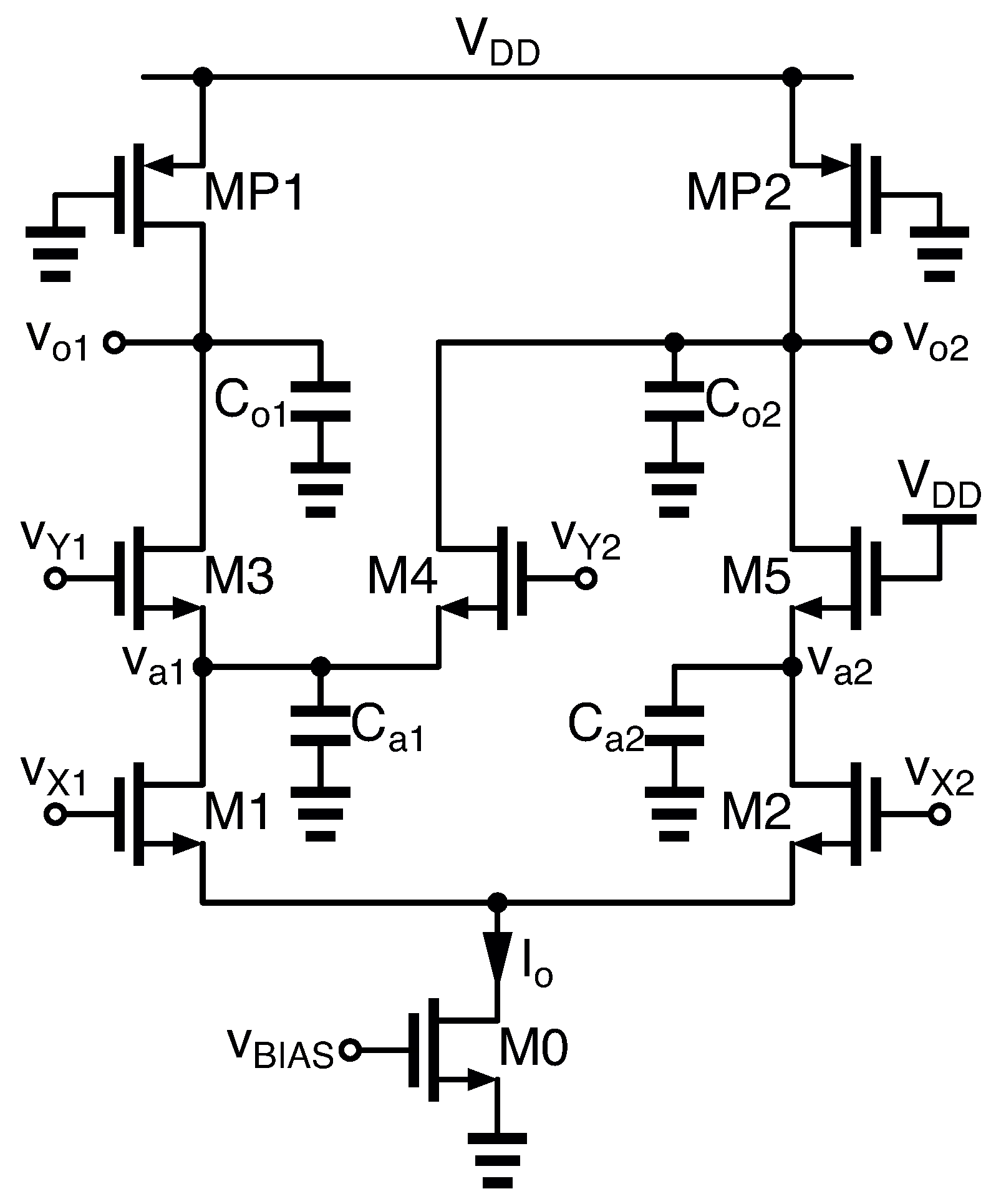

3. MCML Universal Gate Delay Model

3.1. Simplified Analysis of Transitions T9/T10

3.2. Propagation Delay

3.3. Effect of the Asymmetry

3.4. Evaluating the Parameters of the Delay Model

4. Delay Model Validation and Comparison

4.1. 65-nm Standard CMOS

4.2. 28-nm FD-SOI

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Appendix A. First Order Analysis of Asymmetrical Universal Gate

Appendix B. Equivalent Capacitors from Simulation Data

Appendix B.1. BSIM Model of the Channel Charge

Appendix B.2. MCML Inverter

Appendix B.3. MCML Universal Gate

References

- Tang, D.D.; Solomon, P.M. Bipolar Transistor Design for Optimized Power-Delay Logic Circuits. IEEE J. Solid-State Circuits 1979, SC-14, 679–684. [Google Scholar] [CrossRef]

- Chor, E.F.; Brunnschweiler, A.; Ashburn, P. A Propagation-Delay Expression and its Application to the Optimization of Polysilicon Emitter ECL Processes. IEEE J. Solid-State Circuits 1988, 23, 251–259. [Google Scholar] [CrossRef]

- Fang, W. Accurate Analytical Delay Expressions for ECL and CML Circuits and Their Applications to Optimizing High-Speed Bipolar Circuits. IEEE J. Solid-State Circuits 1990, 25, 572–583. [Google Scholar] [CrossRef]

- Fang, W.; Brunnschweiler, A.; Ashburn, P. An analytical maximum toggle frequency expression and its application to optimizing high-speed ECL frequency dividers. IEEE J. Solid-State Circuits 1990, 25, 920–931. [Google Scholar] [CrossRef]

- Konstadinidis, G.; Berger, H. Optimization of Buffer Stages in Bipolar VLSI Systems. IEEE J. Solid-State Circuits 1992, 27, 1002–1013. [Google Scholar] [CrossRef]

- Yang, A.; Chang, Y.H. Physical timing modeling for bipolar VLSI. IEEE J. Solid-State Circuits 1992, 27, 1245–1254. [Google Scholar] [CrossRef]

- Ghannam, M.; Mertens, R.; van Overstraeten, R. An Analytical for the Determination of the Transient Response of CML and ECL Gates. IEEE Trans. Electron Devices 1990, 37, 191–201. [Google Scholar] [CrossRef]

- Sharaf, K.; Elmasry, M. An accurate analytical propagation delay model for high-speed CML bipolar circuits. IEEE J. Solid-State Circuits 1994, 29, 31–45. [Google Scholar] [CrossRef]

- Harada, Y. Delay components of a current mode logic circuit and their current dependency. IEEE J. Solid-State Circuits 1995, 30, 54–60. [Google Scholar] [CrossRef]

- Alioto, M.; Palumbo, G. Modelling and Design Considerations on CML Gates Under High-Current Effects. Int. J. Circ. Theor. Appl. 2005, 33, 503–518. [Google Scholar] [CrossRef]

- Alioto, M.; Palumbo, G. Highly accurate and simple models for CML and ECL gates. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1999, 18, 1369–1375. [Google Scholar] [CrossRef]

- Alioto, M.; Palumbo, G. Modeling and optimized design of current mode MUX/XOR and D flip-flop. IEEE Trans. Circuits Syst. II 2000, 47, 452–461. [Google Scholar] [CrossRef]

- Alioto, M.; Palumbo, G.; Pennisi, S. Modeling of Source Coupled Logic Gates. Int. J. Circ. Theor. Appl. 2002, 30, 459–477. [Google Scholar] [CrossRef]

- Alioto, M.; Palumbo, G. Power-aware design techniques for nanometer MOS current-mode logic gates: A design framework. IEEE Circuits Syst. Mag. 2006, 6, 40–59. [Google Scholar] [CrossRef]

- Musa, O.; Shams, M. An Efficient Delay Model for MOS Current-Mode Logic Automated Design and Optimization. IEEE Trans. Circuits Syst. I 2010, 57, 2041–2052. [Google Scholar] [CrossRef]

- Centurelli, F.; Scotti, G.; Trifiletti, A.; Palumbo, G. Delay models and design guidelines for MCML gates with resistor or PMOS load. Microelectron. J. 2020, 99, 104755. [Google Scholar] [CrossRef]

- Alioto, M.; Palumbo, G. CML and ECL: Optimized Design and Comparison. IEEE Trans. Circuits Syst. I 1999, 46, 1330–1341. [Google Scholar] [CrossRef]

- Alioto, M.; Palumbo, G. Design Strategy for Source Coupled Logic Gates. IEEE Trans. Circuits Syst. I 2003, 50, 640–654. [Google Scholar] [CrossRef] [Green Version]

- Alioto, M.; Palumbo, G. Design strategies of cascaded CML gates. IEEE Trans. Circuits Syst. II 2006, 53, 85–89. [Google Scholar] [CrossRef]

- Alioto, M.; Mita, R.; Palumbo, G. Design of High-Speed Power-Efficient MOS Current-Mode Logic Frequency Dividers. IEEE Trans. Circuits Syst. II 2006, 53, 1165–1169. [Google Scholar] [CrossRef]

- Scotti, G.; Trifiletti, A.; Palumbo, G. A Novel 0.5 V MCML D-Flip-Flop Topology Exploiting Forward Body Bias Threshold Lowering. IEEE Trans. Circuits Syst. II 2020, 67, 560–564. [Google Scholar] [CrossRef]

- Palumbo, G.; Scotti, G. A Multi-Folded MCML for Ultra-Low-Voltage High-Performance in Deeply Scaled CMOS. IEEE Trans. Circuits Syst. I 2020, 67, 4696–4706. [Google Scholar] [CrossRef]

- Centurelli, F.; Scotti, G.; Trifiletti, A.; Palumbo, G. Design of Low-Voltage Power Efficient Frequency Dividers in Folded MOS Current Mode Logic. IEEE Trans. Circuits Syst. I 2021, 68, 680–691. [Google Scholar] [CrossRef]

- Centurelli, F.; Scotti, G.; Palumbo, G. A Very-Low-Voltage Frequency Divider in Folded MOS Current Mode Logic with Complementary n- and p-type Flip-Flops. IEEE Trans. VLSI Syst. 2021, 29, 998–1008. [Google Scholar] [CrossRef]

- Kundan, J.; Hasan, S. Enhanced folded source-coupled logic technique for low-voltage mixed-signal integrated circuits. IEEE Trans. Circuits Syst. II 2000, 47, 810–817. [Google Scholar] [CrossRef]

- Leung, B. VLSI for Wireless Communication; Prentice Hall: Hoboken, NJ, USA, 2002. [Google Scholar]

- Razavi, B. Prospect of CMOS technology for high-speed optical communication circuits. IEEE J. Solid-State Circuits 2002, 37, 1135–1145. [Google Scholar] [CrossRef]

- Razavi, B. Design of Integrated Circuits for Optical Communications; McGraw-Hill Inc.: Boston, MA, USA, 2003. [Google Scholar]

- Yektaei, M.; Ghaznavi-Ghoushchi, M.B. PDP and TPD flexible MCML and MTCML ultralow-power and high-speed structures for wireless and wireline application. IEEE Trans. VLSI Syst. 2020, 28, 1782–1795. [Google Scholar] [CrossRef]

- Allstot, D.; Kiaei, S.; Zele, R. Analog logic techniques steer around the noise. IEEE Circuits Devices Mag. 1993, 9, 18–21. [Google Scholar] [CrossRef]

- Anis, M.; Allam, M.; Elmasry, M. Impact of technology scaling on CMOS logic styles. IEEE Trans. Circuits Syst. II 2002, 49, 577–588. [Google Scholar] [CrossRef]

- Alioto, M.; Palumbo, G. Model and Design of Bipolar and MOS Current Mode Logic: CML, ECL and SCL Digital Circuits; Springer: Dordrecht, The Netherlands, 2005. [Google Scholar]

- Jang, I.; Lee, Y.; Kim, S.; Kim, J. Power-Performance Tradeoff Analysis of CML-Based High-Speed Transmitter Designs Using Circuit-Level Optimization. IEEE Trans. Circuits Syst. I 2016, 63, 540–550. [Google Scholar] [CrossRef]

- Bai, Y.; Song, Y.; Bojnordi, M.N.; Shapiro, A.; Friedman, E.G.; Ipek, E. Back to the Future: Current-Mode Processor in the Era of Deeply Scaled CMOS. IEEE Trans. VLSI Syst. 2016, 24, 1266–1279. [Google Scholar] [CrossRef]

- Srivastava, P.; Yadav, R.; Srivastava, R. Robust circuit implementation of 4-bit 4-tube CNFET based ALU at 16-nm technology node. Analog Integr. Circuits Signal Process. 2021, 109, 127–134. [Google Scholar] [CrossRef]

- Centurelli, F.; Scotti, G.; Palumbo, G. 0.5-V Frequency Dividers in Folded MCML Exploiting Forward Body Bias: Analysis and Comparison. Electronics 2021, 10, 1383. [Google Scholar] [CrossRef]

- Rafiee, M.; Ghaznavi-Ghoushchi, M.B. Low-voltage and high-speed stand-alone multiple-input complex gates for error correction coding applications. Int. J. Circ. Theor. Appl. 2021, 49, 921–937. [Google Scholar] [CrossRef]

- Mita, R.; Palumbo, G.; Poli, M. Propagation Delay of an RC-Chain with a Ramp Input. IEEE Trans. Circuits Syst. II 2007, 54, 66–70. [Google Scholar] [CrossRef]

- Mita, R.; Palumbo, G. Propagation delay of an RC-circuit with a ramp input: An analytical very accurate and simple model. Int. J. Circ. Theor. Appl. 2009, 37, 987–994. [Google Scholar] [CrossRef]

- Rabaey, T.M. Digital Integrated Circuits—A Design Perspective; Prentice Hall: Hoboken, NJ, USA, 1996. [Google Scholar]

| Transition | Transition | ||||||

|---|---|---|---|---|---|---|---|

| T1 (LL → LH) | L | ↑ | H | T7 (HH → HL) | H | ↓ | ↑ |

| T2 (LH → LL) | L | ↓ | H | T8 (HL → HH) | H | ↑ | ↓ |

| T3 (LL → HL) | ↑ | L | H | T9 (HH → LH) | ↓ | H | ↑ |

| T4 (HL → LL) | ↓ | L | H | T10 (LH → HH) | ↑ | H | ↓ |

| T5 (LH → HL) | ↑ | ↓ | H | T11 (HH → LL) | ↓ | ↓ | ↑ |

| T6 (HL → LH) | ↓ | ↑ | H | T12 (LL → HH) | ↑ | ↑ | ↓ |

| Transistor | 65-nm CMOS [nm/nm] | 28-nm FD-SOI [nm/nm] |

|---|---|---|

| M0 | 2000/240 | 1000/120 |

| M1, M2, M3 *, M4 *, M5 * | 300/60 | 320/30 |

| MP1, MP2 | 135/205 | 80/94 |

| Parameter | 65-nm CMOS | 28-nm FD-SOI | ||||

|---|---|---|---|---|---|---|

| ‘H’ | ‘L’ | avg | ‘H’ | ‘L’ | avg | |

| [fF] | 0.821 | 0.964 | 0.893 | 0.532 | 0.589 | 0.561 |

| [fF] | 0.964 | 0.821 | 0.893 | 0.589 | 0.532 | 0.561 |

| [S] | 32.38 | 66.63 | 49.50 | 16.10 | 49.38 | 32.74 |

| [S] | 66.63 | 32.38 | 49.50 | 49.38 | 16.10 | 32.74 |

| Parameter | 65-nm CMOS | 28-nm FD-SOI | ||||

|---|---|---|---|---|---|---|

| ‘H’ | ‘L’ | avg | ‘H’ | ‘L’ | avg | |

| [fF] | 0.833 | 0.962 | 0.898 | 0.426 | 0.518 | 0.472 |

| [fF] | 1.164 | 1.044 | 1.104 | 0.636 | 0.543 | 0.589 |

| [fF] | 0.968 | 0.779 | 0.873 | 0.530 | 0.433 | 0.482 |

| [fF] | 0.569 | 0.740 | 0.654 | 0.317 | 0.411 | 0.364 |

| [S] | 35.11 | 66.25 | 50.68 | 16.76 | 49.33 | 33.04 |

| [S] | 66.16 | 34.95 | 50.55 | 48.30 | 16.66 | 32.98 |

| [A/V] | 149.2 | 8.900 | 79.05 | 141.0 | 1.440 | 71.22 |

| [A/V] | 8.800 | 149.4 | 79.10 | 1.440 | 140.9 | 71.17 |

| [1,2,3,4] | [5,6] | [8,9] | [10,11,12] | [17,18,19,20] | This Work | |

|---|---|---|---|---|---|---|

| Technology | Bipolar | Bipolar | Bipolar | Bipolar | MOS | MOS |

| Strategy | Sensitivity analysis | Average branch current | Linear device model | Small-signal model (1 pole) | Small-signal model (1 pole) | Small-signal model (2 poles) |

| Model complexity | Complex | Simple | Average | Simple | Simple | Simple |

| Number of parameters | High | Average | Average | Low | Low | Low |

| Model accuracy | Average | Low | Low | High | High | Higher |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Giustolisi, G.; Scotti, G.; Palumbo, G. Simple and Accurate Model for the Propagation Delay in MCML Gates. Electronics 2023, 12, 2680. https://doi.org/10.3390/electronics12122680

Giustolisi G, Scotti G, Palumbo G. Simple and Accurate Model for the Propagation Delay in MCML Gates. Electronics. 2023; 12(12):2680. https://doi.org/10.3390/electronics12122680

Chicago/Turabian StyleGiustolisi, Gianluca, Giuseppe Scotti, and Gaetano Palumbo. 2023. "Simple and Accurate Model for the Propagation Delay in MCML Gates" Electronics 12, no. 12: 2680. https://doi.org/10.3390/electronics12122680

APA StyleGiustolisi, G., Scotti, G., & Palumbo, G. (2023). Simple and Accurate Model for the Propagation Delay in MCML Gates. Electronics, 12(12), 2680. https://doi.org/10.3390/electronics12122680